# MODEM TRANSMIT/RECEIVE CLOCK GENERATOR

- INDEPENDANT TRANSMIT AND RECEIVE CLOCK GENERATORS WITH DIGITAL PHASE LOCKED LOOPS

- TRANSMIT DPLL SYNCHRONIZATION ON EXTERNAL TERMINAL CLOCK OR INTERNAL RECEIVE CLOCK

- RECEIVE DPLL SYNCHRONIZATION CON-TROLLED FROM THE BUS

- FOUR EXTERNAL CLOCKS AVAILABLE, PLE-SIOCHRONOUS ON TRANSMIT AND RE-CEIVE CHANNELS:

- BIT RATE CLOCK

- BAUD RATE CLOCK

- SAMPLING CLOCK

- MULTIPLEXING CLOCK

- DIRECT INTERFACE WITH STANDARD MPU 8-BIT BUS

- LOW POWER CMOS TECHNOLOGY

- AVAILABLE IN DIL OR SURFACE MOUNT PACKAGE

### DESCRIPTION

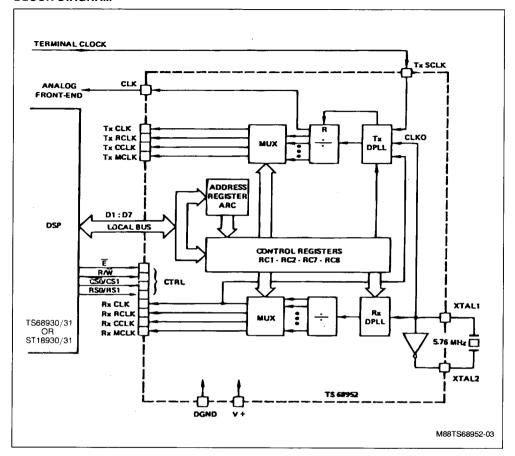

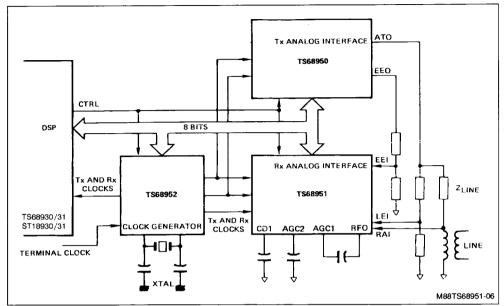

The TS68952 is a Clock Generator circuit designed to generate all the necessary clocks frequencies needed by high-speed modems applications.

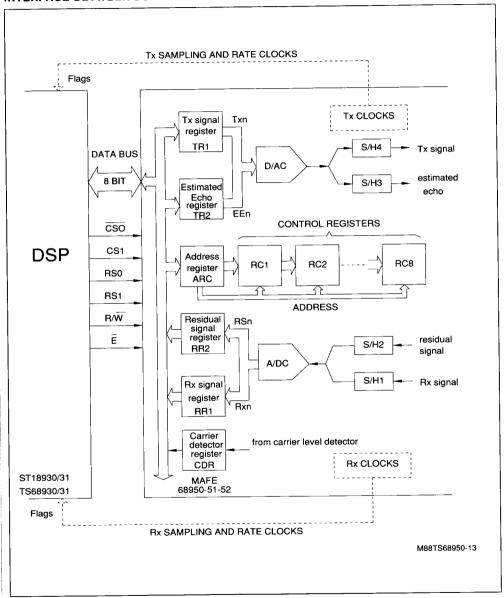

The TS68952 copes with all the CCITT recommendations from V.22 to V.33 including full-duplex recommendations. Used in conjunction with the TS68950 Transmit (Tx) Analog Front-End circuit and the TS68951 Receive Analog Front-End\*, it provides a very cheap and efficient interface to digital signal processing functions in high speed modems.

\*The interconnection between the 3 chics of the Modem Analog

\* The interconnection between the 3 chips of the Modern Analog Front-end (MAFE) and a DSP is decribed page 11/17.

November 1988

1/17

# **BLOCK DIAGRAM**

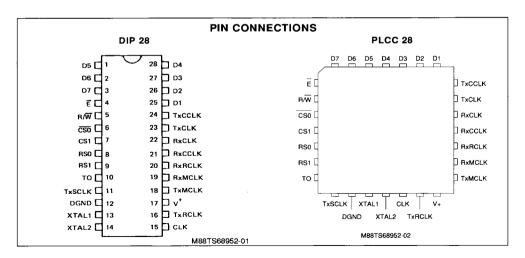

#### PIN FUNCTIONS

| Name           | Function                                                                                                                                                                                                         |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D1-D7          | Data Bus Inputs to Internal Registers. (DO is not used)                                                                                                                                                          |

| Ē              | Enable Input. Data are strobed on the positive transitions of this input.                                                                                                                                        |

| R/W            | Read/Write Selection Input. Internal registers can be written when R/W = 0. Reading mode is only used for Rx analog front-end chip.                                                                              |

| CS0-CS1        | Chip Select Inputs. The chip set is selected when $\overline{\text{CS0}}$ = 0 and $\overline{\text{CS1}}$ = 1                                                                                                    |

| RS0-RS1        | Register Select Inputs. Used to select address or control registers.                                                                                                                                             |

| ТО             | Test Output. Must be left open.                                                                                                                                                                                  |

| TxSCLK         | Transmit Synchronizing Clock Input. Normally tied to an external terminal clock. When this pin is tied to a permanent logical level, transmit DPLL free-runs or can be synchronized to the receive clock system. |

| DGND           | Digital Ground = 0 V All digital signals are referenced to this pin.                                                                                                                                             |

| XTAL1          | Crystal Oscillator or Pulse Generator Input                                                                                                                                                                      |

| XTAL2          | Crystal Oscillator Output                                                                                                                                                                                        |

| CLK            | 1.44 MHz Clock output useful for Tx and Rx analog front-end chips.                                                                                                                                               |

| TxRCLK         | Transmit Baud Rate Clock Output                                                                                                                                                                                  |

| V <sup>+</sup> | Positive Power Supply Voltage = + 5 V ± 5 %                                                                                                                                                                      |

| TxMCLK         | Transmit Multiplexing Clock Output                                                                                                                                                                               |

| RxMCLK         | Receive Multiplexing Clock Output                                                                                                                                                                                |

| RxRCLK         | Receive Baud Rade Clock Output                                                                                                                                                                                   |

| RxCCLK         | Receive Conversion Clock Output                                                                                                                                                                                  |

| RxCLK          | Receive Bit Rate Clock Output                                                                                                                                                                                    |

| TxCLK          | Transmit Bit Rate Clock Output                                                                                                                                                                                   |

| TxCCLK         | Transmit Conversion Clock Output                                                                                                                                                                                 |

#### **FUNCTIONAL DESCRIPTION**

The TS68952 is a digital circuit that synthesises all the frequencies required to implement synchronous voice-grade MODEMs from 1200 bps to 19200 bps. It consists of two clock generators using Digital Phase Locked Loops (DPLLs). Frequency programing and DPLL updating can be obtained through four control registers accessed by indirect or cyclical addressing (see p 8117).

This circuit is a part of a three chip Modem Analog Front-End that also includes the TS68950 transmit

analog interface and the TS68951 receive analog interface.

## POWER-UP INITIAL CONDITIONS

Following power-up, the eight transmit and receive clock outputs are undefined and may deliver any frequencies. Control registers RC1 and RC2 must be properly programmed to obtain the requested operation

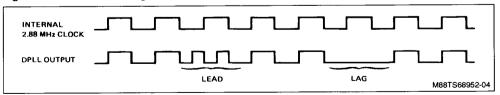

Figure 1: DPLL Lead and Lag.

3/17

### **CLOCK GENERATION**

Master clock is obtained from either a crystal tied between XTAL1 and XTAL2 pins or an external signal connected to the XTAL1 pin; in this case, the XTAL2 pin should be left open. Clock frequency nominal value is 5.76 MHz, but 5.12 MHz and 5.40 MHz frequencies are also specified for particular applications.

The different transmit (Tx) and receive (Rx) clocks are obtained by frequency division in several counters and output selection through digital multiplexers. They can be synchronized on external signal via two independent digital phase locked loops (DPLL).

#### TRANSMIT DPLL

As shown figure 1, the TxDPLL operates by adding or subtracting pulses to a 2.88 MHz internal clock, with a reference frequency that is a submultiple of the programmed "rate clock" frequency. This corresponds to phase leads or phase lags of about 350 ns duration, more precisely, two master clock periods

The TxDPLL can be synchronized on an external terminal clock tied to TxSCLK pin or on the receive bit clock RxCLK internally generated from the RxDPLL. It can also free-run without any phase shift, when the TxSCLK input is tied to a fixed logical level.

## TRANSMIT CLOCKS

The TS68952 delivers four synchronous Tx clocks:

- a bit clock, TxCLK, whose frequency equals the bit rate ot the modem,

- a baud clock, TxRCLK, whose frequency equals the baud rate of the modem,

- a conversion clock, TxCCLK, that gives the sampling frequency of the Tx converter (also used by the Rx converter in echo cancelling applications)

- a multiplexing clock, TxMCLK, usable when several terminals are multiplexed on a single physical link.

The frequencies of these four clocks are programmable through RC1 and RC2 control registers. Their cyclical ratio is exactly 1:2, except for the 16.8 kHz

frequency whose cyclical ratio is slightly modulated around 1:2, and their relative phase locking is ensured without user intervention, by periodic reset of the counters.

Immediate phasing of these clocks on the synchronizing external TxSCLK or internal RxCLK clock can be obtained through bit 7 or RC8 register. The content of this register is automatically cleared after phasing completion.

The TS68952 also delivers, on pin CLK, a 1.44 MHz clock that is synchronous with the Tx clock system and will be used as the main clock to the TS68950/51 analog interface circuits.

#### RECEIVE DPLL

RxDPLL phase shifts are performed by addition and subtraction of pulses from an internal 1.44 MHz clock under the control of RC8 register. Two modes of operation are provided:

- a coarse phase lag whose amplitude has been loaded into RC7 register, can be controlled by one bit of RC8 register. This mode is useful for a fast synchronization of the RxDPLL. The phase lag is obtained by suppressing a variable number of pulses at the input of the counters.

- a fine phase shift with lead or lag amplitude equal to two master clock periods, can be controlled by two bits of RC8. This mode corresponds to normal operation. The phase shifts are obtained by addition or suppression of pulses as indicated in figure 1.

RC8 register is automatically cleared when the programmed phase shift is completed. Simultaneous programming of Tx and Rx control bits of this register has to be avoided.

#### RECEIVE CLOCKS

The TS68952 delivers four Rx clocks with the same nominal frequency values as their Tx counterparts:

- a bit clock RxCLK,

- a baud clock RxRCLK.

- a conversion clock RxCCLK.

- a multiplexing clock RxMCLK.

The Rx and Tx output clocks are plesiochronous.

# BIT CLOCK FREQUENCY PROGRAMMING (Tx and Rx)

|     |     | RC1 | Regis | ter |     |     | _             |                    |                           |

|-----|-----|-----|-------|-----|-----|-----|---------------|--------------------|---------------------------|

| D7  | D6  | D5  | D4    | D3  | D2  | D1  | Ou            | tput Frequency (kF | IZ)                       |

| HB4 | HB3 | HB2 | HB1   | HR3 | HR2 | HR1 | Fa = 5.76 MHz | FQ = 5.40 MHz      | F <sub>Q</sub> = 5.12 MHz |

| 0   | 0   | 0   | 0     |     |     |     | 19.2          |                    |                           |

| 0   | 0   | 0   | 1     |     |     |     | 16.8          |                    |                           |

| 0   | 0   | 1   | 0     |     |     |     | 14.4          |                    |                           |

| 0   | 0   | 1   | 1     |     |     |     | 12.0          |                    |                           |

| 0   | 1   | 0   | 0     |     |     |     | 9.6           |                    |                           |

| 0   | 1   | 0   | 1     |     |     |     | 7.2           |                    | 6.4                       |

| 0   | 1   | 1   | 0     |     |     |     | 6.4           |                    |                           |

| 0   | 1   | 1   | 1     |     |     |     | 6.0           |                    |                           |

| 1   | 0   | 0   | 0     |     |     |     | 4.8           |                    |                           |

| _11 | 0   | 0   | 1     |     |     |     | 3.2           | 3.0                |                           |

| 1   | 0   | 1   | 0     |     |     |     | 2.4           |                    |                           |

| 1   | 0   | 1   | 1     |     |     |     | 1.2           |                    |                           |

| 1   | 1   | 0   | 0     |     |     |     | 0.6           |                    |                           |

| 1   | 1   | 0   | _ 1   |     |     |     | 0.6           |                    |                           |

| 1   | 1_  | 1   | 0     |     | Ċ   |     | 0.6           |                    |                           |

| 1   | 1   | 1   | 1     |     |     |     | 0.6           |                    |                           |

Fo = crystal oscillator frequency.

# RATE CLOCK FREQUENCY PROGRAMMING (Tx and Rx)

|     |     | RC1 | Regis | ster |     |     |                           |                           |                           |  |  |

|-----|-----|-----|-------|------|-----|-----|---------------------------|---------------------------|---------------------------|--|--|

| D7  | D6  | D5  | D4    | D3   | D2  | D1  | Output Frequency (kHZ)    |                           |                           |  |  |

| HB4 | нвз | HB2 | HB1   | HR3  | HR2 | HR1 | F <sub>Q</sub> = 5.76 MHz | F <sub>Q</sub> = 5.40 MHz | F <sub>Q</sub> = 5.12 MHz |  |  |

|     |     |     |       | 0    | 0   | 0   | 2.4                       |                           | 2.133                     |  |  |

|     |     |     |       | 0    | 0   | 1   | 2.0*                      |                           |                           |  |  |

|     |     |     |       | 0    | 1   | 0   | 1.6**                     | 1.5                       |                           |  |  |

|     |     |     |       | 0    | 1   | 1   | 1.2                       |                           |                           |  |  |

|     |     |     |       | 1    | 0   | 0   | 0.6                       |                           |                           |  |  |

|     |     |     |       | 1    | 0   | 1   | 0.6                       |                           |                           |  |  |

|     |     |     |       | 1    | 1   | 0   | 0.6                       |                           |                           |  |  |

|     |     |     |       | 1    | 1   | 1   | 0.6                       |                           |                           |  |  |

Note: Phase shift frequency of TxDPLL is 600 Hz excepted for (\*) 1000 Hz and for (\*\*) 800 Hz.

# CONVERSION CLOCK FREQUENCY PROGRAMMING (Tx and Rx)

|     |     | RC2 | Regis | ter        |               |      |                         | tput Frequency (kF        | <b>17</b> \               |                           |  |

|-----|-----|-----|-------|------------|---------------|------|-------------------------|---------------------------|---------------------------|---------------------------|--|

| D7  | D6  | D5  | D4    | D3         | D2            | D1   | Cutput Frequency (kinz) |                           |                           |                           |  |

| нмз | HM2 | HM2 | HM1   | HS2 HS1 HT | S2 HS1 HTHR - | HTHR | _                       | F <sub>Q</sub> = 5.76 MHz | F <sub>Q</sub> = 5.40 MHz | F <sub>Q</sub> = 5.12 MHz |  |

|     |     |     | 0     | 0          |               |      | 9.6                     | 9.0                       | 8.533                     |                           |  |

|     |     |     | 0     | 1          |               |      | 8.0                     | 7.5                       |                           |                           |  |

|     |     |     | 1     | 0          |               |      | 7.2                     |                           |                           |                           |  |

|     |     |     | 1     | 1          |               |      | 7.2                     |                           |                           |                           |  |

# MULTIPLEXING CLOCK FREQUENCY PROGRAMMING (Tx and Rx)

|     |     | RC  | 2 Regis | ster |      |    | Output Frequency (kHz)    |

|-----|-----|-----|---------|------|------|----|---------------------------|

| D7  | D6  | D5  | D4      | D3   | D2   | D1 | Output Frequency (kitz)   |

| нмз | HM2 | HM1 | HS2     | HS1  | HTHR | -  | F <sub>Q</sub> = 5.76 MHz |

| 0   | 0   | 0   |         |      |      |    | 1440                      |

| 0   | 0   | 1   |         |      |      |    | 288                       |

| 0   | 1   | 0   |         |      |      |    | 12                        |

| 0   | 1   | 1   |         |      |      |    | 9.6                       |

| 1   | 0   | 0   |         |      |      |    | 7.2                       |

| 1   | 0   | 1   |         |      |      |    | 4.8                       |

| 1   | 1   | 0   |         |      |      |    | 2.4                       |

| 1   | 1   | 1   |         |      |      |    | 1.2                       |

## Tx SYNCHRONIZATION SIGNAL PROGRAMMING

|     |        | RC  | 2 Regi | ster       |    |    |                        |  |  |

|-----|--------|-----|--------|------------|----|----|------------------------|--|--|

| D7  | D6     | D5  | D4     | D3         | D2 | D1 | Synchronization Signal |  |  |

| нмз | HM2    | HM1 | HS2    | HS1 HTHR - |    |    |                        |  |  |

|     |        |     |        |            | 0  |    | RxCLK                  |  |  |

|     | ļ ———— |     |        |            | 1  |    | TxSCLK (note 1)        |  |  |

Note: 1. TxDPLL free-runs if there is no transition on this input.

# **TXCLOCK GENERAL RESET**

|     | RC  | 8 Regi | ster (n | otes 2, | , 3) |   | The Tx counters are resetted on the first negative-going  |

|-----|-----|--------|---------|---------|------|---|-----------------------------------------------------------|

| D7  | D6  | D5     | D4      | D3      | D 2  |   | transition of the synchronization signal following MPE    |

| MPE | SPR | AVRE   | VAL     | INIT    | _    | - | programming to 1.                                         |

| 1   | 0   | 0      | 0       | 0       |      |   | Next Negative-Going Transition on Synchronization Signal. |

Notes: 2. RC8 register is cleared after the programmed control operation is completed.

3. INIT bit is only used for test purpose.

## RXCLOCK PHASE SHIFT PROGRAMMING

|     | F   | C8 Re | gister | (note 2 | 2) |    |                                                 |  |

|-----|-----|-------|--------|---------|----|----|-------------------------------------------------|--|

| D7  | D6  | D5    | D4     | D3      | D2 | D1 | 1 Action on RxDPLL                              |  |

| MPE | SPR | AVRE  | VAL    | INIT    | •  | -  |                                                 |  |

| 0   | 1   | 0     | 0      | 0       |    |    | Phase Lag of Programmed Amplitude               |  |

| 0   | 0   | 0     | 1      | 0       |    |    | Phase Lag of Two 5.76 MHz Master Clock Periods  |  |

| 0   | 0   | 1     | 1      | 0       |    |    | Phase Lead of Two 5.76 MHz Master Clock Periods |  |

# RXCLOCK PHASE SHIFT AMPLITUDE PROGRAMMING

|     |     | RC  | 7 Regi | ster |     |    | Di Ot in    |            |                        |

|-----|-----|-----|--------|------|-----|----|-------------|------------|------------------------|

| D7  | D6  | D5  | D4     | D3   | D2  | D1 | Phase Shift | in Degrees | Number of Master Clock |

| SP5 | SP4 | SP3 | SP2    | SP1  | -   | -  | 1200 Bauds* | 1600 Bauds | Pulses Suppressed      |

| 0   | 0   | 0   | 0      | 0    |     |    | 1.5         | 2          | 20                     |

| 0   | 0   | 0   | 0      | 1    |     |    | 3           | 4          | 40                     |

| 0   | 0   | 0   | 1      | 0    | ĺ   |    | 4.5         | 6          | 60                     |

| 0   | 0   | 0   | 1      | 1    |     |    | 6           | 8          | 80                     |

| 0   | 0   | 1   | 0      | 0    |     |    | 7.5         | 10         | 100                    |

| 0   | 0   | 1   | 0      | 1    |     |    | 9           | 12         | 120                    |

| 0   | 0   | 1   | 1      | 0    |     |    | 10.5        | 14         | 140                    |

| 0   | 0   | 1   | 1      | 1    |     |    | 12          | 16         | 160                    |

| 0   | 1   | 0   | 0      | 0    |     |    | 13.5        | 18         | 180                    |

| 0   | 1   | 0   | 0      | 1    |     |    | 15          | 20         | 200                    |

| 0   | 1   | 0   | 1      | 0    |     |    | 16.5        | 22         | 220                    |

| 0   | 1 1 | 0   | 1      | 1    |     |    | 18          | 24         | 240                    |

| 0   | 1   | 1   | 0      | 0    |     |    | 19.5        | 26         | 260                    |

| 0   | 1   | 1   | 0      | 1 1  |     |    | 21          | 28         | 280                    |

| 0   | 1   | 1   | 1      | 0    |     |    | 22.5        | 30         | 300                    |

| 0   | 1   | 1   | 1      | 1    |     |    | 24          | 32         | 320                    |

| 1   | 0   | 0   | 0      | 0    |     |    | 22.5        | 30         | 300                    |

| 1   | 0   | 0   | 0      | 1    |     |    | 45          | 60         | 600                    |

| 1   | 0   | 0   | 1      | 0    |     |    | 67.5        | 90         | 900                    |

| 1   | 0   | 0   | 1      | 1    |     |    | 90          | 120        | 1200                   |

| 1   | 0   | 1   | 0      | 0    |     |    | 112.5       | 150        | 1500                   |

| 1   | 0   | 1   | 0      | 1    | - 1 |    | 135         | 180        | 1800                   |

| 1   | 0   | 1   | 1      | 0    |     |    | 157.5       | 210        | 2100                   |

| 1   | 0   | 1   | 1      | 1    | - 1 |    | 180         | 240        | 2400                   |

| 1   | 1   | 0   | 0      | 0    | ĺ   |    | 202.5       | 270        | 2700                   |

| 1   | 1   | 0   | 0      | 1    |     |    | 225         | 300        | 3000                   |

| 1   | 1   | 0   | 1      | 0    | 1   |    | 247.5       | 330        | 3300                   |

| 1   | 1   | 0   | 1      | 1    |     |    | 270         | 360        | 3600                   |

| 1   | 1   | 1   | 0      | 0    |     |    | 292.5       |            | 3900                   |

| 1   | 1   | 1   | 0      | 1    | - 1 |    | 315         |            | 4200                   |

| 1   | 1   | 1   | 1      | 0    |     |    | 337.5       |            | 4500                   |

| 1   | 1   | 1   | 1      | 1    |     |    | 360         |            | 4800                   |

<sup>(\*) 2400</sup> bauds : multiply by two. 600 bauds : divide by two.

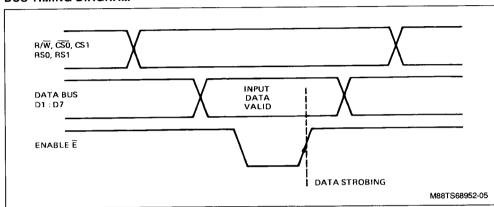

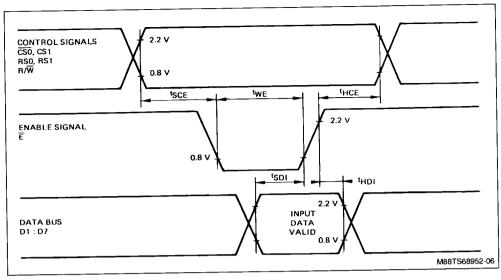

### DATA BUS CONTROL

Six signals control the access from the bus to the internal registers according to the table and the timing diagram given below. Control registers are written using an indirect addressing mode where the internal address is stored in the 3 bit ARC register. After each write operation to a control register, the ARC register value is automatically increased by one. This allows cyclical addressing of the eight registers of the MODEM chip set.

| R/W | CSO | CS1 | RS0 | RS1 | Ē | Accessed Register                        |

|-----|-----|-----|-----|-----|---|------------------------------------------|

| 0   | 0   | 1   | 1   | 0   |   | Address Register ARC                     |

| 0   | 0   | 1   | 1   | 1   |   | Control Register whose Address is in ARC |

#### BUS TIMING DIAGRAM

#### DATA FORMAT

|                    | c    | ta Loaded in AR | Da   |

|--------------------|------|-----------------|------|

| Addressed Register | D5   | D6              | D7   |

|                    | ARC1 | ARC2            | ARC3 |

| RC1                | 0    | 0               | 0    |

| RC2                | 1    | 0               | 0    |

| RC7                | 0    | 1               | 1    |

| RC8                | 1    | 1               | 1    |

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                    | Min.       | Max.    | Unit |

|----------------------------------------------|------------|---------|------|

| V <sup>+</sup> Supply Voltage to DGND Ground | - 0.3      | 7       | V    |

| Voltage at any Input or Output               | DGND - 0.3 | V + 0.3 | V    |

| Current at any Output                        | - 20       | 20      | mA   |

| Power Dissipation                            |            | 500     | mW   |

| Operating Temperature Range                  | 0          | 70      | ∞    |

| Storage Temperature Range                    | - 65       | + 150   | . ∘c |

8/17

SGS-THOMSON MICROELECTRONICS

356

# **OPERATING RANGE**

|                                 | Ambient Temperature | <br>V +       | DGND |

|---------------------------------|---------------------|---------------|------|

| 0 °C ≤ t <sub>amb</sub> ≤ 70 °C |                     | + 5.0 V ± 5 % | 0 V  |

# **ELECTRICAL OPERATING CHARACTERISTICS**

Unless otherwise noted, electrical characteristics are specified over the operating range. Typical values are given for V  $^+$  = 5.0 V and  $T_{amb}$  = 25  $^{\circ}$ C

| Symbol          | Borometer                 | Took Conditions                             |      |      |      |      |

|-----------------|---------------------------|---------------------------------------------|------|------|------|------|

| Symbol          | Parameter                 | Test Conditions                             | Min. | Тур. | Max. | Unit |

| Power           | Dissipation               |                                             |      |      | -    |      |

| 1+              | Positive Supply Current   |                                             |      |      | 5.0  | mA   |

| Digital         | Interface                 |                                             |      |      |      |      |

| V <sub>IL</sub> | Input Low Level Voltage   |                                             |      |      | 0.8  | V    |

| VIH             | Input High Level Voltage  |                                             | 2.2  |      |      | V    |

| l <sub>iL</sub> | Input Low Level Current   | DGND ≤ V <sub>I</sub> ≤ V <sub>IL max</sub> | - 10 |      | 10   | μА   |

| I <sub>IB</sub> | Input High Level Current  | $V_{IH min} \leq V_I \leq V^+$              | - 10 |      | 10   | μА   |

| Vol             | Output Low Level Current  | I <sub>O</sub> = 2.5 mA                     |      |      | 0.4  | v    |

| VoH             | Output High Level Current | I <sub>O</sub> = - 2.5 mA                   | 2.4  |      |      | V    |

| Crystal         | Oscillator Interface      |                                             |      |      |      |      |

| VIL             | Input Low Level Voltage   |                                             |      |      | 1.5  | ٧    |

| V <sub>IH</sub> | Input High Level Voltage  |                                             | 3.5  |      |      | ٧    |

| I <sub>fL</sub> | Input Low Level Curent    | DGND ≤ V <sub>I</sub> ≤ V <sub>IL max</sub> | - 15 |      |      | μА   |

| I <sub>IH</sub> | Input High Level Current  | $V_{IH min} \leq V_{I} \leq V^{+}$          |      |      | 15   | μΑ   |

## **TIMING CHARACTERISTICS**

| Symbol           | Baramata.                     | T                            |      |       |      |      |

|------------------|-------------------------------|------------------------------|------|-------|------|------|

|                  | Parameter                     | Test Conditions              | Min. | Тур.  | Max. | Unit |

| Data B           | us Access                     |                              |      |       |      |      |

| tsce             | Control Signals Set-up Time   | CS0, CS1, RS0, RS1, R/W to E | 40   |       |      | ns   |

| tHCE             | Control Signals Hold Time     | CS0, CS1, RS0, RS1, R/W to E | 10   |       |      | ns   |

| tsol             | Data-in Set-up Time           | D1 : D7 to E                 | 120  |       |      | ns   |

| t <sub>HDI</sub> | Data-in Hold Time             | D1 : D7 to E                 | 10   |       |      | ns   |

| twe              | Enable Signal Low Level Width | Ē                            |      | 180   |      | ns   |

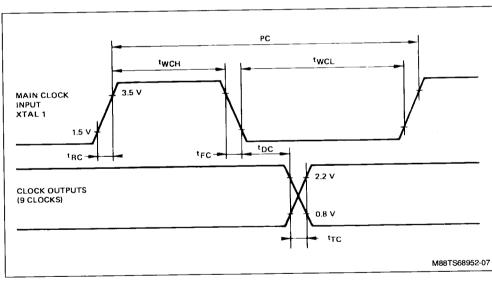

| Clock \          | Vave forms                    |                              |      |       |      |      |

| PC               | Main Clock Period             | XTAL1 Input                  | 150  | 173.6 |      | ns   |

| twcL             | Main Clock Low Level Width    | XTAL1 Input                  | 50   |       |      | ns   |

| twch             | Main Clock High Level Width   | XTAL1 Input                  | 50   |       |      | ns   |

| t <sub>RC</sub>  | Main Clock Rise Time          | XTAL1 Input                  |      |       | 50   | ns   |

| t <sub>FC</sub>  | Main Clock Fall Time          | XTAL1 Input                  |      |       | 50   | ns   |

| t <sub>DC</sub>  | Clock Output Delay Time       | All Clock Outputs CL = 50 pF |      |       | 500  | ns   |

| t⊤c              | Clock Output Transition Time  | All Clock Outputs CL = 50 pF |      |       | 100  | ns   |

10/17 SGS-THOMSON MICROELECTRODICS

358

#### **APPLICATIONS INFORMATIONS**

MODEM ANALOG FRONT-END CHIP SET (TS38950/51/52).

Notes: 1.1777 Digital ground.

Analog ground.

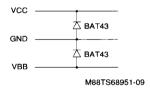

2. In some cases, external-user circuitry may induce power-up sequency latch-up problems that can be efficiently avoided using ST BAT43 schottky small signal diodes as follow:

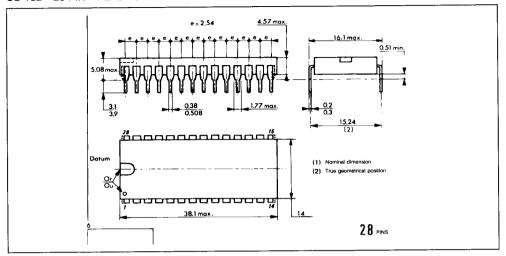

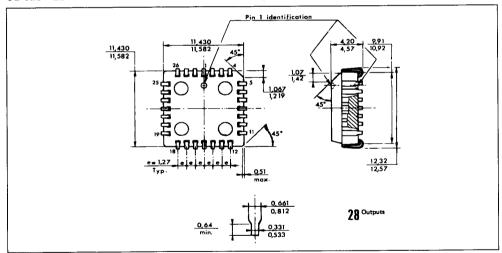

## ORDERING INFORMATION

| Part Number | Temperature<br>Range | Package |  |  |

|-------------|----------------------|---------|--|--|

| TS68952CP   | 0 to + 70 °C         | DIP28   |  |  |

| TS68952CFN  | 0 to + 70 °C         | PLCC28  |  |  |

### PACKAGE MECHANICAL DATA

CB-132 - 28 PIN - PLASTIC DIP

# CB-520 - 28 PIN - PLASTIC LEADLESS CHIP CARRIER

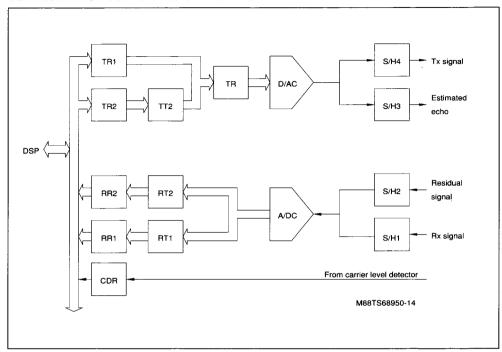

# INTERFACE BETWEEN DSP AND MODEM ANALOG FRONT-END (TS68950/51/52)

## DETAILED INPUT/OUTPUT REGISTERS DIAGRAM

|         | R/W | RS0 | RS1   | Register Accessed                 |  |  |  |

|---------|-----|-----|-------|-----------------------------------|--|--|--|

|         | 0   | 0   | 0     | TR1                               |  |  |  |

|         | l ō | l o | lil   | TR2                               |  |  |  |

| Vriting | Ō   | 1 1 | l o l | ARC                               |  |  |  |

|         | O   | 1   | 1     | Control Register Addressed by ARC |  |  |  |

|         | 1   | 0   | 0     | RR1 ·                             |  |  |  |

|         | 1 1 | 0   | 1 1   | RR2                               |  |  |  |

| eading  | 1   | 1   | 0 1   | CDR                               |  |  |  |

|         | 1 1 | 1   | 1 1   | Not Used                          |  |  |  |

# CONTROL REGISTERS PROGRAMMING

| Register<br>Name | Circuit<br>Including | Register Content |      |      |      |      |      |     |    |    | ARC Content (register address) |    |  |

|------------------|----------------------|------------------|------|------|------|------|------|-----|----|----|--------------------------------|----|--|

|                  | this Register        | <b>D</b> 7       | D6   | D5   | D4   | D3   | D2   | D1  | D0 | D7 | D6                             | D5 |  |

| RC1              | 68952                | HB4              | нвз  | HB2  | HB1  | HR3  | HR2  | HR1 | -  | 0  | 0_                             | 0_ |  |

| RC2              | 68952                | нмз              | HM2  | HM1  | HS2  | HS1  | HTHR | -   | -  | 0  | 0                              | 1  |  |

| RC3              | 68951                | HP2              | HP1  | LP2  | LP1  | REJ  | S/A  | REC | -  | 0  | 1                              | 0  |  |

| RC4              | 68950                | ATE4             | ATE3 | ATE2 | ATE1 | -    | EM2  | EM1 | -  | 0  | 1                              | 1  |  |

| RC5              | 68951                | GR5              | GR4  | GR3  | GR2  | GR1  | T -  | -   | -  | 1  | 0                              | 0  |  |

| RC6              | 68951                | GDS2             | GDS1 | HDS  | -    | -    | -    | -   | -  | 1  | 0                              | 1  |  |

| RC7              | 68952                | SP5              | SP4  | SP3  | SP2  | SP1  | -    | -   | -  | 1  | 1                              | 0  |  |

| RC8              | 68952                | MPE              | SPR  | AVRE | VAL  | INIT | -    | -   | -  | 1  | 1                              | 1_ |  |

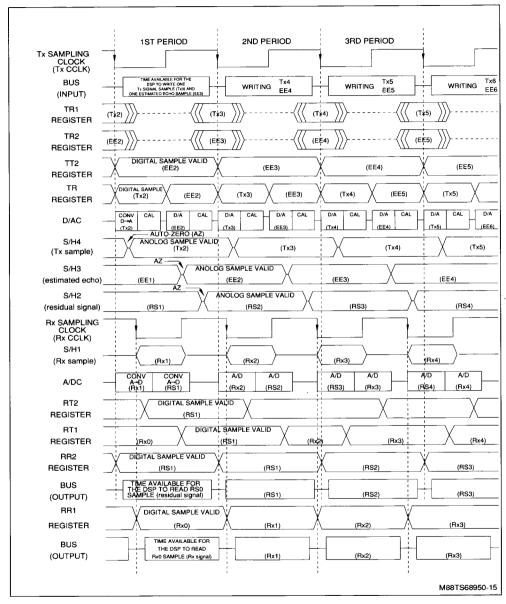

APPENDIX 4

PROGRESSION OF THE DIGITAL AND ANALOG SAMPLES IN THE MAFE

16/17

SGS-THOMSON MICROELECTRONICS

#### **FURTHER REFERENCES**

#### 1/MAFE CHARACTERIZATION REPORT

This report gives the results of the measurements performed on the TS68950-51-52 Modem Analog Front-End (MAFE) chip set.

Chapter 1 describes the configuration and the method used for these measurements.

Chapter 2 comments the results obtained on the two signal paths of the transmit (Tx) analog front-end TS68950. i.e the echo path and the Tx signal path. Similarly chapter 3 gives the results obtained on the echo path and the receive (Rx) signal path of the Rx analog front-end TS68951.

Performances obtained on the TS68951 when using plesiochronous clocks are given in chapter 4. In this case, the TS68952 clock generator delivers the main clock and the two sampling clocks to the Rx analog interface.

### 2/MAFE EVALUATION BOARD (EFRMAFE)

The MAFE evaluation board is a complete unit for evaluation of the TS68950/51/52 MAFE chip set.

The MAFE evaluation board is equipped with the TS68950/51/52 chip set and phone line interface facilities.

It can be directly connectable to an external Digital Signal Processor through a 50-pins connector or can be linked to the SGS-THOMSON family of digital signal processors emulation-evaluation tools. In this case, along with the software tools (MACROASSEMBLER, SIMULATOR and LINKER), it provides a ready-to-use Digital Signal Processor System Interface well adapted to the analog word and high speed moderns development.

# 3/APPLICATION NOTE

This application note describes the development of Real-Time Algorithms using the SGS-THOMSON Digital Signal Processor TS68930 and the MAFE chip set.