# ST18930/31

## DIGITAL SIGNAL PROCESSOR

80 ns INSTRUCTION CYCLE TIME \* (1.2 μ CMOS technology)

SGS-THOMSON MICROELECTRONICS

- PARALLEL HARVARD ARCHITECTURE

- SEPARATED PROGRAM AND DATA BUSES

- THREE DATA BUSES STRUCTURE

- DUAL EXTERNAL BUSES

- ONE CYCLE 16-BIT R/W OPERATION ON EX-TERNAL DATA MEMORY

- THREE DATA TYPES : 16-BIT REAL, 32-BIT REAL, 16 + 16-BIT COMPLEX

- HARDWARE MASKABLE INTERRUPT

- COMPLEX MULTIPLIER

- 320 x 16-BIT INTERNAL RAMs, 512 x 16-BIT IN-TERNAL COEFFICIENT ROM

- 3 K x 32-BIT WORDS OF INTERNAL PRO-GRAM ROM

- LOW POWER MODE

- REALTIME EMULATION OF ST18930 ROM VERSION WITH ST18931 ROMLESS VER-SION

#### DESCRIPTION

The ST18930/31 HCMOS digital signal processors are members of SGS-THOMSON family of general purpose DSP's fully software and hardware compatible with previous members of the family.

By virtue of their highly parallel architecture, these digital signal processors are well suited to a wide range of applications including those requiring operations on complex numbers.

Typical examples are found in telecommunications, modems, image and speech processing, high speed control, digital filtering, sonar and radar applications.

They are able to execute simultaneously within 100 ns an ALU function, a Multiplication, two Read and one Write operations with associated address calculation.

The on-chip large memory resources and multiprocessor direct interface allows the development at the lowest cost/complexity of high performance applications. The ST18931 is the ROMless version of the ST18930. In addition of the ST18930 features, it provides the capability of addressing

December 1988

\* Also available 100 and 160 ns cycle time versions.

up to 64Kx32-bit external instruction memory and allows a total realtime emulation of the ST18930. It is also particularly well adapted for applications where large program memory is required or for low quantities.

#### **DEVELOPMENT SYSTEMS**

The ST18930 is supported by a complete set of hardware and software tools for applications development. Software packages include assembler, linker and simulator on VAX and PC as well as a high level "C" compiler and optimizer.

Hardware tools include a stand-alone emulator, eprom emulation module and a powerful multiprocessor development station.

| TABLE OF CONTENTS | т | A | в | LE | OF | C | ٥N | ١T | E١ | Ν | TS |

|-------------------|---|---|---|----|----|---|----|----|----|---|----|

|-------------------|---|---|---|----|----|---|----|----|----|---|----|

| 1. | BLOCK DIAGRAM                      | Page<br>5 |

|----|------------------------------------|-----------|

| 2. | PIN DESCRIPTION                    | 6         |

| 3. | FUNCTIONAL DESCRIPTION             | 8         |

|    | 3.1 General architecture concept   | 8         |

|    | 3.2 Operating unit                 | 9         |

|    | 3.3 Data memories                  | 12        |

|    | 3.4 Sequencer block                | 13        |

|    | 3.5 Inputs / Outputs               | 15        |

|    | 3.6 Other resources                | 23        |

| 4. | TYPICAL APPLICATION CONFIGURATIONS | 25        |

| 5. | INSTRUCTION SET                    | 29        |

| 6. | ELECTRICAL SPECIFICATIONS          | 42        |

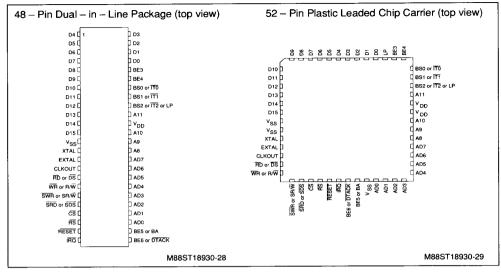

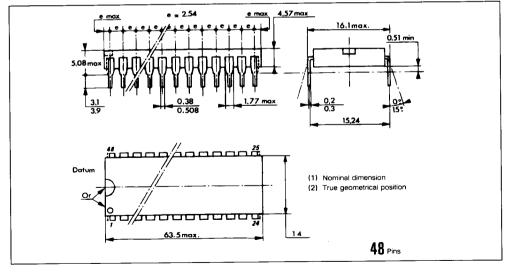

| 7. | PIN CONNECTIONS                    | 57        |

| 8. | ORDER CODES                        | 58        |

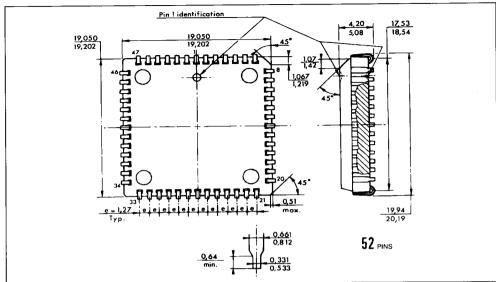

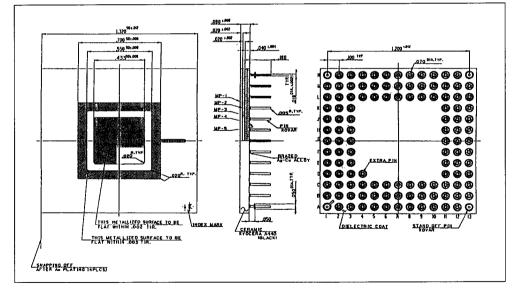

| 9. | PACKAGE MECHANICAL DATA            | 58        |

|    | TABLE OF APPENDICES                |           |

| Α. | BENCHMARKS                         | 60        |

| в. | DEVELOPMENT PROCESS                | 61        |

| C. | MASKING INFORMATION                | 62        |

| D. | SUMMARY OF RESOURCES/FUNCTION      | 64        |

2/66 554

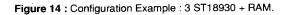

Page Figure 1 : Pin description. 6 10 Figure 2 : ALU block diagram. Figure 3 : Multiplier efficiency. 10 13 Figure 4 : Data memory blocks. 15 Figure 5 : Interrupt inputs and conditions. Figure 6 : Dual bus interface - system configuration. 16 Figure 7 : Local bus description. 17 17 Figure 8 : Separate local buses. 18 Figure 9 : System bus description. 19 Figure 10 : Mailbox connection. 20 Figure 11.A : Mailbox exchange - example 1. Figure 11.B : Mailbox exchange - example 2. 21 Figure 12 : Reset timing. 24 Figure 13 : Configuration example ST18930 + RAM + MAFE. 25 26 Figure 14 : Configuration example ST18930 + RAM. Figure 15 : Configuration example ST18930 + RAM + MAFE. 27 28 Figure 16 : Interfacing CROM, IRAM to ST18931. 31 Figure 17 : OPIN calculation instruction with indirect addressing. 32 Figure 18 : OPDI calculation instruction with direct addressing. 33 Figure 19 : OPIM calculation instruction with immediate operand. Figure 20 : ASR, LSL, LSR, ROR shift instructions. 34 35 Figure 21 : BRI immediate branch instructions. Figure 22 : BRC computed branch instructions. 36

TABLE OF FIGURES

#### SGS-THOMSON MICROELECTRONICS

|                                                                                                 | Page   |

|-------------------------------------------------------------------------------------------------|--------|

| Figure 23 : SVR data transfer instructions.                                                     | 37     |

| Figure 24 : INI initialization and control instruction.                                         | 38     |

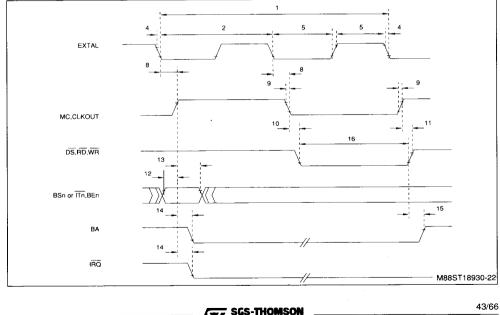

| Figure 25 : Clock and control pins timing for Extal + 2 mode (80 and 100 ns cycle time).        | 42     |

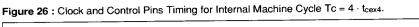

| Figure 26 : Clock and control pins timing for Extal + 4 mode (160 ns a TS68930/31 compability). | and 43 |

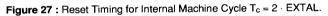

| Figure 27 : Reset timing for internal machine cycle $T_C = 2 \cdot EXTAL$ .                     | 43     |

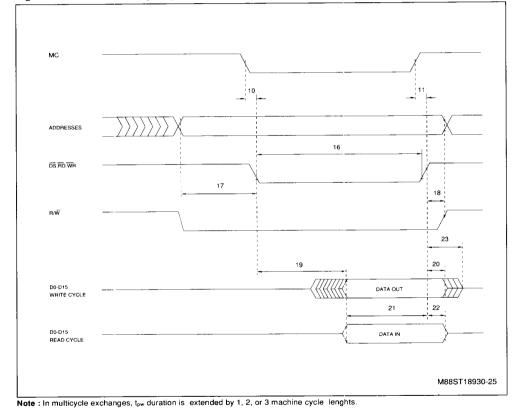

| Figure 28 : Local bus timing diagram.                                                           | 45     |

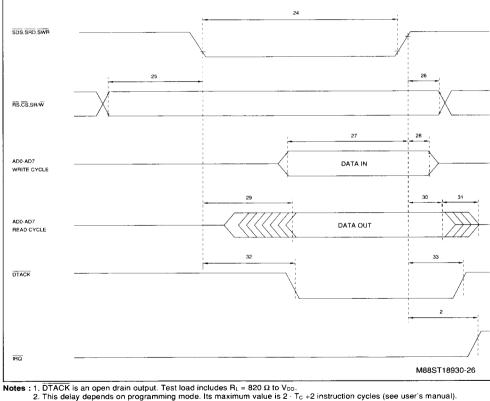

| Figure 29 : System bus timing diagram for transfer of one byte.                                 | 46     |

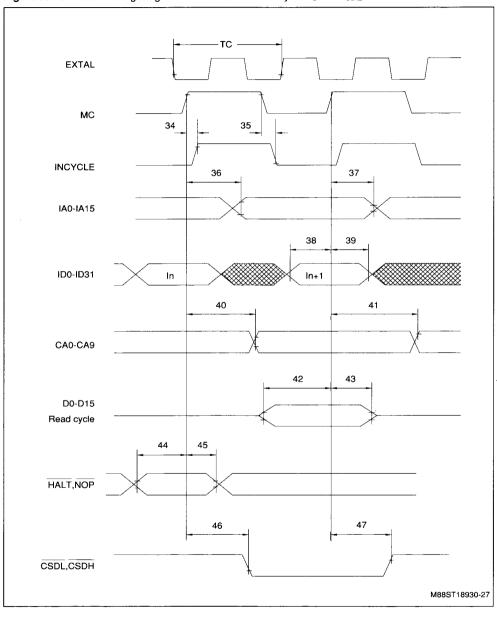

| Figure 30 : Instruction interface timing diagram (ST18931 only).                                | 48     |

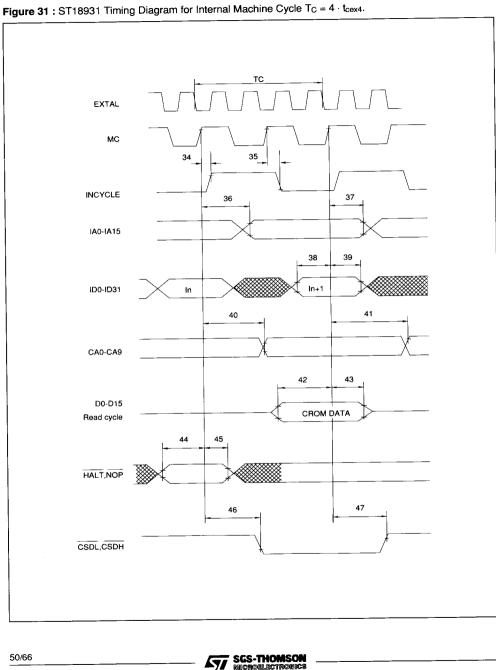

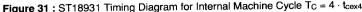

| Figure 31 : Timing diagram for internal machine cycle $T_C = 4 \times t_{cex}$ (ST18931 only).  | 49     |

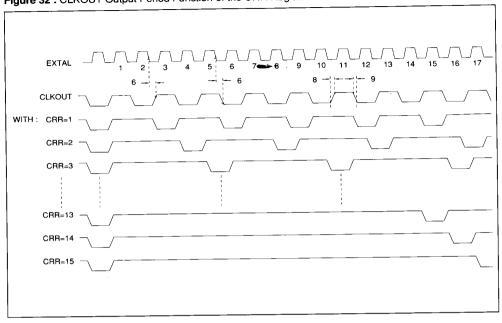

| Figure 32 ; CLKOUT output period.                                                               | 50     |

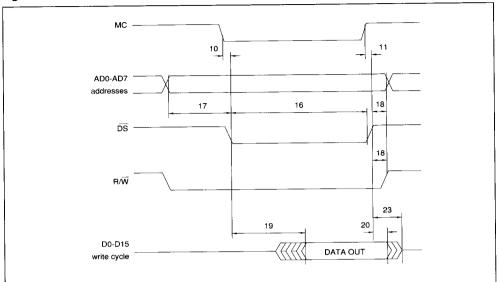

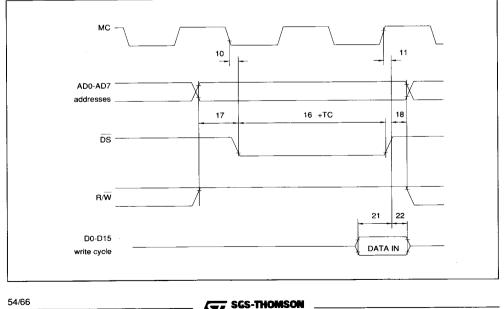

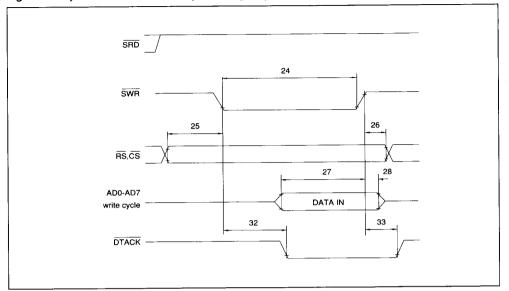

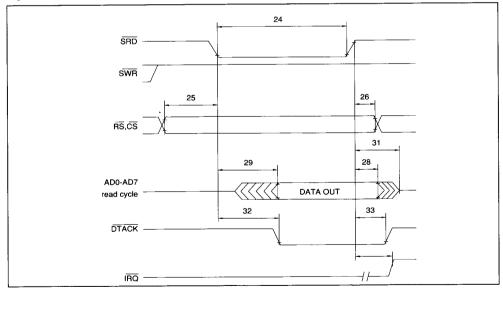

| Figure 33 : Local bus "Motorola" write cycle timing diagram.                                    | 51     |

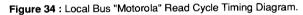

| Figure 34 : Local bus "Motorola" read cycle timing diagram.                                     | 51     |

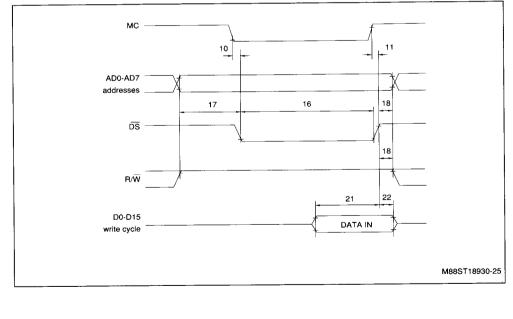

| Figure 35 : Local bus "Intel" write cycle timing diagram.                                       | 52     |

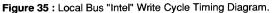

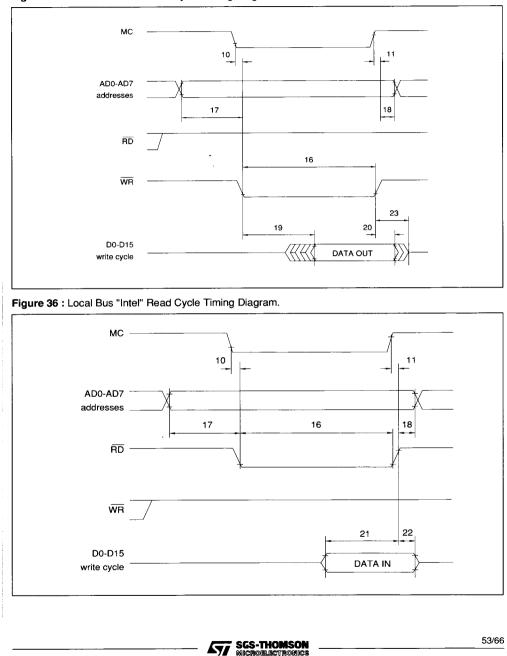

| Figure 36 : Local bus "Intel" read cycle timing diagram.                                        | 52     |

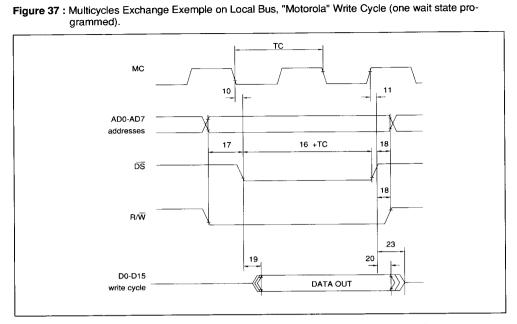

| Figure 37 : Multicycles exchange exemple on local bus,<br>"Motorola" write cycle.               | 53     |

| Figure 38 : Multicycles exchange exemple on local bus<br>"Motorola" read cycle.                 | 53     |

| Figure 39 : System bus, "Motorola" write cycle timing diagram.                                  | 54     |

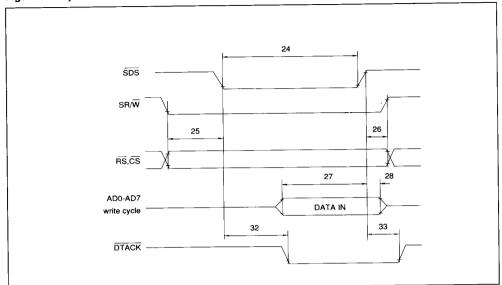

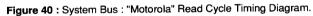

| Figure 40 : System bus, "Motorola" read cycle timing diagram.                                   | 54     |

| Figure 41 : System bus, "Intel" write cycle timing diagram.                                     | 55     |

| Figure 42 : System bus, "Intel" read cycle timing diagram.                                      | 55     |

|                                                                                                 |        |

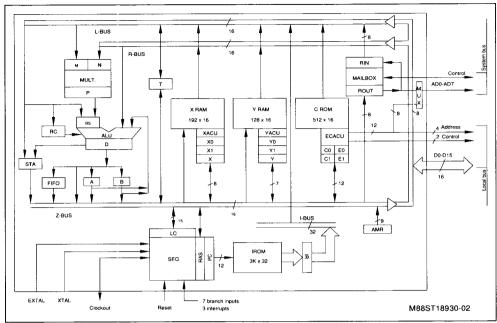

## 1. BLOCK DIAGRAM (ST18930)

**DEFINITION OF ACRONYMS**

| L-bus  | : Left data bus              | CROM      | : Coefficient ROM                      |

|--------|------------------------------|-----------|----------------------------------------|

| R-bus  | : Right data bus             | X0, X1, X | K : Addressing registers XRAM          |

| М      | : Multiplier input register  | Y0, Y1, Y | Y : Addressing registers YRAM          |

| N      | : Multiplier input register  | C0, C1    | : Addressing registers CROM            |

| Р      | : Multiplier output register | E0, E1    | : Addressing registers ERAM            |

| BS     | : Barrel Shifter             | XACU      | : Address calculation unit XRAM        |

| ALU    | : Arithmetic and Logic Unit  | YACU      | : Address calculation unit YRAM        |

| D      | : ALU output register        | ECACU     | : Address calculation unit CROM & ERAM |

| RC     | : Replace Code register      | RIN       | : Input register of mailbox            |

| STA    | : Status register            | ROUT      | : Output register of mailbox           |

| FIFO   | : ALU output FIFO            | AMR       | : Access mode register                 |

| Α      | : ALU accumulator            | IR        | : Instruction register                 |

| в      | : ALU accumulator            | PC        | : Program counter                      |

| Z- bus | : Result data bus            | RAS       | : Return address stack                 |

| т      | : Transfer register          | SEQ       | : Sequencer                            |

| XRAM   | : X Data RAM                 | LC        | : Loop Counter                         |

| YRAM   | : Y Data RAM                 | IROM      | : Instruction ROM                      |

|        |                              |           |                                        |

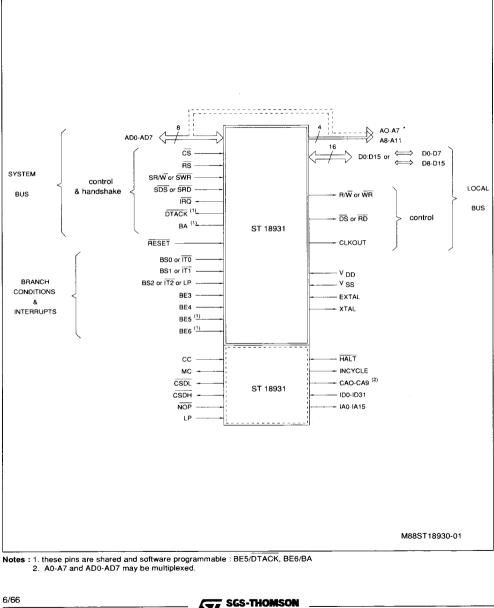

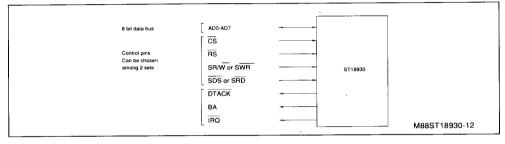

#### 2. PIN DESCRIPTION

Figure 1 : Input/Output Pins.

558

This Material Copyrighted By Its Respective Manufacturer

LECTRONICS

## LOCAL INTERFACE

| Name      | Pin<br>Type | Function         | Description                                           |  |

|-----------|-------------|------------------|-------------------------------------------------------|--|

| D0-D15    | I/O         | Data Bus         | Can be concatenated or separate D (0:7), D (8:15).    |  |

| A8-A11    | 0           | Address Bus      | High order addresses for local interface (RAM).       |  |

| DS or RD  | 0           | Data Strobe/Read | ad Synchronizes the transfer on local bus/read cycle. |  |

| R/W or WR | 0           | Read/write/Write | Indicates the current bus cycle state/write cycle.    |  |

| CLKOUT    | 0           | Clock Output     | Frequency programmable from EXTAL + 2 to EXTAL + 16.  |  |

| A0-A7     | I/O         | Address Bus      | Low order addresses for local interface (RAM).        |  |

## SYSTEM INTERFACE

| Name                  | Pin<br>Type | Function                     | Description                                                                     |

|-----------------------|-------------|------------------------------|---------------------------------------------------------------------------------|

| AD0-AD7               | 1/0         | System Data Bus              | System data bus for exchanges between the processor and a host via the mailbox. |

| cs                    | I           | Chip Select                  | Used by a host to gain access to the mailbox and system bus.                    |

| RS                    | 1           | Register Select              | Used by a host to gain access to the mailbox and system bus.                    |

| SD <u>S</u><br>or SRD | 1           | Data Strobe/read             | Synchronizes the transfer on the system bus/read cycle.                         |

| SR/W<br>or SWR        | I           | Read/write/Write             | Indicates the current system bus cycle state/write cycle.                       |

| DTACK                 | 0           | Data Transfer<br>Acknowledge | Indicates that the processor has recognized the access data transfer.           |

| BA                    | 0           | Bus Available                | Indicates the availability of the sytem bus to the host.                        |

| IRQ                   | 0           | Interrupt Request            | Handshake signal sent to the host to gain access to the mailbox.                |

## EXTERNAL BRANCH CONDITIONS AND INTERRUPT

| Name                          | Pin<br>Type | Function                     | Description                                                                                 |

|-------------------------------|-------------|------------------------------|---------------------------------------------------------------------------------------------|

| BS <u>0-BS2</u><br>or IT0-IT2 | 1           | Branch on State<br>Interrupt | External Branch Conditions.<br>(low power mode through BS2 see 3, 6, 4) Interrup Input Pins |

| BE3-BE6*                      | 1           | Branch on Edge               | External conditions. Falling edge is memorised and reset when tested.                       |

\* BE5 shares pin with BA BE6 shares pin with DTACK

OTHER PINS

| Name  | Pin<br>Type | Function     | Description                                                                   |

|-------|-------------|--------------|-------------------------------------------------------------------------------|

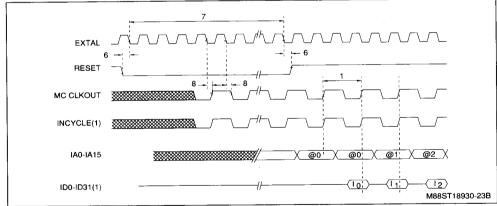

| EXTAL | 1           | Clock        | Are used for crystal oscillator ; if crystal oscillator is not used, pin XTAL |

| XTAL  | 0           | Clock        | is not connected.                                                             |

| VDD   | 1           | Power Supply |                                                                               |

| VSS   | 1           | Ground       |                                                                               |

| RESET | 1           | Reset        |                                                                               |

| LP    | 1           | Low Power    | Active at high state. Freezes the circuit operation.                          |

| Name         | Pin<br>Type | Function                                        | Description                                                                                                               |  |

|--------------|-------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|

| ID0-ID31     | I           | Instruction Data                                | Instruction Data Bus                                                                                                      |  |

| IA0-IA15     | 0           | Instruction Address                             | Instruction Address Bus                                                                                                   |  |

| CA0-CA9      | 0           | Coef. ROM Address<br>or External RAM<br>Address | External coefficient ROM address 10 bit or External RAM address<br>(9-bit address – output enable signal) (8-bit address) |  |

| HALT         | I           | Halt Signal                                     | Halts the processor. This signal freezes the program and loop counters                                                    |  |

| INCYCLE      | 0           | Instruction<br>Cycle Clock                      | A transition from low to high indicates that a new instruction is processed                                               |  |

| NOP          | I           | Hardware NOP                                    | Force NOP instruction for development system.                                                                             |  |

| CSDL<br>CSDH | 0           | Bus Low Z Control                               | $\rm D0-\rm D7$ (CSDL) and $\rm D8-\rm D15$ (CSDH) are data valid control pins for external buffers                       |  |

| CC           | I           | Clock Cycle Control                             | Machine cycle = 2 $T_c$ (EXTAL) or 4 $T_c$ (EXTAL)                                                                        |  |

| MC           | 0           | Master clock                                    | EXTAL + 2 Output                                                                                                          |  |

#### 3. FUNCTIONAL DESCRIPTION

3.1. GENERAL ARCHITECTURE

The ST18930/31 architecture is based upon the innovative architectural concepts already proven in the previous members of SGS-THOMSON digital signal processors family.

Therefore, the compatibility is kept at object code level with the TS68930/31.

The ST18930/31 confirm the efficiency of a highly parallel and pipelined operation using a true Harvard memory space and bus structure. This efficiency is there improved by the advanced 1.2  $\mu$  HCMOS technology providing 80 ns instruction cycle.

The block diagram shows four main blocks :

. The sequencer block

. The operating unit (ALU, Multiplier and Barrel Shifter)

. The data memories

. The inputs/outputs

These four blocks can be considered as four independent units working in parallel and communicating through a network of 16/32 - bit buses.

By taking advantage of the 32 - bit wide instruction bus, the ST18930/31 are able to execute simultaneously the following operations during each 80 ns machine cycle :

. Read two operands from internal or external memory . Execute a multiplication

. Perform an ALU operation

- . Write a result into internal or external memory

- . Post modify three pointers independently

- . Store data into the transfer register

In addition, data exchanges through mailbox occur concurrently and independently of internal operations.

All instructions are executed in a single cycle time except branch instructions.

Some additional features give the ST18930/31 extremely powerful performances. They provide three operating modes (real, complex and double precision) dynamically set by software and user transparent.

In complex mode, the hardware multiplier provides (16 + 16 - bit) results from 2 x (16 + 16 - bit) inputs each machine cycle.

(25 - million multiplications per second).

The ALU, reinforced by a barrel shifter, provides 30 basic arithmetic and logic functions.

Three dedicated calculation units control the four data memory spaces.

A large 3Kx32 (96Kbits) program ROM (for the ST18930) enlarge the usual digital signal processor applications possibilities, using the efficiency of the

code and architecture. The following sections will detail all the hardware blocks of the ST18930/31 and demonstrate its software performances provided by the high level of parallelism in the operations.

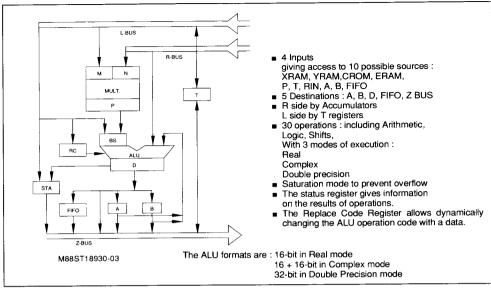

#### 3.2. OPERATING UNIT

One of the most useful features of the ST18930/31 is to provide the user three operating modes which can be dynamically set by software.

These three modes are :

. REAL 16 - bit

. COMPLEX 16 - bit real + 16 - bit imaginary

. DOUBLE PRECISION 32 - bit

Thus, the DSP is seen by the user as a standard 16 - bit real or complex machine or a 32 - bit real machine. All operating units and working registers are automatically adjusted by the processor to the right length. In real mode, all instructions are executed in a single machine cycle. In complex and double precision mode, the instruction time is doubled.

In all modes, the number representation used is signed 2's complement.

**3.2.1. 16/32 - Bit ALU/Accumulator** (fig. 2). The ALU can be seen either as a 16 or 32 - bit ALU. The ALU is loaded on the right side by the R - bus or by the A or B accumulators.

On the left side, the operands always access the ALU through the barrel shifter, coming either for the L (left) - bus or the hardware multiplier output register P.

The result of an ALU operation is automatically written in the D register and, if required into the Accumulator or FIFO. The ALU provides a range of 30 codes for operations which execute in a single machine cycle. They include arithmetic and logic operations, shift and rotate operations. The high degree of parallelism of the ST18930/31 processor allows more combinations than previous generation DSP devices which require a more complex instruction set.

The complete list of ALU codes and description is given in 3.8.2.

**3.2.2. Barrel Shifter.** The 16 - bit barrel shifter located on the left side of the ALU performs all logic/arithmetic shifts and rotations. It is used for normalization and formatting of data in floating point operations and bit or byte manipulations. Two types of operations are allowed in the barrel shifter.

- Operations defined by ALU codes (shifts of 1 or 8 bits) see 3.8.2

- Operations defined by specific dedicated instructions :

ASR  $(0 \rightarrow 15)$  arithmetic shift right by N  $(0 < N \le 15)$

LSR  $(0 \rightarrow 15)$  logical shift right by N  $(0 < N \le 15)$

LSL  $(0 \rightarrow 15)$  logical shift left by N  $(0 \le N \le 15)$

ROR (0  $\rightarrow$  15) rotation right by N (0 < N  $\leq$  15)

In complex mode, the barrel shifter performs the same operations on complex and imaginary part.

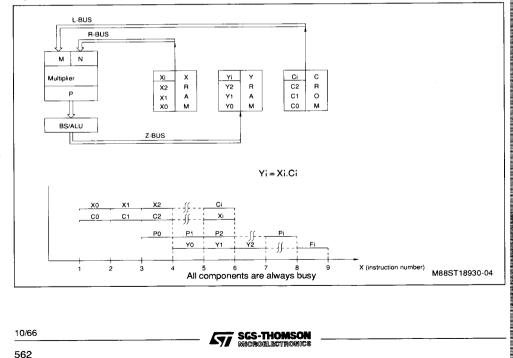

**3.2.3. Multiplier.** The multiplier executes a 16 x 16bit multiplication with a 32-bit result at each machine cycle. The operands are loaded into the M and N registers and the result of a previous multiplication is written in the P register during the same cycle.

The pipeline structure makes the multiplication result available with a delay of two instruction cycles.

The multiplier provides a multiplier overflow flag OVFM which is memorized in the status register in complex mode only (see 3.2.4).

The efficiency of the parallel pipeline operation of the multiplier is shown in fig. 3.

## Figure 2 : Alu Block Diagram.

#### Figure 3 : Multiplier Efficiency.

#### 3.2.4. Associated registers.

Registers A, B.

A and B store the results from the ALU. They are sized according to the mode of operation. They also provide capability to feedback the ALU for a new operation with the ALU result of a previous operation.

Register FIFO.

The 4 x 16-bit FIFO is used for intermediate storages. Initialization of the FIFO (empty FIFO) can be made by an INI instruction.

A result loaded in FIFO at instruction N is available at least at instruction N+2 in real mode and N+1 in complex and double precision modes.

Register RC (Replace Code register).

This register can dynamically load an ALU code to be executed by the processor from the data memories.

This register is 6-bit wide and is loaded by the  $6\,MSB$  of L-bus :

Bit 1 to 5 contain the executable ALU code corresponding to the bits I21-I17. Bit 0 allows the choice of ALU output destination (A or B register).

Its contents is defined by three ALU codes : (see 5.2.)

| ALU<br>Code | Function                                                     |  |  |

|-------------|--------------------------------------------------------------|--|--|

| RCR         | Load ALU control code in register RC                         |  |  |

| RCE         | Execute ALU code contained in register RC                    |  |  |

| RCER        | Execute ALU code contained in RC and load new ALU code in RC |  |  |

Status register (STA).

This register provides a status of the ALU, operating and addressing modes, and multiplier. It is divided into two sub-registers :

CCR (Condition Code Register) STR (State Register)

A detailed description of this register is given in  $\delta$  5.4.

Transfer register T.

The transfer register provides a direct transfer capability between L-bus and Z-bus.

It can either be source or destination for the two buses.

Its various uses include :

- \* Loop back to the multiplier in one cycle

- \* Temporary register between memory and ALU

- \* Temporary register between memory and multiplier

- \* Operation between two accumulators in the same instruction

- \* Memory to memory transfer

- \* Saving program counter (in a branch instruction)

The status register content can be saved using instruction SVR.

The condition code register CCR can be read in OPIN instruction and it can be loaded via L-bus (ALU code LCCR).

The state register STR can be programmed by an INI instruction or an SVR instruction (except EF bit).

Register D.

This is an intermediate register which is loaded with ALU result at each machine cycle.

3.3. DATA MEMORY BLOCKS.

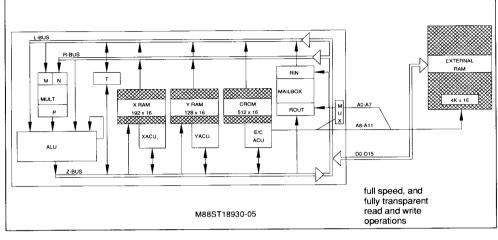

**3.3.1. Available spaces.** The ST18930/31 provides four separated memory spaces (see fig. 4)

. two internal RAMs of respectively 192 x 16-bit (XRAM) and 128 x 16-bit (YRAM)

. one internal data ROM (independent from the program ROM) of 512 x 16-bit (CROM) (ST18930 only)

. one optional external memory (ERAM) of 4 K x 16-bit accessible in 1 single instruction cycle in exactly the same way as internal memories.

This external memory is controlled by an Intel or Motorola type control interface and offers full speed, fully transparent, Read and Write operations.

However slower external memories or peripherals can be accessed by using slow exchanges mode.

The powerful instruction set and the Harvard architecture allows many combinations of simultaneous memory accesses. The only forbidden situations are :

- read and write access is the same RAM within the same instruction

- simultaneous access to CROM and ERAM

**3.3.2. Address Calculation Units.** Three different Addresses Calculation Units are available.

XACU is associated with XRAM

YACU is associated with YRAM

ECACU is associated with the ERAM and the CROM

**3.3.3. Addressing modes.** The ST18930/31 provides four addressing modes :

- Direct addressing

- \_ Immediate operand

- Indirect addressing with or without post modification of the pointers

- Circular addressing (also called virtual shift mode) for XACU and YACU.

The circular addressing mode is of particular interest in digital signal processing typical operations like convolution algorithms used in FIR filters. It has the same function as a shift register but does not move the data stored.

For this feature, three pointers are used in the memory space chosen (X or Y). The current address is given by a specific X pointer shifting repetitively between two limits X0 and X1 (respectively Y, Y0 and Y1).

The circular mode is declared in the status register STA (see 3.2.4) by an INI instruction.

**3.3.4. Pointers.** The ST18930/31 offers a large number of address pointers for each memory space

- \_ X0, X1 and X for XRAM

- \_ Y0, Y1 and Y for YRAM

- C0, C1 for CROM

- E0, E1 for ERAM

The pointers Xi, Yi, Ci and Ei can be independently incremented, decremented or maintained. The two pointers X and Y are specific to the circular addressing mode. The pointers can be loaded with new addresses (constant or computed values) through Z-bus. In this case, the value of unused Z-bus MSBs are irrelevant. The unused bits are set to 1.

**3.3.5 Odd/Even addresses.** In complex and double precision modes, the processor automatically generates the two addresses necessary to store

one data word (even first, then odd addresses).

The user can reverse this order by setting to 1 the ADOF bit with the INI instruction (refer to OPCODE). This feature is available independently for XRAM and YRAM.

|              | COMPLEX WORD   | DOUBLE PR. WORD |

|--------------|----------------|-----------------|

| Even Address | Real Part      | Lower Part      |

| Odd Address  | Imaginary Part | Upper Part      |

#### Figure 4 : Data Memory Blocks.

#### 3.4. SEQUENCER BLOCKS

**3.4.1. Sequencer.** The purpose of the sequencer is to generate the next instruction address.

The sequencer takes into account the current operating mode of the ST18930/31 to execute this task. The instruction is executed in one cycle time in real mode and two cycles time in complex or double precision mode.

The linear address program generation may be interrupted by several means hereunder described.

- A. Execution of a branch instruction

- unconditional branch always.

- seven ALU conditions flagged from the status register :

- SR Sign real

- SI Sign Imaginary

- CR Carry Real

- CI Carry Imaginary

- Z Zero

- OVF Overflow

MOVF Memorized overflow MOVF is reset when tested by branch instruction.

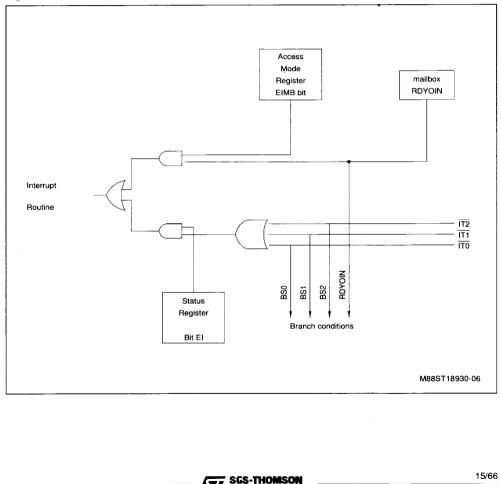

- three external conditions on state of pins BS0, BS1, BS2 (the pins BS0, BS1, BS2 can also be used as interrupt pins if enable interrupt is programmed).

- four edge sensitive external conditions on pins BE3, BE4, BE5, BE6. The falling edges of BE3-BE6 are memorized internally and reset when tested by the branch instruction. The external test conditions are used to synchronize different processes.

- The mailbox flag RDYOIN indicating mailbox availability.

All the branch conditions can be tested on true or false conditions.

#### ST18930/31

- B. Subroutine call

- C. Loop execution

One of the most powerful features of the ST18930/31 is its ability to repeat the execution of several instructions with very straightforward commands. The loop execution is set with the instructions : REPEAT, BEGIN, END which respectively define the number of loops, the beginning of loop and its end. The DSP will then manage all the necessary pointers to execute the loop with no overhead time (see 3.4.4.).

D. Execution of an interrupt routine

When the Enable Interrupt bit (EI) of the status register (STA) is set, a low level on any of IT0, IT1 and IT2 inputs forces the PC content at \$ 0001. Mailbox interrupts can be enabled separately from IT inputs interrupt; it occurs when a mailbox exchange has been completed (see & 3.5.6). During interrupt routines execution, the program counter is saved in the Return Address Stack (RAS).

**3.4.2. Instruction ROM.** The ST18930 instruction ROM has a capacity of 3072 words of 32-bit available for the user. The ROM code is defined following the user's information (see appendix C for masking information). The ST18931 does not provide an on-chip ROM memory, but can address an external 64 K program memory space in a single cycle.

**3.4.3. Program Counter.** The program counter is a 16-bit wide Register ; 12 bits are used in the ST18930 (ROM version).

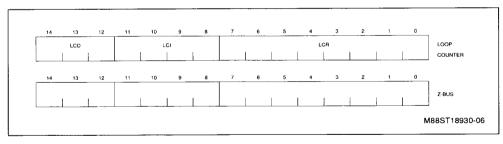

3.4.4. Loop Counter. The loop counter does considerably increase the efficiency of the processor in repeated calculations, very commonly used in digital signal processing.

Three counters define a hardware loop :

- LCI Instruction Loop Counter (4-bit). Counts the number of instructions to be executed in the loop.

- LCR Repeat Loop Counter (8-bit). Gives the number of times the loop will be repeated (can be loaded by a calculated value).

- LCD Delay Loop Counter (3-bit). Gives the delay between the declaration and the start of a loop.

The loop counter content can be saved (SVR instruction) with the format shown in table below :

The loop counter is set by the three pseudo-instructions Begin, Repeat and End in the Macroassembler.

The loop counter is frozen during an interrupt routine.

On the ST18931, a HALT freezes the state of the loop counter. A RESET signal resets the loop counter.

**3.4.5. Return Address Stack.** The JSR instruction allows one level of subroutine nesting with automatic saving of the PC on to the Return Address Stack. Multiple Level of subroutine nesting can be implemented in RAM using either of the two pointers as stack pointer.

567

#### 3.5. INPUTS/OUTPUTS

A very important feature of a signal processor is its ability to be inserted in a complete system including memories, other processes, analog interface circuits.

Basically, the external world seen by a ST18930/31 can be divided in two main sections : communications with its own local resources (peripheral, memories, converters) and communications with control processor, either microcontroller or master DSP in a multiprocessor application.

To communicate with its local resources, the ST18930/31 uses its local bus.

Figure 5 : Interrupt Inputs and Conditions.

To interface with a host, the ST18930/31 uses its system bus and interrupt/branch capabilities.

However, the local and system bus configuration is flexible and allows many combinations for the architecture of a system based around a ST18930/31.

**3.5.1. Interrupt branches.** Several sources of interrupt and branch conditions are accepted by the ST18930/31. Depending on the initialization (INI) the ST18930/31 can accept interrupts from pins, ITO, IT1, IT2. It can also and independently accept software interrupts transmitted through the mailbox.

The various sources/conditions of interrupts are summarized in fig. 5 :

**3.5.2. Dual bus interface.** In order to provide the maximum flexibility, the ST18930/31 provides two buses. One is called the system bus and is found on pins AD0-AD7, the other one called local bus is situated on pins D0-D15. The system bus provides a very straightforward interface to a host controller, while the local bus allows the ST18930/31 to make an efficient use of external resources such as memories, analog interface circuits etc... This dual bus structure allows many combinations of circuits where the ST18930/31 can act in different ways :

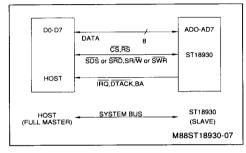

Fig. 6A as a microprocessor peripheral

#### Figure 6 A : HOST/ST18930.

#### Figure 6 C : HOST/ST18930/RAM.

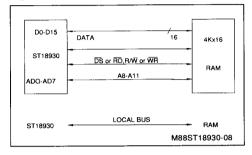

Fig. 6B as a processor with its associated memory

Fig. 6C as an intelligent peripheral having its own external memory and connected to a microprocessor.

It must be emphasized that, in most configurations, the connections are absolutely direct and do not use any external additional logic.

Furthermore, thanks to the dual bus structure, several ST18930/31 can be very simply combined together in multiprocessor applications, thereby directly increasing the processing power.

#### Figure 6 B : ST18930/RAM.

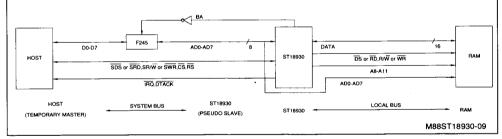

**3.5.3. Host/slave configuration.** The processor acts as a host on its local bus and as a slave on its system bus.

In configurations in which the ST18930 accesses external RAMS on its local bus, pins AD0-AD7 can be used to provide 8 LSB addresses, while A8-A11 provides 4 MSB addresses to the RAM.

In this case, the ST18930/31 prevents the host from using the system bus and is then called a pseudo-slave.

Since the host can only temporarily access the system bus it is defined as a temporary master. That mode of operation is software controlled through the Access Mode Register (AMR) (see 3.5.7.).

On the ST18931 the pins CA0-CA7, which present the least significant bits of external ERAM/CROM addresses can be connected to that RAM in place of system bus pins AD0-AD7.

3.5.4. Local bus. The local bus uses two software programmable signals to control the data on D0-D15.

DS : Data Strobe. Synchronizes the transfer on local bus.

B/W · Bead/Write. Indicates the direction of the data.

These signals are used for Motorola-like bus compatibility.

Figure 7 : Local Bus Pin Description.

- D0-D7 16 hit data bus can be concatenated or separate - D8-D15 4 address hits A8-A11 ST18930 - R/W or WR Control bits. Can be chosen among 2 sets - DS or BD Additional adress bits (in pseudo-slave mode) M88ST18930-10

The four address bits of the local bus are usually sufficient to address peripherals. When an access to external RAM is necessary with the ST18930/31. the address bus can then be extended by using the AD0-AD7 pins of the system bus as address lines.

If an external peripheral or external memories are too slow to answer in one machine cvcle. the ST18930/31 can be programmed to execute an external access in several cycles (2, 3 or 4) using the bits ES0 and ES1 of Access Mode Register (see 3.5.7.).

This mode is particularly useful for peripherals such

PSEUDO

SI AVE

TO OTHER SLAVES D8-D15 A11 A10  $D_0 - D_7$  $D_8 - D_{15}$ ST18930 MASTER Selection High Impedance 0 0 ADD-AD7 ٥ 1 High Impedance Selection D0-D7 Selection 1 0 High Impedance ST18930

RAM

DATA

1

1

M88ST18930-11

High Impedance

Selection

Figure 8 : Separate Local Buses.

RD : Read, Read clock pulse.

WR : Write, Write clock pulse.

These signals are used for Intel-like bus compatibilitv.

A8-A11 : Address bits (4)

AD0-AD7 : Optional additional address bits (8)

as data converters, or dedicated interface like the MAFE chip set (Modem Analog Front End) from SGS-THOMSON.

The local data bus can also be splitted into two independent 8-bit buses. This is used in a multiprocessor architecture when a pseudo-slave uses the system bus to transfer its own RAM addresses on D0-D7 (fig. 8). By dividing its local bus, the temporary master can remain a full-master on bus D8-D15 and does not require a bus transceiver on D0-D7. The selection between the two buses is then made by the addresses A10-A11 as indicated in Fig. 8.

**3.5.5. System Bus**: The system bus uses two software programmable signals to control the data on AD0-AD7.

The system bus mode of operation (Intel or Motorola) is set by asserting the SIM Flag using an INI instruction). SR/ $\overline{W}$  and  $\overline{SDS}$  signals are used for Motorola-like bus compatibility.

SWR and SRD signals are used for Intel-like compatibility.

| CS/RS                     | Mailbox control signal. Also used by a host to gain access to the bus.                                                                               |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| SR/W or SWR<br>SDS or SRD | System Read/Write ) Generated by an external processor (host)<br>System Data Strobe )                                                                |

| IRQ                       | Handshake Signal (see 3.5.6)                                                                                                                         |

| DTACK                     | Data Transfer Acknowledge. Compatibility with 68000 family. Is programmed by Access<br>Mode Register.                                                |

| BA                        | Bus Available. The ST18930/31 is not currently using the system data bus to generate addresses. BA is also programmable by the Access Mode Register. |

Figure 9 : System Bus Description.

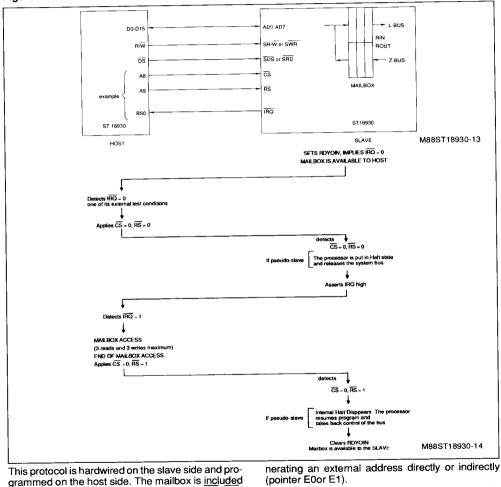

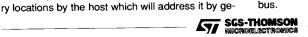

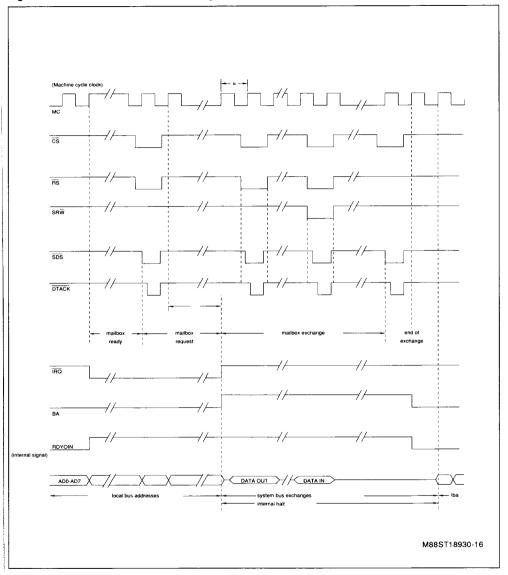

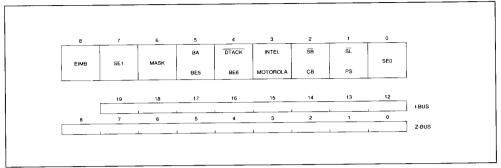

**3.5.6. Mailbox.** The mailbox is a set of registers which interface with the system data bus. The mailbox is divided in two parts :

- RIN (3 x 8 bit register) : This register is read internally by the ST18930/31 on the upper byte of Lbus (L8-L15) and written externally from the system bus. After each write or read operation the data is shifted by one byte.

- ROUT (3 x 8 bit register): This register is written internally with the upper byte of the Z-bus (Z8-Z15) and read externally on the system bus. After each operation (read or write), the data is shifted by one byte.

#### protocol signal description.

#### RDYOIN.

Internal flag indicating the status of the mailbox

- 0 = DSP has access to the mailbox

- 1 = host has access to the mailbox

- a. RDYOIN is set by the DSP and reset by the host. That means that the DSP gives the mailbox to the host when it finishes using it and vice-versa. In no case can the host or the DSP take possession of the mailbox, it can only wait for the other to give it back.

- b. The ST18930/31 sees RDYOIN as a flag :

- \_ tested by a branch instruction

- set to 1 by an initialization instruction in order to give the availability of the mailbox to the host.

#### IRQ.

Handshake signal enabling the host to gain access to the mailbox.

- IRQ is asserted low by the DSP to indicate the availability of the mailbox (at the same time as RDYOIN).

- b. The host after testing IRQ, knows that it can access the mailbox. The access to the bus (which can be currently used by the DSP as a local address bus) must be requested by reading the address CS = 0, RS = 0.

- c. The DSP then answers back by asserting IRQ high. (In pseudo-slave mode, the DSP is halted). The host now has full control of the bus and mailbox.

When the host has completed the exchange it generates the address CS = 0, RS = 1 and the DSP resets RDYOIN.

HALT (internal).

The internal halt has the following effect on the circuit :

- the program is stopped at the end of the current instruction, the program and loop counter are frozen

a NOP is executed

- no more addresses are generated on the system bus

in the slave. The two slave address pins (CS, RS)

Therefore, the slave is seen as two external memo-

are directly connected to two host address lines.

## Figure 10 : Mailbox Connection and Protocol.

MAILBOX INTERRUPT.

Enabled by initializing the bit EIMB of Access Mode Register (AMR). When RDYOIN is reset, the PC is forced to address \$ 0001.

Refer to figures 11.A and 11.B for timing detail of mailbox protocol.

By addressing the location 00 the host echoes the IRQ to the slave and accesses the mailbox.

By addressing the location 01 the host releases the bus.

ST18930/31

21/66

This Material Copyrighted By Its Respective Manufacturer

5

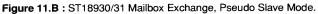

SGS-THOMSON MICROELECTRONICS **3.5.7. Access Mode Register (AMR).** The AMR is a 9-bit register which defines the processor external access modes.

It is loaded by an INI or SVR instruction and saved by an SVR instruction. Its fields are defined as follows :

Bits 0 and 7 - SE0, SE1.

These two bits define the number of cycles fixed by the user to access external resources. If the user defines a multicycle exchange (i.e. for access to slow memories), internal wait states are automatically inserted allowing the processor to wait for the completion of the external exchanges. The instruction executes once with the number of cycles chosen by the programmer.

Multicycles exchanges can be programmed in any operating mode (real, complex or double precision).

| SE1 | SE0 | Number of machine cycles<br>for external access |

|-----|-----|-------------------------------------------------|

| 0   | 0   | 1                                               |

| 0   | 1   | 2                                               |

| 1   | 0   | 3                                               |

| 1   | 1   | 4                                               |

Bit 1 : SL/PS.

0 = Slave.

1 = Pseudo-slave.

This bit defines the behaviour of the ST18930/31 regarding the system bus (AD0-AD7). In slave mode, the processor will never use the system bus as local bus address.

In pseudo-slave, the processor uses address bus (AD0-AD7) for local resources. These bits are concatenated with A8-A11 to form a 12-bit address bus.

Bit 2 : SB/CB.

0 = Separated bus.

1 = Concatenated bus.

This bit indicates whether the local bus is used as a 16-bit concatenated bus or as 2 independent 8-bit buses.

(see 3.5.4. - local bus description).

22/66

Bit 3 : I ntel/Motorola type local bus

0 = Control pulses Read ( $\overline{RD}$ ) and Write ( $\overline{WR}$ ) are generated. This is the case with an Intel type peripheral or a standard byte-wide <u>RAM</u>.

1 = Control pulses data strobe (DS) and Read/Write (R/W) are generated.

This is the case for exchanges with a slave processor, a Motorola type peripheral, a data converter such as the TS7542 or the M.A.F.E. chip set (TS68950/51/52).

Bit 4 : DTACK/BE6.

0 = DTACK function. The ST18930/31 does acknowledge correct access by generation of a DTACK output.

1 = BE6. An external test condition is available on pin BE6.

Bit 5 : BA/BE5.

0 = Configurates the pin (BA)5 as bus available output indicating the availability of the system bus.

1 = Pin BE5 is used for external test conditions.

Bit 6 : MASK (ST18931 only).

0 = An external Halt applied to the processor will not change the values in the AMR register.

1 = During external Halt applied to the processor the AMR register is forced to following configuration : one cycle exchange, pseudo-slave, concatenated bus, RD and WR control pulses.

This bit can be modified by the programmer even while the HALT is asserted.

Bit 8 : EIMB.

Enables interrupt mailbox. When set to 1, this bit validates the start of an interrupt when RDYOIN internal flag goes low.

This bit is programmed with an INI instruction.

574

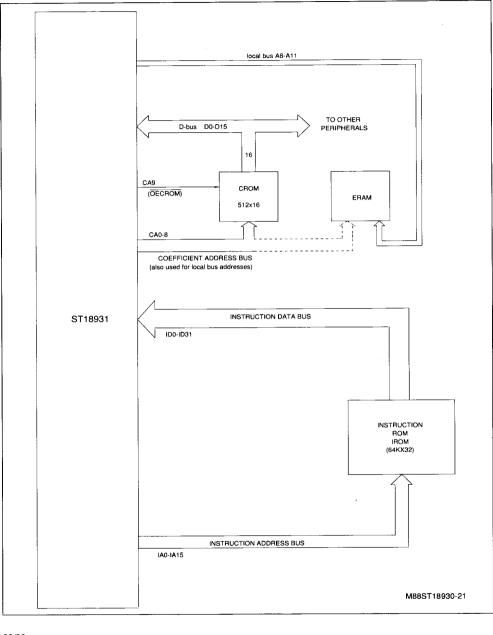

**3.5.8.** Instruction interface and system control (ST18931 only). On the ST18931, the coefficient ROM and the instruction ROM (CROM & IROM) are external. The device provides the necessary buses to access these data. Instructions are read on ID0 : ID31 using IA0-IA15 for addressing. Coefficients are read on local address bus D0-D15 using CA0-CA8 for addressing. CA9 is at low level for address validation. CA0-CA7 also contains external RAM addresses (if necessary) associated with a high level for CA9.

So, for the ST18931, there is no need of a pseudo slave mode as AD0-AD7 remain available for data transfer on the system bus. Clock signals are also provided fo<u>r interfacing purposes</u> (3.6.1.). Controls signals on CSDL and CSDH indicates data transfers on D0-<u>D7 and D8-D15</u> respectively when at a low level. A NOP control input is also provided on ST18931 to allow hardware simplification of development systems. This input forces a NOP instruction when low and forces all addresses in high impedance state.

**3.5.9. Halt (ST18931 only).** The external HALT signal will freeze the program counter, the loop counter and the multiplier. The instruction register can then be loaded from an external source. This signal is used for system development.

#### 3.6. OTHER RESOURCES

**3.6.1. Clock generators.** Three different clock outputs are available on the ST18931 and one on the ST18930.

CLKOUT : available on ST18930 and ST18931.

INCYCLE and MC (master clock) : available on ST18931 only.

The internal processor cycle is equal to the frequency of the EXTAL input divided by 2 or 4. The choice of the dividing factor is done by option at the masking level for the ST18930 and by control of CC input on the ST18931. If CC = 1 then the dividing factor is 2, if CC = 0 it becomes 4 for TS68930/31 compatibility.

The CLKOUT output period is function of the EX-

TAL period and the value of CRR register programmed by INI instruction.

| CRR (3; 0) | CLKOUT/EXTAL RATIO |  |

|------------|--------------------|--|

| 1          | 2                  |  |

| 2          | 3                  |  |

|            |                    |  |

| 15         | 16                 |  |

The INCYCLE output is equal to instruction cycle. The MC output period is equal to half of EXTAL period.

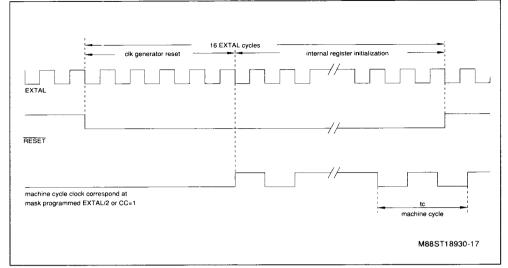

**3.6.2. Reset.** The reset signal acts on several processors blocks as follows :

- Sequencer : the program counter (PC) and the loop counter (LC) are cleared to zero. The instruction register is loaded with NOP instruction.

- Status register : set in real mode, no saturation, empty FIFO (EF = 1), overflows (MOVF = AOVF = OVFM = 0), interrupt disabled (EI = 0), and XRAM and YRAM in non circular addressing mode.

- Access Mode Register (AMR) : set for one cycle external exchange, slave mode, concatenated bus, RD and WR, BE5 and BE6.

- Motorola mode is set on system bus.

- Mailbox control is disabled.

The reset signal must be maintained for a minimum of 16 cycles of EXTAL signal (see fig. 12 for timing). If machine cycle = EXTAL  $\div$  2.

**3.6.3. Watchdog capability** (ST18930 only). The watchdog prevents the processor from staying locked in an undesired state or internal loop caused by adverse conditions. The circuitry does include a 2-bit counter which is incremented by each falling edge on BE3 input and reset by software testing of the BE3 condition. If three falling edges of BE3 input occurs without a test of the condition, the ST18930 is reset by the watchdog circuit. This capability is a mask option of the ST18930.

#### Figure 12 : Reset Timing.

**3.6.4. Low power mode.** The low power mode freezes the circuit operation and divide by 16 the internal clock generator frequency (see masking options).

In this mode, the DSP will use typically less than 5 mA.

The access to this mode can be done by software or hardware.

- Hardware mode :

On the ST18931 and the ST18930 in PLCC 52 package the LP pin forces the low power mode.

For the ST18930 in 48 pin package, the BS2 pin can be configurated by a mask option as a low power mode input pin. In this case, if the bit El of the status register is set to 1, BS2 pin will work as low power control pin, and

If EI = 0, BS2 will work as a branch condition pin.

- Software mode :

The low power mode is activated by an INI instruction.

The return from low power mode is obtained with a reset or an interrupt.

## ST18930/31

## 4. TYPICAL APPLICATION CONFIGURATIONS

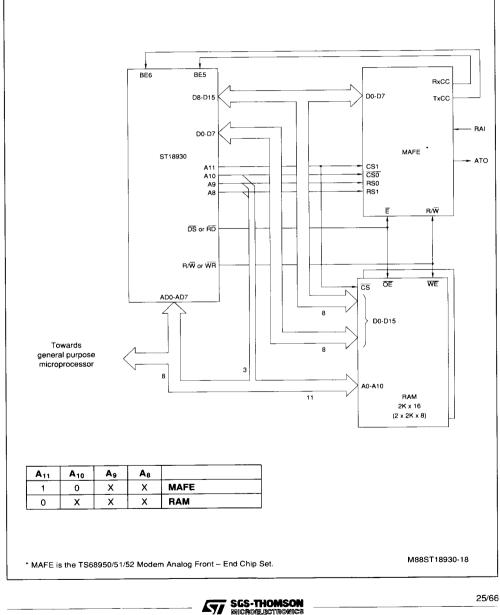

## Figure 13 : Configuration Example with ST18930 + RAM + MAFE\*.

ST18930/31

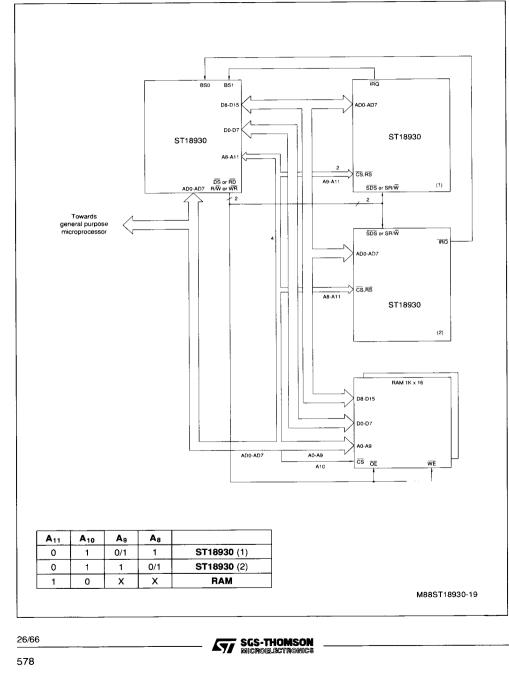

Figure 15 : Configuration Example 4 ST18930 + MAFE + RAM.

SGS-THOMSON MICROELECTHONICS

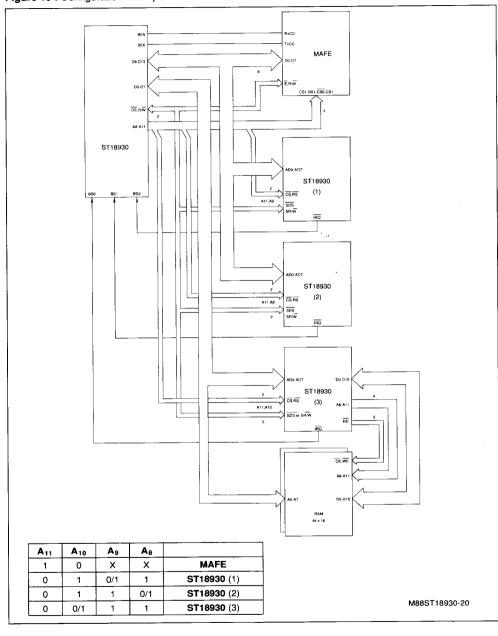

Figure 16 : Interfacing CROM, IROM to ST18931.

580

Ц

## 5. INSTRUCTION SET

|                          |                                                     |                                                                                       | Number | of Cycles    |

|--------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------|--------|--------------|

| Symbol                   | Туре                                                | Operation                                                                             | REAL   | CPLX<br>DBPR |

| OPIN                     | Calculation Instruction with Indirect<br>Addressing | This instruction refers to operands indirectly addressed.                             | 1      | 2            |

| OPDI                     | Calculation Instruction with Direct<br>Addressing   | The operand sourcing the L-BUS is directly addressed.                                 | 1      | 2            |

| OPIM                     | Calculation Instruction with Immediate<br>Operand   | An immediate operand is read on R-BUS.                                                | 1      | 2            |

| ASR<br>ASL<br>LSR<br>ROR | General Shift Instruction                           | The operand sourcing the L-BUS can be shifted/rotated by $0 \rightarrow 15$ bits.     | 1      | 2            |

| BRI                      | Immediat Branch Instruction                         | Conditional/unconditionnal branch to direct address.                                  | 2      | 2            |

| BRC                      | Computed Branch Instruction                         | Conditional/unconditional branch to<br>computed address.                              | 2      | 2            |

| SVR<br>TFR               | Data Transfer Instruction                           | This instruction is used to save<br>register contents in external or<br>internal RAM. | 1      | 2            |

| INI                      | Initialization and Control Instruction              | Pointers, acces mode register, loop counter, mode initialization, interrupts.         | 1      | 2            |

## INSTRUCTION SET LANGUAGE DEFINITIONS

| LDT       Load L-BUS source into Transfer Register T         R SRC       R-BUS Source         L SRC       L-BUS Source         SL       ALU Input Selection Left Side         SR       ALU Input Selection Right Side         ALU DST       ALU Output Destination         ALU CODE       ALU Codes         LDM       Load L-BUS Source into Multiplier Input M         LDN       Load R-BUS Source into Multiplier Input N         Z SRC       Z-BUS SOURCE         Z DST       Z-BUS DESTINATION         ZT       Load Z-BUS into Transfer Register T         ACE       Post Incrementation Pointers CROM or ERAM |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L SRC       L-BUS Source         SL       ALU Input Selection Left Side         SR       ALU Input Selection Right Side         ALU DST       ALU Output Destination         ALU CODE       ALU Codes         LDM       Load L-BUS Source into Multiplier Input M         LDN       Load R-BUS Source into Multiplier Input N         Z SRC       Z-BUS SOURCE         Z DST       Z-BUS DESTINATION         ZT       Load Z-BUS into Transfer Register T                                                                                                                                                           |

| SL       ALU Input Selection Left Side         SR       ALU Input Selection Right Side         ALU DST       ALU Output Destination         ALU CODE       ALU Codes         LDM       Load L-BUS Source into Multiplier Input M         LDN       Load R-BUS Source into Multiplier Input N         Z SRC       Z-BUS SOURCE         Z DST       Z-BUS DESTINATION         ZT       Load Z-BUS into Transfer Register T                                                                                                                                                                                            |

| SR       ALU Input Selection Right Side         ALU DST       ALU Output Destination         ALU CODE       ALU Codes         LDM       Load L-BUS Source into Multiplier Input M         LDN       Load R-BUS Source into Multiplier Input N         Z SRC       Z-BUS SOURCE         Z DST       Z-BUS DESTINATION         ZT       Load Z-BUS into Transfer Register T                                                                                                                                                                                                                                           |

| ALU DST       ALU Output Destination         ALU CODE       ALU Codes         LDM       Load L-BUS Source into Multiplier Input M         LDN       Load R-BUS Source into Multiplier Input N         Z SRC       Z-BUS SOURCE         Z DST       Z-BUS DESTINATION         ZT       Load Z-BUS into Transfer Register T                                                                                                                                                                                                                                                                                           |

| ALU CODE       ALU Codes         LDM       Load L-BUS Source into Multiplier Input M         LDN       Load R-BUS Source into Multiplier Input N         Z SRC       Z-BUS SOURCE         Z DST       Z-BUS DESTINATION         ZT       Load Z-BUS into Transfer Register T                                                                                                                                                                                                                                                                                                                                        |

| LDM       Load L-BUS Source into Multiplier Input M         LDN       Load R-BUS Source into Multiplier Input N         Z SRC       Z-BUS SOURCE         Z DST       Z-BUS DESTINATION         ZT       Load Z-BUS into Transfer Register T                                                                                                                                                                                                                                                                                                                                                                         |

| LDN       Load R-BUS Source into Multiplier Input N         Z SRC       Z-BUS SOURCE         Z DST       Z-BUS DESTINATION         ZT       Load Z-BUS into Transfer Register T                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Z SRC     Z-BUS SOURCE       Z DST     Z-BUS DESTINATION       ZT     Load Z-BUS into Transfer Register T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Z DST     Z-BUS DESTINATION       ZT     Load Z-BUS into Transfer Register T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ZT Load Z-BUS into Transfer Register T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ACE Post Incrementation Pointers CROM or ERAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AY Post Incrementation Pointers YRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AX Post Incrementation Pointers XRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BRA Branch Address Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| FT False/True Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SVPC Save Program Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| JDST Destination Register for J Constant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| KDST Destination Register for K Constant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MODE Operating Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SAT Saturation Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ADOF Even/odd Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| J Constant 8-bit Constant used to initialize registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| K Constant 12-bit constant used to initialize registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

ΙE

30/66 582

#### 5.1 OPERATING CODE FORMATS

| Bit                        | Field    | Operations and Codes                                                       |

|----------------------------|----------|----------------------------------------------------------------------------|

| 31<br>30                   | OP CODE  | 00                                                                         |

| 29                         | LDT      | 0-NO LOAD, 1-LBUS $\rightarrow$ T                                          |

| 28<br>27                   | R SRC    | 00 01 10 11<br>[X0] [E0] [Y0] [Y1]                                         |

| 26<br>25<br>24             | L SRC    | 000 001 010 011 100 101 110 111<br>[X0] [X1] [Y0] RIN T [E1] [C0] [C1]     |

| 23                         | SL       | 0-LBUS / 1-P                                                               |

| 22                         | SR       | 0-RBUS / 1-A/B (refer to ALU DST)                                          |

| 21<br>20<br>19<br>18<br>17 | ALU CODE | cf. Special Table                                                          |

| 16<br>15                   | ALU DST  | 00 01 10 11<br>D F A B                                                     |

| 14<br>13<br>12             | Z SRC    | 000 001 010 011 100 101 110 111<br>D F A B T CCR                           |

| 11                         | LDM      | 0-NO LOAD / 1-LBUS $\rightarrow$ M                                         |

| 10                         | LDN      | 0-NO LOAD / 1-RBUS $\rightarrow$ N                                         |

| 9<br>8                     | ACE      | 00 01 10 11<br>+ 0 + 1 1                                                   |

| 7<br>6                     | AY       | 00 01 10 11<br>+ 0 + 1 1                                                   |

| 5<br>4                     | AX       | 00 01 10 11<br>+ 0 + 1 1                                                   |

| 3<br>2<br>1                | Z DST    | 000 001 010 011 100 101 110 111<br>NONE ROUT [Y0] [Y1] [E0] [E1] [X0] [X1] |

| 0                          | ZT       | 0-NO LOAD / 1 ZBUS $\rightarrow$ T                                         |

Fig. 17 : OPIN : Calculation Instruction with Indirect Addressing.

| Bit                                                            | Field                     | Operations and Codes                                                                                                         |

|----------------------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 31<br>30<br>29                                                 | OP CODE                   | 010                                                                                                                          |

| 28<br>27                                                       | R SRC                     | 00 01 10 11<br>[X0] [E0] [Y0] [Y1]                                                                                           |

| 26<br>25<br>24                                                 | L SRC                     | 000 001 010 011 100 101 110 111<br>X - Y RIN T E - C                                                                         |

| 23                                                             | Z SRC                     | 0-D / 1-F                                                                                                                    |

| 22                                                             | SR                        | 0-RBUS / 1-A                                                                                                                 |

| 21<br>20<br>19<br>18<br>17                                     | ALU CODE                  | cf. Special Table                                                                                                            |

| 16                                                             | ALU DST                   | 0-F / 1-A                                                                                                                    |

| 15<br>14<br>13<br>12<br>11<br>10<br>9<br>8<br>7<br>6<br>5<br>4 | LBUS<br>DIRECT<br>ADDRESS | MSB<br>LSB                                                                                                                   |

| 32                                                             | Z DST                     | 0000 0010 0100 0110 1000 1010 1100 1110<br>NONE ROUT [Y0] [Y1] [E0] [E1] [X0] LCR<br>0001 0011 0101 0111 1001 1011 1101 1111 |

| 1<br>0                                                         |                           | X0 X1 Y0 Y1 E0 E1 C0 C1                                                                                                      |

1.

Fig. 18 : OPDI : Calculation Instruction with Direct Addressing.

32/66 584 SGS-THOMSON

| Bit                                                                                | Field                         | Operations and Codes                                                   |

|------------------------------------------------------------------------------------|-------------------------------|------------------------------------------------------------------------|

| 31<br>30<br>29<br>28<br>27                                                         | OP CODE                       | 01110                                                                  |

| 26<br>25<br>24                                                                     | L SRC                         | 000 001 010 011 100 101 110 111<br>[X0] [X1] [Y0] RIN T [E1] [C0] [C1] |

| 23                                                                                 | SL                            | 0-LBUS / 1-P                                                           |

| 22                                                                                 | SR                            | 0-RBUS / 1-A                                                           |

| 21<br>20<br>19<br>18<br>17                                                         | ALU CODE                      | cf. Special Table                                                      |

| 16                                                                                 | ALU DST                       | 0-F / 1-A                                                              |

| 15<br>14<br>13<br>12<br>11<br>10<br>9<br>8<br>7<br>6<br>5<br>4<br>3<br>2<br>1<br>0 | IMMEDIATE<br>VALUE<br>(R-BUS) | MSB                                                                    |

Fig. 19 : OPIM : Calculation Instruction with Immediate Operand.

| Bit                                                            | Field                     | Operations and Codes                                                |

|----------------------------------------------------------------|---------------------------|---------------------------------------------------------------------|

| 31<br>30<br>29<br>28<br>27                                     | OP CODE                   | 01111                                                               |

| 26<br>25<br>24                                                 | L SRC                     | 000 001 010 011 100 101 110 111<br>X – Y RIN T E – C                |

| 23                                                             | SL                        | 0-LBUS / 1-P                                                        |

| 22<br>21                                                       | ALU CODE                  | 00 01 10 11<br>ASR LSL LSR ROR                                      |

| 20<br>19<br>18<br>17                                           | SHIFT<br>VALUE            | NOTE : When LSR, ASR, ROR           0000 0001 1111           0 1 15 |

| 16                                                             | ALU DST                   | 0-F / 1-A                                                           |

| 15<br>14<br>13<br>12<br>11<br>10<br>9<br>8<br>7<br>6<br>5<br>4 | LBUS<br>DIRECT<br>ADDRESS | MSB<br>LSB                                                          |

| 3                                                              |                           |                                                                     |

| 2                                                              |                           |                                                                     |

| 0                                                              | l                         |                                                                     |

.

Fig. 20 : ASR, LSL, LSR, ROR, Shift Instructions.

34/66 586

Ц

| Fig. 21.                                                                                 | ig. 21 : BRI : Branch Immediate Instruction. |                                                                   |  |  |

|------------------------------------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------|--|--|

| Bit                                                                                      | Field                                        | Operations and Codes                                              |  |  |

| 31<br>30<br>29                                                                           | OP CODE                                      | 100                                                               |  |  |

| 28                                                                                       | BRA                                          | 0-IR, 1-RAS                                                       |  |  |

| 27                                                                                       | FT                                           | 0-FALSE, 1-TRUE                                                   |  |  |