## ST18940/41

## DIGITAL SIGNAL PROCESSOR

#### MAIN FEATURES

- 100ns MACHINE CYCLE TIME (1.2 CMOS Technology)

- PARALLEL HARVARD ARCHITECTURE

- TRIPLE DATA BUSES STRUCTURE

- 3 DATA MODES . SINGLE PRECISION . DOUBLE PRECISION . COMPLEX

- 32-BIT INSTRUCTION

- MULTIPLIER 16 x 16 -> 32, SIGNED AND UN-SIGNED

- 32-BIT BARREL SHIFTER, 32-BIT ALU

- PROVISION FOR FLOATING POINT

- FOUR 32-BIT ACCUMULATORS, FOUR LE-VEL 32-BIT FIFO

- IMMEDIATE AND COMPUTED BRANCH

- 8-LEVEL STACK

- 9 EXTERNAL AND 3 INTERNAL INTERRUPTS

- AUTOMATIC LOOP, UP TO 256 TIMES 32 INSTRUCTIONS

- 2 INDEPENDENT PARALLEL BUSES; LOCAL AND SYSTEM

- FULL SPEED ACCESS TO EXTERNAL 64K x 16-BIT MEMORY ON THE LOCAL BUS

- HARDWARE AND/OR SOFTWARE WAIT STATES MODE TO ACCESS SLOWER EX-TERNAL MEMORIES/PERIPHERALS, DMA CHANNEL

- 2 x 16 BYTES FIFO ON THE SYSTEM BUS

- SERIAL CHANNEL FOR DIRECT INTERFACE WITH CODEC, ISDN IC's...

- GENERAL PURPOSE PARALLEL PORT

- ON CHIP DATA RAM 2 x 256 x 16-bit

- FOUR INDEPENDENT ADDRESS CALCULA-TION UNITS

- ADDRESSING MODES: IMMEDIATE, DIRECT, INDIRECT WITH POST MODIFICATION, CIR-CULAR, BIT REVERSED

- 2 VERSIONS:-ST18940 (PLCC/PGA 84) CLO-SED VERSION WITH 3K x 32-BIT ON-CHIP PROGRAM ROM AND 512 x 16-BIT COEFFI-CIENT ROM

- ST18941 (PGA 144) OPEN VERSION WITH 64K x 32-BIT OFF-CHIP PRO-GRAM ROM AND 128 x 16 BIT ON-CHIP COEF-FICIENT RAM

- POWER DOWN MODE

- TYPICAL CONSUMPTION 0.5W

#### **DEVELOPMENT SYSTEM**

The ST18940-41 is supported by a complete set of hardware and software tools for system development. The software package includes an assembler/linker, a simulator, and a "C" compiler and optimizer which run under several VAX and PC operating systems. Hardware tools include a standalone emulator, an EPROM emulation module, a multiprocessor development station and an evaluation module (PC compatible).

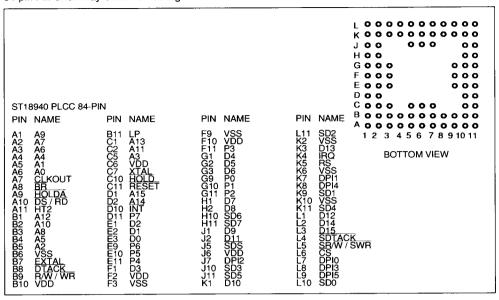

ST18941 - PIN GRID ARRAY - 144-pin

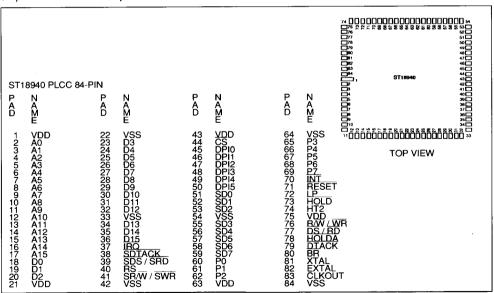

ST18940 - PLASTIC LEADED CHIP CARRIER - 84-pin

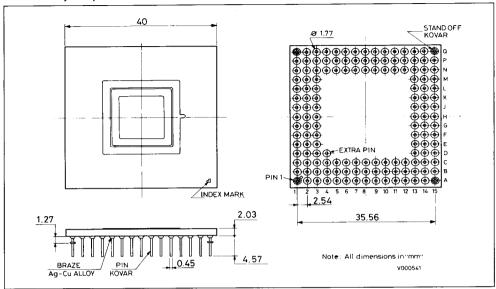

ST18940 - PIN GRID ARRAY - 84-pin

March 1989

1/50

#### DESCRIPTION

The ST18940/41 Digital Signal Processor is a member of SGS-THOMSON Microelectronics ST18 family.

The ST18 family comprises 3 products covering a wide spectrum of DSP applications. Complete development tools (hardware and software) are available as aids to efficient system designs.

The first processor in the ST18 family is the TS68930/31 (NMOS) with a 160ns machine cycle time. The second member of the family, the ST18930/31, is a CMOS version of the TS68930 with a faster instruction cycle time (80ns) and the inclusion of additional hardware and software features (The ST18930 is pin compatible with the TS68930).

The ST18940/41, which is described in this datasheet, is the third member in the family. It is upward compatible with the other members of the family, but provides enhanced arithmetic capabilities, addressing modes and additional I/O functions. It is an advanced HCMOS single chip general purpose DSP designed for fast arithmetic intensive applications in the areas of telecommunications, modems, speech processing, graphic/image processing spectrum analysis, audio processing, digital filtering, high speed control, instrumentation, numeric processing...

The ST18940 structure is based on a triple 16-bit data bus, a 16 x 16 multiplier, a 32-bit ALU. The powerful parallel and serial Input/Output interfaces and the DMA channel contribute to the flexibility of the system interface with external environment.

Two versions are available:

- \_ the ST18940 includes 3K x 32-bit program ROM and 512 x 16-bit coefficient ROM.

- the ST18941 microprocessor version can address up to 64K of program memory on a dedicated bus, thus providing true real-time emulation of the ST18940 ROM version. In addition to the two internal RAMs (X and Y), a 128 x 16-bit coefficient RAM is included for coefficient memory emulation.

## **TABLE OF CONTENTS**

|    | TITLE                                      | Page |

|----|--------------------------------------------|------|

| 1. | PIN DESCRIPTION                            | 6    |

|    | 1.1. LOCAL BUS                             | 7    |

|    | 1.2. SYSTEM BUS                            | 7    |

|    | 1.3. DMA/SERIAL I/O INTERFACE              | 7    |

|    | 1.4. PARALLEL/INTERRUPT INTERFACE          | 8    |

|    | 1.5. POWER SUPPLY/CLOCK                    | 9    |

|    | 1.6. OTHER PINS                            | 9    |

|    | 1.7. SPECIFIC PINS TO THE ST18941          | 9    |

| 2. | ARCHITECTURE                               | 9    |

| 3. | BLOCK DIAGRAM                              | 10   |

| 4. | FUNCTIONAL DESCRIPTION                     | 10   |

|    | 4.1. INTRODUCTION                          | 10   |

|    | 4.2 PROGRAM CONTROLLER                     | 10   |

|    | 4.3. DATA ARITHMETIC UNIT                  | 12   |

|    | 4.4. DATA STORAGE UNIT                     | 16   |

|    | 4.5. INPUT/OUTPUT                          | 18   |

| 5. | SYSTEM CONFIGURATION                       | 22   |

|    | 5.1. MINIMUM APPLICATION (ST18940)         | 22   |

|    | 5.2. BUS EXTENSION                         | 24   |

|    | 5.3. SPECIFIC APPLICATION WITH THE ST18941 | 25   |

| 6. | SOFTWARE                                   | 26   |

|    | 6.1. INSTRUCTION FORMAT                    | 26   |

|    | 6.2. INSTRUCTION SET                       | 27   |

|    | CO DEOCEDAMMING EYAMDI E                   | 29   |

|     | TITLE                                | Page |

|-----|--------------------------------------|------|

| 7.  | ELECTRICAL SPECIFICATIONS            | 30   |

|     | 7.1. ABSOLUTE MAXIMUM RATINGS        | 30   |

|     | 7.2. DC ELECTRICAL CHARACTERISTICS   | 30   |

|     | 7.3. CLOCK CHARACTERISTICS           | 30   |

|     | 7.4. AC MEASUREMENTS CONDITIONS      | 31   |

|     | 7.5. EXTERNAL CLOCK OPTION           | 32   |

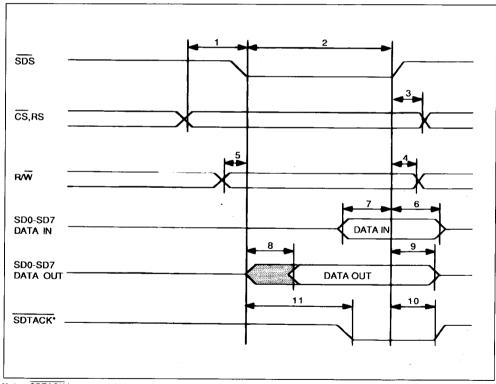

|     | 7.6. SYSTEM BUS TIMING               | 33   |

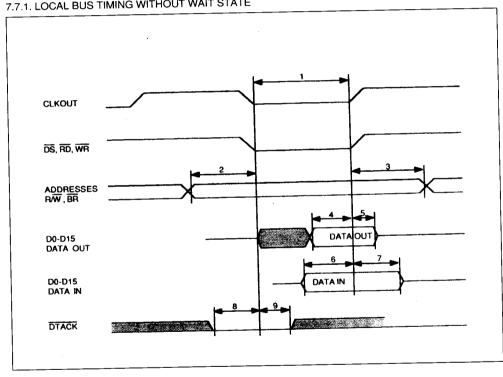

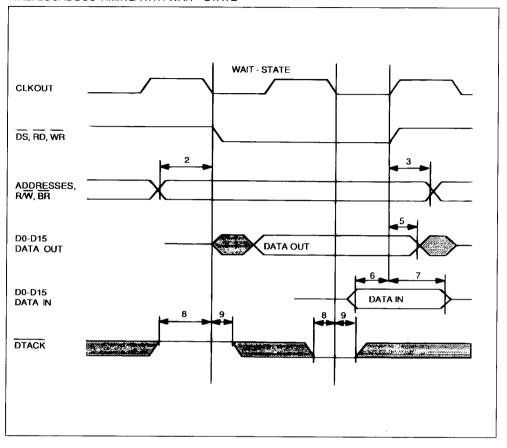

|     | 7.7. LOCAL BUS TIMING                | 34   |

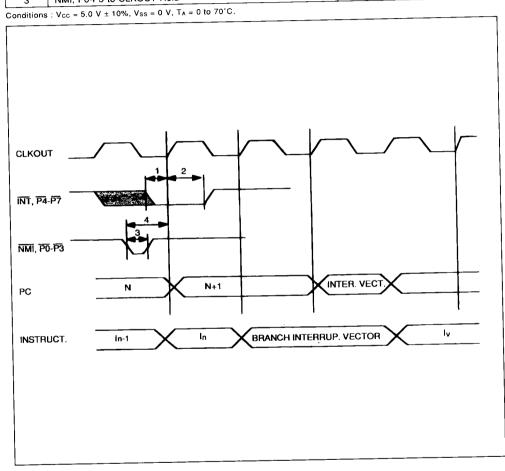

|     | 7.8. INTERRUPT TIMING                | 36   |

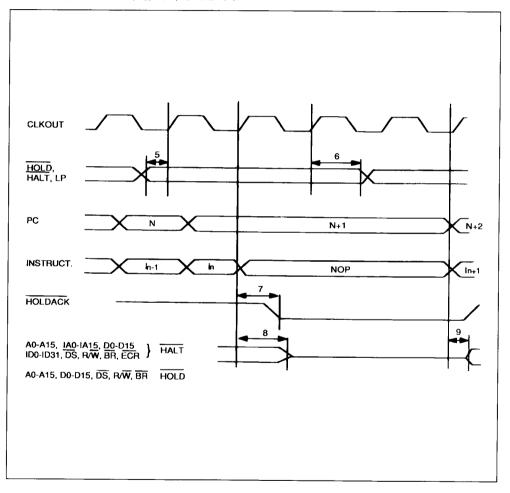

|     | 7.9. HOLD, LP, HALT TIMING           | 37   |

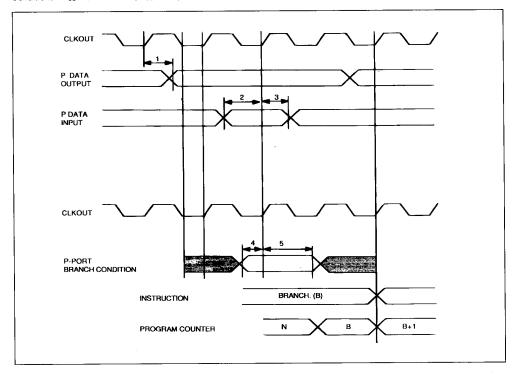

|     | 7.10. P-PORT TIMING                  | 38   |

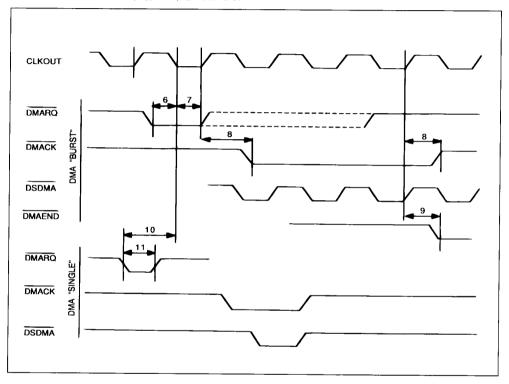

|     | 7.11. DMA TIMING                     | 39   |

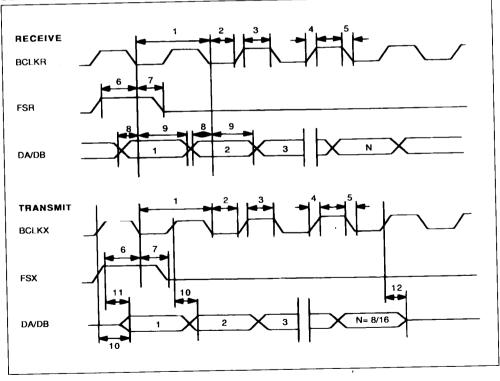

|     | 7.12. SERIAL CHANNEL TIMING          | 40   |

|     | 7.13. INSTRUCTION BUS TIMING ST18941 | 43   |

| 8.  | PIN CONNECTIONS                      | 44   |

|     | 8.1. ST18941 - OPEN VERSION          | 44   |

|     | 8.2. ST18940 - MASKED VERSION        | 45   |

| 9.  | ORDERING INFORMATION                 | 46   |

|     | 9.1. DEVICE                          | 46   |

|     | 9.2. SOFTWARE TOOLS                  | 46   |

|     | 9.3. HARDWARE TOOLS                  | 46   |

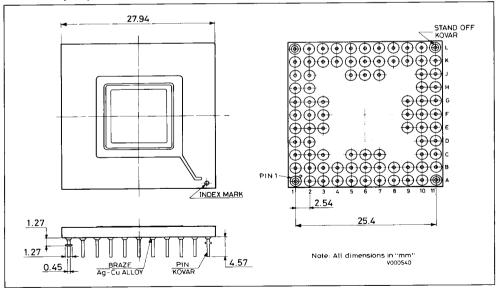

| 10. | MECHANICAL DATA                      | 47   |

| 11. | DEVELOPMENT TOOLS                    | 48   |

|     |                                      |      |

|     | TABLE OF APPENDICES                  |      |

|     | A. BENCHMARK                         | 49   |

**B. MASKING INFORMATION**

50

| TITLE                                          | Page |

|------------------------------------------------|------|

| TABLE OF FIGURES                               |      |

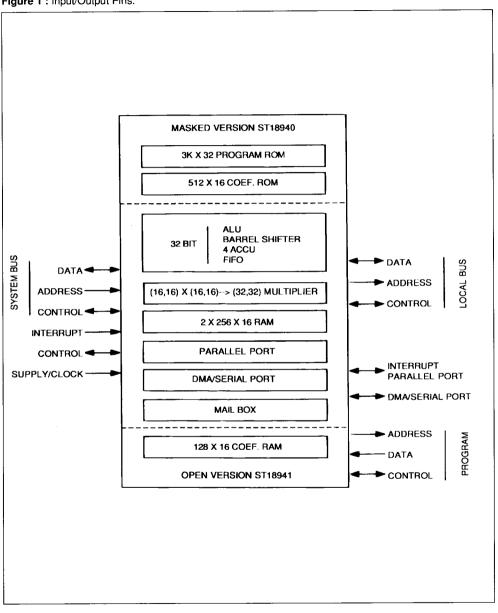

| Figure 1 : Input/output pins.                  | 6    |

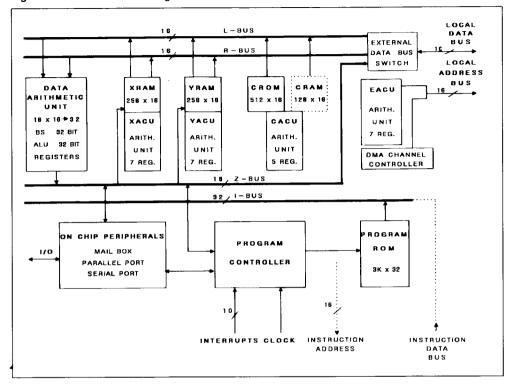

| Figure 2 : ST18940-41 Block diagram.           | 10   |

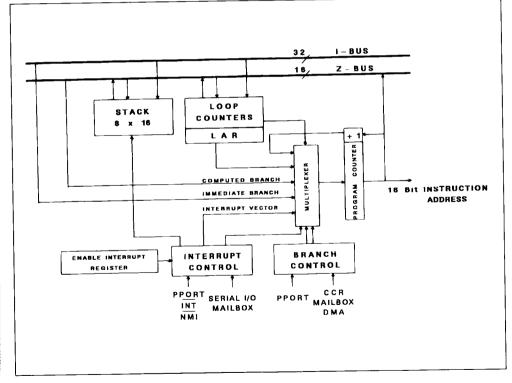

| Figure 3: ST18940-41 Program controller.       | 11   |

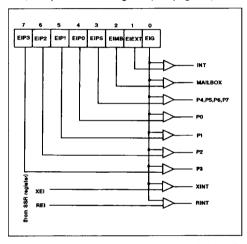

| Figure 4: Interrupt-enable Register.           | 12   |

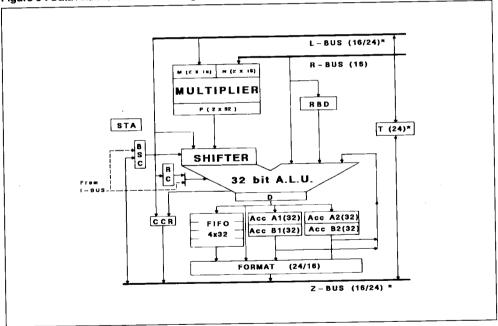

| Figure 5 : Data Arithmetic unit block diagram. | 13   |

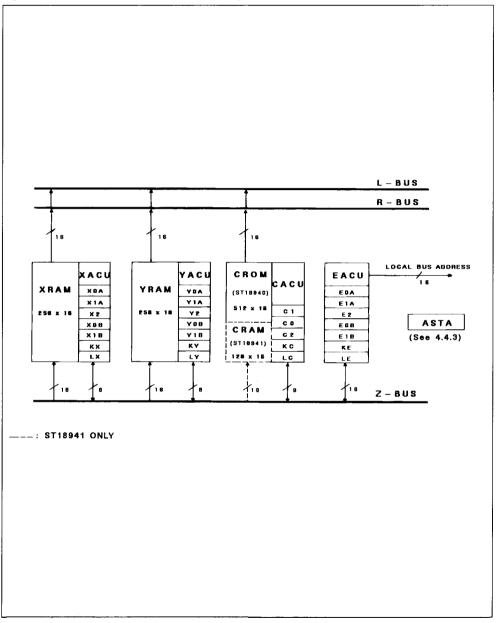

| Figure 6 : Data Storage unit block diagram.    | 17   |

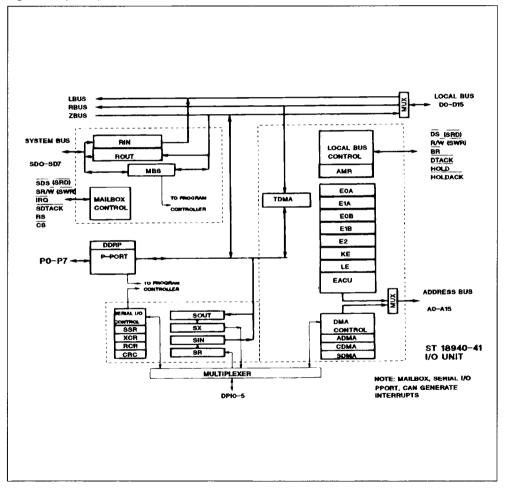

| Figure 7 : Input/Output functions.             | 19   |

#### 1. PIN DESCRIPTION

Figure 1: Input/Output Pins.

6/50

624

SGS-THOMSON

#### 1.1. LOCAL BUS

| Name     | Pins | Function                  | Description                                                                                                                         |

|----------|------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

|          | Type |                           |                                                                                                                                     |

| D0-D15   | 1/0  | Local Data Bus            | 16-Bit Data Bus. In high impedance when exchanges are not active or when RESET, HOLD, HALT or LP are active.                        |

| A0-A15   | 0    | Local Address Bus         | 16-Bit Address Bus for Local Data. In high impedance when HOLD, HALT or LP are active.                                              |

| DS/RD    | 0    | Data Strobe/read          | Synchronizes the transfer on local bus/read cycle.                                                                                  |

| R/W / WR | 0    | Read/write/write          | Indicates the current bus cycle state/write cycle.                                                                                  |

| DTACK    | ī    | Data Transfer Acknowledge | Indicates exchange acknowledgement.                                                                                                 |

| BR       | 0    | Bus Request               | Active at each exchange on the local bus. In combination with DTACK, can be used to address resources shared by several processors. |

| HOLD     | I    | Hold Data                 | Used to free local bus in shared memory application. To HALT state if an access is attempted.                                       |

| HOLDACK  | 6    | Hold Acknowledge          | Indicates that the processor is in hold state.                                                                                      |

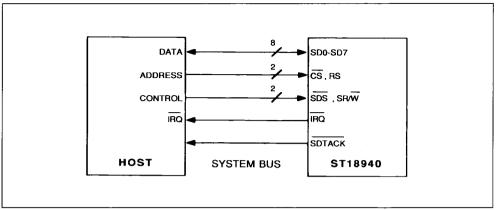

## 1.2. SYSTEM BUS

| Name     | Pins<br>Type | Function                            | Description                                                                            |

|----------|--------------|-------------------------------------|----------------------------------------------------------------------------------------|

| SD0-SD7  | I/O          | System Data Bus                     | 8-Bit data bus used for exchanges between the processor<br>and a host via the mailbox. |

| CS       |              | Chip Select                         | Selection of the system bus interface.                                                 |

| RS       | 1            | Register Select                     | Address to select data FIFO or status register (MBS).                                  |

| SDS/SRD  | ī            | Data Strobe/read                    | Synchronizes the transfer on the system bus/read cycle.                                |

| SR/W/SWR | 1            | Read/write/write                    | Indicates the current system bus cycle/write cycle.                                    |

| SDTACK   | 0            | System Data Transfer<br>Acknowledge | Indicates data exchange is acknowledged. Open drain.                                   |

| IRQ      | 0            | Interrupt Request                   | Signal sent to the host to signal readiness for mailbox data exchange.                 |

## 1.3 DMA/SERIAL I/O INTERFACE : DUAL PURPOSE INTERFACE

Internally the DMA channel and serial I/O are implemented as fully independent separate blocks, al-

though externally they are share 4 dual purpose I/O pins.

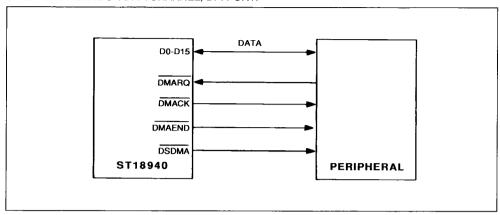

#### - DMA CHANNEL

| Name   | Pins<br>Type | Function        | Description                                                                                                  |

|--------|--------------|-----------------|--------------------------------------------------------------------------------------------------------------|

| DMARQ  | ı            | DMA Request     | Activated by the device requesting the DMA. Can be a pulse ("single" mode) or a level ("burst" mode) (DPI0). |

| DMACK  | 0            | DMA Acknowledge | Indicates that the request for DMA is acknowledged (DPI1).                                                   |

| DMAEND | 0            | DMA End         | Indicates the end of the DMA exchange. Active as long as the channel is not reinitialized (DPI2).            |

| DSDMA  | 0            | Data Strobe DMA | Synchronizes the DMA exchange (DPI3).                                                                        |

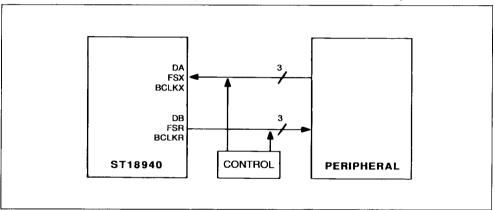

#### - SERIAL INPUT/OUTPUT INTERFACE

| Name  | Pins<br>Type | Function                             | Description                                                                      |

|-------|--------------|--------------------------------------|----------------------------------------------------------------------------------|

| FSR   | 1/0          | Frame<br>Synchronization<br>Receive  | Synchronizes the receive. Can be generated or received by the processor (DPI0).  |

| BCLKR | I/O          | Bit Clock<br>Receive                 | Receive bit clock. Can be generated or received by the processor (DPI1).         |

| DA    | I/O          | Data A                               | Input or Output of Data A (DPI2).                                                |

| DB    | I/O          | Data B                               | Input or Output of Data B (DPI3).                                                |

| FSX   | I/O          | Frame<br>Synchronization<br>Transmit | Synchronizes the transmit. Can be generated or received by the processor (DPI4). |

| BCLKX | I/O          | Bit Clock<br>Transmit                | Transmit bit clock. Can be generated or received by the processor (DPI5).        |

Note: DMARQ/FSR, DMACK/BCKLR, DMAEND/DA, DSDMA/DB are multiplexed.

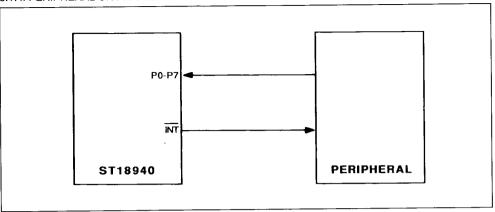

#### 1.4 PARRALLEL/INTERRUPT INTERFACE

This 8-bit port can be configured either as an interrupt controller or as a parallel input/output port.

#### - INTERRUPT CONTROLLER

| Name  | Pins<br>Type | Function                         | Description                                                                    |

|-------|--------------|----------------------------------|--------------------------------------------------------------------------------|

| P0-P3 | 1            | Maskable<br>Interrupt<br>Request | A negative transition on these input pins will initiate an interrupt sequence. |

| P4-P7 | ı            | Maskable<br>Interrupt<br>Request | A low level on these input pins will initiate an interrupt sequence.           |

## - PARALLEL INTERFACE

| Name  | Pins<br>Type | Function      | Description                                                                                                                                                                                    |

|-------|--------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0-P7 | I/O          | Parallel Port | 8-Bit parallel port with each bit programmable individually as input or output. Can be used as test conditions in branch instructions; four bits are edge sensitive, four are level sensitive. |

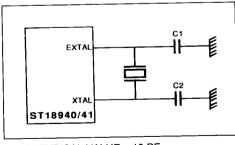

## 1.5. POWER SUPPLY - CLOCK

| Name            | Pins<br>Type | Function       | Description                                                                                                                                     |

|-----------------|--------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| XTAL            | 0            | Crystal Output | Internal oscillator output for crystal. Not connected if the internal oscillator is not used.                                                   |

| EXTAL/<br>CLKIN | 1            | Crystal Input  | Internal oscillator input. External clock input, when the internal oscillator is not used. Oscillator frequency is twice the machine frequency. |

| CLKOUT          | 0            | Clock Out      | Internal clock output (oscillator frequency ÷ 2).                                                                                               |

| V <sub>CC</sub> |              | 5 Volts        | Power Supply.                                                                                                                                   |

| Vss             |              | Ground         | Connected to Ground.                                                                                                                            |

### 1.6 OTHER PINS

| Name  | Pins<br>Type | Function  | Description                                                                                                                                                              |

|-------|--------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT   | 1            | Interrupt | Maskable interrupt request. Active Low                                                                                                                                   |

| RESET |              | Reset     | Program counter is loaded with Hex. 0 and a NOP instruction is executed. Clock generator is resynchronized.                                                              |

| LP    | ı            | Low Power | Stops the processor at the end of the current cycle, forces the NOP instruction and puts the processor in the powerdown mode. The internal processor state is conserved. |

| HT2   | 0            | Clock     | Reserved for test.                                                                                                                                                       |

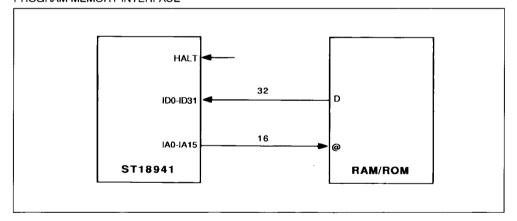

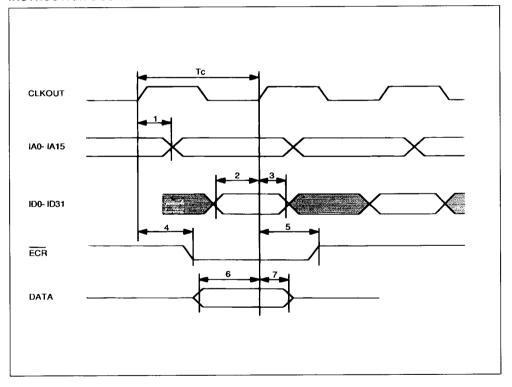

## 1.7. SPECIFIC PINS TO THE 18941 (open version)

| Name     | Pins<br>Type | Function                | Description                                                                                                                     |

|----------|--------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| IA0-IA15 | 0            | Instruction Address Bus | 16-Bit address <u>bus</u> for external program memory. In high impedance if HALT is active or during a DMA exchange.            |

| ID0-ID31 |              | Instruction Data Bus    | 32-Bit data bus from external program memory.                                                                                   |

| NMI      | ı            | Non Maskable Interrupt  | Interrupt input edge sensitive. Program counter is loaded with Hex. A.                                                          |

| HALT     | l            | Halt                    | Stops the processor at the end of the current instruction.<br>Local bus and instruction address buses are in high<br>impedance. |

| ECR      | 0            | Enable CROM             | Indicates that the A0-A8 addresses are used for the external emulation of the CROM.                                             |

| INCYCLE  | 0            | Instruction Clock       | A falling edge indicates the start of a new instruction cycle.                                                                  |

#### 2. ARCHITECTURE

The architecture is HARVARD like with separate instruction bus and data buses. The block diagram shows four main blocks (see fig. 2):

- the program controller

- the data arithmetic unit

- (ALU, multiplier and barrel shifter)

- the data storage unit

- the inputs/outputs

These four blocks can be considered as four independent processors working in parallel and communicating via three 16-bit data buses.

Within a single machine cycle the processor is able to execute all of the following operations:

- read two operands in internal or external memory

- execute a multiplication

- execute an ALU operation

- write a result to internal or external memory

- modify three address pointers

- in addition, I/O operations with on-chip peripherals may take place concurrently with internal operations.

SGS-THOMSON MICROELECTROPICS

9/50

#### 3. BLOCK DIAGRAM

Figure 2: ST18940/41 Block Diagram.

#### 4. FUNCTIONAL DESCRIPTION

#### 4.1. INTRODUCTION

One of the key features of the ST1840/41 is that all hardware resources have been designed to support the following three data types:

- simple precision: 16-bit data

- double precision: 32-bit data

- complex: 16-bit real and 16-bit imaginary

Any one of the above three arithmetic modes can be dynamically selected by means of a single program instruction. Once the mode has been selected, all resources (such as ALU, memories, registers, multiplier) are automatically configured for the appropriate operations. The same assembler instructions are used in all three modes. In double-precision and complex modes the data are

stored in two contiguous memory locations, with an automatic adjustment of the address calculation unit. Two's complement representation is used throughout. In real mode, all instructions except branch are executed in one cycle time. In complex and double precision modes, all instructions are executed in two cycle times.

#### 4.2. PROGRAM CONTROLLER

4.2.1. PROGRAM CONTROLLER (see figure 3). The purpose of the program controller is to generate the next instruction address to be executed, this instruction being in external memory for the ST18941 (64K word of 32-bit) or in the masked ROM for the ST18940 (3K word of 32-bit). The program controller takes into account the current mode to execute the instruction; one cycle per instruction in

10/50

SGS-THOMSON MICROELECTRONICS

real mode, two cycles per instruction in double precision and complex mode. The HALT. HOLD. LP and the "WAIT STATES" suspend the sequencer cycle.

Exceptions in linear program address generation are the following:

- Execution of a branch instruction

- Call and return of a subroutine

- Execution of an interrupt routine : 2 types of hardware interrupt sources are possible : external interrupt [INT + P PORT + NMI (ST18941 only)], internal interrupt (Mailbox, serial port). The El register enables or disables these interrupt sources.

- An 8-level stack is used to save and restore the PC in case of interrupts or subroutines.

- Loop execution: Automatic loop execution is possible by means of the loop register. This register defines the number of loops to be executed (max. 256), and the number of instructions in the loop (max. 32).

Figure 3: ST18940/41 Program Controller.

## Programming model for loop execution

LOOP: Loop Register

It is used to automatically control the execution of a loop. This 16-bit register is divided in to 3 fields, LCI, LCR, LCD.

LCI (Loop Count Instruction) defines the number of instructions to be executed in a loop; the maximum is 32 (5-bit).

LCR (Loop Count Register) defines the repeat count of the loop; the maximum is 256 (8-bit).

LCD (Delay) defines, in terms of the number of instructions, the delay between the loop declaration and the beginning of the loop execution. The maximum is 7 (3-bit).

This "repeat of instruction blocks" feature provides code compaction and time efficient execution for vector and array processing frequently used in DSP algorithms. It is set at the macroassembler level by using a simple REPE-BEGIN-END construct.

11/50

SGS-THOMSON

#### 422 INTERRUPT CONTROL

- \* There are two types of hardware interrupt sources on the ST18940/41 : internal and external.

- -The internal sources include chip peripheral devices : Mailbox (input/output)

Serial port (1 for transmit, 1 for Receive)

-The external interrupts include RESET, INT, NMI (ST18941 only) and the P Port (8 pins)

RESET, INT, P4, P5, P6, P7 are low level sensitive interrupts and NMI, P0, P1, P2, P3 are falling edge sensitive.

\* The EI (enable interrupt) register is an 8-bit wide enable interrupt register. It controls the following interrupt sources: Mailbox, INT, P Port (see figure 4).

**Figure 4**: ST18940/41 Enable Interrupt Register XEI, REI part of SSR Register (see page 21).

- \* Software interrupt can be implemented using P-Port.

- \* When an interrupt is acknowledged, the current program counter is pushed on the stack and the interrupt vector corresponding to the interrupt source (see table 1) is loaded into the program counter (PC). Upon completion of interrupt routine, a RTI (re-

turn from interrupt) instruction is processed. The content of the top location in the stack is popped into the PC.

Table 1 : Interrupt Vectors.

| Address | Interrupt Sources           |

|---------|-----------------------------|

| 0       | RESET                       |

| 1       | INT                         |

| 2       | R INT (serial I/O receive)  |

| 3       | X INT (serial I/O Transmit) |

| 4       | B INT (mailbox)             |

| 5       | P4, P5, P6, P7              |

| 6       | P0                          |

| 7       | P1                          |

| 8       | P2                          |

| 9       | P3                          |

| 10      | NMI (ST18941 only)          |

#### 4.3. DATA ARITHMETIC UNIT (figure 5)

One of the most useful features of the ST18940-41 is to provide the user with three operating modes which can be dynamically set by software.

These three modes represent different data types :

- -REAL 16-bit data

- -Complex (CPLX) 16-bit real + 16-bit imaginary data

- -Double-precision (DBPR) 32-bit data.

In double precision mode, data moves from and to memories are performed on 32 bits. This is especially useful in adaptive processing to keep track of L.S.B. updated coefficients.

Thus the DSP is seen by the user as a standard 16-bit real or complex machine or a 32-bit real machine. All operating units are automatically adjusted by the processor to the right length.

In all modes, the number representation used is siqued 2's complement.

- 4.3.1. MULTIPLIER. In real and double-precision modes, the multiplier executes a 16x16-bit —> 32-bit signed or unsigned multiplication every instruction cycle.

- -The operands are loaded into the M and N registers and the result of a previous multiplication is written in the P register during the same cycle.

-In complex mode the multiplier executes a complex multiplication every instruction cycle (2 x machine cycles) ie :

$(a + jb) \times (c + jd) = (ac - bd) + j(ad + bc).$ In this case the registers M and N are  $2 \times 16$ -bit and the P register is  $2 \times 32$ -bit.

-The pipeline structure makes the multiplication result available 2 instruction cycles later in all 3 modes. The status bits relating to the multiplier are in STA (Status register) and the multiplier overflow (complex mode only) is updated in the Code Condition Register.

4.3.2. 32-Bit ALU/ACCUMULATOR. The 32-bit ALU is loaded on the right side by the R bus, by the RBD register or by the accumulators (A, B). On the left side, the operands always access the ALU through the barrel shifter, coming either from the L (left) bus or from the multiplier output register P.

The result of an ALU operation is automatically written in the D register and, if required, into the accu-

mulators or FIFO.

The ALU performs 32 different operations. These include the usual arithmetic, logical and shift operations e.g. ADD, SUB and AND. Additional special operations are also implemented. These include ADDS or SUBS (addition and subtraction with automatic prescaling of the left-side ALU input), and AB-Solute value and EDGE operations (used for first significant bit detection and exponent adjustment).

The complete list of ALU codes and description is given in table 2 - p 27.

4.3.3. BARREL SHIFTER. The 32-bit barrel shifter located on the left side of the ALU performs all logic/arithmetic shifts and rotations. The shift value comes from the ALU code or from the BSC (Barrel Shift Control) register loaded by the Z bus. This feature combined with EDGE (Alu Code) allows easy, efficient and dynamic normalization used in floating point and dynamic scaling operations.

Figure 5 : Data Arithmetic Unit Block Diagram.

\* See Note Page 15/58.

## 4.3.4. PROGRAMMING MODEL

| Name   | Function                                           | Description                                                                                                                        |

|--------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| М      | 16 - Bit Register<br>2x16 - Bit (complex mode)     | Left side operand of multiplier loaded via L bus.                                                                                  |

| N      | 16 - Bit Register<br>2x16 - Bit (complex mode)     | Right side operand of multiplier loaded via R bus.                                                                                 |

| Р      | 32 - Bit Register<br>2x32 - Bit Register (complex) | Multiplication Result                                                                                                              |

| D      | 32 - Bit Register                                  | ALU Result .                                                                                                                       |

| A1, A2 | 2x32 - Bit Registers                               | Accumulators A1 and A2 are selected by ACS bit 2 of STA register in real and double precision modes.                               |

| B1, B2 | 2x32 - Bit Registers                               | Accumulators B1 and B2 are selected by ACS bit 2 of STA register in real and double precision modes.                               |

| FIFO   | 4x32 - Bit Registers                               | FIFO loaded by ALU.                                                                                                                |

| Т      | 2x24 - Bit Registers                               | Bidirectional register between L bus and Z bus.                                                                                    |

| RBD    | 2x16 - Bit Registers                               | Right bus delay, this register is used as a buffer on the ALU right side.                                                          |

| STA    | 16 - Bit Register                                  | Status register defining the state of the data arithmetic unit.                                                                    |

| CCR    | 16 - Bit Register                                  | Condition code register containing the flags generated by the data arithmetic unit. Every bit can be tested as a branch condition. |

| RC     | 7 - Bit Register                                   | This register, directly connected to the ALU control unit, can be dynamically loaded by the L bus.                                 |

| BSC    | 5 - Bit Register                                   | Barrel shift control register is loaded by the Z bus and contains the shift value for the barrel shifter.                          |

## **CONDITION CODE REGISTER (CCR)**

| Name | Bit # | Function                                                                                                                                                                             | Description                                                                                                                                               |

|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| SR   | 15    | Sign Real Set if the MSB of the ALU result is 1. Cleared Otherwis                                                                                                                    |                                                                                                                                                           |

| SI   | 14    | Sign Imaginary                                                                                                                                                                       | Set if the MSB of the ALU imaginary result is 1 (in complex mode). Cleared Otherwise.                                                                     |

| CR   | 13    | Carry Real                                                                                                                                                                           | Set if carry is generated out of the MSB of the result for arithmetic and shift operations. Cleared Otherwise.                                            |

| CI   | 12    | Carry Imaginary                                                                                                                                                                      | Set if a carry is generated out of the MSB of the imaginary part of the result for complex arithmetic and shift operations. Cleared Otherwise.            |

| Z    | 11    | Zero                                                                                                                                                                                 | Set if the ALU result equals zero. In complex mode it is set if both real and imaginary parts are equal to zero.                                          |

| OVF  | 10    | Overflow  Set if an arithmetic overflow occurs. This implies that result cannot be represented in the operand size. In a mode it is set for an overflow of either the real or image. |                                                                                                                                                           |

| MOVE | 09    | Memorized Overflow Set under the same conditions as overflow. Cleared tested by a branch instruction.                                                                                |                                                                                                                                                           |

| AOVF | 08    | Advanced Overflow                                                                                                                                                                    | Exclusive OR of bits 30 and 31 of the ALU. Set and memorized if arithmetic overflow occurs on half capacity. Cleared when tested by a branch instruction. |

| OVFM | 07    | Overflow Multiplier                                                                                                                                                                  | Set and memorized if the multiplier has overflowed in complex mode. Cleared by LCCR ALU instruction.                                                      |

| EF   | 06    | Empty FIFO                                                                                                                                                                           | Set if FIFO is empty. Cleared Otherwise.                                                                                                                  |

| -    | 05→00 |                                                                                                                                                                                      | Reserved                                                                                                                                                  |

## **STATUS REGISTER (STA)**

| Name | Bit # | Function                  | Description                               |

|------|-------|---------------------------|-------------------------------------------|

| EPI  | 15    | Enable Imaginary Product  | Imaginary product enable under interrupt. |

| EPR  | 14    | Enable Real Product       | Real product enable under interrupt.      |

| SE   | 13    | Smallest Exponent         | Conditional Load of BSC                   |

|      | 12    | Reserved                  |                                           |

|      | 11    | Reserved                  |                                           |

|      | 10    | Reserved                  |                                           |

| MODE | 09/08 |                           | Real /CPLX/DBPR                           |

| EMI  | 07    | Enable Multiplier Input   | Multiplier enable under interrupt.        |

| тсм  | 06    | Two's Complement M        | M signed/unsigned.                        |

| TCN  | 05    | Two's Complement N        | N signed/unsigned.                        |

| CPR  | 04    | Conjugate Product Result  | M x N conjugate.                          |

| SAT  | 03    | SATuration                | ALU Saturation                            |

| ACS  | 02    | ACcumultator Selection    | A1 or A2 and B1 or B2                     |

| FORM | 01    | FORMat * see note 1.      | 24 MSB/16 LSB Selection                   |

| RBDS | 00    | Right Bus Delay Selection | RBD Register Selection                    |

Note: The data buses and the T register are 24 bits wide enabling 24-bit wide ALU results to be fed back to the left ALU input.

## 4.4. DATA STORAGE UNIT (figure 6)

The ST18940/41 provides four different data memories within two categories: the data memories and the coefficient memory. The coefficient memory in the ST18940 is a 512 x 16-bit masked ROM (CROM). For emulation of the ST18940 CROM, a 128x16 internal CRAM is provided in addition to the external 512x16 CRAM. Internal CRAM is usefull when coefficients are to be used in conjunction with external data in the same instruction. For both versions the internal data memories consist of two 256x16 bit RAM's denoted XRAM and YRAM. The external addressing space is of size 64k x 16-bit (ERAM) and is accessible via the local bus using a single instruction as for the internal memories.

Each memory is controlled by a dedicated Address Calculation Unit called XACU for the XRAM, YACU for the YRAM, CACU for the CRAM or CROM and EACU for the ERAM.

- 4.4.1. ADDRESSING MODES. The addresses are generated by each ACU according to the four addressing modes:

- Immediate addressing : the data is in the instruction

- Direct addressing :

- the address is in the instruction

- Indirect addressing :

the address is in one of the ACU registers

- Circular addressing : also called virtual shift mode Bit reversed mode

- 4.4.2. ADDRESS CALCULATION UNITS (ACU). The dedicated ACU's are independent and contain 7 registers: two banks of dual pointers selected by a bit in the ASTA register, one current pointer used in the circular addressing mode, and, two post-incrementing/decrementing registers. The register structure of XACU is given below:

X0A, X1A: dual pointer bank A X0B, X1B: dual pointer bank B

X2: current pointer in circular addressing

K, L: two post-incrementing/decrementing registers

The CACU is the only ACU with a single pointer bank.

The circular addressing mode uses the A bank pointer for the minimum and maximum limits and the curent pointer for the current address.

Each ACU (with the exception of CACU) supports bit reversed addressing as required for the FFT algorithms.

For the external data memory in direct addressing mode, the 16-bit address is obtained by concatenating the 13 bits contained in the instruction (LSB) to the 3 bits of the page register (MSB).

Figure 6: ST18940/41 - Data Memories Block Diagram.

SGS-THOMSON MICROELECTROMICS

17/50

## 4.4.3. ASTA REGISTER - ADDRESS STATUS REGISTER

| Name             | Bit # | Function                        | Description                                       |  |  |

|------------------|-------|---------------------------------|---------------------------------------------------|--|--|

| RBX              | 15    | Register Bank Selection RAMX    |                                                   |  |  |

| RBY              | 14    | Register Bank Selection RAMY    | Select Bank A or B                                |  |  |

| RBE              | 13    | Register Bank Selection<br>ERAM | for X, Y or ERAM                                  |  |  |

|                  | 12    |                                 | Reserved.                                         |  |  |

| EC               | 11    | External Coefficient            | ST18941 only, Internal or External CRAM Selection |  |  |

| BRX              | 10    | Bit reversed RAMX.              |                                                   |  |  |

| BRY              | 09    | Bit reversed RAMY.              | Set bit reversed mode.                            |  |  |

| BRE              | 08    | Bit reversed ERAM.              |                                                   |  |  |

| хc               | 07    | Circular RAMX                   |                                                   |  |  |

| Y <sub>.</sub> C | 06    | Circular RAMY                   | Set circular addressing mode.                     |  |  |

| E <sub>C</sub>   | 05    | Circular ERAM                   | Co. Gilbara addiscoming meta-                     |  |  |

| c <sup>-</sup> c | 04    | Circular CROM                   |                                                   |  |  |

| ADOFX            | 03    | ADOF RAMX                       |                                                   |  |  |

| ADOFY            | 02    | ADOF RAMY                       | Force the 1st address in complex or double.       |  |  |

| ADOFE            | 01    | ADOF ERAM                       | Precision mode to be odd or even.                 |  |  |

| ADOFC            | 00    | ADOF CROM                       |                                                   |  |  |

#### 4.5. INPUT/OUTPUT

The ST18940/41 provides four I/O interfaces:

- -the system bus

- -the local bus

- -the parallel port

- -the serial interface

- 4.5.1. THE SYSTEM BUS. For asynchronous exchanges between the ST18940/41 and a host (general purpose MCU and/or other ST18940/41 processors), the ST18940/41 is provided with a "mailbox mechanism" comprising a double 16-byte FIFO, one for input (RIN), one for output (ROUT).

A 6-bit status register MBS is accessible to both the ST18940/41 and the host. Internally RIN is connected to the L bus and ROUT to the Z bus. Externally SD0-SD7 gives access to RIN and ROUT.

The CS input selects the mail box (RIN, ROUT, MBS) in the host system addressing space while the RS input selects RIN-ROUT or MBS. The (SR/W, SWR) and (SDS, SRD) inputs synchronize and control the exchanges on the system bus. These signals are programmable (AMR bit 7) in order to be directly compatible with MOTOROLA or INTEL hosts.

#### MBS REGISTER: MAILBOX STATUS REGISTER (6-BIT - R/W)

| Name | Bit # | Function                 | Description                                                          |

|------|-------|--------------------------|----------------------------------------------------------------------|

| RIE  | 5     | Register Input Empty     | Input FIFO Empty                                                     |

| RIF  | 4     | Register Input Full      | Input FIFO Full                                                      |

| RISH | 3     | Register Input DSP/host  | Input to processor/host indicates to which input mailbox belongs to. |

| ROE  | 2     | Register Output Empty    | Output FIFO Empty                                                    |

| ROF  | 1     | Register Output Full     | Output FIFO Full                                                     |

| ROSH | 0     | Register Output DSP/host | Output to processor/host indicates to which mailbox belongs to       |

Figure 7: Input/output Functions.

4.5.2. LOCAL BUS. On this 16-bit bus (16-bit data, 16-bit address) the ST18940/41 can access external memories or peripherals. To access slow devices, the DSP can stretch its external memory cycle by the insertion of wait states. This can be achieved using either of the two following methods:

-Hardware mechanism: the external memory or peripherals generates a DTACK pulse to signal the end of the exchange

-Programmable multicycle exchanges: the exchange lasts for the number of cycles programmed by the ESO and ES1 bits of the Access Mode Register. Easy implementation of multiprocessor application using the local bus is allowed by mean of the HOLD function. External devices can take control of the local bus by using the HOLD and HOLDA pins.

## -AMR REGISTER: ACCESS MODE REGISTER (8 - BIT, R/W)

| Name         | Bit # | Functions                                                                                    | Description                                                                                                                                                                    |

|--------------|-------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/M          | 7     | Intel/MOTOROLA Format<br>System Bus                                                          | Must be set according to the host control : $(\overline{RD}, \overline{WR})$ or $(\overline{SDS}, \overline{SW/R})$                                                            |

| MASK         | 6     |                                                                                              | When this bit is set, an interrupt will reset the AMR bits: ES0, ES1, DTACKEN, CSS0, CSS1 (at the end of the interrupt routine, previous AMR state is automatically restored). |

| DPIF         | 5     | Dual Purpose Interface                                                                       | DPI Function Selection (serial I/O or DMA)                                                                                                                                     |

| CSS1<br>CSS0 | 4 3   | Control Signal Selection Select one of the three possible sets of control signals local bus. |                                                                                                                                                                                |

| DTACKEN      | 2     | DTACK Enable                                                                                 | DTACK Validation                                                                                                                                                               |

| ES1          | 1     |                                                                                              | Exchange speed (1 to 4 cycles)                                                                                                                                                 |

| ES0          | 0     |                                                                                              |                                                                                                                                                                                |

4.5.3. PARALLEL INTERFACE. The P port is a general purpose 8-bit port, where each bit is programmable as input or as output by means of the DDR 8-bit register. In addition each bit can be used as an interrupt source. Four bits (P0-P3) are edge sensitive and four bits (P4-P7) are level sensitive.

4.5.4. DMA CHANNEL. The DMA channel controls transparent exchanges on the local bus between internal XRAM, YRAM or ERAM and an external device.

Single and burst modes are provided. In single mode, the exchange is <u>processed</u> word by word and synchronized by the DMARQ signal (edge sensitive). In burst mode, the exchange is carried out on a block basis with the number of words to be transferred stored in CDMA (13-bit register). In this case the DMARQ is level sensitive and the end of the exchange is indicated by the assertion of the DMAEND signal. The DMA channel is accessed through four pins of DPI port (Dual Purpose interface) and is programmed by the three following registers:

#### -SDMA REGISTER: STATUS DMA (6 - BIT-R/W)

| Name  | Bit # | Functions | Description            |

|-------|-------|-----------|------------------------|

| DMEND | 5     |           | End of DMA             |

| O/I   | 4     |           | DMA as Input or Output |

| E     | 3     |           | DMA with ERAM          |

| Υ     | 2     |           | DMA with YRAM          |

| x     | 1     |           | DMA with XRAM          |

| B/S   | 0     |           | Burst/single Mode      |

ADMA Register (13-bit-R/W) : contains the DMA address

TDMA Register (16-bit-R/W) : DMA data buffer

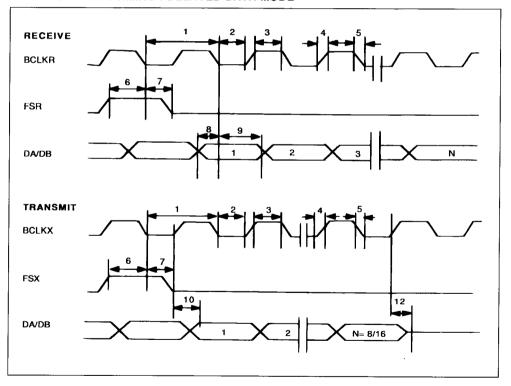

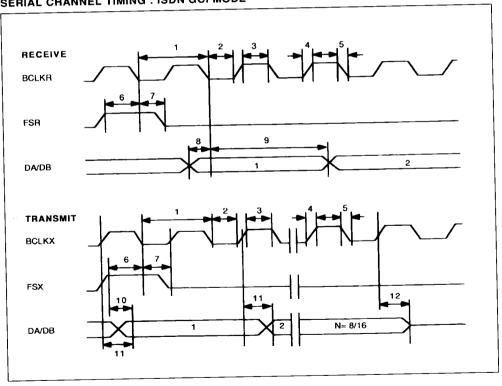

4.5.5. SERIAL I/O. This serial port provides 2 bidirectional lines DA and DB programmable as input or output to give access to the receive or to the transmit part of the port.

Four pins are dedicated to clock and synchronization:

- -BCLKX and BCLKR: Transmit and Receive Clocks Frequency equals to single or double the data rate.

- -FSX and FSR: Frame synchro pulse.

These four signals can be internally or externally generated.

- -Transmitted and received words can be programmed to 8 or to 16 bits (XWL-RWL).

- -In one frame several words can be transmitted or received. XS0-XS5 (resp. RS0-RS5) indicate the starting time slot for the transmit (resp. receive) part, XE0-XE5 (resp. RE0-RE5) indicate the ending time slot for the transmit (resp. receive) part.

- -The serial port shares 4 pins with the DMA channel controller.

- -Direct interfacing with serial devices (such as CO-DEC, ISDN...) is provided.

- -SIN Serial Input Register (8 16-bit Read)

- -SOUT Serial output Register (8 16-bit Write).

#### SSR - SERIAL STATUS REGISTER (16-bit - R/W)

| Name | Bit # | Functions                         |

|------|-------|-----------------------------------|

| XEI  | 15    | Transmit - Interrupt Enable       |

| XRE  | 14    | Transmit - Interrupt (SOUT empty) |

| XER  | 13    | Transmit - Underspeed Error       |

| XEN  | 12    | Transmit - Enable                 |

| XWL  | 11    | Transmit - Word Length (8 or 16)  |

| XF   | 10    | Transmit - Frequency              |

| XDL  | 09    | Transmit - Delay Synchro          |

| xcs  | 08    | Transmit - Internal Clock         |

| REI  | 07    | Receive - Interrupt Enable        |

| RRF  | 06    | Receive - Interrupt (SIN full)    |

| RER  | 05    | Receive - Overspeed Error         |

| REN  | 04    | Receive - Enable                  |

| RWL  | 03    | Receive - World Length (8 or 16)  |

| RF   | 02    | Receive - Frequency               |

| RDL  | 01    | Receive - Delay Synchro           |

| RCS  | 00    | Receive - External Clock          |

#### XCR - TRANSMIT CONTROL REGISTER (15-bit - R/W)

| Name    | Bit # | Functions                     |

|---------|-------|-------------------------------|

| XZ      | 14    | Level 1 High Impedance        |

| XV      | 13    | Output Buffer Enable          |

| X A/B   | 12    | Transmit on DA or DB          |

| XEO-XE5 | 06-11 | Time Slot # End of Transmit   |

| XSO-XS5 | 00-05 | Time Slot # Start of Transmit |

#### RCR - RECEIVE CONTROL REGISTER (13-bit - R/W)

| Name    | Bit # | Functions                    |  |

|---------|-------|------------------------------|--|

| R A/B   | 12    | Receive on DA or DB          |  |

| REO-RE5 | 06-11 | Time Slot # End of Receive   |  |

| RSO-RS5 | 00-05 | Time Slot # Start of Receive |  |

#### CRC - CLOCK CONTROL REGISTER(16-bit - R/W)

| Name     | Bit # | Functions                     |  |

|----------|-------|-------------------------------|--|

| Reserved | 15    | Reserved                      |  |

| T0-T5    | 09-14 | Frame Synchro Frequency       |  |

| PSC      | 08    | Prescaler 1/8                 |  |

| CDO-CD7  | 00-07 | Internal Clock Division Range |  |

## 5. SYSTEM CONFIGURATIONS

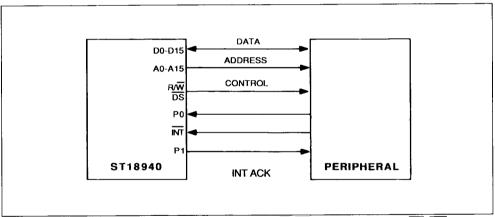

# 5.1. MINIMUM APPLICATION (ST18940 + peripherals)

The ST18940/41 input/output architecture has been designed to support a wide variety of peripherals types, speeds, and organizations without the use of

additional circuit chips (glue chip). A minimum application consists of one processor connected to one peripheral.

The following examples show the method to interface several types of peripherals with the ST18940.

#### 5.1.1. PERIPHERAL ON LOCAL BUS.

The peripheral can be A/D converter, parallel CO-DEC...

Exchange can be initialized by interrupt or polling (branch condition).

<sup>\* (</sup>R/ $\overline{W}$ ,  $\overline{DS}$ ) can be changed to ( $\overline{RD}$ ,  $\overline{WR}$ ) signals.

## 5.1.2. PERIPHERAL ON DMA CHANNEL, DPI PORT.

5.1.3. PERIPHERAL ON SERIAL PORT (TYPICAL APPLICATION - SERIAL CODEC)

Several peripherals can be connected, assuming they use different time - slots (up to 64)

## 5.1.4. PERIPHERAL ON PARALLEL PORT.

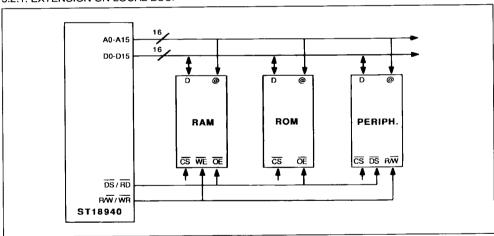

#### 5.2. BUS EXTENSION

The external double-bus architecture is well suited for connections to memory extensions or to a host computer. The system bus/mailbox is intended for

communication with other procesors while the local bus is designed for flexible straightforward memory extension interfacing.

#### 5.2.1. EXTENSION ON LOCAL BUS.

#### 5.2.2. HOST PROCESSOR INTERFACE ON SYSTEM BUS.

<sup>\* (</sup>SDS, SR/W) can be changed to (SRS, SWR) signals.

# 5.3. SPECIFIC APPLICATION WITH ST18941 (ROMLESS VERSION)

The ST18941 (open version) provides a dedicated

PROGRAM MEMORY INTERFACE

bus to access 64K x 32-bit of external program memory without any additional logical glue.

#### 6. SOFTWARE

#### 6.1. INSTRUCTION FORMAT

The instruction set is divided into 5 instruction types:

\* calculation instruction : OPIM with immediate addressing

OPIN with indirect addressing

OPDI with direct addressing

\* shift instruction : SHIFT with direct addressing \* transfer instruction : TFR with direct addressing

\* transfer instruction : IFR with direct addressing

\* branch instruction : BRI Immediate branch

BRC Computed branch

\* Initialization instruction : PINI Pointer initialization RINI Register initialization

By virtue of the parallel architecture, each instruction controls a number of concurrent operations. The instruction format is divided into a number of fields, which can be used to specify source and destination and operation type for the 4 resources: Zbus, Lbus, Rbus and ALU.

Typical instruction format:

<instr. mnemonioc>, <Z bus field>, < bus field>,

<bus field>,

Typical field:

<mnemonic>, and < sources>.

and <destinations>

All instructions (except control instructions) are executed in 1 machine cycle (100ns) in REAL mode. All instructions are executed in 2 machine cycles (200ns) in complex and double-precision modes.

In all three modes, every instruction occupies 1 single word (32-bit) of program memory.

#### 6.2. INSTRUCTION SET

6.2.1. ALU CODES. The ALU code is used with calculation instructions (section 6.3.2). Enhanced shift

operations are available with the shift instruction (section 6.3.3).

Table 2: List of Alu Codes

| Туре          | Mnemonic                                               | Function                                                                                                                                                                                         |

|---------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADD           | ADD<br>ADDC<br>ADDS<br>ADDX                            | Addition Addition with Carry Addition with L side operand shifted by N bits. Add the complex conjugate of L-side.                                                                                |

| SUB           | SBC<br>SBCR<br>SUB<br>SUBR<br>SUBS                     | Substract with Carry Reversed substract with carry (Rside - Lside). Substract Lside - Rside Substract R side - L side Substract with L side operand shifted by N bits.                           |

| LOGIC         | AND<br>COM L or R<br>XOR<br>OR                         | Logical AND Complement R side or L side Exclusive OR Inclusive OR                                                                                                                                |

| SHIFT         | ASL<br>ASR<br>LSL<br>LSLB<br>LSR<br>LSRB<br>ROR        | Arithmetic Shift Left Arithmetic Shift Right Logical Shift Left Logical Shift Left of 8 Positions Logical Shift Right Logical Shift Right Rogical Shift Right Rogical Shift Right of 8 Positions |

| RC            | RCE<br>RCER<br>RCR                                     | Execute RC Execute and replace RC. Load RC                                                                                                                                                       |

| MISCELLANEOUS | ABS<br>CLR<br>NOP<br>SET<br>LCCR<br>TRA L or R<br>EDGE | Absolute Value Clear no Operation Set to One Load L Bus into CCR Register Transfer operation from L side or R side. Edge Transition for Binary Point Detection                                   |

6.2.2. CALCULATION INSTRUCTION. The three instruction types OPIM, OPDI, OPIN have the same structure but differ in terms of addressing mode. OPIM is for use with immediate addressing on R source operands. OPDI is for use with direct addressing on L source operands. OPIN is for use with indirect addressing on all operands. With the exception of some shift operations, the calculation

instructions are the only instructions providing access to the ALU codes.

Instruction structures are given below for each class.

Detailed information is provided in the user's manual and in the programming reference card.

|      | Z Field |          | L Field  |       | R Field  |       | ALU<br>Code |

|------|---------|----------|----------|-------|----------|-------|-------------|

| OPIN | Source  | Dest.    | Source   | Dest. | Source   | Dest. | Source      |

|      | (1)     | Indirect | Indirect | (2)   | Indirect | (2)   | Dest.       |

Most of the typical DSP algorithms are implemented on the ST18940-41 system using OPIN class instructions.

|      |        | Z Field L Fie   |        | ield R.F. |          | ield  | ALU            |

|------|--------|-----------------|--------|-----------|----------|-------|----------------|

| OPDI | Source | Dest.           | Source | Dest.     | Source   | Dest. | Code<br>Source |

| OFBI | (1)    | Indirect Direct | Direct | (2)       | Indirect | (2)   | Dest.          |

| OPIM | Z Field            | L Field  |       | R Field |       | ALU<br>Code |

|------|--------------------|----------|-------|---------|-------|-------------|

|      | NOT                | Source   | Dest. | Source  | Dest. | Source      |

|      | NOT –<br>AVAILABLE | Indirect | (2)   | Value   | (2)   | Dest.       |

<sup>(1)</sup> Sources of the Z field are typically selected from the set of options: ALU output (D register), accumulators A1, B1, A2, B2 and FIFO.

(2) Destinations of the Lbus and Rbus are typically the multiplier input registers and the ALU inputs (which are not latched).

6.2.3. SHIFT INSTRUCTIONS. The shift instruction

grammable shift values.

| SHIFT SHIFT CODE VALUE |       | LE     | Bus   | Z Bus  |          |

|------------------------|-------|--------|-------|--------|----------|

|                        |       | Source | DEST. | Source | DEST.    |

|                        | VALUE | Direct | (2)   | (1)    | Indirect |

6.2.4. TRANSFER INSTRUCTION. The transfer instruction TFR is used to move data through the Z

bus. All internal registers can be accessed in read and write through the Z bus.

|     |          | Z Bus         |               |

|-----|----------|---------------|---------------|

| TFR | Source   | DESTINATION 1 | DESTINATION 2 |

|     | Register | Register      | Direct        |

6.2.5. BRANCH INSTRUCTION. The branch address for conditional branch operations may be immediate or computed. In the latter case the new PC value may be loaded from accumulators A, B, FIFO

or the T register. Twenty three conditions can be tested (Condition Code Register, mailbox and DMA flags, and PPORT).

| BRANCH | Branch     | Branch Address  | PC Save Operations<br>Z Bus |             |  |

|--------|------------|-----------------|-----------------------------|-------------|--|

|        |            | Immediate<br>or | Source                      | DESTINATION |  |

|        | Conditions | Computed        | PC                          | Indirect    |  |

The "PC save" field allows stack extension in data memory (either internal or external) with a minimum execution time overhead.

# 6.2.6. INITIALIZATION INSTRUCTIONS. The PINI instruction is used for pointer initialization.

In addition to mode setting, PINI instruction provides initialization of 2 address pointers in one cycle.

|      |      | Fiel               | d 1                        | Fie                | ld 2                       |

|------|------|--------------------|----------------------------|--------------------|----------------------------|

| PINI | Mode | Immediate<br>Value | Register<br>or<br>Resource | Immediate<br>Value | Register<br>or<br>Resource |

The RINI instruction is used to initialize index address registers. DMA registers, loop counters as

well as the bits of the status (STA register).

| RINI   | Value | Register | Register |

|--------|-------|----------|----------|

| 111141 | Value | Dest. 1  | Dest. 2  |

Note: Two registers cannot be initialized in the same RINI instruction. Only one register of class 1 or 2 can be initialized within a single instruction.

#### 6.3. PROGRAMMING EXAMPLE

OPIN ST B [E0] + K; LDL [X0] + L M; LDR [Y0] - K N; ADDS P A, A\

OPIN Instruction type

ST B [E0] + K Z field : B is stored into ERAM location addressed

by E0. The next E0 value will be E0 + KE

LDL [X0] + L M L field : XRAM location addressed by X0 is trans-

ferred via the LBUS and stored in the MULTIPLIER

input M. The next X0 value will be X0 + LX

LDR [Y0] - K N R field : YRAM location addressed by Y0 is trans-

ferred via the RBUS and stored in the MULTI-PLIER input N. The next Y0 value will be Y0 - KY

ADDS PA, A ALU field : product scaled by BARREL SHIFTER

(shift value given by BSC) is added to previous va-

lue of A, result is stored into A.

## 7. ELECTRICAL SPECIFICATIONS

## 7.1. DC ABSOLUTE MAXIMUM RATINGS

| ymbol             | Parameter                   | Value        | Unit |

|-------------------|-----------------------------|--------------|------|

|                   | Supply Voltage              | - 0.3 to 7.0 | V    |

| V <sub>CC</sub> * | Input Voltage               | - 0.3 to 7.0 | V    |

|                   | Operating Temperature Range | 0 to 70      | •€   |

| T <sub>A</sub>    | Storage Temperature Range   | - 55 to 150  | _0€  |

| T <sub>stg</sub>  | Maximum Power Dissipation   | 0.8          | W    |

<sup>\*</sup>With respect to Vss.

Stresses above those hereby listed may cause permanent damage to the device. The ratings are stress ones only and functional operation of the device at these or any conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. Standard MOS circuits handling procedure should be used to avoid possible damage to the device.

## 7.2. DC ELECTRICAL CHARACTERISTICS

Conditions :  $V_{CC} \pm 10\%$ , Ambient Temperatures =  $0^{\circ}C$  to  $70^{\circ}C$

| Symbol          | Parameter                                   | Min.  | Тур. | Max.                 | Unit |

|-----------------|---------------------------------------------|-------|------|----------------------|------|

|                 | Power Supply                                | 4.5   | 5    | 5.5                  | V    |

| Vcc             | Input Low Level                             | - 0.3 |      | 0.8                  | V    |

| VIL             | Input High Level                            | 2.4   |      | V <sub>CC</sub> +0.3 | ٧    |

| V <sub>IH</sub> | Input Leakage Current                       | - 10  |      | 10                   | μΑ   |

| V <sub>OH</sub> | Output High Level (I <sub>OH</sub> = 300μA) | 2.7   |      |                      | V    |

| VOL             | Output Low Level (I <sub>OL</sub> = 2mA)    |       |      | 0.5                  | V_   |

| PD              | Power Dissipation                           |       | 0.5  |                      | W    |

## 7.3. CLOCK CHARACTERISTICS

| 7.5. 020                                         | on on a more than the second of the second o |          |      |      | Unit |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|------|------|

| Symbol                                           | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Min.     | Typ. | Max. | Unit |

| <del>-                                    </del> | Fromunnov                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5        | !    | 20   | Mhz  |

| Fx                                               | Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | 10   |      | pF   |

|                                                  | C1, C2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <u> </u> |      |      |      |

The CKLOUT frequency is half the crystal operating frequency.

## INTERNAL CLOCK OPTION

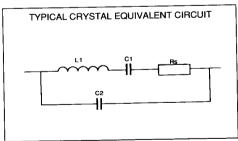

A crystal can be connected across XTAL and EXTAL functioning in the parallel resonant fundamental mode, AT – cut.

C1, C2 TYPICAL VALUE = 10 PF

TYPICAL VALUES : RS = 10 OHMS C2 = 4 PF C1 = 0.02 PF Q > 30 K

30/50

SGS-THOMSON MICROELECTRONICS

648

#### 7.4. AC MEASUREMENT CONDITIONS

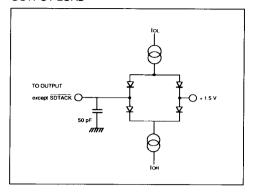

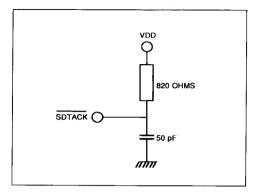

#### **OUTPUT LOAD**

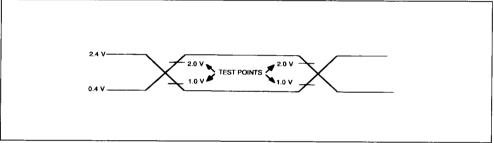

## AC TESTING INPUT, OUTPUT WAVEFORM

AC TESTING INPUTS ARE DRIVEN AT 2.4V FOR A LOGIC "1" AND 0.4V FOR A LOGIC "0".

TIMING MEASUREMENTS ARE MADE AT 2V FOR A LOGIC "1" AND AT 1.0V FOR A LOGIC "0".

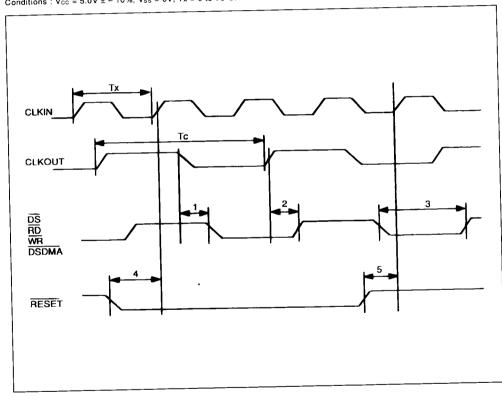

## 7.5. EXTERNAL CLOCK OPTION

|      | Parameter                   | Min.       | Тур.              | Max. | Unit |

|------|-----------------------------|------------|-------------------|------|------|

| Num. | Palameter                   | 50         |                   | 200  | ns   |