Z8038

# Z-FIO/FIFO INPUT/OUTPUT INTERFACE UNIT

#### DESCRIPTION

February 1989

The Z8038 FIO (FIFO Input/Output Interface Unit) is a 128-byte buffer that interfaces two CPUs or a CPU and a peripheral device. Multiple FIOs can be used to create a 16-bit or wider data path, or two can be connected to form a 256-byte FIFO RAM buffer.

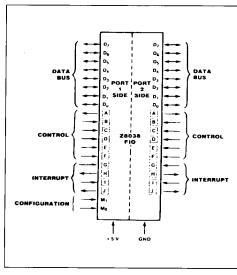

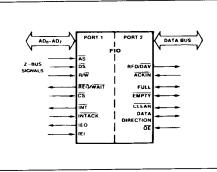

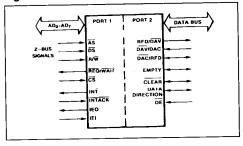

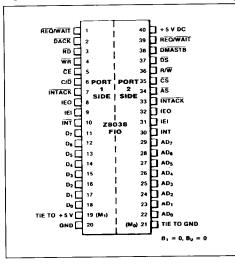

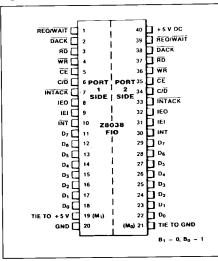

SGS-THOMSON MICROELECTRONICS

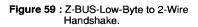

The FIO manages data transactions by assuming one of 12 operating modes, using one or more of the following signal configurations : Z-BUS<sup>TM</sup> highbyte microprocessor, Z-BUS low-byte microprocessor, non-Z-BUS microprocessor, interlocked 2-wire handshake I/O, and 3-wire handshake I/O. These configurations interface dissimilar CPUs or CPUs and peripheral devices running at different speeds or under different protocols. This allows asynchronous data transactions and byte-per-cycle DMA operation and cuts I/O overhead by as much as two orders of magnitude. Figure 1 and 2 illustrate logic functions and pin configuration.

Figure 1 : FIO Logic Functions.

#### 1/85

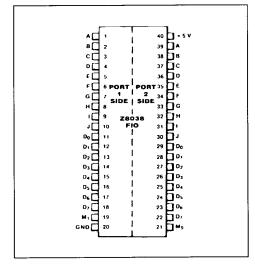

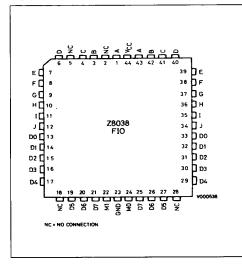

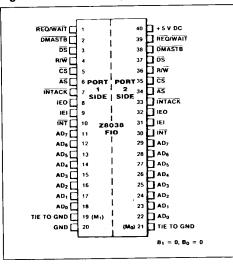

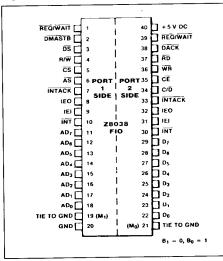

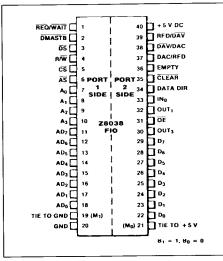

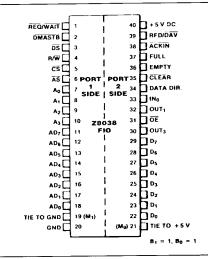

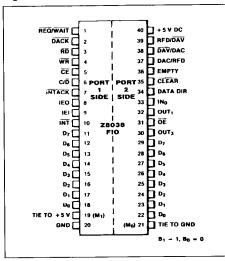

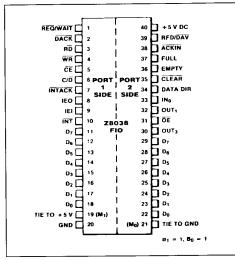

Figure 2 : Dual in Line Pin Connection.

#### ARCHITECTURAL DESCRIPTION

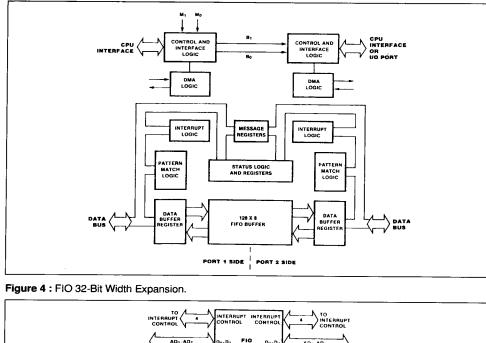

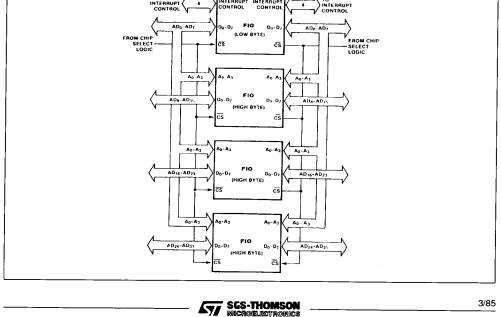

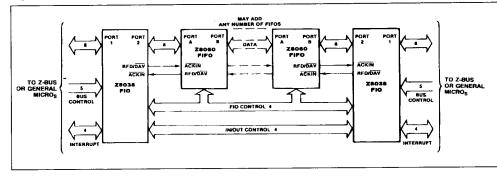

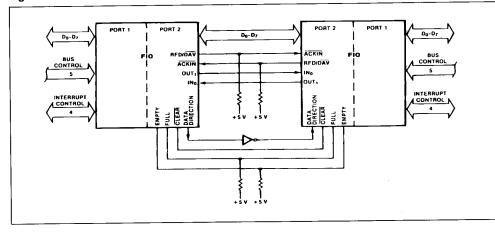

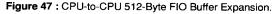

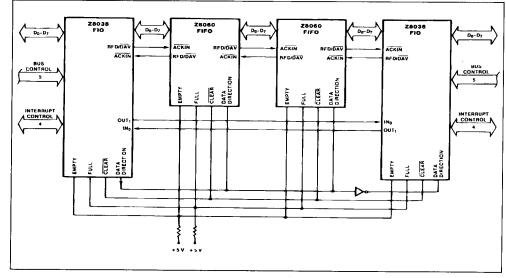

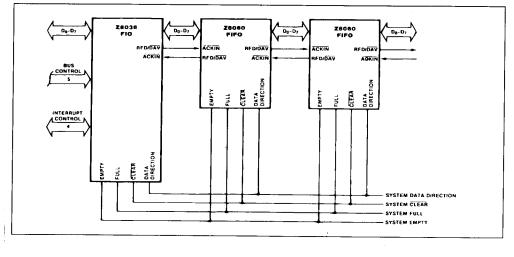

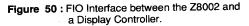

The FIO provides an asynchronous, 128-byte FIFO buffer between two CPUs or between a CPU and a peripheral device. Figure 3 shows the general architecture of the FIO. Two or more FIOs can be used in parallel to create a 16-bit or larger interface. Figure 4 shows a 32-bit interface constructed from four FIOs. Two FIOs can be combined to create 256 bytes of buffer space, and additional buffer space can be provided by adding one or more Z8060 FI-FO buffers. Figure 5 shows a 512-byte buffer constructed from two FIOs and two FIFOs. Figure 2a: Chip Carrier Pin Connection.

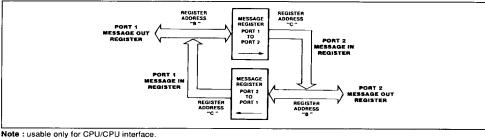

The two ports (1 and 2) are controlled through 16 programmable, directly accessible registers. These registers specify the operating mode of the FIO and provide a message register for CPU-to-CPU communication without involving the FIFO buffer.

The FIO supports DMA operation by facilitating variably-sized block transfers and data transactions to or from memory each machine cycle. Since devices can write to or read from either side of the FIO buffer asynchronously, as well as enable interrupts upon specified conditions, system I/O overhead can be significantly reduced.

# **ARCHITECTURAL DESCRIPTION** (continued)

Figure 3 : FIO Functional Block Diagram.

This Material Copyrighted By Its Respective Manufacturer

## **ARCHITECTURAL DESCRIPTION** (continued)

Figure 5 : FIO-FIFO 512-Byte Buffer Expansion.

#### FUNCTIONAL DESCRIPTION

The FIO manages data transfers by assuming one of the 12 operating modes listed in Table 1. These modes are various combinations of the five interfacing protocols.

The five interfacing protocols are Z-BUS high-byte microprocessor, Z-BUS low-byte microprocessor, non-Z-BUS microprocessor (a generalized microprocessor interface), 2-wire interlocked handshake, and 3-wire handshake. Pins A through J carry the signals used in these interfaces; Table 1-2 shows the pin assignments for each of the interfaces. Also see Appendix A for all 12 pin assignments.

Sixteen programmable registers control each port. Once the operating mode is specified, the internal registers are programmed to specify the direction of data transfer, the transfer of inter-CPU message bytes, external interrupt control, and various internal interrupt conditions.

The FIO improves I/O transaction efficiency by providing seven sources of interrupt generation. The FIO also provides an Interrupt vector that can be programmed to identify the reason for the interrupt.

| Mode | M1 | MO | B1 | BO | Port 1          | Port2           |

|------|----|----|----|----|-----------------|-----------------|

| 0    | 0  | 0  | 0  | 0  | Z-BUS Low Byte  | Z-BUS Low Byte  |

| 1    | 0  | 0  | 0  | 1  | Z-BUS Low Byte  | Non Z-BUS       |

| 2    | 0  | 0  | 1  | 0  | Z-BUS Low Byte  | 3-Wie HS        |

| 3    | 0  | 0  | 1  | 1  | Z-BUS Low Byte  | 2-Wire HS       |

| 4    | 0  | 1  | 0  | 0  | Z-BUS Low Byte  | Z-BUS High Byte |

| 5    | 0  | 1  | 0  | 1  | Z-BUS High Byte | Non Z-BUS       |

| 6    | 0  | 1  | 1  | 0  | Z-BUS High Byte | 3-Wire HS       |

| 7    | 0  | 1  | 1  | 1  | Z-BUS High Byte | 2-Wire HS       |

| 8    | 1  | 0  | 0  | 0  | Non Z-BUS       | Z-BUS Low Byte  |

| 9    | 1  | 0  | 0  | 1  | Non Z-BUS       | Non Z-BUS       |

| 10   | 1  | 0  | 1  | 0  | Non Z-BUS       | 3-Wire HS       |

| 11   | 1  | 0  | 1  | 1  | Non Z-BUS       | 2-Wire HS       |

#### Table 1 : Operating Modes.

4/85

### FUNCTIONAL DESCRIPTION (continued)

Table 2 : Pin Assignments.

|   | Z-BUS<br>Low Byte | Z-BUS<br>High Byte | Non Z-BUS | Interlocked<br>HS Port * | 3-Wire<br>HS Port * |

|---|-------------------|--------------------|-----------|--------------------------|---------------------|

| Α | REQ/WAIT          | REQ/WAIT           | REQ/WAIT  | RFD/DAV                  | RFD/DAV             |

| в | DMASTB            | DMASTB             | DACK      | ACKIN                    | DAV/DAC             |

| С | DS                | DS                 | RD        | FULL                     | DAC/RFD             |

| D | R/W               | R/W                | WR        | EMPTY                    | EMPTY               |

| Е | CS                | CS                 | CE        | CLEAR                    | CLEAR               |

| F | ĀS                | ĀS                 | C/D       | DATA DIR                 | DATA DIR            |

| G | INTACK            | Ao                 | INTACK    | IN <sub>0</sub>          | IN <sub>0</sub>     |

| Н | IEO               | A <sub>1</sub>     | IEO       | OUT1                     | OUT1                |

| I | IEI               | A <sub>2</sub>     | IEI       | ŌE                       | ŌE                  |

| J | INT               | A <sub>3</sub>     | INT       | OUT <sub>3</sub>         | OUT <sub>3</sub>    |

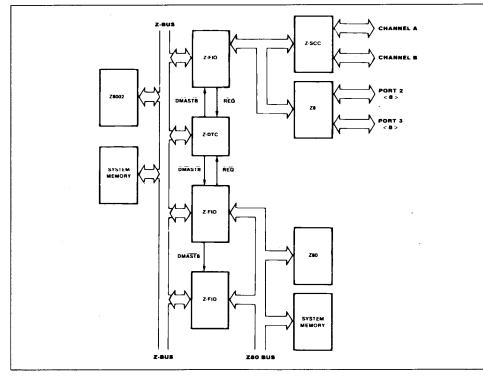

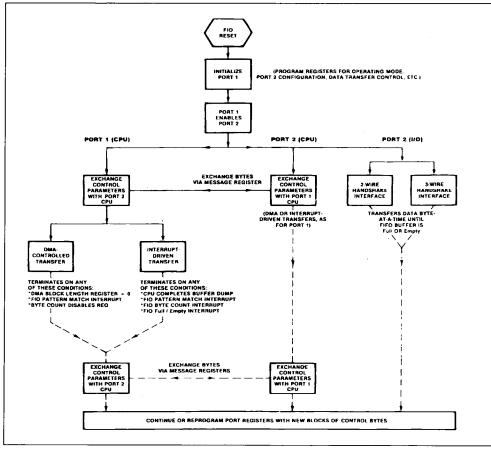

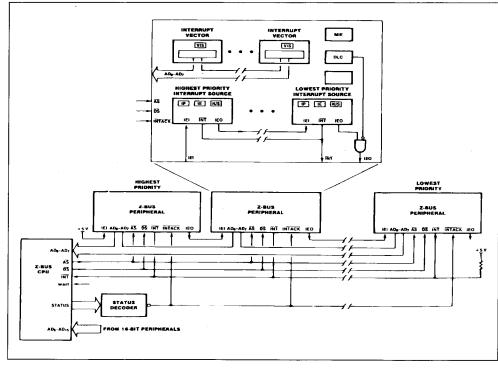

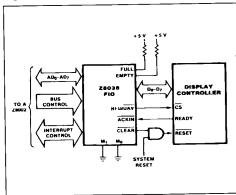

### FIO IN DISTRIBUTED NETWORKS

In typical interfacing applications, such as the distributed processing system shown in Figure 6, the Port 1 CPU (Z8002) loads a series of bytes to the FIO's Port 1 registers. This block of control information characterizes the FIO's signal configuration for a specific transaction. The Port 2 CPU can then specify Port 2 operating conventions. The Port 1 CPU remains in control, dynamically reading or writing to the Port 1 registers, either to cause a single change or to replace an entire block of control bytes as specified.

# FUNCTIONAL DESCRIPTION (continued)

Figure 6 : Using FIOs in a Distributed Network.

### ARCHITECTURAL DESCRIPTION

As figure 3 shows, the FIO architecture is organized as two sets of interface logic and registers. Once programmed, these registers define the two groups of signal lines (A-J) that provide interfacing and timing data to control data flow into and out of the FIO. Table 3 shows how control signals are mapped to these pins in each of the five interfacing protocols.

This chapter also describes the 16 registers in each side of the FIO : the Control registers, Data Buffer register, Byte Count registers, Pattern Match registers, Message registers, and the Interrupt Status registers. All registers, are directly addressable, although in certain operating modes registers must be addressed indirectly.

### **REGISTER ARCHITECTURE**

Thirty-two registers (16 for each port) control the operating modes and pin signals of the FIO. All registers are addressable and can be read from or written to, except the Byte Count and Message In registers, which are read only. All 16 registers are used by Port 1; Port 2 uses all 16 except for Control Register 2. These registers are organized into six groups that control similar functions or signals.

The control registers define the operating mode for both ports, as well as control device-level interrupts, some functional interrupts, addressing, Reset, Request/Wait, Data Direction, and Clear. The Data Buffer register buffers data into and out of the 128byte FIFO. The Byte Count registers monitor the number of bytes left in the FIFO buffer and provides a compare byte for interrupt generation when a specified value is reached during data transfers. The Pattern Mathc registers hold a bit pattern that is compared with the byte in the data buffer. If the bit patterns match, the FIO requests an interrupt. They also provide a mask byte, which forces true comparisons for any bit set. The Message registers transfer byte messages between Port 1 and Port 2 CPUs when in the CPU-to-CPU interface modes. The Interrupt Status registers control generation of interrupt requests. The following sections describe these registers in detail.

**Register Addressing Z-BUS High and Low Byte.** The Right Justify Address (RJA) bit in Control Register 0 specifies the bits used in register addressing. In the Z-BUS low-byte configuration, when RJA is 0 (the default condition), Address/Data lines AD1-AD4 carry the register address. When RJA is 1, Address/Data lines AD0-AD3 carry the register address, allowing CPUs to place a 4-bit address on the lowest nibble of the Address/Data lines. Table 4 describes FIO register addressing.

The Z-BUS high-byte configuration is normally used with another FIO in the Z-BUS low-byte configuration, forming a 16-bit interface. In this configuration, Address/Data lines AD<sub>0</sub>-AD<sub>3</sub> or AD<sub>1</sub>-AD<sub>4</sub> are wired to pins G-J, as appropriate, and the RJA bit does not affect register addressing.

| Pin                 | Pin                 | Pin     | Signal                                      |

|---------------------|---------------------|---------|---------------------------------------------|

| Signals             | Names               | Numbers | Description                                 |

| M <sub>0</sub>      | M <sub>0</sub>      | 21      | M1 and M0 Program Port 1 Side CPU Interface |

| M <sub>1</sub>      | M <sub>1</sub>      | 19      |                                             |

| + 5 V <sub>dc</sub> | + 5 V <sub>dc</sub> | 40      | DC Power Source                             |

| GND                 | GND                 | 20      | DC Power Ground                             |

#### PINS COMMON TO BOTH SIDES

7/85 369

## Table 3 : Pin Description.

### Z-BUS LOW BYTE MODE

| Pin<br>Signals                             | Pin<br>Names                   | Pin Numbers<br>Port<br>1 2 |       | Signal<br>Description                                                                                                                       |

|--------------------------------------------|--------------------------------|----------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------|

| AD <sub>0</sub> -AD <sub>7</sub>           | D <sub>0</sub> -D <sub>7</sub> | 11-18                      | 29-22 | Multiplexed Bidirectionnal Address/data Lines,<br>Z-BUS Compatible                                                                          |

| REQ/WAIT<br>(request/wait)                 | A                              | 1                          | 39    | Output, Active Low, REQUEST (ready) Line for<br>DMA Transfer ; WAIT Line (open-drain) Output for<br>Synchronized CPU and FIO Data Transfers |

| DMASTB<br>(direct memory access<br>strobe) | В                              | 2                          | 38    | Input, Active Low. Strobes DMA Data to and from the FIFO Buffer.                                                                            |

| DS<br>(data strobe)                        | С                              | 3                          | 37    | Input, Active Low. Provides timing for data transfer to or from FIO                                                                         |

| R/W<br>(read/write)                        | D                              | 4                          | 36    | Input, active High signals CPU read from FIO ;<br>Active Low signals CPU write to FIO.                                                      |

| CS<br>(chip select)                        | E                              | 5                          | 35    | Input, Active Low. Enables FIO. Latched on the Rising Edge of AS.                                                                           |

| AS<br>(address strobe)                     | F                              | 6                          | 34    | Input, Active Low. Addresses, CS and INTACK sampled while AS Low.                                                                           |

| INTACK<br>(interrupt<br>acknowledge)       | G                              | 7                          | 33    | Input, Active Low. Acknowledge an Interrupt.<br>Latched on the Rising Edge of AS.                                                           |

| IEO<br>(interrupt enable out)              | Н                              | 8                          | 32    | Output, Active High. Sends interrupt enable to<br>lower priority device IEI pin.                                                            |

| IEI<br>(interrupt enable in)               | I                              | 9                          | 31    | Input, Active High. Receives interrupt enable from<br>higher priority device IEO signal.                                                    |

| INT<br>(interrupt)                         | J                              | 10                         | 30    | Output, Open Drain, Active Low. Signals FIO interrupt request to CPU.                                                                       |

8/85 370

# Z-BUS HIGH BYTE MODE

|                                            |                                | • • • • • • • • •          |       |                                                                                                                                             |

|--------------------------------------------|--------------------------------|----------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>Signals                             | Pin<br>Names                   | Pin Numbers<br>Port<br>1 2 |       | Signal<br>Description                                                                                                                       |

| AD <sub>0</sub> -AD <sub>7</sub>           | D <sub>0</sub> -D <sub>7</sub> | 11-18                      | 29-22 | Multiplexed Bidirectionnal Address/data Lines,<br>Z-BUS Compatible                                                                          |

| REQ/WAIT<br>(request/wait)                 | A                              | 1                          | 39    | Output, Active Low, REQUEST (ready) Line for<br>DMA Transfer ; WAIT Line (open-drain) Output for<br>Synchronized CPU and FIO Data Transfers |

| DMASTB<br>(direct memory access<br>strobe) | В                              | 2                          | 38    | Input, Active Low. Strobes DMA Data to and from the FIFO Buffer.                                                                            |

| DS<br>(data strobe)                        | С                              | 3                          | 37    | Input, Active Low. Provides Tlming for Transfer of<br>Data to or from FIO.                                                                  |

| R/W<br>(read/write)                        | D                              | 4                          | 36    | Input, Active High. Signals CPU read from FIO ;<br>Active Low signals CPU write to FIO.                                                     |

| CS<br>(chip select)                        | E                              | 5                          | 35    | Input, Active Low. Enables FIO. Latched on the Rising Edge of AS.                                                                           |

| AS<br>(address strobe)                     | F                              | 6                          | 34    | Input, Active Low. Addresses, CS and INTACK are sampled while AS is Low.                                                                    |

| A <sub>0</sub><br>(address bit 0)          | G                              | 7                          | 33    | Input, Active High.With $A_1$ , $A_2$ and $A_3$ , Addresses FIO Internal Registers.                                                         |

| A <sub>1</sub><br>(address bit 1)          | Н                              | 8                          | 32    | Input, Active High. With $A_0$ , $A_2$ and $A_3$ , Addresses FIO Internal Registers.                                                        |

| A <sub>2</sub><br>(address bit 2)          | I                              | 9                          | 31    | Input, Active High. With $A_0$ , $A_1$ and $A_3$ , Addresses FIO Internal Registers.                                                        |

| A <sub>3</sub><br>(address bit 3)          | J                              | 10                         | 30    | Input, Active High. With $A_0$ , $A_1$ and $A_2$ , Addresses FIO Internal Registers.                                                        |

9/85

371

# NON-Z-BUS MODE

| Pin<br>Signals                    | Pin<br>Names                   | Pin Numbers<br>Port<br>1 2 |       | Signal<br>Description                                                                                                                       |  |  |

|-----------------------------------|--------------------------------|----------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| D <sub>0</sub> -D <sub>7</sub>    | D <sub>0</sub> -D <sub>7</sub> | 11-18                      | 29-22 | Bidirectional Data Bus                                                                                                                      |  |  |

| REQ/WT<br>(request/wait)          | A                              | 1                          | 39    | Output, Active Low, REQUEST (ready) Line for<br>DMA Transfer ; WAIT Line (open-drain) Output for<br>Synchronized CPU and FIO Data Transfer. |  |  |

| DACK<br>(DMA acknowledge)         | В                              | 2                          | 38    | Input, Active Low. DMA Acknowledge                                                                                                          |  |  |

| RD<br>(read)                      | С                              | 3                          | 37    | Input, Active Low. Signals CPU read from FIO                                                                                                |  |  |

| WR<br>(write)                     | D                              | 4                          | 36    | Input, Active Low. Signals CPU write to FIO                                                                                                 |  |  |

| CE<br>(chip select)               | E                              | 5                          | 35    | Input, Active Low. Used to Select FIO                                                                                                       |  |  |

| C/D<br>(control/data)             | F                              | 6                          | 34    | Input, Active High. Identifies control byte on D0-D7 ;<br>Active low indentifies Data byte on D0-D7.                                        |  |  |

| INTACK<br>(interrupt acknowledge) | G                              | 7                          | 33    | Input, Active Low. Acknowledges an Interrupt                                                                                                |  |  |

| IEO<br>(interrupt enable out)     | Н                              | 8                          | 32    | Output, Active High. Sends interrupt enable to lower<br>priority device IEI pin.                                                            |  |  |

| IEI<br>(interrupt enable in)      | 1                              | 9                          | 31    | Input, Active High. Receives interrupt enable from<br>higher priority device IEO signal.                                                    |  |  |

| INT<br>(interrupt)                | J                              | 10                         | 30    | Output, Open Drain, Active Low. Signals FIO<br>interrupt to CPU.                                                                            |  |  |

10/85

SGS-THOMSON

This Material Copyrighted By Its Respective Manufacturer

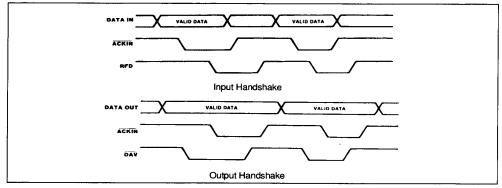

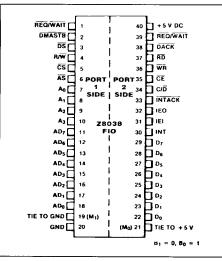

# PORT 2- I/O PORT MODE

| Pin<br>Signals                                   | Pin<br>Names                   | Pin<br>Numbers | Mode                    | Signal<br>Description                                                                                                                                                                                      |

|--------------------------------------------------|--------------------------------|----------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D <sub>0</sub> -D <sub>7</sub>                   | D <sub>0</sub> -D <sub>7</sub> | 29-22          | 2-Wire HS*<br>3-Wire HS | Bidirectional Data Bus                                                                                                                                                                                     |

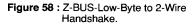

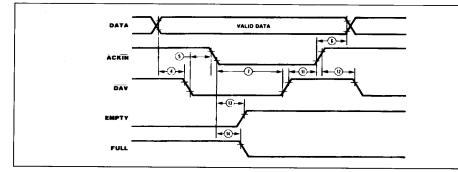

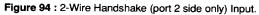

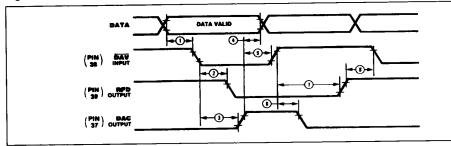

| RFD/DAV<br>(ready for<br>data/data<br>available) | A                              | 39             | 2-Wire HS<br>3-Wire HS  | Output, RFD Active High. Signals peripherals that<br>FIO is ready to receive data. DAV active low<br>signals that FIO is ready to send data to<br>peripherals.                                             |

| ACKIN<br>(acknowledge<br>input)                  | В                              | 38             | 2-Wire HS               | Input, Active Low. Signals FIO that output data is received by peripherals or that input data is valid.                                                                                                    |

| DAV/DAC<br>(data<br>available/data<br>accepted)  | В                              | 38             | 3-Wire HS               | Input ; DAV (active low) signals that data is valid<br>on bus. DAC (active high) signals that output data<br>is accepted by peripherals.                                                                   |

| FULL                                             | с                              | 37             | 2-Wire HS               | Output, Open Drain, Active High. Signals that FIO buffer is full.                                                                                                                                          |

| DAC/RFD<br>(data<br>accepted/ready<br>for data)  | С                              | 37             | 3-Wire HS               | Direction Controlled by Internal Programming. Both<br>Active High. DAC (an output) signals that FIO has<br>received data from peripheral; RFD (an input)<br>signals that the listeners are ready for data. |

| EMPTY                                            | D                              | 36             | 2-Wire HS<br>3-Wire HS  | Output, Open Drain, Active High. Signals that FIO buffer is empty.                                                                                                                                         |

| CLEAR                                            | E                              | 35             | 2-Wire HS<br>3-Wire HS  | Programmable Input or output, Active Low. Clears all Data from FIFO Buffer.                                                                                                                                |

| Data Direction                                   | F                              | 34             | 2-Wire HS<br>3-Wire HS  | Programmable Input or output. Active High Signals<br>Data Input to Port 2 ; Low Signals Data Output<br>from Port 2.                                                                                        |

| IN <sub>0</sub>                                  | G                              | 33             | 2-Wire HS<br>3-Wire HS  | Input Line to $D_0$ of Control Register 3.                                                                                                                                                                 |

| OUT <sub>i</sub>                                 | н                              | 32             | 2-Wire HS<br>3-Wire HS  | Output Line from $D_1$ of Control Register 3.                                                                                                                                                              |

| Output Enable                                    | I                              | 31             | 2-Wire HS<br>3-Wire HS  | Input Active Low. When Low, enables bus drivers.<br>When High, floats bus drivers at high impedance.                                                                                                       |

| OUT <sub>3</sub>                                 | J                              | 30             | 2-Wire HS<br>3-Wire HS  | Output Line from D <sub>3</sub> of Control Register 3.                                                                                                                                                     |

\* Handshake

11/85

Table 4 : Register Addressing.

| Non-Z-BUS                      | D7-D4              | D <sub>3</sub> | D <sub>2</sub>                     | <b>D</b> 1                         | Do          |                 |

|--------------------------------|--------------------|----------------|------------------------------------|------------------------------------|-------------|-----------------|

| Z-BUS High                     |                    | A3             | A <sub>2</sub>                     | A1                                 | A           |                 |

| Z-BUS Low RJA = 0<br>RJA = 1   | AD7-AD5<br>AD7-AD4 |                | AD <sub>3</sub><br>AD <sub>2</sub> | AD <sub>2</sub><br>AD <sub>1</sub> |             | AD <sub>0</sub> |

| Description                    |                    |                |                                    |                                    | <del></del> |                 |

| Control Register 0             | x                  | 0              | 0                                  | 0                                  | 0           | ×               |

| Control Register 1             | x                  | 0              | 0                                  | 0                                  | 1           | <u>×</u>        |

| Interrupt Status Register 0    | x                  | 0              | 0                                  | 1                                  | 0           | ×               |

| Interrupt Status Register 1    | ×                  | 0              | 0                                  | 1                                  | 1           | x               |

| Interrupt Status Register 2    | ×                  | 0              | 1                                  | 0                                  | 0           | x               |

| Interrupt Status Register 3    | ×                  | 0              | 1                                  | 0                                  | 1           | x               |

| Interrupt Vector Register      | ×                  | 0              | 1                                  | 1                                  | 0           | x               |

| Byte Count Register            | x                  | 0              | 1                                  | 1                                  | 1           | <u>×</u>        |

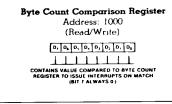

| Byte Count Comparison Register | ×                  | 1              | 0                                  | 0                                  | 0           | ×               |

| Control Register 2*            | ×                  | 1              | 0                                  | 0                                  | 1           | x               |

| Control Register 3             | ×                  | 1              | 0                                  | 1                                  | 0           | ×               |

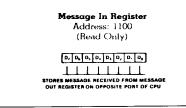

| Message Out Register           | ×                  | 1              | 0                                  | 1                                  | 11          | x               |

| Message In Register            | x                  | 1              | 1                                  | 0                                  | 0           | ×               |

| Pattern Match Register         | ×                  | 1              | 1                                  | 0                                  | 1           | x               |

| Pattern Mask Register          | ×                  | 1              | 1                                  | 1                                  | 0           | x               |

| Data Buffer Register           |                    | 1              | 1                                  | 1                                  | 1           | x               |

x = Don't Care

\* Register is only on Port 1 side

**Non-Z-BUS (Nonmultiplexed) Microprocessor.** In the non-Z-BUS microprocessor configuration, the FIO connects to the system data bus via Do-Dr but not to the address bus. The CPU must provide address information on the data bus and the FIO must distinguish between control and data bytes. The  $C\overline{D}$  line (pin F) is pulled Low to indicate that the byte on Data lines  $D_0$ - $D_7$  should go into the Data Buffer register. When the  $C/\overline{D}$  line is held High, incoming bytes are interpreted as control bytes. To write to any Control register,  $C/\overline{D}$  is forced High; the address of the destination register is written to the Register.

**Port 2 I/O Mode.** When Port 2 is programmed for either I/O Port mode, none of the Port 2 side Control registers can be programmed. The only register available is Port 2's Data Buffer register.

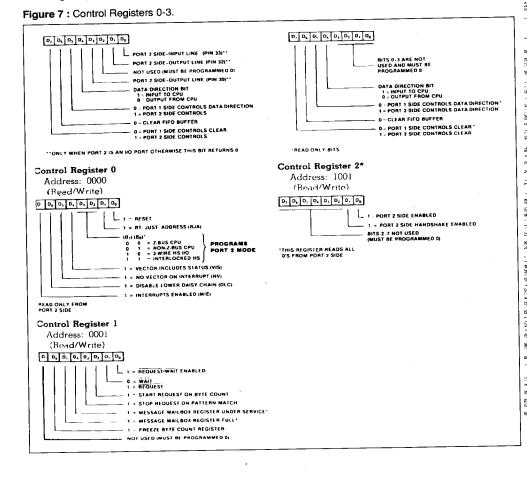

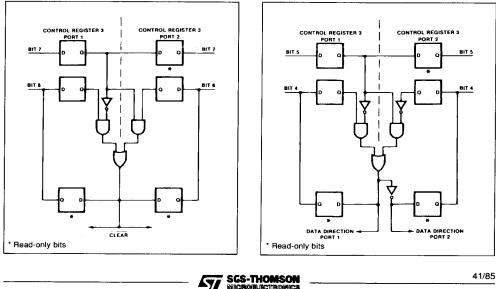

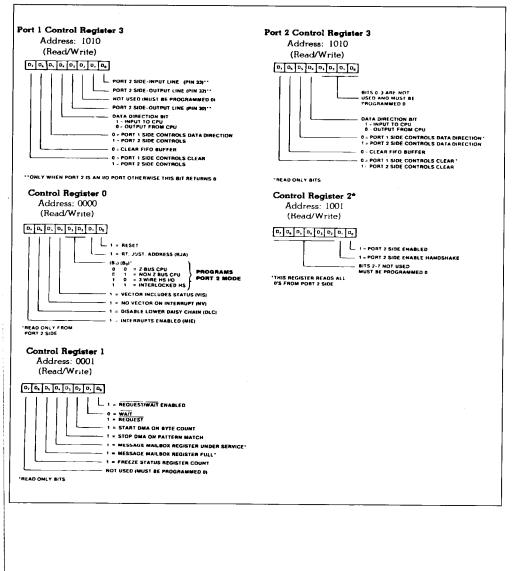

**Control Registers.** Control Registers 0-3 define FIO operation according to their programming. The Port 1 Control registers must always be programmed; the Port 2 Control registers are functional only if Port 2 is in a CPU interface mode, and not if Port 2 is in an I/O interface mode. Even when Port 2 interfaces to a CPU, the Port 2 interface is disabled unless the Port 1 CPU enables Port 2 by setting bit 0 in the Port 1 Control Register 2. Figure 7 shows the four Control registers.

Unless noted in the following descriptions, the register architectures of Port 1 and Port 2 are identical.

**Control Register 0.** Control Register 0 controls the Master Interrupt Enable, Disable Lower Daisy Chain, Nonvectored Interrupt, Vector Includes Status, Port 2 Operating Mode Select, Right Justify Address, and Reset functions. All bits except Do are grammed by a single bit, except for the Port 2 Operating Mode Select, which requires two bits to program one of four possible interfaces. When programming bits in this register, be careful not to accidentally change the Port 2 Operating Mode Control bits, B1 and B0.

If reset, bit 7 (Master Interrupt Enable) disables all interrupts from the FIO. If set, individual interrupts can be enabled by setting the appropriate IE (Interrupt Enable) bit in the Interrupt Status registers.

Bit 6 (Disable Lower Daisy Chain), if set, disables interrupt generation by devices with a lower priority on the Z-BUS interrupt daisy chain by forcing IEO Low.

Bit 5 (No Vector On Interrupt), if set, floats the data bus outputs at high impedance during an active Interrupt Acknowledge signal. The interrupt source can be identified by polling the Interrupt Status registers' Interrupt Pending bits, or by testing to find which IUS bit was set. Do not set this bit when using the nonvectored interrupt on the Z8000.

Bit 4 (Vector Includes Status), if set, codes the reason for the interrupt request into the Interrupt vector, where it can be read by the CPU.

Bits 3 and 2 program the Port 2 operating mode, as described in Table 1. In this table, bit 3 is shown as  $B_1$  and bit 2 is shown as  $B_0$ . (See also figure 7).

Bit 1 (Right Justify Address), if reset, specifies that bits 1-4 of the Address/Data bus address the internal FIO registers. This convention is compatible with the Z8001 and Z8002 byte I/O addressing modes and is the default state. When this bit is set, it specifies that bits 0-3 of the bus address the internal FIO registers. This convention supports other CPUs such as the Z8. Since the address of Control Register 0 is 00<sub>H</sub>, the setting of RJA has no effect on addressing this register in any mode. In the non-Z-BUS configurations, it is forced to 1. This bit has no effect in Z-BUS High Byte mode, since the address information comes in on pins G, H, I, and J.

Bit 0 (Reset), if set, forces the FIO into a reset state, with all Control registers cleared and all Port 2 outputs at high impedance. This bit must be reset before initialization can take place.

**Control Register 1.** As shown in figure 7, bits in Control Register 1 freeze the Byte Count register value, indicate transmitted or received messages in the Message registers, stop request transfers upon pattern match or start request on Byte Count register true match, and enable Wait/Request signals. All bits in this register are cleared by reset.

Bit 7 of Control Register 1 is not used and must be programmed to 0. This bit always reads 0.

Bit 6 (Freeze Byte Count), if set, freezes the present value in the Byte Count register so the CPU can obtain a stable value to read. Since bytes can be transferred to and from FIO RAM while such a read is in progress, the frozen value in the Byte Count register might not reflect the ongoing byte count within FIO RAM. Bit 6 is reset upon completion of the CPU read of the Byte Count register. The ongoing count appears in the Byte Count register after the read. Bit 5 (Message Register Out Full), if set, indicates that the CPU has placed a message in its Message Out register. This bit is reset when the receiving CPU reads the message in its Message In register. This bit is the other CPU's message IP bit and is a read-only bit.

Bit 4 (Message Register Interrupt Under Service), if set, indicates that the other CPU has received a message in its Message In register. This bit is the message IUS (Interrupt Under Service) bit of the other CPU and is a read-only bit.

Bit 3 (Stop Request On Pattern Match), if set, forces the request line High upon a true match between the current byte in the data buffer and the byte loaded into the Pattern Match register. DMA operation halts when the Request line is forced High.

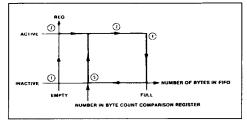

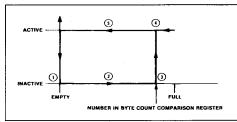

Bit 2 (Start Request On Byte Count), if set, forces the Request line Low upon a true match between the current count in the Byte Count register and the value loaded into the Byte Count Compare register. DMA operation starts when the Request line is forced Low. See figures 27 and 28 for more details.

Bit 1 (Request/Wait), if set, selects the request function for use in high-speed data transfers, such as DMA transactions. If bit 1 is reset, the Wait function is selected (and the output is open drain) for use in lower-speed data transfers and CPU synchronization.

Bit 0 (Request/Wait Enable), if set, enables the Request/Wait signals (see bit 1) during CPU-to-CPU transactions. When reset, the Request/Wait pin is at high impedance.

**Control Register 2.** Only bits 0 and 1 are used in Control Register 2 (figure 7). Bits 7 through 2 are not used and should be programmed to 0. These bits always read 0. Bits 0 and 1 are cleared by reset. Only Port 1 has a Control Register 2. When the Port 2 CPU reads its Control Register 2, it will always read  $00_{\text{H}}$ .

Bit 1 (Port 2 Side Handshake Enabled), if set, enables Port 2 I/O operation when bits 2 and 3 of Control Register 0 specify one of the I/O Handshake modes shown in Table 1. When this bit is reset, the handshake are disabled; RFD/DAV is forced High.

Bit 0 (Port 2 Enabled), if set, allows the Port 2 CPU to program the Port 2 registers-when Port 2 is programmed as a CPU interface-and to assume control of Port 2 operation. The Port 2 side is at high impedance until this bit equals 1.

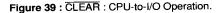

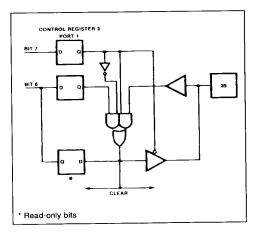

Control Register 3. Bits 7-4 in Control Register 3 enable and control the Clear and Data Direction si-

gnals (figure 7) ; bits 3, 1, and 0 are simple I/O bits for the Port 1 CPU only. Bits 3-0 on the Port 2 side always read 0. Bit 2 is not used and must be programmed to 0 ; it will always read 0. All bits in this register are cleared to 0 by reset. Bits 7 and 5 can be programmed only by the Port 1 CPU. These bits are read-only in the Port 2 Control Register 3.

Bit 7 (Clear, Port 2/Port 1), for CPU-to-CPU operation if set, specifies that Port 2 CPU controls the Clear signal (bit 6). If bit 7 is reset, Port 1 CPU controls the Clear signal. If Port 2 is programmed as an I/O port, this bit programs pin 35 as either input or output (0 = output, 1 = input). This bit can be programmed only by the Port 1 CPU. This is a read-only bit for the Port 2 CPU.

Bit 6 (Clear FIFO Buffer), if reset, clears the FIO RAM buffer. Bit 7 controls which CPU issues Clear signals. (See preceding paragraph). This bit becomes a read-only bit by the CPU not in control of the Clear function.

Bit 5 (Data Direction, Port 2/Port 1), for CPU-to-CPU operation, if set, specifies that Port 2 CPU controls the direction of data flow through FIO RAM. If bit 5 is reset, Port 1 CPU controls the Data Direction signal. If Port 2 is programmed as an I/O port, this bit programs pin 34 as either an input or an output (0 =output, 1 =input). This bit can be programmed only by the Port 1 CPU. This is read-only bit for the Port 2 CPU.

Bit 4 (Data Direction), if set, specifies that data moves from the FIO into the CPU (1 = input to CPU; 0 = output from CPU). If bit 4 is reset, data moves from the controlling CPU into the FIO. When Port 2 is an I/O port, a zero (0) on the Data Direction pin (pin 34) means that Port 2 is an output handshake port. Conversely when the Data Direction pin is a one (1), Port 2 is an input handshake port.

Bits 3 and 1 are Port 2 outputs (pins 30 and 32, respectively) when Port 2 is programmed as an I/O port. These bits always read 0 for the Port 2 CPU.

Bit 2 is not used and must be programmed to 0. This bit always reads 0.

Bit 0 reads pin 33, a Port 2 input, when Port 2 is pro-

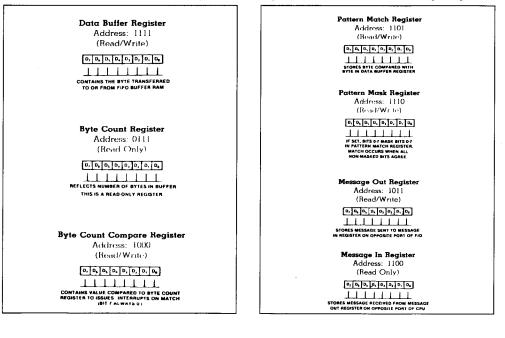

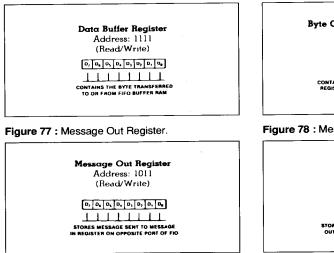

Figure 8 : Data Buffer and Byte Count Registers.

grammed as an I/O port. When Port 2 is not programmed as an I/O port, this bit reads 0. This bit always reads 0 for the Port 2 CPU.

**Data Buffer Register.** The Data Buffer register (figure 8) latches the byte written to or read from FIO RAM. When the Pattern Match register contains a compare byte, it is compared with the bytes passing through the Data Buffer register.

Byte Count Registers. There are two Byte Count registers (figure 8). One contains the ongoing count of bytes present in FIO RAM ; the other holds a byte value that is compared with this ongoing count.

Byte Count Register. The Byte Count register contains an ongoing count of the number of bytes in FIO RAM. This value is the number of bytes written into RAM minus the number of bytes read from RAM. The largest value contained in this register is  $80_H$  (128 decimal). This value can be frozen by setting bit  $D_6$  in Control Register 1. This halts the count so an accurate read can be accomplished. This is a read-only register.

Byte Count Compare Register. The Byte Count Compare register is loaded with a byte value that is

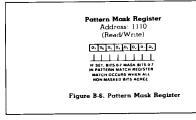

Figure 9 : Pattern Match and Message Registers.

15/85

continuously compared with the ongoing byte count in the Byte Count register. The largest programmable value is  $7F_H$  (127 decimal). Bit 7 always reads 0. If the Byte Count Compare Interrupt bit is set (see Interrupt Status Register 2), an interrupt occurs upon a true match.

Pattern Match Registers. The Pattern Match register contains a byte for comparison with the byte in the Data Buffer. The Pattern Mask register contains a byte pattern used to force a true match.

The Pattern Match and Data Buffer registers are in an unknown state on power-up or after reset and may therefore match. This match may set the Pattern Match IP and the Pattern Match flag.

Pattern Match Register. The Pattern Match register (figure 9) contains a byte for comparison with the byte in the Data Buffer register. As each byte in a data transaction passes through the Data Buffer register, it is compared with the value programmed in the Pattern Mathc register. Upon a true match, an interrupt can be generated if enabled in Interrupt Status Register 1. One or more bits in the Pattern Match register can be masked by the value in the Pattern Mask register.

Pattern Mask Register. The Pattern Mask register (figure 9) contains a bit pattern used to force a true match between the pattern in the Pattern Match register and the pattern in the Data Buffer register. If a Pattern Mask bit is set, the corresponding bit in the Pattern Match register always matches the corresponding bit in the Data Buffer register. A match occurs when all nonmasked bits agree. All 1s in this register forces a pattern match. This register is cleared to 0 by reset.

Message Registers. The Message registers (figure 9) transfer messages between CPUs.

Message Out Register. The CPU sends a message by writing the byte into its Message Out register which also puts it in the other CPU's Message In register. When this is done, the receiving CPU receives an interrupt request (if the IE bit is enabled in Interrupt Status Register 0). The Message Out register of one CPU is the Message In register for the other CPU.

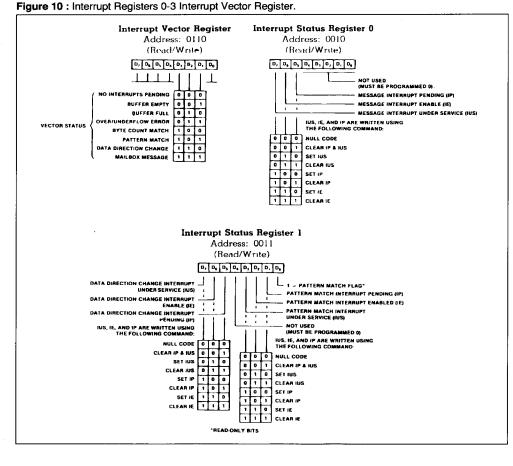

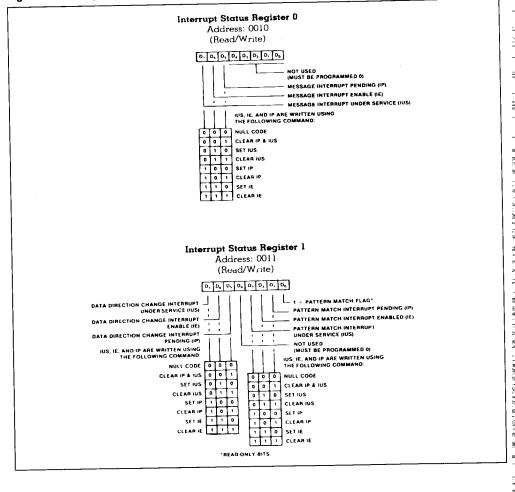

**Message in Register.** The CPU receiving a message byte also receives an interrupt request (if the IE bit is enabled in Interrupt Status Register 0), which signifies that a message has appeared in its Message In register. This is a read-only register. Interrupt Registers. There are four Interrupt Status registers, shown in figure 10, which control and monitor the FIO internal interrupt functions. Prioritized interrupts can occur if they are enabled. The CPU can read the appropriate status register to see if a specific interrupt condition is enabled; other bits in the Interrupt Status registers show if an interrupt is pending or if it under service. Each interrupt condition is described by three Interrupt Status bits : IE (Interrupt Enabled), IP (Interrupt Pending) and IUS (Interrupt Under Service).

Interrupt Status Register 0. In Interrupt Status Register 0, only bits 7, 6, and 5 are used. Bits 4-0 must be programmed to 0; these bits always read 0. All bits are cleared to 0 by reset.

Bit 7 is the Message Interrupt Under Service (IUS) bit and, when set, indicates that a Message interrupt is under service by the receiving CPU.

Bit 6 is the Message Interrupt Enable (IE) bit and, when set, indicates that a message interrupt will be issued when a message is received in the Message In register.

Bit 5 is the Message Interrupt Pending (IP) bit and, when set, indicates that a message interrupt to the receiving CPU is pending. This bit is reset when the read of the Message In register is completed.

Interrupt Status Register 1. Interrupt Status Register 1 controls and monitors Data Direction Change interrupts and Pattern Match interrupts. It also shows if a true pattern match has taken places. All bits except  $D_1$  and  $D_0$  are cleared by reset. Bits  $D_1$  and  $D_0$  may be a 1 or 0 depending upon whether a match condition exists or not.

Bits 7, 6 and 5 show the status of Data Direction Change interrupts and are cleared by reset. When bit 7 is set, a Data Direction Change interrupt is under service. When bit 6 is set, Data Direction Change interrupts are enabled. When bit 5 is set, a Data Direction Change interrupt is pending. Bits 7 and 5 can also be set or reset by program command. Bit 6 is programmed set or reset.

Bit 4 is not used and must be programmed to 0. This bit always reads 0.

Bits 3, 2, and 1 show the status of Pattern Match interrupts. When bit 3 is set, a Pattern Match interrupt is under service. When bit 2 is set, Pattern Match interrupts are enabled. When bit 1 is set, a Pattern Match interrupt is pending. Bits 3 and 1 can also be

16/85

set or reset by program command. Bit 2 is programmed set or reset. Because of a possible match condition on power-up or reset, the match IP bit should be cleared before enabling the Pattern Match IE bit.

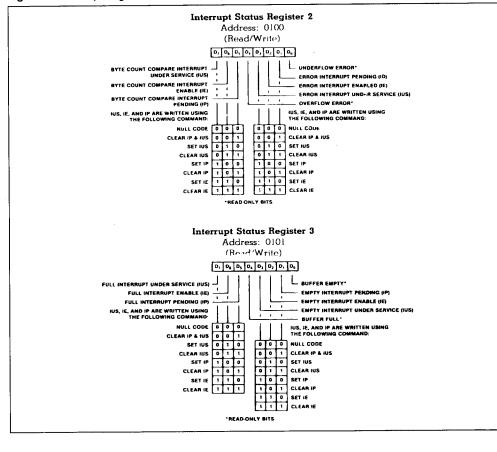

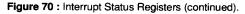

Bit 0 (Pattern Match Flag) is 1 whenever a true pattern match exists between the Data Buffer and the Pattern Match register. The Data Buffer register and the Pattern Match register initialize in an undefined state during reset or power-up. Consequently, the Pattern Match Flag bit can be set, indicating a false pattern match. If Pattern Match interrupts are not going to be used, this bit can be put in a known state, 1, by writing FF<sub>H</sub> to the Pattern Mask register. Interrupt Status Register 2. Interrupt Status Register 2 controls and monitors Byte Count Compare and Overflow and Underflow Error interrupts. This register is cleared to 0 by reset.

Bits 7, 6, and 5 show the status of Byte Count Compare interrupts. When bit 7 is set, a Byte Count Compare interrupt is under service. When bit 6 is set, Byte Count Compare Interrupts are enabled. When bit 5 is set, a Byte Count Compare Interrupt is pending. Bits 7 and 5 can also be set or reset by program command. Bit 6 is programmed set or reset.

Bit 4 is set whenever an attempt is made to write into a full FIO (Overflow Error). This bit is cleared when

17/85

57/

SGS-THOMSON

MICROELECTROMICS

the Error IP bit is cleared. This bit is not set when the Wait function is programmed.

Bits 3, 2, and 1 show the status of Error interrupts. These bits control overflow and underflow errors ; the CPU must read bits 0 and 4 to determine whether overflow or underflow conditions apply. When bit 3 is set, an Error interrupt is under service. When bit 2 is set, Error interrupts are enabled. When bit 1 is set, an Error interrupt is pending. Bits 3 and 1 can also be set or reset by program command. Bit 2 is programmed set or reset. from an empty FIO (underflow error). This bit is cleared when the Error IP is cleared. This bit is not set when the Wait function is programmed.

Interrupt Status Register 3. Interrupt Status Register 3 controls and monitors Buffer Full and Buffer Empty interrupts. All bits except  $D_0$  are cleared by reset.

Bits 7, 6, and 5 show the status of Buffer Full interrupts. When bit 7 is set, a Buffer Full interrupt is under service. When bit 6 is set, Buffer Full interrupts are enabled. When bit 5 is set, a Buffer Full interrupt

×.

Bit 0 is set whenever an attempt is made to read

Figure 10 : Interrupt Registers 0-3 and Interrupt Vector Register (continued).

18/85

280

is pending. Bits 7 and 5 can also be set or reset by program command. Bit 6 is programmed set or reset. In CPU-to-I/O operation for handshake, the full IP bit is set when the buffer is full and the Full pin (pin 37) is High. For the 3-wire handshake the Buffer Full IP is set when the FIO buffer is full.

Bit 4 is a 1 when the FIO buffer is full in CPU-to-CPU operation. In CPU-to-I/O operation for 2-wire handshake, bit 4 is 1 when the buffer is full and the Full pin (pin 37) is High. For the 3-wire handshake this bit is a 1 when the FIO buffer is full.

Bits 3, 2, and 1 show the status of Buffer Empty interrupts. When bit 3 is set, a Buffer Empty interrupts is under service. When bit 2 is set, Buffer Empty interrupts are enabled. When bit 1 is set, a Buffer Empty interrupt is pending. In CPU-to-I/O operation, the Empty IP bit is set when the buffer is empty and the Empty pin (pin 37) is High.

Bit 0 is 1 when the FIO buffer is empty in CPU-to-CPU operation. In CPU-to-I/O operation, bit 0 is 1 when the buffer is empty and when the Empty pin (pin 36) is High.

Interrupt Vector Register. The Interrupt Vector register (figure 10) holds a byte used as the address of an interrupt service routine (or of a table indexing into such groups of routines). This register can be used in two ways. The Interrupt Vector register can be programmed with a byte address that is gated

Table 5 : Data Read from Interrupt Vector Register.

onto the address bus lines during the Interrupt Acknowledge cycle. This provides a direct vector to a generalized interrupt service routine. If bit 4 of Control Register 0 (Vector Includes Status) is set, however, the Interrupt Vector register includes a 3bit status code reflecting the reason for the interrupt request as the contents of bits 3, 2, and 1. When MIE is 1, other than during an Interrupt Acknowledge cycle, the Interrupt Vector register always reflects the FIO status in these bits, regardless of whether or not the Vector Includes Status bit is set. When MIE is 0, the base vector can be read back. This provides a means to read what was written to this register (also see table 5). The bit codes are :

| С(<br>3 | ode B<br>2 | its<br>1 | Encoded Data                               |

|---------|------------|----------|--------------------------------------------|

| 1       | 1          | 1        | Received Message in Message<br>In Register |

| 1       | 1          | 0        | Change in Data Transaction<br>Direction    |

| 1       | 0          | 1        | Valid Pattern Match                        |

| 1       | 0          | 0        | Valid Byte Count Compare                   |

| 0       | 1          | 1        | Overflow or Underflow Error                |

| 0       | 1          | 0        | Buffer Full                                |

| 0       | 0          | 1        | Buffer Empty                               |

| 0       | 0          | 0        | No Interrupts Pending                      |

|                     | MIE = 1 | MIE = 1       | MIE = 0          |

|---------------------|---------|---------------|------------------|

|                     | VIS = 1 | VIS = 0       | VIS = 1 or 0     |

| Interrupt           | Status  | No Status     | Interrupts       |

| Acknowledge         | With    | With Vector   | Are Disabled     |

| Read (INTACK = 0 )  | Vector  | (base vector) | (high impedance) |

| Non Interrupt       | Status  | Status        | No Status        |

| Ackno <u>wledge</u> | With    | With          | With Vector      |

| Read (INTACK = 1)   | Vector  | Vector        | (base vector)    |

#### FUNCTIONAL DESCRIPTION

The FIO provides an interface between two CPUs or between a CPU and an I/O device. It interfaces to both Z-BUS and non-Z-BUS systems and emulates 2-wire and 3-wire I/O protocols. Figure 11 shows possible FIO operations.

These interfacing tasks require different sets of control signals. After removing the FIO from its reset state and programming the various registers, the FIO assumes one of the 12 operating modes shown in Table 1. In each mode, Port 2 presents one of five possible groups of signals on pins A-J. These signals correspond to the Z-BUS high-byte configuration, Z-BUS low-byte configuration, non-Z-BUS (general microprocessor) configuration, 2-wire hands-hake configuration, and 3-wire handshake configuration. Port 1 presents one of three groups of signals on pins A-J, corresponding to Z-BUS high-byte, Z-BUS low-byte, or non-Z-BUS configurations.

This chapter describes the signals used in FIO data transactions; discusses reset operation and uses for the 12 operating modes; and explains how control signals form interfaces to other devices, how DMA transactions occur, and how the FIO handles internal interrupts and participates in the system-level, daisy-chain interrupt protocols.

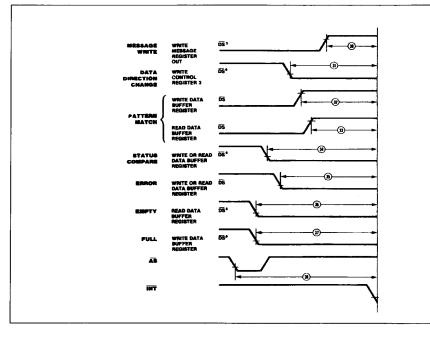

#### INTERFACING SIGNAL

The FIO manages data transfers with control signals, some issued from the bus master CPU, satellite CPU, DMA device, or I/O device, some created from external logic, and some issued from within the FIO itself. There are five basic signal configurations that combine to form 12 operating modes, as shown in Table 1. The control signals used in each configuration are shown mapped to their respective pins in figure 2. The signals fall into various groups, as described in the following sections. Reset is not actually a control signal states (or programming) it is treated as such here.

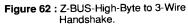

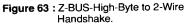

**Z-BUS High-Byte and Low-Byte.** The Z-BUS highbyte and low-byte microprocessor configurations are normally used together to form a 16-bit multiplexed address/data bus interface that is compatible with the Z-BUS. The Z-BUS low-byte microprocessor configuration can be used by itself as an 8bit interface to a multiplexed bus. The Z-BUS highbyte microprocessor configuration can also be used this way, but it lacks interrupt interfacing signals.

**Signals.** In the Z-BUS cofigurations, the FIO uses the following set of signals :

Request/Wait, DMA Strobe, Data Strobe, Read/Write, Chip Select, Address Strobe, and the interrupt arbitration signals Interrupt Acknowledge, Interrupt Request, Interrupt Enable In, and Interrupt Enable Out.

**REQ/WAIT** (Request/Wait, output, 3-state, active Low). REQ is sent to a DMA device to begin a DMA transfer, and WAIT (an open drain output) tells the CPU that the FIO buffer is full (if data is output from the CPU to the FIO) or that the FIO buffer is empty (if data is input to the CPU from the FIO).

**DMASTB** (*DMA Strobe, input, active Low*). This signal is received by the FIO from a DMA controller. When Low, it acts like a Read/Write signal, strobing data to or from the Data Buffer register directly during DMA transactions.

**DS** (*Data Strobe, input, active Low).* When Low, DS specifies that the multiplexed address/data bus is carrying data rather than address information.

$\mathbf{R}/\overline{\mathbf{W}}$  (*Read/Write, input*). Read and Write signals specify read and write operations. When  $\mathbf{R}/\overline{\mathbf{W}}$  is Low, writes are enabled. When  $\mathbf{R}/\mathbf{W}$  is High, reads are enabled.

$\overline{CS}$  (Chip Select, input, active Low).  $\overline{CS}$  is usually a signal derived from the controlling CPU's signals by external logic. When Low,  $\overline{CS}$  selects the FIO and enables it for operation. This signal is latched on the rising edge of AS.

**AS** (Address Strobe, input, active Low). When low, AS specifies that the multiplexed address/data bus is carrying address information rather than data.

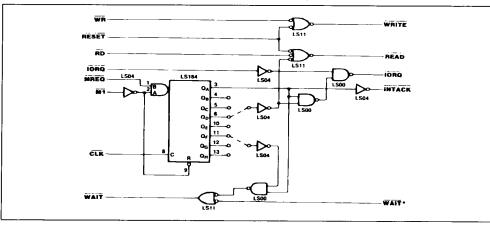

**Z-BUS Low-Byte Configuration Only.** In the Z-BUS low-byte configuration, the FIO uses four interrupt arbitration signals to participate in the daisychain prioritized interrupt arbitration scheme.

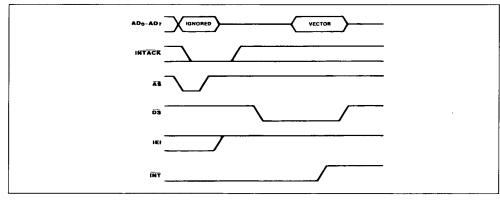

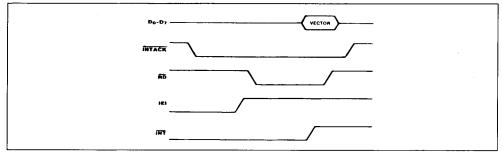

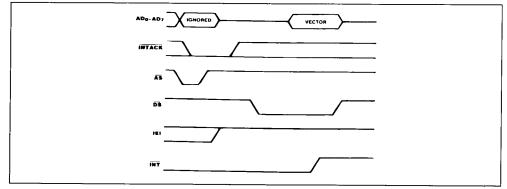

**INTACK** (Interrupt Acknowledge, input, active Low), IEI (Interrupt Enable In, input, active High), IEO (Interrupt Enable Out, output, active High), INT (Interrupt Request, output, open drain, active Low). IN-TACK, IEI, IEO, and INT control FIO interrupt operation. INT requests an interrupt from the CPU when

20/85 382

SGS-THOMSON

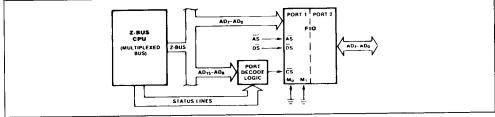

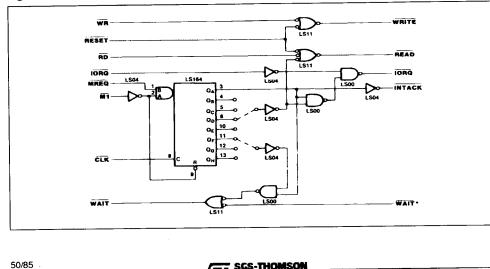

active (Low) ; INTACK is the interrupt acknowledgement from the CPU. IEI is the input for the daisy-chain, prioritized interrupt enable signal. IEO is the corresponding output for the same signal. Figure 12 shows a typical use of the Z-BUS lowbyte configuration. The  $M_0$  and  $M_1$  pins are shown tied to ground ; this specifies Z-BUS low-byte configuration.

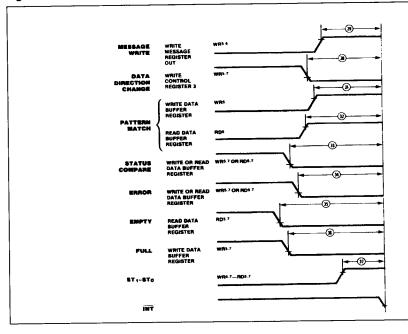

# Figure 11 : FIO Operational Summary.

21/85

Figure 12 : Z-BUS Low-Byte Configuration.

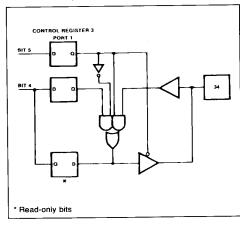

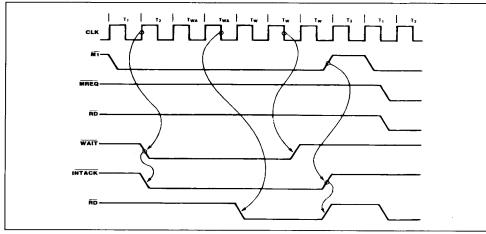

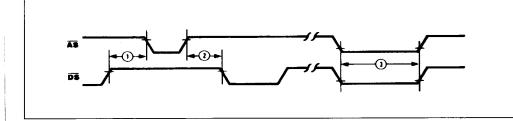

**Z-BUS Low Byte Interface Operation.** Address/Data lines AD<sub>0</sub>-AD<sub>15</sub> leave the CPU. During the time  $\overline{AS}$  is active, signifying that the address/data bus currently carries and address, lines AD<sub>0</sub> – AD<sub>7</sub> carry the 4-bit address of the internal register addressed within the FIO.

Once the Z-BUS low-byte configuration has been specified as shown in Table 1, the  $\overline{CS}$  signal is Low, and the address information has been delivered (as shown by the removal of an active  $\overline{AS}$  Signal), the  $\overline{DS}$  signal goes Low and data appears on  $AD_0 - AD_7$ . When bit 0 is set in Control register 0, the FIO reset, all control registers cleared, and all outputs (except IEO on the port 1 side) floating at high impedance, the FIO is ready to program.

**Register Addressing.** In the Z-BUS low-byte configuration, the FIO allows two methods for register addressing under control of the Right Justify Address bit (bit D<sub>1</sub>) of Control Register 0. When bit D<sub>1</sub> is reset (the default condition), address bus lines AD<sub>1</sub> – AD<sub>4</sub> are used for register addressing, and the other Address/Data lines are ignored. This convention assures compatibility with the Z8000 byte I/O addressing protocols. When D<sub>1</sub> is set, address bus lines AD<sub>0</sub>-AD<sub>3</sub> are used for register addresses and the other Address/Data lines are ignored. Lines AD<sub>8</sub> – AD<sub>15</sub> carry the 8-bit port address decoded by the port decode logic along with status to provide an active  $\overline{CS}$  signal ;  $\overline{AS}$  latches it into the FIO. Table 6 describes Z-BUS low-byte register addressing.

| Z-BUS Low RJA = 0<br>RJA = 1   | AD <sub>7</sub> -AD <sub>5</sub><br>AD <sub>7</sub> -AD <sub>4</sub> | AD <sub>4</sub><br>AD <sub>3</sub> | AD <sub>3</sub><br>AD <sub>2</sub> | AD <sub>2</sub><br>AD <sub>1</sub> | AD <sub>1</sub><br>AD <sub>0</sub> | ADo |

|--------------------------------|----------------------------------------------------------------------|------------------------------------|------------------------------------|------------------------------------|------------------------------------|-----|

| Description                    |                                                                      |                                    |                                    |                                    | <b></b>                            |     |

| Control Register 0             | x                                                                    | 0                                  | 0                                  | 0                                  | 0                                  | ×   |

| Control Register 1             | x                                                                    | 0                                  | 0                                  | 0                                  | 1                                  | ×   |

| Interrupt Status Register 0    | x                                                                    | 0                                  | 0                                  | 1                                  | 0                                  | ×   |

| Interrupt Status Register 1    | x                                                                    | 0                                  | 0                                  | 1                                  | 1                                  | x   |

| Interrupt Status Register 2    | x                                                                    | 0                                  | 1                                  | 0                                  | 0                                  | x   |

| Interrupt Status Register 3    | x                                                                    | 0                                  | 1                                  | 0                                  | 1                                  | ×   |

| Interrupt Vector Register      | x                                                                    | 0                                  | 1                                  | 1                                  | 0                                  | x   |

| Byte Count Register            | x                                                                    | 0                                  | 1                                  | 1                                  | 1                                  | ×   |

| Byte Count Comparison Register | x                                                                    | 1                                  | 0                                  | 0                                  | 0                                  | x   |

| Control Register 2*            | x                                                                    | 1                                  | 0                                  | 0                                  | 1                                  | x   |

| Control Register 3             | x                                                                    | 1                                  | 0                                  | 1                                  | 0                                  | x   |

| Message Out Register           | x                                                                    | 1                                  | 0                                  | 1                                  | 1                                  | ×   |

| Message in Register            | x                                                                    | 1                                  | 1                                  | 0                                  | 0                                  | ×   |

| Pattern Match Register         | ×                                                                    | 1                                  | 1                                  | 0                                  | 1                                  | ×   |

| Pattern Mask Register          | x                                                                    | 1                                  | 1                                  | 1                                  | 0                                  | x   |

| Data Buffer Register           | x                                                                    | 1                                  | 1                                  | 1                                  | 1                                  | x   |

#### Table 6 : Register Addressing.

x = Don't care

\* Register is only on Port 1 side

22/85

**Reset Operation.** In the Z-BUS configurations, the FIO is hardware reset when both AS and DS are forced Low (normally an illegal condition) or it is software reset by writing a 1 to the reset bit in Control Register 0. When Port 1 is reset, Port 2 is also reset. If the Port 1 CPU reads the Port 1 registers during reset, they return all 0s except Control Register 0, which reads  $01_{\rm H}$ . All of Port 2's signal lines are floating in this state, and all inputs are ignored. If Port 2 is reset by itself, Port 1 registers during reset, When the Port 2 CPU reads the Port 2 registers during reset, they return all 0s except Control Register 0, which reads  $01_{\rm H}$ . All of Port 2 registers during reset, they return all 0s except Control Register 0, which reads  $01_{\rm H}$ .

Before data transactions can take place, the FIO must be taken out of the reset state by writing  $00_H$  to Control Register 0. No other bits in this register can be programmed while clearing the reset bit. The Port 1 CPU then enables Port 2 by setting bit  $D_0$  of the Port 1 Control Register 2. The Port 2 CPU can determine when it is enabled by reading its Control Register 0, which is read as a "floating" data bus if not enabled or as  $01_H$  if enabled.

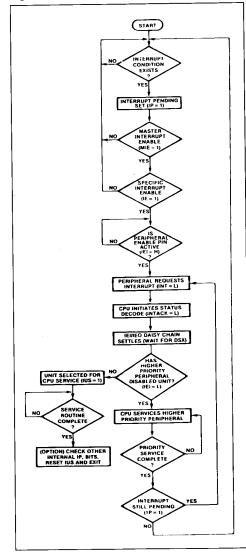

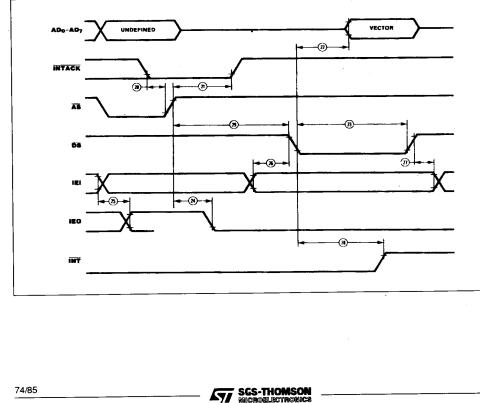

Interrupts. The Z-BUS low-byte configuration supports the prioritized daisy-chain interrupt protocols. INTACK, IEI, IEO, and INT control FIO interrupt operation. INT sends an interrupt signal to the CPU; IN-TACK is the interrupt acknowledgement from the CPU. IEI is the input for the daisy-chain prioritized interrupt signal. IEO is the corresponding output for the same signal. When using two FIOs as a 16-bit Z-BUS interface, the low-byte FIO must handle external interrupt transactions, since the corresponding pins on the high-byte FIO are used for internal register addressing. This is not a handicap, since all INT conditions are the same for both FIOs, except for the pattern match condition.

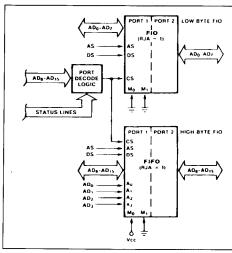

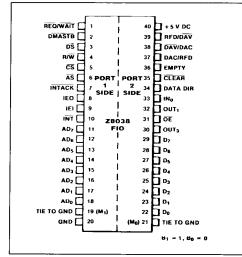

Figure 13 shows a typical use of the Z-BUS low-byte and high-byte configurations with two FIOs, forming a 16-bit multiplexed bus interface. The single FIO in figure 12 runs parallel with another FIO in the Z-BUS high-byte configuration. The Z-BUS high-byte configuration is specified as shown in Table 1.

**Z-BUS High Byte Interface Operation.** As in the Z-BUS low-byte configuration, Address/Data lines  $AD_0 - AD_{15}$  leave the Port 1 CPU. During an active AS signal, lines  $AD_0 - AD_7$  carry the address of the internal register addressed within the FIO.

While  $\overline{AS}$  is active, lines  $AD_8 - AD_{15}$  carry the port address to the port decode logic, which issues an active  $\overline{CS}$  signal. This signal is also supplied to the high-byte FIO. The RJA bit is not used on the highbyte FIO.

Figure 13: Z-BUS High-Byte and Low-Byte Configuration.

Once the low-byte and high-byte configurations have been specified as shown in Table 1, the  $\overline{CS}$  signal is Low, and the address information has been delivered (as shown by the removal of an active AS signal), the  $\overline{DS}$  signal goes Low, indicating that true data is on the Address/Data lines.

**Register Addressing.** Both FIOs require the same internal register address, but lines  $AD_0 - AD_7$  go to the low-byte FIO only. For this reason, the signals on the four Address/Data pins used to specify FIO internal register addresses must be supplied to pins  $A_0 - A_3$  of the high-byte FIO, as shown in figure 14. Since pins  $AD_0 - AD_3$  are used for addressing, the low-byte FIO must handle external interrupt interfacing. Table 7 describes Z-BUS high byte register addressing.

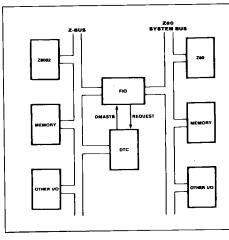

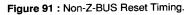

**Reset Operation.** In the Z-BUS configurations, the FIO is hardware reset when both  $\overrightarrow{AS}$  and  $\overrightarrow{DS}$  are forced Low (normally an illegal condition) or it is software reset by writing a 1 to the reset bit in Control Register 0. When Port 1 is reset, Port 2 is also reset. If the Port 1 CPU reads the Port 1 registers during reset, they return all 0s except Control Register 0, which reads 01<sub>H</sub>. All of Port 2's signal lines are floating in this state, and all inputs are ignored. If Port 2 is reset by itself, Port 1 registers during reset, they return all 0s except Control Register Port 2 is reset by itself, Port 1 registers during reset, they return all 0s except Control Register 0, which reads 01<sub>H</sub>.

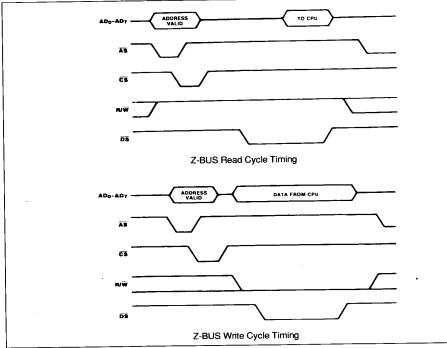

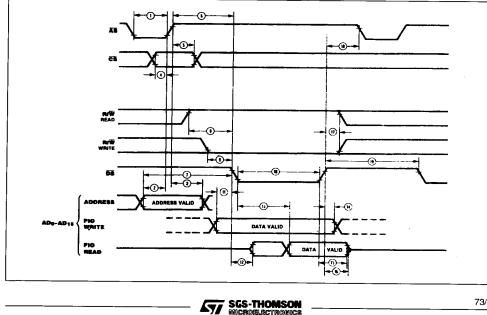

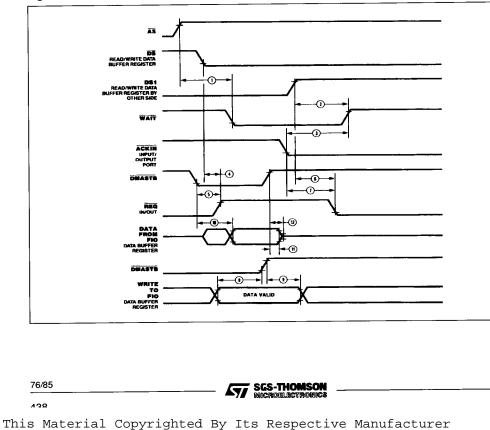

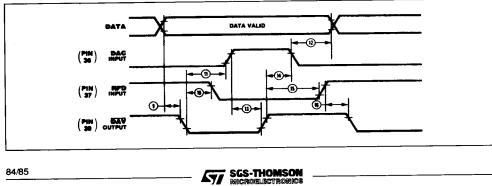

Figure 14: Z-BUS Configuration Timing.

Before data transactions can take place, the FIO must be taken out of the reset state by writing  $00_H$  to Control Register 0. No other bits in this register can be programmed while clearing the reset bit. The Port 1 CPU then enables Port 2 by setting bit Do of the Port 1 Control Register 2. The Port 2 CPU can determine when it is enabled by reading its Control Register 0, which is read as a "floating" data bus if not enabled or as  $01_H$  if enabled.

**Z-BUS High - and Low-Byte Programming.** The FIOs, like other Z-BUS-compatible peripheral devices, accept byte-serial programming. The CPU must replicate the programming byte sent to  $AD_0 - AD_7$  on the  $AD_8 - AD_{15}$  address lines, insuring that the same programming byte goes to the high-byte FIO as to the low-byte FIO. The first programming byte is typically sent to Control Register 0. The FIO is then ready to program. Once programming is complete, 16-bit data transfers can take place, with the low-byte FIO transferring the byte on lines  $AD_0 - AD_7$ .

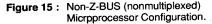

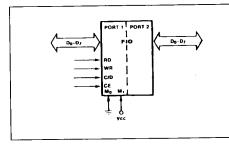

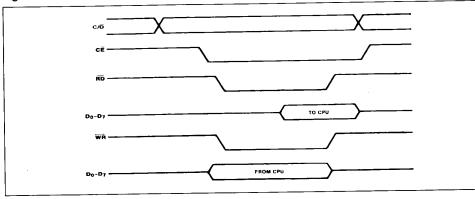

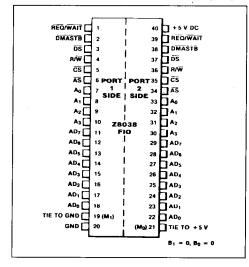

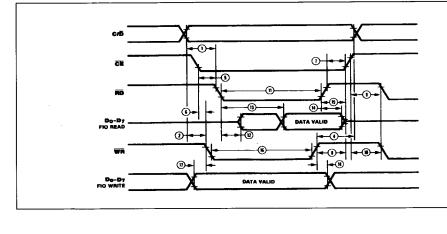

**Non-Z-BUS** (nonmultiplexed) **Microprocessor**. The non-Z-BUS (nonmultiplexed) microprocessor configuration interfaces the FIO to a variety of microprocessors that use separate data and address uses, such as the Z80. Figure 15 shows a typical non-Z-BUS configuration. Figure 16 shows non-Z-BUS configuration timing information.

24/85

386

SGS-THOMSOF

### Table 7 : Register Addressing.

| Z-BUS High Byte                | A3 | A <sub>2</sub> | A1 | A <sub>0</sub> |

|--------------------------------|----|----------------|----|----------------|

| Description                    |    | <u> </u>       |    |                |

| Control Register 0             | 0  | 0              | 0  | 0              |

| Control Register 1             | 0  | 0              | 0  | 1              |

| Interrupt Status Register 0    | 0  | 0              | 1  | 0              |

| Interrupt Status Register 1    | 0  | 0              | 1  | 1              |

| Interrupt Status Register 2    | 0  | 1              | 0  | 0              |

| Interrupt Status Register 3    | 0  | 1              | 0  | 1              |

| Interrupt Vector Register      | 0  | 1              | 1  | 0              |

| Byte Count Register            | 0  | 1              | 1  | 1              |

| Byte Count Comparison Register | 1  | 0              | 0  | 0              |

| Control Register 2*            | 1  | 0              | 0  | 1              |

| Control Register 3             | 1  | 0              | 1  | 0              |

| Message Out Register           | 1  | 0              | 1  | 1              |

| Message in Register            | 1  | 1              | 0  | 0              |

| Pattern Match Register         | 1  | 1              | 0  | 1              |

| Pattern Mask Register          | 1  | 1              | 1  | 0              |

| Data Buffer Register           | 1  | 1              | 1  | 1              |

\* Register is only on Port 1 side

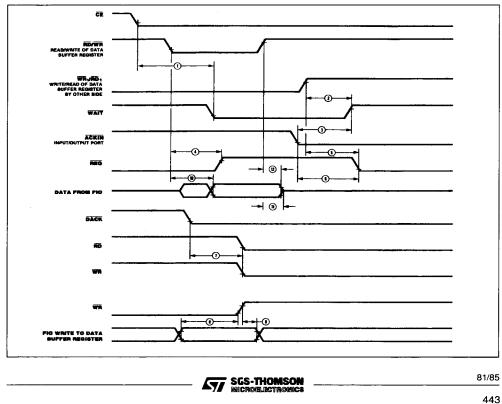

Figure 16 : Non-Z-BUS (nonmultiplexed) Microprocessor Configuration Timing.

25/85

**Δ**7/

SGS-THOMSON

LECTRONICS

Signals. In the non-Z-BUS (nonmultiplexed) microprocessor configurations, the following signals control data transactions : Request/Wait, DMA Acknowledge, Read, Write, Chip Enable, Control/Data, Interrupt Acknowledge, Interrupt Enable Input, Interrupt Enable Output, and Interrupt Request.

**REQ/WAIT** (Request/Wait, output, 3-state, active Low). The request signal is sent to a DMA device to begin a DMA transfer, and the Wait (open drain output) signal tells the CPU that the FIO buffer is full (if data is output from the CPU to the FIO) or that the FIO buffer is empty (if data is input to the CPU from the FIO). Bit D<sub>1</sub> of Control Register 1 selects the Request or Wait signals.

**DACK** (*DMA Acknowledge, input, active Low*). This signal is received by the FIO from a DMA controller. When Low, it forces the next read or write to the FIO to go through the Data Buffer register, regardless of the C/D conditions.

**RD** (*Read, input, active Low*). The Read signal tells the FIO that the CPU wants to read data from it.

WR (Write, input, active Low). The Write signal tells the FIO that the CPU wants to write data to it.

**CE** (*Chip Enable, input, active Low*). The Chip Enable signal selects the FIO when the CPU needs to carry out a data transaction involving it. The CE signal is usually generated from CPU address and status signals by external logic.

$C/\overline{D}$  (*Control/Data, input*). The C/D signal is used to distinguish between control and data bytes.

**INTACK** (Interrupt Acknowledge, input, active Low), IEI (Interrupt Enable In, input, active High), IEO (Interrupt Enable Out, output, active High), INT (Interrupt Request, output open drain, active Low). IN-TACK, IEI, IEO, and INT control FIO interrupt operation. INT requests an interrupt from the CPU when Low, INTACK is the interrupt acknowledgement from the CPU. IEI is the input for the daisy-chain, prioritized interrupt enable signal. IEO is the corresponding output for the same signal.

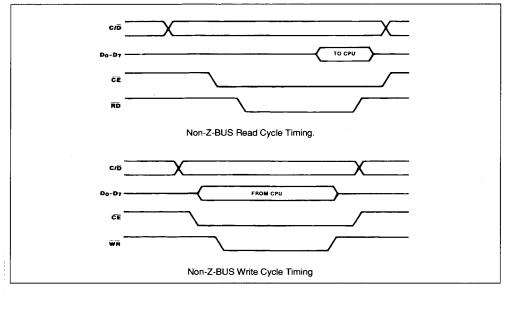

**Register Addressing.** In the nonmultiplexed configurations, the FIO connects to the system data bus via  $D_0 - D_7$ , but not to the address bus. The CPU must provide address information on the data bus, and the FIO must distinguish between address and data bytes. The Control/Data  $(C\overline{D})$  pin does this with the help of the following programming conventions.

Figure 17 shows the register access state diagram. Before programming either port of the FIO, it should be reset, clearing all control registers. Getting out of the reset state is described in the next section.

To move data bytes to or from the FIFO buffer, simply lower  $C\overline{D}$  to 0 ( $C\overline{D}$  is typically tied to an address pin) and read or write directly into the Data Buffer register. To read or write to all registers (including the Data Buffer register) is a two step operation. First, write the address ( $C\overline{D} = 1$ ) of the register to be accessed into the Pointer Register (state 0 to state 1). The Pointer Register (4 bits) holds the register address. Second, read or write ( $C\overline{D} = 1$ ) to the register addressed previously (state 1 to state 0).

The Pointer Register is not modified or cleared when going from state 1 to state 0. The Pointer Register is only changed by a write  $(C/\overline{D} = 1)$  while in state 0. Consequently, status monitoring can be done while in state 0 by doing a read with  $C/\overline{D} = 1$ .

For example, if the last register address was Control Register 2, then by doing a read with  $C/\overline{D} = 1$  (stay in state 0) the contents of Control Register 2 will again be read out. This may be useful for doing polling operations.

In the non-Z-BUS configuration, the RJA bit (D<sub>1</sub> of Control Register 0) is set. This specifies that bits 0-3 carry the address of the FIO internal registers and supports such CPUs as the Z80. Table 8 describes the Non-Z-BUS register addressing.

Figure 17 : Register Access State Diagram.

26/85 388 10.00

2

SGS-THOMSON

Table 8 : Register Addressing.

| Non-Z-BUS                      | D7-D4 | D3 | D <sub>2</sub> | D <sub>1</sub> | Do |

|--------------------------------|-------|----|----------------|----------------|----|

| Description                    |       | •  | •••            | •              | •  |

| Control Register 0             | x     | 0  | 0              | 0              | 0  |

| Control Register 1             | x     | 0  | 0              | 0              | 1  |

| Interrupt Status Register 0    | x     | 0  | 0              | 1              | 0  |

| Interrupt Status Register 1    | x     | 0  | 0              | 1              | 1  |

| Interrupt Status Register 2    | x     | 0  | 1              | 0              | 0  |

| Interrupt Status Register 3    | x     | 0  | 1              | 0              | 1  |

| Interrupt Vector Register      | x     | 0  | 1              | 1              | 0  |

| Byte Count Register            | x     | 0  | 1              | 1              | 1  |

| Byte Count Comparison Register | x     | 1  | 0              | 0              | 0  |

| Control Register 2*            | x     | 1  | 0              | 0              | 1  |

| Control Register 3             | x     | 1  | 0              | 1              | 0  |

| Message Out Register           | x     | 1  | 0              | 1              | 1  |

| Message in Register            | x     | 1  | 1              | 0              | 0  |

| Pattern Match Register         | x     | 1  | 1              | 0              | 1  |

| Pattern Mask Register          | x     | 1  | 1              | 1              | 0  |

| Data Buffer Register           | ×     | 1  | 1              | 1              | 1  |

x = Don't care

\* Register is only on Port 1 side

**Reset Operation.** In non-Z-BUS configuration, the FIO is hardware reset by forcing both RD and WR Low (normally an illegal condition) or by writing a 1 to the reset bit in Control Register 0. After reset is asserted, the only register that can be read from or written to is Control Register 0 (Control Register 0 will read a 01<sub>H</sub>). If  $C/\overline{D}$  is 1, the next byte writes into Control Register 0. When in the reset state, a write should not be done when  $C/\overline{D}$  is 0. The reset state is exited by writing 00<sub>H</sub> when  $C/\overline{D}$  is 1. When Port 1 is reset, Port 2 is also reset. All of Port 2's signal lines are floating in this state and all inputs are ignored. If the Port 1 or Port 2 CPU (if enabled) reads any of its registers during reset, they return to 01<sub>H</sub> (Control Register 0).

Software Reset. To software reset the FIO, it must be in state 1 and the Pointer register must point to Control Register 0. Table 9 outlines a method for resetting the FIO. The left column explains the software procedures used if the port was already reset. The right column shows the procedures used if the port was not reset. This procedure resets the FIO and then removes the reset making the FIO ready for programming. The table assumes that  $C/\overline{D}$  is 1.

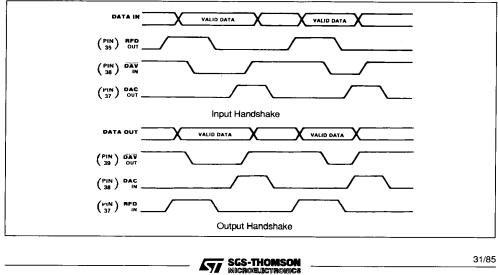

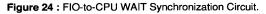

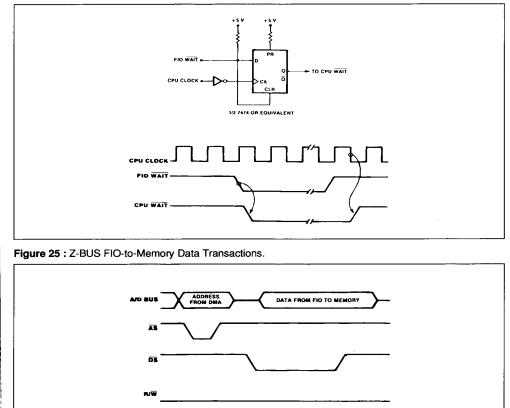

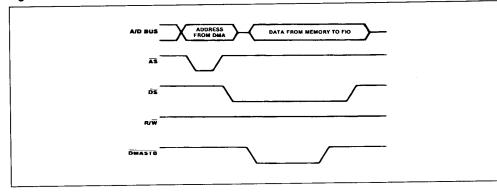

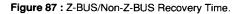

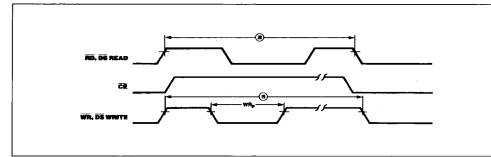

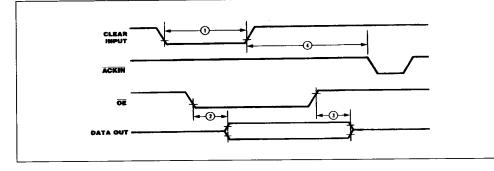

In Reset. If the port is already reset, reading it will have no effect and will return 01<sub>H</sub>, since the reset bit