# MOTOROLA SEMICONDUCTOR TECHNICAL DATA

## Product Preview

## Programmable Timer High-Performance Silicon-Gate CMOS

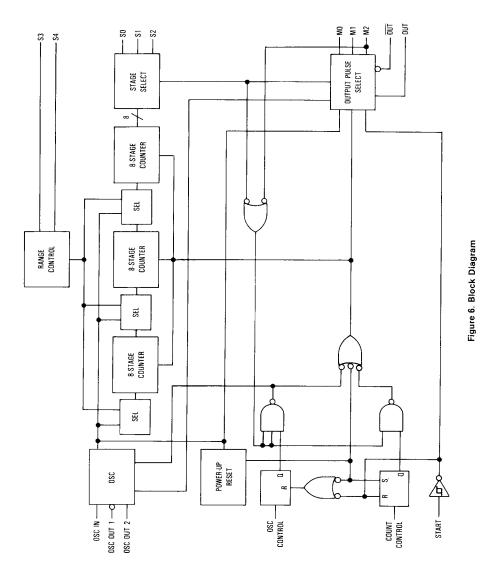

The MC54 '74HC9000 is a precision programmable timer that, when used in conjunction with a 32 kHz to 20 MHz crystal, can provide time durations from 4.2 minutes to 100 ns. Using the on-chip oscillator function and external RC components, even longer time durations can be obtained. Both true and complementary outputs are available for use with the edge-sensitive oscillator control and count control. These control pins facilitate several timer and "one-shot" type configurations (see Application Information).

- Has On-Chip Crystal or RC Oscillator Capability; or may be Driven by External Frequency Source

- More Accurate than Monostable Multivibrators when used with a Crystal

- Low Power Consumption Characteristic of CMOS Devices

- Wide Operating Voltage Range: 2.5 to 6 Volts

- OUT and OUT Drive Capability: 10 LSTTL Loads

- High Noise Immunity Characteristics of CMOS Devices

- Very Low Power Consumption in Standby Mode

- Double Diode Protection on all Inputs

- Divide Range of 2 to 2<sup>24</sup>

- Select Inputs (S0, S1, S2, S3, S4) Facilitate Programming and Incoming Inspection

- Mode Inputs (M0, M1, M2) for Functional Versatility

- Chip Complexity: 923 FETs or 231 Equivalent Gates

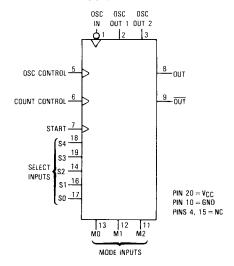

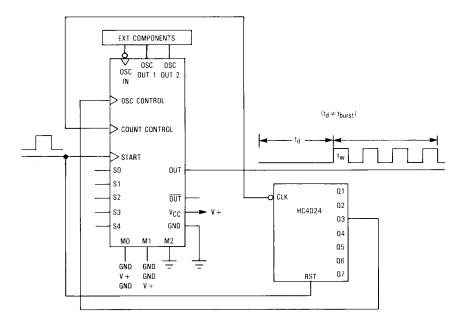

#### LOGIC DIAGRAM

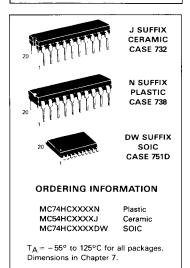

## MC54/74HC9000

This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice.

## MAXIMUM RATINGS\*

| Symbol           | Parameter                                                                                         | Value                          | Unit |

|------------------|---------------------------------------------------------------------------------------------------|--------------------------------|------|

| Vcc              | DC Supply Voltage (Referenced to GND)                                                             | -0.5 to +7.0                   | ٧    |

| Vin              | DC Input Voltage (Referenced to GND)                                                              | - 1.5 to V <sub>CC</sub> + 1.5 | ٧    |

| Vout             | DC Output Voltage (Referenced to GND)                                                             | -0.5 to V <sub>CC</sub> +0.5   | V    |

| lin              | DC Input Current, per Pin                                                                         | ± 20                           | mA   |

| lout             | DC Output Current, per Pin                                                                        | ± 25                           | mΑ   |

| lcc              | DC Supply Current, VCC and GND Pins                                                               | ± 50                           | mA   |

| PD               | Power Dissipation in Still Air, Plastic or Ceramic DIP†<br>SOIC Package†                          | 750<br>500                     | mW   |

| T <sub>stg</sub> | Storage Temperature                                                                               | - 65 to + 150                  | °C   |

| TL               | Lead Temperature, 1 mm from Case for 10 Seconds<br>(Plastic DIP or SOIC Package)<br>(Ceramic DIP) | 260<br>300                     | °C   |

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation,  $V_{in}$  and  $V_{out}$  should be constrained to the range GND  $\leq$  ( $V_{in}$  or  $V_{out}$ )  $\leq$   $V_{CC}$ .

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or VCC). Unused outputs must be left open.

Functional operation should be restricted to the Recommended Operating Conditions.

†Derating — Plastic DIP: -10 mW/°C from 65° to 125°C Ceramic DIP: -10 mW/°C from 100° to 125°C

SOIC Package: -7 mW/°C from 65° to 125°C

For high frequency or heavy load considerations, see Chapter 4 subject listing on page 4-2.

## RECOMMENDED OPERATING CONDITIONS

| Symbol                            | Parameter                                                             | Min                                        | Max                | Unit  |    |  |

|-----------------------------------|-----------------------------------------------------------------------|--------------------------------------------|--------------------|-------|----|--|

| Vcc                               | DC Supply Voltage (Referenced to GND)                                 |                                            | 2.5*               | 6.0   | V  |  |

| V <sub>in</sub> ,V <sub>out</sub> | DC Input Voltage, Output Voltage (Referenced to                       | o GND)                                     | 0                  | Vcc   | V  |  |

| TA                                | Operating Temperature, All Package Types                              |                                            | - 55               | + 125 | °C |  |

| t <sub>r</sub> , t <sub>f</sub>   | Input Rise and Fall Time VC( Except OSC IN and START VC (Figure 1) VC | 0<br>0<br>0                                | 1000<br>500<br>400 | ns    |    |  |

|                                   | Input Rise and Fall Time (OSC IN or                                   | Input Rise and Fall Time (OSC IN or START) |                    |       |    |  |

<sup>\*</sup>The oscillator is guaranteed to function at 2.5 V minimum. However, parametrics are tested at 2.0 V by driving Pin 1 with an external clock source.

#### DC ELECTRICAL CHARACTERISTICS (Voltages Referenced to GND)

|        |                                                   |                                                                                                      |                                                             | vcc                | Gua                | ranteed Li         | mit               | Unit |

|--------|---------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------|--------------------|--------------------|-------------------|------|

| Symbol | Parameter                                         | Test Con                                                                                             | Test Conditions                                             |                    | 25°C to<br>-55°C   | ≤85°C              | ≤ 125°C           |      |

| VIH    | Minimum High-Level Input<br>Voltage               | $V_{out} = 0.1 \text{ V or } V_{CC}$<br>$ I_{out}  \le 20 \mu\text{A}$                               | 2.0<br>4.5<br>6.0                                           | 1.5<br>3.15<br>4.2 | 1.5<br>3.15<br>4.2 | 1.5<br>3.15<br>4.2 | ٧                 |      |

| VIL    | Maximum Low-Level Input<br>Voltage                | $V_{out} = 0.1 \text{ V or V}_{CC}$<br>$ I_{out}  \le 20 \mu\text{A}$                                | 2.0<br>4.5<br>6.0                                           | 0.3<br>0.9<br>1.2  | 0.3<br>0.9<br>1.2  | 0.3<br>0.9<br>1.2  | V                 |      |

| VOH    | Minimum High-Level Output<br>Voltage (OUT, OUT)   | $V_{\text{in}} = V_{\text{IH}} \text{ or } V_{\text{IL}}$<br>$ I_{\text{Out}}  \le 20 \ \mu\text{A}$ |                                                             | 2.0<br>4.5<br>6.0  | 1.9<br>4.4<br>5.9  | 1.9<br>4.4<br>5.9  | 1.9<br>4.4<br>5.9 | V    |

|        |                                                   | Vin=VIH or VIL                                                                                       | I <sub>out</sub>   ≤ 4.0 mA<br> I <sub>out</sub>   ≤ 5.2 mA | 4.5<br>6.0         | 3.98<br>5.48       | 3.84<br>5.34       | 3.70<br>5.20      |      |

| VOL    | Maximum Low-Level Output<br>Voltage (OUT, OUT)    | $V_{in} = V_{IH} \text{ or } V_{IL}$<br>$ I_{out}  \le 20 \mu A$                                     |                                                             | 2.0<br>4.5<br>6.0  | 0.1<br>0.1<br>0.1  | 0.1<br>0.1<br>0.1  | 0.1<br>0.1<br>0.1 | ٧    |

|        |                                                   | V <sub>in</sub> =V <sub>IH</sub> or V <sub>IL</sub>                                                  | I <sub>out</sub>   ≤ 4.0 mA<br> I <sub>out</sub>   ≤ 5.2 mA | 4.5<br>6.0         | 0.26<br>0.26       | 0.33<br>0.33       | 0.40<br>0.40      |      |

| lin    | Maximum Input Leakage Current                     | Vin = VCC or GND                                                                                     |                                                             | 6.0                | ± 0.1              | ± 1.0              | ± 1.0             | μΑ   |

| lcc    | Maximum Quiescent Supply<br>Current (per Package) | $V_{in} = V_{CC}$ or GND<br>$I_{out} = 0 \mu A$                                                      |                                                             | 6.0                | 8                  | 80                 | 160               | μΑ   |

NOTE: Information on typical parametric values can be found in Chapter 4 subject listing on page 4-2.

## MOTOROLA HIGH-SPEED CMOS LOGIC DATA

5-632

5

<sup>\*</sup>Maximum Ratings are those values beyond which damage to the device may occur.

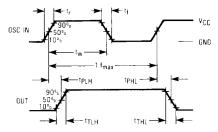

## AC ELECTRICAL CHARACTERISTICS ( $C_L = 50 \text{ pF}$ , Input $t_r = t_f = 6 \text{ ns}$ )

|                  |                                                                                        | 1,,               | Pr                |                   |                   |      |

|------------------|----------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|------|

| Symbol           | Parameter                                                                              | Vcc               | 25°C to<br>-55°C  | ≤85°C             | ≤125°C            | Unit |

| f <sub>max</sub> | Maximum Clock Frequency (Modes 1-7) (50% Duty Cycle) (Figures 1 and 2)                 | 2.0<br>4.5<br>6.0 | 4.0<br>20<br>24   | 3.2<br>16<br>19   | 2.6<br>13<br>15   | MHz  |

| f <sub>max</sub> | Maximum Clock Frequency (Mode 0) (50% Duty Cycle)<br>(Figures 1 and 2)                 | 2.0<br>4.5<br>6.0 | 2.0<br>10<br>11.8 | 1.6<br>8.0<br>9.4 | 1.3<br>6.7<br>7.9 | MHz  |

| tPLH,<br>tPHL    | Maximum Propagation Delay, OSC IN to OUT or OUT (One Stage Selected) (Figures 1 and 2) | 2.0<br>4.5<br>6.0 | 250<br>50<br>43   | 315<br>63<br>54   | 375<br>75<br>64   | ns   |

| tPLH,<br>tPHL    | Maximum Propagation Delay, START to OUT or OUT (One Shot Mode) (Figures 3 and 2)       | 2.0<br>4.5<br>6.0 | 250<br>50<br>43   | 315<br>63<br>54   | 375<br>75<br>64   | ns   |

| tTLH,<br>tTHL    | Maximum Output Transition Time, Any Output<br>(Figures 1 and 2)                        | 2.0<br>4.5<br>6.0 | 75<br>15<br>13    | 95<br>19<br>16    | 110<br>22<br>19   | ns   |

| Cin              | Maximum Input Capacitance                                                              |                   | 10                | 10                | 10                | pF   |

#### NOTES:

- 1. For propagation delays with loads other than 50 pF, see Chapter 4 subject listing on page 4-2.

- 2. Information on typical parametric values can be found in Chapter 4.

| C <sub>PD</sub> | Power Dissipation Capacitance (Per Package)                         | Typical @ 25°C, V <sub>CC</sub> =5.0 V |    |

|-----------------|---------------------------------------------------------------------|----------------------------------------|----|

|                 | Used to determine the no-load dynamic power consumption:            |                                        |    |

|                 | $P_D = C_{PD} V_{CC}^2 f + I_{CC} V_{CC}$                           | TBD                                    | pF |

|                 | For load considerations, see Chapter 4 subject listing on page 4-2. |                                        |    |

## TIMING REQUIREMENTS (Input $t_f = t_f = 6 \text{ ns}$ )

|                                 |                                                                          |                   | Projected Limit    |                    |                    |      |

|---------------------------------|--------------------------------------------------------------------------|-------------------|--------------------|--------------------|--------------------|------|

| Symbol                          | Parameter                                                                | V <sub>CC</sub>   | 25°C to<br>-55°C   | ≤85°C              | ≤ 125°C            | Unit |

| t <sub>su</sub>                 | Minimum Setup Time, S0-S4 or M0-M2 to START (Figure 3)                   | 2.0<br>4.5<br>6.0 | 100<br>20<br>17    | 125<br>25<br>21    | 150<br>30<br>26    | ns   |

| t <sub>d</sub>                  | Minimum Delay Time, START to OUT or OUT (Figure 3)                       | 2.0<br>4.5<br>6.0 | 500<br>100<br>85   | 625<br>125<br>106  | 750<br>150<br>128  | ns   |

| t <sub>b</sub>                  | Minimum Burst Time, Count Control<br>(Figure 3)                          | 2.0<br>4.5<br>6.0 | 500<br>100<br>85   | 625<br>125<br>106  | 750<br>150<br>128  | ns   |

| t <sub>w</sub>                  | Minimum Pulse Width, START (Figure 3)                                    | 2.0<br>4.5<br>6.0 | 80<br>16<br>14     | 100<br>20<br>17    | 120<br>24<br>20    | ns   |

| tw                              | Minimum Pulse Width, OSC IN (Figure 1)                                   | 2.0<br>4.5<br>6.0 | 80<br>16<br>14     | 100<br>20<br>17    | 120<br>24<br>20    | ns   |

| t <sub>w</sub>                  | Minimum Pulse Width, OUT or OUT (One-Shot Mode) (Figure 3)               | 2.0<br>4.5<br>6.0 | 500<br>100<br>85   | 625<br>125<br>106  | 750<br>150<br>128  | ns   |

| tw                              | Minimum Pulse Width, OUT or OUT (Delayed Multiple Pulse Mode) (Figure 3) | 2.0<br>4.5<br>6.0 | 125<br>25<br>21    | 155<br>31<br>26    | 190<br>38<br>32    | ns   |

| t <sub>r</sub> , t <sub>f</sub> | Maximum Input Rise and Fall Times, Except OSC IN or START                | 2.0<br>4.5<br>6.0 | 1000<br>500<br>400 | 1000<br>500<br>400 | 1000<br>500<br>400 | ns   |

| t <sub>r</sub> , t <sub>f</sub> | Maximum Input Rise and Fall Times, OSC IN or START (Figure 1)            | -                 |                    | No Limit           |                    | _    |

NOTE: Information on typical parametric values can be found in Chapter 4 subject listing on page 4-2.

## MOTOROLA HIGH-SPEED CMOS LOGIC DATA

#### PIN DESCRIPTIONS

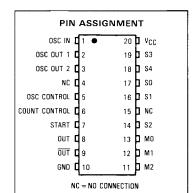

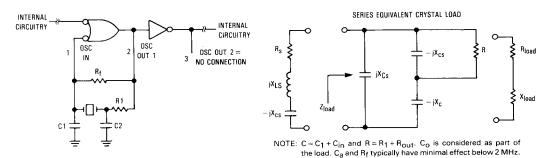

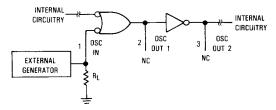

#### OSC IN, OSC OUT 1, OSC OUT 2 (Pins 1, 2, 3)

These pins, used in conjunction with external components, form an on-chip reference oscillator. The frequency of this oscillator and the number of counters selected determines the amount of time-out desired (see Figures 7 and 8). An external generator may be used instead of the internal oscillator. In this case, the signal should swing from ground to VCC and should be fed into OSC IN. OSC OUT 1 and OSC OUT 2 must be left floating (see Figure 9). With the crystal oscillator configuration shown in Figure 7, OSC OUT 2 must be left opencircuited.

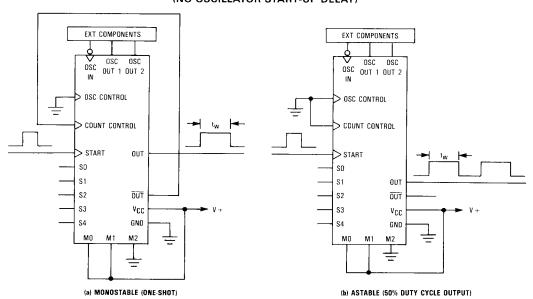

#### OSC CONTROL (Pin 5)

This pin is used to enable or disable the oscillator. A low-to-high transition on this pin resets all counters and shuts down the oscillator. This puts the device into a low-power standby condition.

#### **COUNT CONTROL (Pin 6)**

A low-to-high transition on this pin also resets all counters. The oscillator continues to run, but the counters do not increment. This condition eliminates oscillator start-up delay time.

#### START (Pin 7)

A low-to-high transition on this pin causes the oscillator to start up, if previously disabled, and timing begins. The START input is Schmitt-triggered to allow for slow rise and fall input pulses. When using only one or two stages of delay, it is recommended that an external time base, synchronized with the start pulse, be used. With no synchronization, a start pulse occurring when the clock is high produces a different initial delay than when the start pulse occurs when the clock is low. This effect causes less error as more delay stages are selected.

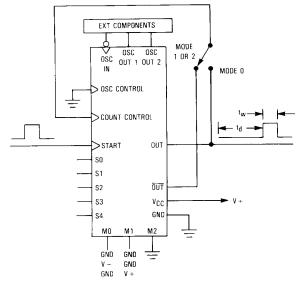

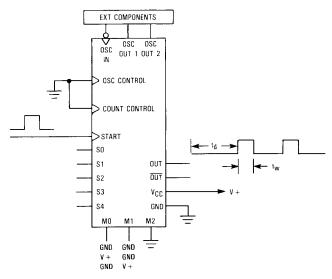

#### M0, M1, M2 (Pins 13, 12, 11)

Mode inputs. These pins determine the timer's mode of operation (see Table 1).

#### S0, S1, S2, S3, S4 (Pins 17, 16, 14, 19, 18)

Select inputs. These pins select the exact divide ratio desired (see Table 2).

#### OUT (Pin 8)

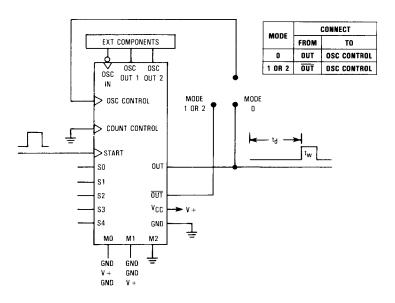

This pin is the output of the timer. OUT can be fed back to either OSC CONTROL or COUNT CONTROL to inhibit counting.

#### OUT (Pin 9)

OUT is the complement of OUT. OUT can also be fed back to OSC CONTROL or COUNT CONTROL to inhibit counting.

#### NC (Pins 4, 15)

No connect pins. These pins are not connected internally.

Table 1. Output Mode Selection Table

| Mode Inputs |    | de Inputs |    |                                                                                     |            |  |

|-------------|----|-----------|----|-------------------------------------------------------------------------------------|------------|--|

| Mode        | M2 | М1        | M0 | Output Pulse Description                                                            | Figure     |  |

| 0           | 0  | 0         | 0  | Delayed Pulse (t <sub>w</sub> = 1/2f)                                               | 11, 13     |  |

| 1           | 0  | 0         | 1  | Delayed Pulse (t <sub>W</sub> = 2/f)                                                | 11, 13     |  |

| 2           | 0  | 1         | 0  | Delayed Pulse (t <sub>W</sub> = 8/f)                                                | 11, 13     |  |

| 3           | 0  | 1         | 1  | Monostable Multivibrator                                                            | 10         |  |

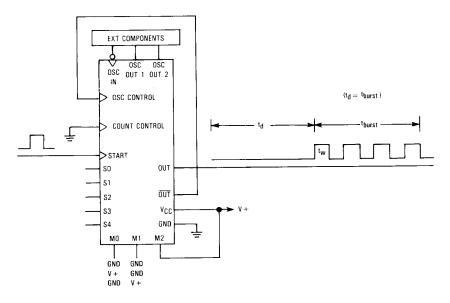

| 4           | 1  | 0         | 0  | Delayed Burst Pulse (t <sub>W</sub> = 1/2f) t <sub>delay</sub> = t <sub>burst</sub> | 14         |  |

| 5           | 1  | 0         | 1  | Delayed Burst Pulse (t <sub>w</sub> = 2/f) t <sub>delay</sub> = t <sub>burst</sub>  | 14         |  |

| 6           | 1  | 1         | 0  | Delayed Burst Pulse (t <sub>w</sub> = 8/f) t <sub>delay</sub> = t <sub>burst</sub>  | 14         |  |

| 7           | 1  | 1         | 1  | Programmable Counter or Test Mode (50% Output Duty Cycle)                           | 12, 15, 17 |  |

Table 2. Select Divide Range

|    | Se | lect Inp | Number of Counter |    |                                            |

|----|----|----------|-------------------|----|--------------------------------------------|

| S4 | S3 | S2       | S1                | S0 | Stages Selected, N<br>( ÷ 2 <sup>N</sup> ) |

| 0  | 0  | 0        | 0                 | 0  | 1                                          |

| 0  | 0  | 0        | 0                 | 1  | 2                                          |

| 0  | 0  | 0        | 1                 | 0  | 3                                          |

| 0  | 0  | 0        | 1                 | 1  | 4                                          |

| 0  | 0  | 1        | 0                 | 0  | 5                                          |

| 0  | 0  | 1        | 0                 | 1  | 6                                          |

| 0  | 0  | 1        | 1                 | 0  | 7                                          |

| 0  | 0  | 1        | 1                 | 1  | 8                                          |

| 0  | 1  | 0        | 0                 | 0  | 9                                          |

| 0  | 1  | 0        | 0                 | 1  | 10                                         |

| 0  | 1  | 0        | 1                 | 0  | 11                                         |

| 0  | 1  | 0        | 1                 | 1  | 12                                         |

| 0  | 1  | 1        | 0                 | 0  | 13                                         |

| 0  | 1  | 1        | 0                 | 1  | 14                                         |

| 0  | 1  | 1        | 1                 | 0  | 15                                         |

| 0  | 1  | 1        | 1                 | 1  | 16                                         |

|    | Se | lect Inp | Number of Counter |    |                                            |

|----|----|----------|-------------------|----|--------------------------------------------|

| S4 | S3 | S2       | <b>S</b> 1        | S0 | Stages Selected, N<br>( ÷ 2 <sup>N</sup> ) |

| 1  | 0  | 0        | 0                 | 0  | 17                                         |

| 1  | 0  | 0        | 0                 | 1  | 18                                         |

| 1  | 0  | 0        | 1                 | 0  | 19                                         |

| 1  | 0  | 0        | 1                 | 1  | 20                                         |

| 1  | 0  | 1        | 0                 | 0  | 21                                         |

| 1  | 0  | 1        | 0                 | 1  | 22                                         |

| 1  | 0  | 1        | 1                 | 0  | 23                                         |

| 1  | 0  | 1        | 1                 | 1  | 24                                         |

| 1  | 1  | 0        | 0                 | 0  | 1*                                         |

| 1  | 1  | 0        | 0                 | 1  | 2*                                         |

| 1  | 1  | 0        | 1                 | 0  | 3*                                         |

| 1  | 1  | 0        | 1                 | 1  | 4*                                         |

| 1  | 1  | 1        | 0                 | 0  | 5*                                         |

| 1  | 1  | 1        | 0                 | 1  | 6*                                         |

| 1  | 1  | 1        | 1                 | 0  | 7*                                         |

| 1  | 1  | 1        | 1                 | 1  | 8*                                         |

<sup>\*</sup>Configured internally such that the 24 stage counter is parallel clocked as three 8-bit counters. This allows for shorter incoming inspection testing times.

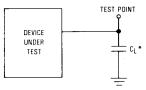

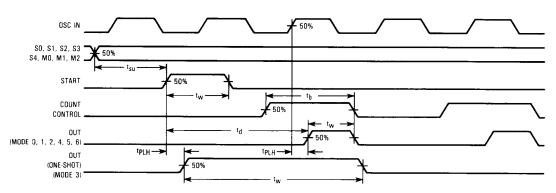

Figure 1. Switching Waveforms

\*Includes all probe and jig capacitance.

Figure 2. Test Circuit

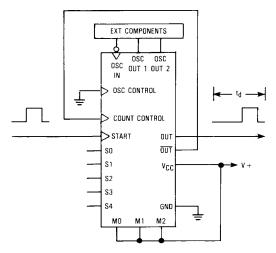

Figure 3. Functional Timing Diagram

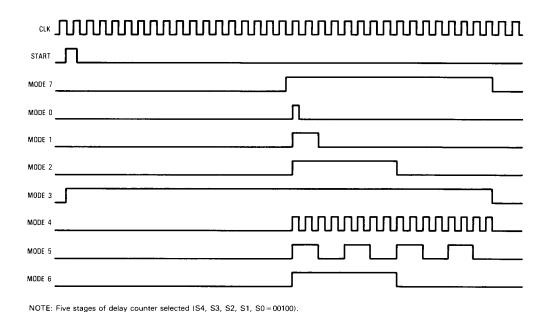

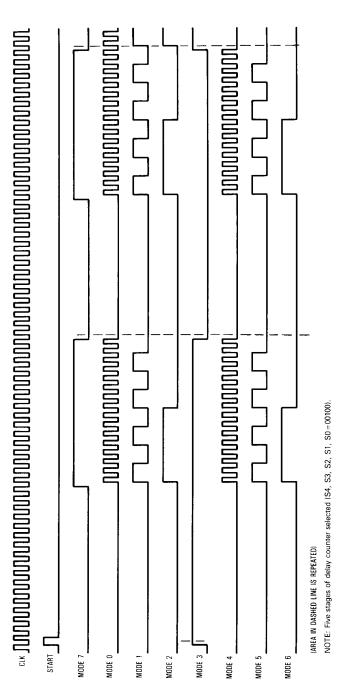

Figure 4. Timing Diagram Using Feedback

MOTOROLA HIGH-SPEED CMOS LOGIC DATA

5-636

This Material Copyrighted By Its Respective Manufacturer

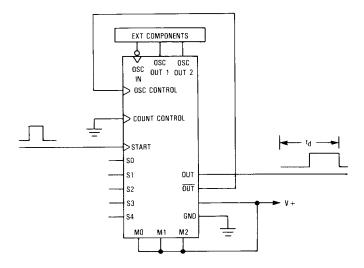

Figure 5. Timing Diagram Using No Feedback

MOTOROLA HIGH-SPEED CMOS LOGIC DATA

MOTOROLA HIGH-SPEED CMOS LOGIC DATA

## OSCILLATOR DESIGN INFORMATION

Figure 7. Pierce Oscillator

#### EQUIVALENT CIRCUIT FOR CRYSTAL NEAR RESONANCE

NOTE: Values are supplied by crystal manufacturer (parallel resonant crystal).

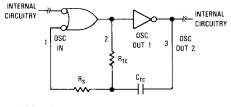

10  $R_{tc} > R_S > 2 R_{tc}$ 400 Hz  $\leq$  f  $\leq$  400 kHz:

$f = \frac{1}{2.3~R_{tc}C_{tc}} (f \text{ in Hz, } R_{tc} \text{ in ohms, } C_{tc} \text{ in farads})$

The formula may vary for other frequencies.

Figure 8. RC Oscillator

Figure 9. External Generator

#### MOTOROLA HIGH-SPEED CMOS LOGIC DATA

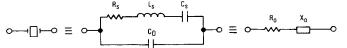

The following procedure applies for oscillators operating below 2 MHz where Z is a resistor R<sub>1</sub>. Above 2 MHz, additional impedance elements may be considered: Cout and Ca of the amp, feedback resistor Rf, and amplifier phase shift error from 180°.

Step 1: Calculate the equivalent series circuit of the crystal at the frequency of oscillation.

$$Z_{e} = \frac{-jX_{CO}(R_{s} + jX_{Ls} - jX_{Cs})}{-jX_{CO} + R_{s} + jX_{Ls} - jX_{Cs}} = R_{e} + jX_{e}$$

Reactance jXe should be positive, indicating that the crystal is operating as an inductive reactance at the oscillation frequency. The maximum R<sub>S</sub> for the crystal should be used in the equation.

Step 2: Determine  $\beta$ , the attenuation, of the feedback network. For a closed loop gain of 2,  $A_V\beta = 2$ ,  $\beta = 2/A_V$  where Ay is the gain of the HC9000 amplifier.

Step 3: Determine the manufacturer's loading capacitance. For example: a manufacturer may specify an external load capacitance of 32 pF at the required frequency.

Step 4: Determine the required Q of the system, and calculate Rioad. For example: a manufacturer specifies a crystal Q of 100,000. The desired in-circuit Q is set at 20% below crystal Q or 80,000. Then  $R_{load} = (2\pi f_0 L_s/Q) - R_s$ where L<sub>S</sub> and R<sub>S</sub> are crystal parameters.

Step 5: Simultaneously solve, using a computer, equations 1. 2. and 3.

$$\beta = \frac{X_c * X_{c2}}{R * R_e + X_{c2}(X_e - X_c)}$$

(with feedback phase shift = 180°) (1)

$$X_e = X_{c2} + X_c + \frac{R_e X_{c2}}{R} = X_{cload}$$

(where the loading capacitor is an external load not including  $C_c$ ) (2)

$$R_{load} = \frac{RX_{co}X_{c2}((X_c + X_{c2})(X_c + X_{co}) - X_c(X_c + X_{co} + X_{c2}))}{X_{c2}^2(X_c + X_{co})^2 + R^2(X_c + X_{co} + X_{c2})^2} \qquad (3)$$

Here R=R<sub>out</sub>+R<sub>1</sub>. R<sub>out</sub> is amp output resistance, R<sub>1</sub> is Z. The C corresponding to  $X_C$  is given by  $C=C_1+C_{\rm in}$ .

Alternately, pick a value for  $R_1$  (i.e. let  $R_1 = R_S$ ). Solve Equations 1 and 2 for C<sub>1</sub> and C<sub>2</sub>. Use Equation 3 and the fact  $Q = 2\pi f_0 L_s / (R_s + R_{load})$  to find in-circuit Q. If Q is not satisfactory pick another value for R1 and repeat the procedure.

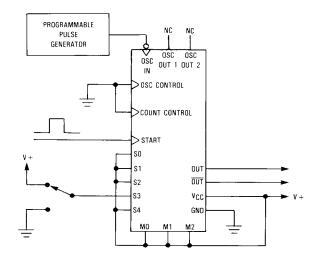

#### APPLICATIONS INFORMATION APPLICATIONS WITH FREE-RUN OSCILLATOR (NO OSCILLATOR START-UP DELAY)

Figure 10. Multivibrator Configurations

## MOTOROLA HIGH-SPEED CMOS LOGIC DATA

(a) DELAYED SINGLE PULSE

(b) DELAYED MULTIPLE PULSE

Figure 11. Delayed Pulse Configurations

Figure 12. Programmable Timer

## LOW STANDBY POWER APPLICATIONS (OSCILLATOR IS STOPPED WHEN IN STANDBY)

Figure 13. Delayed Single-Pulse Configuration

Figure 14. Burst Delayed-Pulse Configuration

Figure 15. Programmable Timer

Figure 16. Delayed Multiple Pulse Configuration (4-Pulse Configured)

Figure 17. Test Mode (28 Divider Configuration)

## NOTE TEST MODE

Setting M0, M1, M2 to a logic level 1 selects the programmable counter option. Setting S3 and S4 to a logic level 1 divides the  $2^{24}$  stage counter into three 8-stage counters. These three 8-stage counters are clocked in parallel. Setting S0, S1, S2, to a logic level 1 sets the counters to divide by  $2^{8}$  (256). Applying a start pulse, and then clocking OSC IN 255 times sets all flip flop stages and OUT to a high level. After setting OUT to a high level. After setting OUT to a high level, S3 is set to a logic level 0 and the counters revert back to  $2^{24}$  operation. Clocking OSC IN one more time causes a 0 to ripple through the counters and OUT goes from a high to a low level (see Figure 17). This method of exercising the delay counter is faster than clocking in  $2^{24}$  clock pulses.