# ADC0804/D, ADC0804/W 8-Bit μP-Compatible A/D Converters

## GENERAL DESCRIPTION

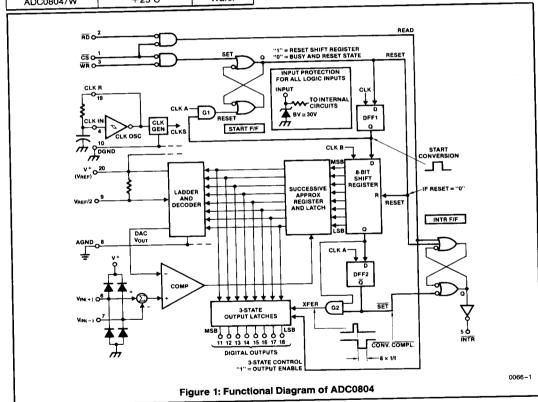

The Intersil ADC0804 is a CMOS 8-bit successive approximation A/D converter which uses a modified potentiometric ladder and is designed to operate with the 8048 control via three-state outputs. The converter appears to the processor as a memory location or I/O port, hence no interfacing logic is required.

The differential analog voltage input has good commonmode-rejection, and permits offsetting the analog zero-input-voltage value. In addition, the voltage reference input can be adjusted to allow encoding any smaller analog voltage span to the full 8 bits of resolution.

## ORDERING INFORMATION

| Part Number | Temperature | Form  |

|-------------|-------------|-------|

| ADC0804/D   | + 25°C      | Dice  |

| ADC0804/W   | + 25°C      | Wafer |

#### **FEATURES**

- 80C48 and 80C80/85 Bus Compatible—No Interfacing Logic Required

- Conversion Time < 100 μs</li>

- Easy Interface to Most Microprocessors

- Will Operate in a "Stand Alone" Mode

- Differential Analog Voltage Inputs

- Works With Bandgap Voltage References

- TTL Compatible Inputs and Outputs

- On-Chip Clock Generator

- 0V to 5V Analog Voltage Input Range (Single +5V Supply)

- No Zero-Adjust Required

INTERSIL'S SOLE AND EXCLUSIVE WARRANTY OBLIGATION WITH RESPECT TO THIS PRODUCT SHALL BE THAT STATED IN THE WARRANTY ARTICLE OF THE CONDITION OF SALE.

THE WARRANTY SHALL BE EXCLUSIVE AND SHALL BE IN LIEU OF ALL OTHER WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING THE IMPLIED WARRANTIES OF

MERCHANTABILITY AND FITNESS FOR A PARTICULAR USE.

NOTE: All typical values have been characterized but are not tested.

## ADC0804/D, ADC0804/W

### **ABSOLUTE MAXIMUM RATINGS**

#### **OPERATING RATINGS**

Supply Voltage Range ......4.5V to 6.3V

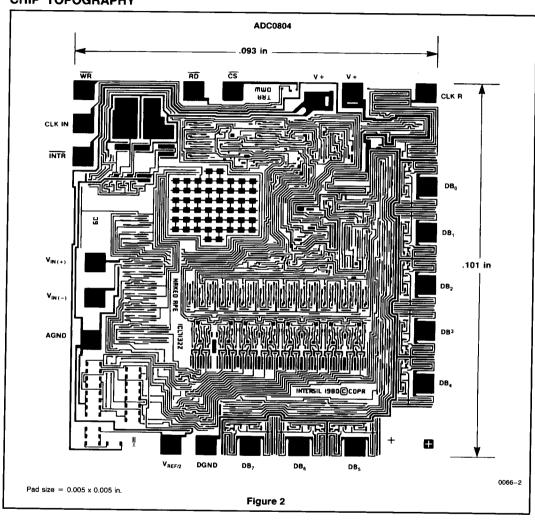

### **CHIP TOPOGRAPHY**

INTERSIL'S SOLE AND EXCLUSIVE WARRANTY OBLIGATION WITH RESPECT TO THIS PRODUCT SHALL BE THAT STATED IN THE WARRANTY ARTICLE OF THE CONDITION OF SALE. THE WARRANTY SHALL BE EXCLUSIVE AND SHALL BE IN LIEU OF ALL OTHER WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR USE.

NOTE: All typical values have been characterized but are not tested.

# ADC0804/D, ADC0804/W

##

## ELECTRICAL CHARACTERISTICS (Notes 1 and 5)

Converter Specifications:  $V^+ = 5V$ ,  $V_{REF}/2 = 2.500V$ ,  $T_A = 25^{\circ}C$ , and  $f_{CLK} = 640$  kHz unless otherwise stated

| Parameter                            | Test Conditions           | Min | Max | Units |

|--------------------------------------|---------------------------|-----|-----|-------|

| ADC0804:<br>Total Unadjusted Error   | Completely Unadjusted     |     | ±1  | LSB   |

| V <sub>RFF</sub> /2 Input Resistance | Input Resistance at Pin 9 | 0.8 |     | kΩ    |

## DC ELECTRICAL CHARACTERISTICS

Digital Levels and DC Specifications: V+ = 5V, T<sub>A</sub> = 25°C, unless otherwise noted

| Symbol             | Parameter                                                              | Test Conditions                                                                                        | Min | Max | Units    |

|--------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----|-----|----------|

|                    | INPUTS (Note 4)                                                        |                                                                                                        |     |     |          |

| V <sup>+</sup> CLK | CLK IN (Pin 4) Positive Going<br>Threshold Voltage                     |                                                                                                        | 2.7 | 3.5 | ٧        |

| V- CLK             | CLK IN (Pin 4) Negative Going<br>Threshold Voltage                     |                                                                                                        | 1.5 | 2.1 | V        |

| V <sub>H</sub>     | CLK IN (Pin 4) Hysteresis<br>(V+ <sub>CLK</sub> )-(V- <sub>CLK</sub> ) |                                                                                                        | 0.6 | 2.0 | ٧        |

| +                  | Supply Current (Includes<br>Ladder Current)                            | $f_{CLK} = 640 \text{ kHz},$ $T_A = +25^{\circ}\text{C} \text{ and } \overline{\text{CS}} = \text{HI}$ |     | 2.5 | mA       |

| DATA OUT           | PUTS AND INTR                                                          |                                                                                                        |     |     |          |

| V <sub>OL</sub>    | Logical "0" Output Voltage                                             | l <sub>o</sub> = 1.6 mA<br>V+ = 4.75V                                                                  |     | 0.4 | ٧        |

| V <sub>OH</sub>    | Logical "1" Output Voltage                                             | $I_0 = -360 \mu\text{A}$ $V^+ = 4.75V$                                                                 | 2.4 |     | ٧        |

| I <sub>LO</sub>    | 3-State Disabled Output<br>Leakage (All Data Buffers)                  | $V_{OUT} = 0V$ $V_{OUT} = 5V$                                                                          | -3  | 3   | μA<br>μA |

| ISOURCE            | Output Short Circuit Current                                           | V <sub>OUT</sub> Short to GND, T <sub>A</sub> = +25°C                                                  | 4.5 |     | mA       |

| ISINK              | Output Short Circuit Current                                           | V <sub>OUT</sub> Short to V <sup>+</sup> , T <sub>A</sub> = 25°C                                       | 9.0 |     | mA       |

NOTE 1: All voltages are measured with respect to GND, unless otherwise specified. The separate AGND point should always be wired to the DGND, being careful to avoid ground loops.

- 2: For V<sub>IN(+)</sub> ≥ V<sub>IN(+)</sub> the digital output code will be 0000 0000. Two on-chip diodes are tied to each analog input which will forward conduct for analog input voltages one diode drop below ground or one diode drop greater than the V<sup>+</sup> supply. Be careful, during testing at low V<sup>+</sup> levels (4.5V), as high level analog inputs (5V) can cause this input diode to conduct, especially at elevated temperatures, and cause errors for analog inputs near full-scale. As long as the analog V<sub>IN</sub> does not exceed the supply voltage by more than 50 mV, the output code will be correct. To achieve an absolute 0V to 5V input voltage range will therefore require a minimum supply voltage of 4.950V over temperature variations, initial tolerance and loading.

- 3: With an asynchronous start pulse, up to 8 clock periods may be required before the internal clock phases are proper to start the conversion process.

- 4: CLK IN (Pin 4) is the input of a Schmitt trigger circuit and is therefore specified separately.

- 5: None of these A/Ds requires a zero-adjust. However, if an all zero code is desired for an analog input other than 0.0V, or if a narrow full-scale span exists (for example: 0.5V to 4.0V full-scale) the V<sub>IN(-)</sub> input can be adjusted to achieve this.

INTERSIL'S SOLE AND EXCLUSIVE WARRANTY OBLIGATION WITH RESPECT TO THIS PRODUCT SHALL BE THAT STATED IN THE WARRANTY ARTICLE OF THE CONDITION OF SALE.

THE WARRANTY SHALL BE EXCLUSIVE AND SHALL BE IN LIEU OF ALL OTHER WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING THE IMPLIED WARRANTIES OF

MERCHANTABILITY AND FITNESS FOR A PARTICULAR USE.

NOTE: All typical values have been characterized but are not tested.