# GSM/DCS1800/PCS1900 Voiceband Baseband Codec AD6421

#### FEATURES

| LATOREO                                        |

|------------------------------------------------|

| Complete Analog/Digital Interface for          |

| Voiceband Input/Output-Signals                 |

| Baseband Input/Output-Signals                  |

| Auxiliary/Control-Signals                      |

| Voiceband Codec                                |

| Complete Linear Coded Codec                    |

| Two Channel 16-Bit A/D Converter with Filter   |

| Two Channel 16-Bit D/A Converter with Filter   |

| Dedicated Buzzer Output                        |

| 32 $\Omega$ Speaker Drive Capability           |

| Programmable Gain on Input and Output          |

| Serial Voice Port                              |

| Baseband Codec                                 |

| Differential I and Q Inputs/Outputs            |

| On-Chip Burst Store                            |

| GMSK Modulator                                 |

| Two 10-Bit D/A Converters                      |

| Two 15-Bit A/D Converters                      |

| On-Chip FIR-Filter                             |

| Serial Baseband Port                           |

| Auxiliary Section                              |

| Support for AGC, AFC and Power Ramping         |

| 10-Bit AGC D/A Converter                       |

| 13-Bit AFC D/A Converter                       |

| 10-Bit RAMP D/A Converter with 4X Interpolator |

| On-Chip RAMP-RAM                               |

| Four Channel 10-Bit A/D-Converter              |

| Serial Auxiliary Port                          |

| Individual Power Down Features                 |

| JTAG Interface                                 |

| 2.7V to 3.3V Operation                         |

| 64-Lead TQFP                                   |

|                                                |

#### APPLICATIONS GSM/ DCS1800/ PCS1900 Mobile Radios

#### GENERAL DESCRIPTION

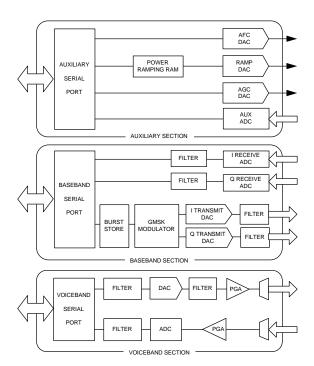

The AD6421 is a monolithic Voiceband Baseband Codec (VBC) that combines on a single chip all A/D and D/A converters that are necessary to build a complete GSM, DCS1800 or PCS1900 mobile radio. It contains complete codecs for voiceband and baseband signals as well as D/A converters to control the radio subsystem and an auxiliary A/D converter for monitoring purposes.

The voiceband codec is a complete analog front-end which can interface directly with a microphone and speaker. For interfacing with external car-kits, separate input and output channels are provided. Input and output gains are user programmable for maximum flexibility.

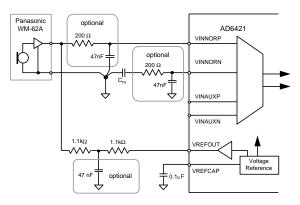

#### Functional Block Diagram

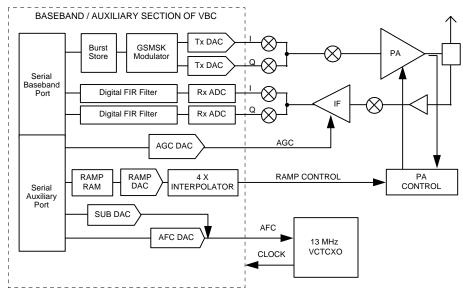

The baseband codec is a complete low power, two channel, input/output port with signal conditioning. The transmit path consists of an on-chip burst store, a GMSK modulator and two high speed DACs with output reconstruction filters. The receive path consists of two 15 bit Sigma Delta A/D converters which include high performance digital filters for RF-channel selection.

The auxiliary section of the VBC consists of D/A converters for Automatic Frequency Control (AFC), Automatic Gain Control (AGC) and control of the transmit-burst envelope (RAMP). Additionally, the VBC provides an auxiliary A/D converter which can be used to monitor four analog signals.

Various power down options as well as the low supply voltage allow the design of mobile radios having minimal power consumption.

#### ORDERING GUIDE

| Model     | Temperature Range                  | Package      |

|-----------|------------------------------------|--------------|

| AD6421AST | $-40^{\circ}$ C to $+85^{\circ}$ C | 64-Lead TQFP |

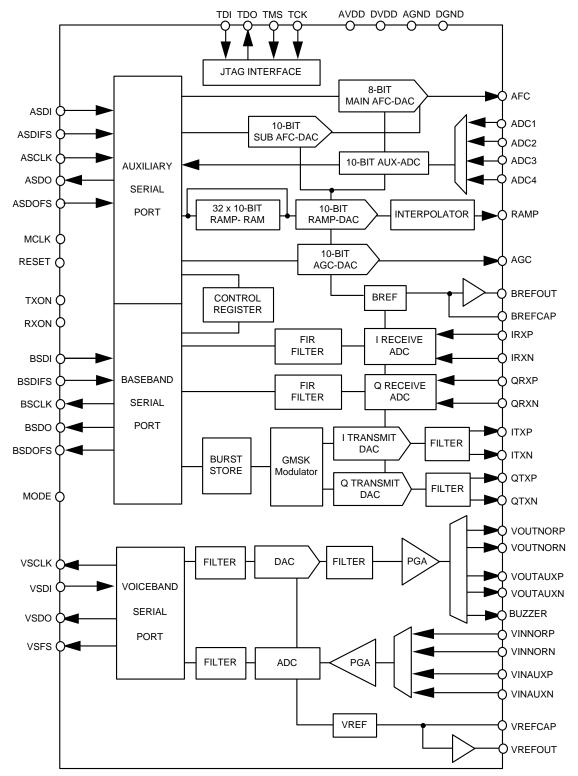

Figure 1. Detailed Block Diagram

### **Table of Contents**

| GENERAL DESCRIPTION 1                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN FUNCTIONALITY                                                                                                                                                                                                                                                                                                                                                          |

| CONTROL                                                                                                                                                                                                                                                                                                                                                                    |

| Control Registers6                                                                                                                                                                                                                                                                                                                                                         |

| Writing and Reading Control Registers7                                                                                                                                                                                                                                                                                                                                     |

| Reset7                                                                                                                                                                                                                                                                                                                                                                     |

| Timing Conventions7                                                                                                                                                                                                                                                                                                                                                        |

| BASEBAND SECTION                                                                                                                                                                                                                                                                                                                                                           |

| Baseband Control Register                                                                                                                                                                                                                                                                                                                                                  |

| Baseband Transmit Section8                                                                                                                                                                                                                                                                                                                                                 |

| Burst Store                                                                                                                                                                                                                                                                                                                                                                |

| GMSK Modulator                                                                                                                                                                                                                                                                                                                                                             |

| Transmit Offset Calibration                                                                                                                                                                                                                                                                                                                                                |

| User-Calibration                                                                                                                                                                                                                                                                                                                                                           |

| Output Timing                                                                                                                                                                                                                                                                                                                                                              |

| Transmit DACs & Output Filters                                                                                                                                                                                                                                                                                                                                             |

| Output Bias Voltage                                                                                                                                                                                                                                                                                                                                                        |

| Output Interface                                                                                                                                                                                                                                                                                                                                                           |

| Baseband Receive Section10                                                                                                                                                                                                                                                                                                                                                 |

| Analog Input & Switched Capacitor Filter10                                                                                                                                                                                                                                                                                                                                 |

| Sigma-Delta ADC                                                                                                                                                                                                                                                                                                                                                            |

| Digital Filter                                                                                                                                                                                                                                                                                                                                                             |

| Receive Offset Calibration                                                                                                                                                                                                                                                                                                                                                 |

| Receive and Offset Canoration Timing                                                                                                                                                                                                                                                                                                                                       |

| Output Timing                                                                                                                                                                                                                                                                                                                                                              |

| Output Timing                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                            |

| BASEBAND REFERENCE                                                                                                                                                                                                                                                                                                                                                         |

| BASEBAND REFERENCE                                                                                                                                                                                                                                                                                                                                                         |

| BASEBAND REFERENCE                                                                                                                                                                                                                                                                                                                                                         |

| BASEBAND REFERENCE    13      AUXILIARY SECTION    14      Auxiliary Control Register    14      RAMP Control    14      RAMP-RAM    14      RAMP-DAC and Interpolator    14                                                                                                                                                                                               |

| BASEBAND REFERENCE       13         AUXILIARY SECTION       14         Auxiliary Control Register       14         RAMP Control       14         RAMP-RAM       14         RAMP-DAC and Interpolator       14         RAMP Timing       15                                                                                                                                 |

| BASEBAND REFERENCE       13         AUXILIARY SECTION       14         Auxiliary Control Register       14         RAMP Control       14         RAMP-RAM       14         RAMP-DAC and Interpolator       14         RAMP Timing       15         AGC Control       15                                                                                                    |

| BASEBAND REFERENCE13AUXILIARY SECTION14Auxiliary Control Register14RAMP Control14RAMP-RAM14RAMP-DAC and Interpolator14RAMP Timing15AGC Control15AFC Control15                                                                                                                                                                                                              |

| BASEBAND REFERENCE13AUXILIARY SECTION14Auxiliary Control Register14RAMP Control14RAMP-RAM14RAMP-DAC and Interpolator14RAMP Timing15AGC Control15AFC Control15Auxiliary ADC16                                                                                                                                                                                               |

| BASEBAND REFERENCE       13         AUXILIARY SECTION       14         Auxiliary Control Register       14         RAMP Control       14         RAMP-RAM       14         RAMP-DAC and Interpolator       14         RAMP Timing       15         AGC Control       15         AFC Control       15         Auxiliary ADC       16         Auxiliary Serial Port       16 |

| BASEBAND REFERENCE13AUXILIARY SECTION14Auxiliary Control Register14RAMP Control14RAMP-RAM14RAMP-DAC and Interpolator14RAMP Timing15AGC Control15AFC Control15AFC Control15Auxiliary ADC16Auxiliary Serial Port16VOICEBAND SECTION17                                                                                                                                        |

| BASEBAND REFERENCE13AUXILIARY SECTION14Auxiliary Control Register14RAMP Control14RAMP-RAM14RAMP-DAC and Interpolator14RAMP Timing15AGC Control15AFC Control15AFC Control16Auxiliary Serial Port16VOICEBAND SECTION17Voiceband Control Registers17                                                                                                                          |

| BASEBAND REFERENCE13AUXILIARY SECTION14Auxiliary Control Register14RAMP Control14RAMP-RAM14RAMP-DAC and Interpolator14RAMP Timing15AGC Control15AFC Control15AFC Control15Auxiliary ADC16Auxiliary Serial Port16VOICEBAND SECTION17                                                                                                                                        |

| BASEBAND REFERENCE13AUXILIARY SECTION14Auxiliary Control Register14RAMP Control14RAMP-RAM14RAMP-DAC and Interpolator14RAMP Timing15AGC Control15AFC Control15AFC Control16Auxiliary ADC16Auxiliary Serial Port16VOICEBAND SECTION17Voiceband Control Registers17ADC Section18                                                                                              |

| BASEBAND REFERENCE13AUXILIARY SECTION14Auxiliary Control Register14RAMP Control14RAMP-RAM14RAMP-DAC and Interpolator14RAMP Timing15AGC Control15AFC Control15AFC Control16Auxiliary ADC16Auxiliary Serial Port16VOICEBAND SECTION17Voiceband Control Registers17Voiceband Reference17ADC Section18Analog Inputs18                                                          |

| BASEBAND REFERENCE13AUXILIARY SECTION14Auxiliary Control Register14RAMP Control14RAMP-RAM14RAMP-DAC and Interpolator14RAMP Timing15AGC Control15AFC Control15AFC Control16Auxiliary ADC16Auxiliary Serial Port16VOICEBAND SECTION17Voiceband Control Registers17ADC Section18Analog Inputs18ADC19                                                                          |

| BASEBAND REFERENCE13AUXILIARY SECTION14Auxiliary Control Register14RAMP Control14RAMP-RAM14RAMP-DAC and Interpolator14RAMP Timing15AGC Control15AFC Control15AFC Control16Auxiliary ADC16Auxiliary Serial Port16VOICEBAND SECTION17Voiceband Control Registers17Voiceband Reference17ADC Section18Analog Inputs18                                                          |

| Analog Smoothing Filter and PGA<br>Output Amplifiers | . 19<br>. 19 |

|------------------------------------------------------|--------------|

| Voiceband Serial Port<br>Normal Mode                 |              |

| SPECIFICATION TERMINOLOGY                            |              |

|                                                      |              |

| Baseband Codec                                       |              |

| Voiceband Codec                                      |              |

| SPECIFICATIONS                                       |              |

| General                                              |              |

| Absolute Maximum Ratings                             |              |

| Baseband Receive Section                             |              |

| Baseband Transmit Section                            |              |

| AGC-DAC, RAMP-DAC                                    |              |

| AFC-DAC, Auxiliary ADC                               | . 28         |

| Voiceband Section                                    |              |

| Voiceband ADC                                        | . 30         |

| Voiceband DAC                                        | . 31         |

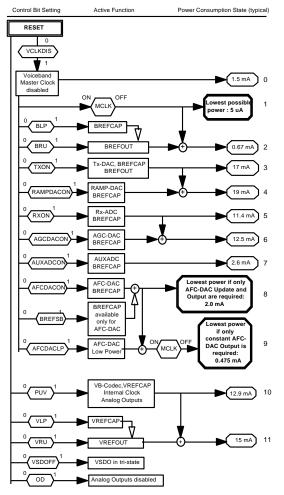

| POWER CONSUMPTION                                    | . 32         |

| Baseband & Auxiliary Section Powerdown               |              |

| Reference                                            |              |

| Converters<br>Clock                                  |              |

| Voiceband Section Powerdown                          |              |

| Power Consumption                                    |              |

| TIMING CHARACTERISTICS                               |              |

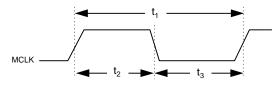

| Clocks                                               |              |

| Master Clock                                         |              |

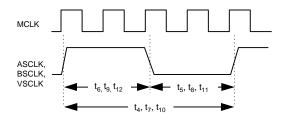

| Serial Port Clocks                                   |              |

| Baseband Serial Port                                 | . 35         |

| Auxiliary Serial Port                                | . 36         |

| Voiceband Serial Port                                | . 37         |

| JTAG                                                 | . 38         |

| APPLICATION NOTES                                    | . 39         |

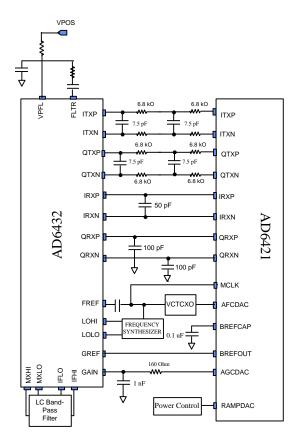

| Interface to the Radio Section                       |              |

| Interface to the AD6432                              |              |

| Receive Interface                                    |              |

| Transmit Filter                                      |              |

| Microphone Interface                                 |              |

| Modulating Consecutive Ones                          |              |

| Grounding and Layout                                 |              |

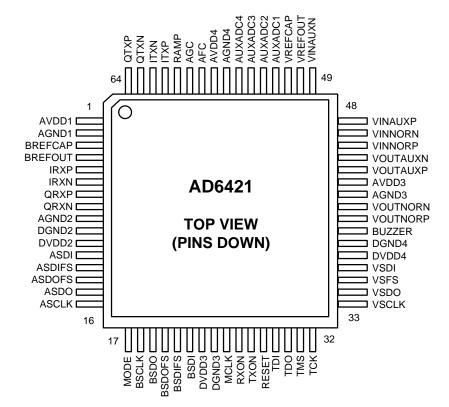

| AD6421 PIN LOCATION                                  |              |

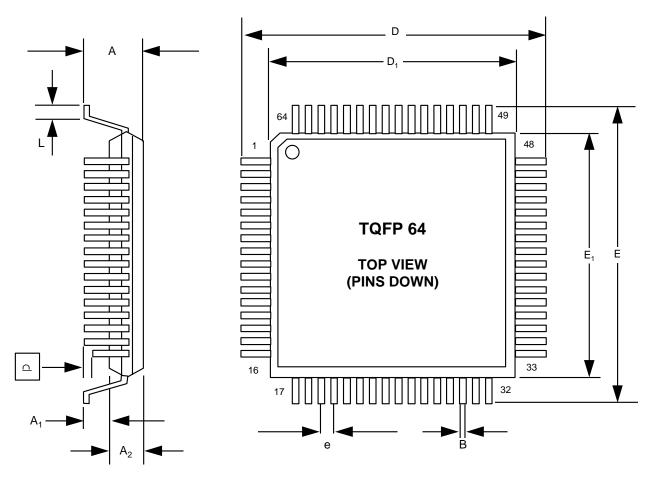

| OUTLINE DIMENSIONS                                   |              |

|                                                      |              |

### PIN FUNCTIONALITY

| Pin Group Name              | Pins | I/O | Function                                                                                                                                      |  |  |  |

|-----------------------------|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Control                     | 5    |     |                                                                                                                                               |  |  |  |

| MCLK                        | 1    | Ι   | Master clock input                                                                                                                            |  |  |  |

| TXON                        | 1    | Ι   | Baseband transmit section power-on input. When powering up/down is controlled by the bit TXON in BCRA, the pin TXON should be tied low.       |  |  |  |

| RXON                        | 1    | Ι   | Baseband receive section power-on input. When powering up/down is controlled<br>by the bit RXON in the BCRA, the pin RXON should be tied low. |  |  |  |

| MODE                        | 1    | Ι   | Proprietary Test Mode input. Should be tied low for normal operation                                                                          |  |  |  |

| RESET                       | 1    | Ι   | Active low reset signal input                                                                                                                 |  |  |  |

| <b>Baseband Serial Port</b> | 5    |     |                                                                                                                                               |  |  |  |

| BSDI                        | 1    | Ι   | Baseband serial port data input                                                                                                               |  |  |  |

| BSDIFS                      | 1    | Ι   | Baseband serial port input-data framing signal input                                                                                          |  |  |  |

| BSCLK                       | 1    | 0   | Baseband serial port clock output                                                                                                             |  |  |  |

| BSDO                        | 1    | 0   | Baseband serial port data output.                                                                                                             |  |  |  |

| BSDOFS                      | 1    | 0   | Baseband serial port output-data framing signal                                                                                               |  |  |  |

| Auxiliary Serial Port       | 5    |     |                                                                                                                                               |  |  |  |

| ASDI                        | 1    | Ι   | Auxiliary serial port data input                                                                                                              |  |  |  |

| ASDIFS                      | 1    | Ι   | Auxiliary serial port input-data framing signal input (level sensitive, active low)                                                           |  |  |  |

| ASCLK                       | 1    | Ι   | Auxiliary serial port clock input                                                                                                             |  |  |  |

| ASDO                        | 1    | 0   | Auxiliary serial port data output. Tri-state when inactive.                                                                                   |  |  |  |

| ASDOFS                      | 1    | Ι   | Auxiliary serial port output-data framing signal input (level sensitive, active low)                                                          |  |  |  |

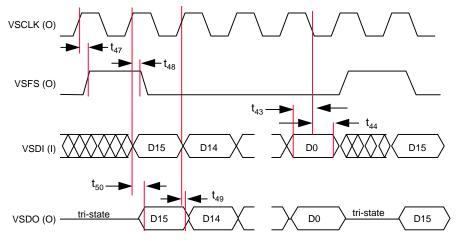

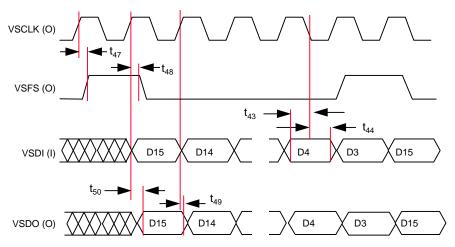

| Voiceband Serial Port       | 4    |     |                                                                                                                                               |  |  |  |

| VSDI                        | 1    | Ι   | Voiceband serial port data input                                                                                                              |  |  |  |

| VSCLK                       | 1    | 0   | Voiceband serial port clock output                                                                                                            |  |  |  |

| VSDO                        | 1    | 0   | Voiceband serial port data output. Tri-state when inactive.                                                                                   |  |  |  |

| VSFS                        | 1    | 0   | Voiceband serial port framing signal output                                                                                                   |  |  |  |

| Analog Baseband Interface   | 10   |     |                                                                                                                                               |  |  |  |

| BREFCAP                     | 1    | 0   | Baseband reference voltage output                                                                                                             |  |  |  |

| BREFOUT                     | 1    | I/O | Buffered baseband reference output / external bias voltage input                                                                              |  |  |  |

| IRXP, IRXN                  | 2    | Ι   | Differential analog input for in-phase receive signal                                                                                         |  |  |  |

| QRXP, QRXN                  | 2    | Ι   | Differential analog input for quadrature receive signal                                                                                       |  |  |  |

| ITXP, ITXN                  | 2    | 0   | Differential analog output for in-phase receive signal                                                                                        |  |  |  |

| QTXP, QTXN                  | 2    | 0   | Differential analog output for quadrature receive signal                                                                                      |  |  |  |

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

| Pin Group Name             | Pins | I/O | Function                                  |  |

|----------------------------|------|-----|-------------------------------------------|--|

| Analog Auxiliary Interface | 7    |     |                                           |  |

| ADC1                       | 1    | Ι   | Auxiliary A/D Converter Input 1           |  |

| ADC2                       | 1    | Ι   | Auxiliary A/D Converter Input 2           |  |

| ADC3                       | 1    | Ι   | Auxiliary A/D Converter Input 3           |  |

| ADC4                       | 1    | Ι   | Auxiliary A/D Converter Input 4           |  |

| AFC                        | 1    | 0   | Automatic Frequency Control signal output |  |

| RAMP                       | 1    | 0   | Power Ramping Control signal output       |  |

| AGC                        | 1    | 0   | Automatic Gain Control signal output      |  |

| Analog Voiceband Interface | 11   |     |                                           |  |

| VREFCAP                    | 1    | 0   | Voiceband reference voltage output        |  |

| VREFOUT                    | 1    | 0   | Buffered voiceband reference output       |  |

| VOUTNORP, VOUTNORN         | 2    | 0   | Differential voiceband normal output      |  |

| VOUTAUXP, VOUTAUXN         | 2    | 0   | Differential voiceband auxiliary output   |  |

| VINNORP, VINNORN           | 2    | Ι   | Differential voiceband normal input       |  |

| VINAUXP, VINAUXN           | 2    | Ι   | Differential voiceband auxiliary input    |  |

| BUZZER                     | 1    | 0   | Buzzer output                             |  |

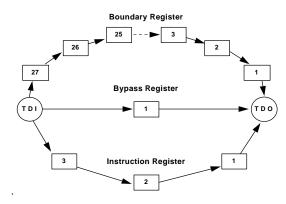

| JTAG Interface             | 4    |     |                                           |  |

| TDI                        | 1    | Ι   | Test data input                           |  |

| TDO                        | 1    | 0   | Test data output                          |  |

| TMS                        | 1    | Ι   | Test mode select                          |  |

| ТСК                        | 1    | Ι   | Test clock                                |  |

| Power Supplies             | 13   |     |                                           |  |

| AVDD1                      | 1    |     | Baseband Analog Power Supply              |  |

| AVDD3                      | 1    |     | Voiceband Analog Power Supply             |  |

| AVDD4                      | 1    |     | Auxiliary Analog Power Supply             |  |

| DVDD2, DVDD3               | 2    |     | Baseband / Auxiliary Digital Power Supply |  |

| DVDD4                      | 1    |     | Voiceband Digital Power Supply            |  |

| AGND1                      | 1    |     | Baseband Analog Ground                    |  |

| AGND2                      | 1    |     | Analog Substrate                          |  |

| AGND3                      | 1    |     | Voiceband Analog Ground                   |  |

| AGND4                      | 1    |     | Auxiliary Analog Ground                   |  |

| DGND2, DGND3               | 2    |     | Baseband / Auxiliary Digital Ground       |  |

| DGND4                      | 1    |     | Voiceband Digital Ground                  |  |

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

#### CONTROL

#### **Control Registers**

The AD6421 has a set of 37 Registers (10 bits wide each), shown in Table 1, which control the operation of the entire chip.

The functionality of all registers will be explained in the individual chapters; a brief overview is provided below.

- TXDATA is the input register for baseband transmit data.

- IRXOFFSET and QRXOFFSET hold the offset values for user calibration.

- TXDELAY1, TXDELAY2 and TXDELAY3 are programmable delays for the transmit phase.

- RXDELAY1 and RXDELAY2 are programmable delays for the receive phase.

- ARDADDR and BRDADDR are read address registers used to read the content of the control registers via the ASPORT or BSPORT.

- RAMPDAC is the input register for the RAMP-DAC.

- AGCDAC is the input register for the AGC-DAC.

- SUBDAC is the input register for the Sub AFC-DAC.

- AFCDAC is the input register for the Main AFC-DAC. Only the 8 LSBs of this register are used as input for the Main AFC-DAC.

- AUXADC1, AUXADC2, AUXADC3 and AUXADC4 are the output registers of the Auxiliary ADC's 4 channels.

- ACRA and ACRB are the two control registers for the auxiliary section.

- BCRA and BCRB are the two control registers for the baseband section.

- VCRA, VCRB and VCRC are the three control registers for the voiceband section.

- BSCLKRATE and VSCLKRATE control the clock frequency of the baseband serial port and the voiceband serial port.

- ITXOFFSET and QTXOFFSET hold the offset values for user calibration of the transmit section.

- ITXDAC and QTXDAC hold the values of the transmit DACs.

Table 1. Control Registers

| Name      | R/W | Address      | Reset  |

|-----------|-----|--------------|--------|

| TXDATA    | R/W | 00 0000 (0)  | BRESET |

| Reserved  |     | 00 0001 (1)  |        |

| Reserved  |     | 00 0010 (2)  |        |

| IRXOFFSET | R/W | 00 0011 (3)  | BRESET |

| QRXOFFSET | R/W | 00 0100 (4)  | BRESET |

| TXDELAY1  | R/W | 00 0101 (5)  | BRESET |

| TXDELAY2  | R/W | 00 0110 (6)  | BRESET |

| RXDELAY1  | R/W | 00 0111 (7)  | BRESET |

| RXDELAY2  | R/W | 00 1000 (8)  | BRESET |

| ARDADDR   | R/W | 00 1001 (9)  | RESET  |

| BRDADDR   | R/W | 00 1010 (10) | RESET  |

| RAMPDAC   | R/W | 00 1011 (11) | ARESET |

| AGCDAC    | R/W | 00 1100 (12) | ARESET |

| SUBDAC    | R/W | 00 1101 (13) | ARESET |

| AFCDAC    | R/W | 00 1110 (14) | ARESET |

| AUXADC1   | R   | 00 1111 (15) | ARESET |

| AUXADC2   | R   | 01 0000 (16) | ARESET |

| AUXADC3   | R   | 01 0001 (17) | ARESET |

| ACRA      | R/W | 01 0010 (18) | ARESET |

| ACRB      | R/W | 01 0011 (19) | ARESET |

| BCRA      | R/W | 01 0100 (20) | BRESET |

| BCRB      | R/W | 01 0101 (21) | BRESET |

| VCRA      | R/W | 01 0110 (22) | VRESET |

| VCRB      | R/W | 01 0111 (23) | VRESET |

| VCRC      | R/W | 01 1000 (24) | VRESET |

| Reserved  |     | 01 1001 (25) |        |

| BSCLKRATE | R/W | 01 1010 (26) | RESET  |

| VSCLKRATE | R/W | 01 1011 (27) | RESET  |

| ITXOFFSET | R/W | 01 1100 (28) | BRESET |

| QTXOFFSET | R/W | 01 1101 (29) | BRESET |

| Reserved  |     | 01 1110 (30) |        |

| ITXDAC    | R   | 01 1111 (31) | BRESET |

| QTXDAC    | R   | 10 0000 (32) | BRESET |

| Reserved  |     | 10 0001 (33) |        |

| Reserved  |     | 10 0010 (34) |        |

| TXDELAY3  | R/W | 10 0011 (35) | BRESET |

| AUXADC4   | R   | 10 0100 (36) | ARESET |

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

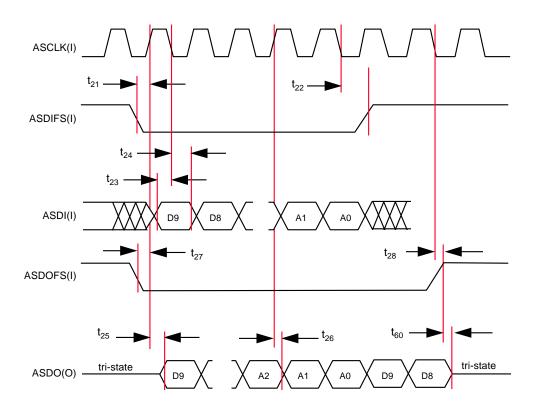

#### Writing and Reading Control Registers

Writing to and reading from control registers is possible via the auxiliary serial port or the baseband serial port (ASPORT or BSPORT). It involves the transfer of 16 bit words, 10 bits of data and 6 bits of address. The write format is shown in Figure 2, bit 15 being the first input bit of the frame. The destination of the 10 bit data is determined by the 6 bit destination address. Note that some registers are read only and hence, cannot be written to.

To read the contents of a register, the address of the appropriate register is written to the read address register, ARDADDR or

BRDADDR, as shown in Figure 3. The time interval between writing to the read address register and the serial port frame synchronization signal becoming active equals 4 MCLK cycles. The frame synchronization signal can be asserted one SCLK cycle after the user has completed writing to the read address register. The read address register is 6 bits wide and bits 11 to 6 of the input frame are used to write to this register, bits 12 to 15 being don't cares. The frame format for reading is identical to that for writing i.e. 10 bits of data followed by 6 address bits corresponding to the source address of the data .

| 15 |    | -  |    |    | -  | -  | -  |    | -  | -  |    | -  |    |    | -  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | A5 | A4 | A3 | A2 | A1 | A0 |

| Figure 2. | Write / Read Format |

|-----------|---------------------|

|-----------|---------------------|

| 15 |   | - |   |    | -  | -  | -  |    | -  | - |   | - |   |   | - |

|----|---|---|---|----|----|----|----|----|----|---|---|---|---|---|---|

| Х  | Х | Х | Х | A5 | A4 | A3 | A2 | A1 | A0 | 0 | 0 | 1 | 0 | 0 | 1 |

Figure 3. Write to the Read Address Register (ARDADDR shown here)

#### Reset

To reset the AD6421, the RESET pin should be pulled low for a fraction of 1 MCLK cycle. The internal logic is edge sensitive and the low signal is latched and held low for 2 MCLK cycles after the signal goes high again. This allows time for the internal reset to be completed.

A system reset requires 8 MCLK cycles.

On reset, all control registers except BSCLKRATE are set to zero.

- BSCLKRATE is set to 4 so that the frequency is 1.625 MHz (MCLK / 8).

- The register VSCLKRATE is set to 0, leading to a frequency of 2.6 MHz (MCLK / 5) for the voiceband clock.

Additionally, the control registers can be reset by dedicated reset bits in certain registers.

- The auxiliary registers can be reset by setting bit ARESET in Auxiliary Control Register A (ACRA) to 1.

- The baseband registers can be reset by setting bit BRESET in Baseband Control Register A (BCRA) to 1.

- Finally the voiceband registers are reset by setting bit VRESET in Voiceband Control Register B (VCRB) to 1.

- The registers ARDADDR, BRDADDR, BSCLKRATE and VSCLKRATE can only be reset using the reset pin.

#### **Timing Conventions**

In a GSM mobile terminal, all timings are related to one master clock of nominal 13 MHz. The AD6421 receives its MCLK signal either directly from the master oscillator or from the AD6422. All timing in the AD6421 are derived from the MCLK period  $T_{MCLK}$ .

| T <sub>MCLK</sub> = | <u>1</u><br>13 MHz | ≈ 76.9 ns |

|---------------------|--------------------|-----------|

|---------------------|--------------------|-----------|

To allow an easier interpretation of the AD6421 timing specifications, time is sometimes expressed in two system related values:  $T_{BIT}$  is the period of one transmitted signal-bit and  $Q_{BIT}$  is one quarter of  $T_{BIT}$ .

$$T_{BIT} = 48 \times T_{MCLK} \approx 3.692 \ \mu s$$

$$O_{BIT} = 12 \times T_{MCLK} \approx 0.923 \ \mu s$$

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

#### **BASEBAND SECTION**

#### **Baseband Control Register**

The baseband section of the AD6421 has two control registers, BCRA and BCRB as shown in Table 2 and Table 3. BCRA contains the control bits for the activation of:

- Transmit and receive autocalibration,

- Fransmit and receive autocaribrat

External Receive autocalibration,

- Bypass of the RAMP-RAM,

- Bypass of the RAMP-RAM,

Transmit and Receive section,

- Reset of the baseband section.

\_\_\_\_\_

BCRB contains the control bits for the on-chip baseband reference.

All control bits reset to 0. "Reserved" bits must never be changed to 1 for proper operation.

| Bit   | Name      | Function                                                                                                                                               |

|-------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| BCRA0 | TXAUTOCAL | Selects Tx-Auto-Calibration<br>when set to 1 and User-<br>Calibration when set to 0                                                                    |

| BCRA1 | RXAUTOCAL | Selects Rx-Auto-Calibration<br>when set to 1 and User-<br>Calibration when set to 0                                                                    |

| BCRA2 | RXEXTCAL  | When set to 1, the Rx Cali-<br>bration operates in external<br>mode. The analog inputs re-<br>main connected to the pins<br>during the autocal routine |

| BCRA3 |           | Reserved (0)                                                                                                                                           |

| BCRA4 | RBBYPASS  | When this bit is set to 1 the<br>ramping RAM is bypassed<br>and data written to address 11<br>goes directly to the<br>RAMPDAC                          |

| BCRA5 | TXON      | Power on for the transmit section when set to 1                                                                                                        |

| BCRA6 | RXON      | Power on for the receive sec-<br>tion when set to 1                                                                                                    |

| BCRA7 | BRESET    | Baseband Reset when set to 1                                                                                                                           |

| BCRA8 |           | Reserved (0)                                                                                                                                           |

| BCRA9 |           | Reserved (0)                                                                                                                                           |

#### Table 2. Baseband Control Register A (BCRA)

Table 3. Baseband Control Register B (BCRB)

| Bit   | Name      | Function                                                                                                                                 |

|-------|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| BCRB0 |           | Reserved (0)                                                                                                                             |

| BCRB1 | BRS       | Baseband Reference Select.<br>When set to 0 BREFOUT =<br>1.2V, when set to 1<br>BREFOUT = 1.35V                                          |

| BCRB2 | BRU       | BREFOUT use;<br>When set to 1, the output<br>buffer for the pin<br>BREFOUT is active;                                                    |

| BCRB3 | BLP       | Baseband Reference Low<br>Power. When set to 1, keeps<br>the baseband reference<br>powered up, when baseband<br>section is powered down. |

| BCRB4 |           | Reserved (0)                                                                                                                             |

| BCRB5 |           | Reserved (0)                                                                                                                             |

| BCRB6 |           | Reserved (0)                                                                                                                             |

| BCRB7 | REFOUTDIS | If set to 1 BREFOUT be-<br>comes an input                                                                                                |

| BCRB8 |           | Reserved (0)                                                                                                                             |

| BCRB9 |           | Reserved (0)                                                                                                                             |

#### **Baseband Transmit Section**

The transmit section of the AD6421 generates GMSK I and Q output signals in accordance with the GSM (Phase 2) specification 05.05. This is accomplished by a digital GMSK (Gaussian Minimum Shift Keying) modulator, followed by 10-bit DACs for the I and Q channels and on-chip reconstruction filters. The GMSK modulator generates I and Q signals in response to the transmit data stream.

The entire baseband transmit section may be powered up/down by setting bit 5 in Baseband Control Register A (BCRA5) or by using the TXON-pin; see Table 4 for details.

| TXON<br>Pin | TXON<br>(BCRA5) | Transmit<br>Section |

|-------------|-----------------|---------------------|

| 0           | 0               | OFF                 |

| 0           | 1               | ON                  |

| 1           | 0               | ON                  |

| 1           | 1               | ON                  |

When the powering up/down of the transmit section is being controlled by the TXON-pin, the TXON-bit should equal zero.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

#### **Burst Store**

To support effective communication between the AD6421 and other components like the AD6422 GSM Processor, a burst store is included. The burst store can hold 160 data bits and is filled by making 16 writes to address 0 of the control register (TXDATA). Bit D0 of the first word written to the burst store will be the first bit to be transmitted. Bit D9 of the last word written to the burst store will be the last bit to be transmitted. When the burst store has been read, the part automatically continues to transmit ones until TXON is taken low.

#### **GMSK Modulator**

The GMSK Modulator is implemented using digital logic and ROM look up tables. The transmit data is first differentially encoded, then fed to the GMSK pulse shaping ROM. The output data of the ROM goes to cosine- (I data) and sine- (Q data) lookup tables which output 10-bit data samples to the transmit DACs. GMSK coding implements a four-bit impulse response, BT = 0.3.

#### **Transmit Offset Calibration**

Included in the transmit section is a circuit by which transmit signal offsets may be calibrated out. Each transmit channel has an offset register which contains a value representing the DC offset of the analog circuitry in the transmit channel. In normal operation, the value stored in the register is subtracted from the GMSK modulator output data before it is fed to the DAC. Auto-calibration or user-calibration can be selected. Auto-calibration will remove internal offsets only while usercalibration allows the user to write to the offset register in order to remove external offsets. The offset registers are 10-bits wide and represent two's complement values. When auto-calibration is disabled, the offset registers will retain their contents until another auto-calibration is performed or a new value is written to the offset registers.

#### **Auto-Calibration**

If transmit auto-calibration is selected by setting bit 0 of the Baseband Control Register A (BCRA0), the AD6421 will initiate an auto-calibration routine each time the transmit path is brought out of power-down. After TXON is asserted, 340 quarter bit periods ( $Q_{BIT}$ ) are allowed for the circuitry to settle and for calibration to be performed. During the calibration, the analog outputs are at  $V_{BIAS}$ . The input offset of the I and Q channel are measured and stored in the ITXOFFSET and QTXOFFSET registers.

#### **User-Calibration**

When user-calibration is selected, the transmit offset register can be written to, allowing offsets in the radio section to be calibrated out also. However, the user is now responsible for calibrating out transmit offsets belonging to the AD6421. When the transmit path enters low-power mode, the registers remain valid. TXDELAY1 must be programmed to a minimum value of 108 quarter bit periods to permit the circuitry to settle.

#### **Output Timing**

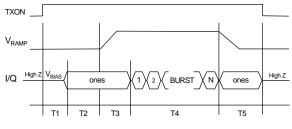

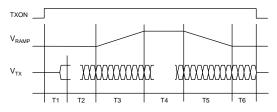

The output timing can be divided into 5 separate periods listed in Table 5 and shown in Figure 4.

Figure 4. Transmit Timing

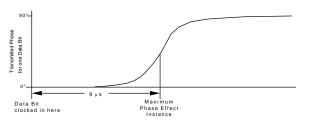

Upon asserting TXON, the output leaves the high impedance state and the period T1 begins. During T1, the output is held at  $V_{BIAS}$  almost to the end. Approximately 32  $Q_{BIT}$  before the end of T1, the modulator begins to modulate consecutive ones. When autocalibration is selected, T1 is equal to 340  $Q_{BIT}$ ; when user-calibration is selected T1 is equal to 0.

When T1 is completed, an internal timer is started which times out a period T2 equal to TXDELAY1. During this interval, the modulator continues to modulate consecutive ones. When user-calibration is selected, TXDELAY1 must be programmed to a minimum value of 108  $Q_{BT}$  to allow analog circuitry to settle. After T2, the power ramp starts by feeding the RAMP-DAC with the values from the RAMP RAM. The time when the modulator begins to modulate the bits in the burst store can be further delayed by the period T3 equal to TXDELAY3. If TXDELAY3 has a value of 0, the power ramping and the modulation of the burst bits commences simultaneously.

Table 5. Transmit Timing

|    | Name                                                       | Q <sub>BIT</sub>       | μS                        |

|----|------------------------------------------------------------|------------------------|---------------------------|

| T1 | T <sub>AUTOCALIBRATE</sub><br>T <sub>USERCALIBRATE</sub>   | 340<br>0               | 313.8<br>0.0              |

| T2 | TXDELAY1 <sub>AUTOCAL</sub><br>TXDELAY1 <sub>USERCAL</sub> | 0 - 1023<br>108 - 1023 | 0 - 944.2<br>99.7 - 944.2 |

| T3 | TXDELAY3                                                   | 0 - 1023               | 0 - 944.2                 |

| T4 | TXDELAY2                                                   | 0 - 1023               | 0 - 944.2                 |

| T5 | depends on TXON                                            | 0 - ∞                  | 0 - ∞                     |

After T3 has expired, the burst bits are modulated for the period T4 equal to TXDELAY2. To ensure proper timing operation of the ramp up sequence during data transmission, the sum of registers TXDELAY3 and TXDELAY2 must be restricted to an even number of  $Q_{BIT}$ s.

After T4, the modulator begins to modulate consecutive ones again. This continues until TXON is deasserted and the analog outputs assume the high impedance state. TXON should not be deasserted until the end of the ramp down sequence.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

#### **Transmit DACs & Output Filters**

The AD6421 contains two 10-bit DACs which have been optimized for matched gain, group delay and phase between the two channels. Analog reconstruction filters smooth the DAC output signals providing continuous time I and Q waveforms at the output pins. These are Butterworth low-pass filters with a cutoff frequency of approximately 300 kHz. The filters are designed to have a linear phase response in the passband and the phase mismatch between the I and Q transmit channels is kept to a minimum.

#### **Output Bias Voltage**

The common mode voltage of the analog outputs is normally equal to  $V_{BREFOUT}$ . The value of this voltage can be programmed by setting bit 1 of the BCRB. Two values are selectable: 1.2V or 1.35V.

Alternatively, an external reference can be used to alter the bias voltage, Vbias. This is done by setting bit REFOUTDIS in register BCRB (see Table 3) to disable the baseband reference output pin, BREFOUT. After disabling BREFOUT, it becomes an input pin to which an external reference may be connected. The input range for this pin is nominal 1.2V to AVDD - 1.35 V. The bias voltage then becomes equal to the value of the external reference. The analog signal range, however, continues to be determined by  $V_{BREFCAP}$ , i.e. the external reference only affects the bias voltage to the Tx analog outputs. The input resistance to this pin is in the range of 10 k $\alpha$  to 20 k $\alpha$ .

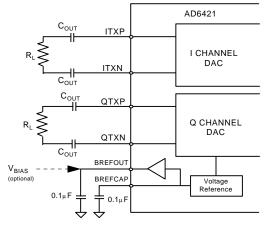

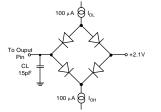

#### **Output Interface**

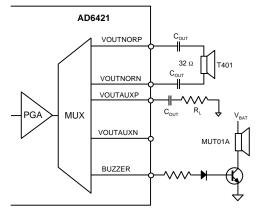

The ITX and QTX outputs are designed to be dc or ac coupled to the external circuits. Figure 5 shows a simplified circuit providing a differential output with ac coupling. The capacitor  $(C_{OUT})$  of this circuit is optional. An external lowpass filter may be required to meet GSM Phase 2 requirements. See section APPLICATION NOTES at the end of the datasheet.

Figure 5. Circuit for Differential Output

#### **Baseband Receive Section**

The receive section consists of I and Q receive channels, each comprised of a switched-capacitor filter followed by a 15-bit sigma-delta ADC. On-chip digital filters, which are part of the sigma-delta ADCs, also perform substantial neighbor channel selection. The receive section also has a low power sleep mode drawing only minimal current.

The entire baseband receive section may be activated or powered down by setting the bit 6 in the Baseband Control Register A (BCRA6) or by using the RXON-pin; see Table 6 for details.

Table 6. Activation of Receive Section

| RXON<br>Pin | RXON<br>(BCRA6) | Receive<br>Section |

|-------------|-----------------|--------------------|

| 0           | 0               | OFF                |

| 0           | 1               | ON                 |

| 1           | 0               | ON                 |

| 1           | 1               | ON                 |

When the powering up/down of the receive section is being controlled by the RXON-pin, the RXON-bit should equal zero. Similarly, when the powering up/down is controlled by the RXON-bit, the RXON-pin should be tied low.

#### Analog Input & Switched Capacitor Filter

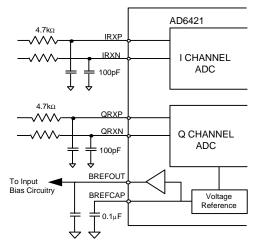

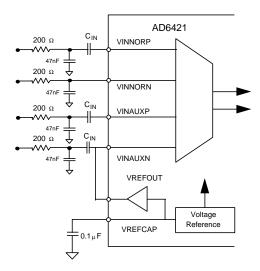

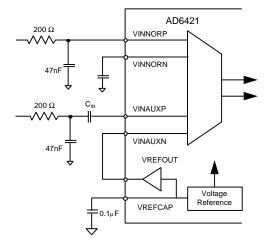

The AD6421 provides differential analog inputs for the I and Q receive signals. Figure 6 shows the recommended circuit.

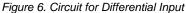

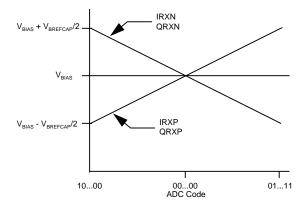

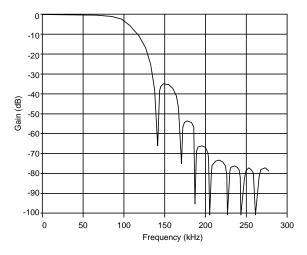

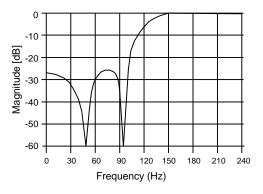

The AD6421 provides a high degree of flexibility to adapt to different input and bias voltages as shown in Table 7. The analog inputs are sampled at 13 MHz by a switched capacitor filter. The filter has a zero at 6.5 MHz as shown in Figure 8a. The receive channel also contains a digital low-pass filter which operates at a clock frequency of 6.5 MHz. Due to the sampling nature of the digital filter, the passband is repeated

about the operating clock frequency and at multiples of the clock frequency (Figure 8b). Because the first null of the switched-capacitor filter coincides with the first image of the digital filter, this image is attenuated by an additional 30 dB (Figure 8c), further simplifying the external anti-aliasing requirements. The circuitry of Figure 6 implements first-order low-pass filters with a 3 dB point at 338 kHz. These are the only filters that must be implemented externally to prevent aliasing of the sampled signal.

| Table 7. Input Signal Ranges | Table | 7. | Input | Signal | Ranges |

|------------------------------|-------|----|-------|--------|--------|

|------------------------------|-------|----|-------|--------|--------|

| Parameter                          | Range                                                     |

|------------------------------------|-----------------------------------------------------------|

| AVDD                               | 3.0V ± 10%                                                |

| VBREFCAP                           | 1.2V ± 5%                                                 |

| ADC overall Signal Range           | 2 V <sub>BREFCAP</sub>                                    |

| VBIAS<br>Differential Input        | V <sub>BREFCAP</sub> /2 to AVDD - V <sub>BREFCAP</sub> /2 |

| Input Signal Range<br>Differential | $V_{BIAS} \pm V_{BREFCAP}/2$                              |

Figure 7. ADC Transfer Function Differential Input

#### Sigma-Delta ADC

The AD6421 receive channels employ a sigma-delta conversion technique, which provides a high resolution 15-bit output for both I and Q channels with system filtering being implemented on-chip.

The output of the switched-capacitor filter is continuously sampled at 6.5 MHz, by a charge-balanced modulator, and is converted into a digital pulse train. Due to the high oversampling rate, which spreads the quantization noise from 0 to 3.25 MHz, the noise energy contained in the band of interest is reduced. To reduce the quantization noise still further, a high-order modulator is employed to shape the noise spectrum so that most of the noise energy is shifted out of the band of interest. The digital filter that follows the modulator removes the large out of band quantization noise, while converting the digital pulse train into parallel 15-bit wide binary data.

c) Combined

#### **Digital Filter**

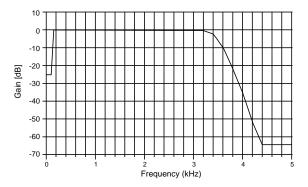

The digital filters used in the AD6421 receive section carry out two important functions. Firstly, they remove the out-of-band quantization noise. Secondly, they ease the design of the radio section by providing substantial neighbor-channel suppression. The digital filter is a 288-tap FIR filter with a 3dB point at 96 kHz. The filter is clocked at 6.5 MHz and has a settling time of 44.3  $\mu$ s.

Even though digital filters have several advantages over analog filters, they cannot remove noise superimposed on the analog signal before it reaches the ADC.

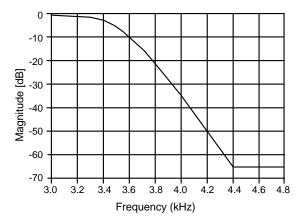

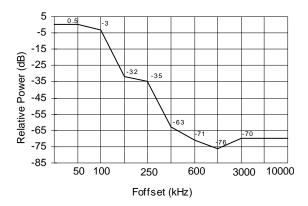

Figure 9. Digital Filter Frequency Response

Therefore, noise peaks riding on signals near full-scale have the potential to saturate the analog modulator, even though the

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

average value of the signal is within limits. To alleviate this problem, the AD6421 has overrange headroom built into the sigma-delta modulator and digital filter which allows overrange excursions of 100 mV.

#### **Receive Offset Calibration**

Each channel of the digital low pass filter has an offset register. In normal operation, the value stored in the offset register is subtracted from the filter output data before the data appears on the serial output. By so doing, dc offsets in the I and Q channels get calibrated out. Auto-calibration or user-calibration can be selected. Auto-calibration will remove internal offsets only while user-calibration allows the user to write to the offset register in order to remove external offsets also.

The 10-bit offset registers can hold any dc offset between  $\pm 150$  mV (1/8th of the input range) however the performance of the Sigma Delta ADCs will degrade if full-scale signals with more than 75mV of offset are experienced. The values in the offset registers are coded in two's complement. The LSB of the offset register corresponds to bit 3 of the Rx words, while the MSB of the offset register corresponds to bit 12 of the Rx words (see Table 8).

Table 8. Position of 10-bit Offset Word

| Rx Data        | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Offset Registe | er |    |    | 9  | 8  | 7  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |   |   |   |

Auto-calibration is selected by setting bit 1 of the Baseband Control register A (BCRA1 = RXAUTOCAL) to 1. If RXAUTOCAL is set to 0, no calibration occurs (see Figure 10). Two types of Auto-calibration can be selected by setting bit 2 of the Baseband Control Register A (BCRA2 = RXEXTCAL).

#### Autocalibration

If auto-calibration is selected by setting the RXAUTOCAL bit in control register BCRA to 1, the AD6421 will perform an auto-calibration routine each time the receive section is brought out of the low-power mode. Two modes of autocalibration can be selected. In internal autocalibration mode, the differential inputs are disconnected from the input pins and shorted together to measure the ADC offset. In external autocalibration mode, the inputs remain connected to the pins, allowing system offset along with the internal offsets to be evaluated. This is averaged sixteen times to reduce noise and the result is placed in the offset register. The input to the ADC is then switched back for normal operation and the circuitry is permitted to settle.

#### **User Calibration**

When user calibration is selected by setting RXAUTOCAL to 0, the receive offset register can be written to, allowing offsets in the IF-demodulation circuitry to be calibrated out also. However, the user is now responsible for calibrating out receive offsets belonging to the AD6421. When the receive path enters the low power mode, the registers remain valid. After powering up, the first I/Q sample pair is output once time has elapsed for circuitry to settle and also for the output of the digital filter to settle.

Figure 10. Receive Offset Calibration Flowchart

#### **Receive and Offset Calibration Timing**

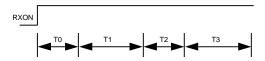

The timing of the receive and offset calibration process can be divided into 4 periods T0 - T3 as shown in Figure 11 and Table 9. RXDELAY1 and RXDELAY2 reset to zero and can be user programmed for periods from 0 to 255  $T_{BIT}$ .

Table 9. Receive Offset Calibration Timing

| Period | Name                   | T <sub>BIT</sub> | μS            |

|--------|------------------------|------------------|---------------|

| Т0     | T <sub>SETTLE</sub>    | 36               | 132.9         |

| T1     | RXDELAY1               | 15 - 255         | 55.38 - 941.5 |

| T2     | T <sub>CALIBRATE</sub> | 40               | 147.7         |

| Т3     | RXDELAY2               | 0 - 255          | 0 - 941.5     |

Figure 11. Receive Offset Calibration Timing

After RXON is asserted, the RXAUTOCAL bit determines the path in the flow diagram shown in Figure 10.

If user-calibration is selected, the fixed period T0 (36  $T_{BIT}$  periods) transpires. After T0 has expired, the period T1 starts which

is a programmable period RXDELAY1. To allow time for the analog and digital circuitry to settle, RXDELAY1 must be programmed to a minimum value of  $15 T_{BIT}$ , value 0x00F. After T1 has expired, a second programmable period, T3 equal to RXDELAY2, is inserted. After T3 has expired, the first valid output word appears at the output.

If autocalibration is selected, the RXEXTCAL bit determines whether external or internal autocalibration is selected. Again, the calibration process starts with the period T0 followed by T1 programmed to a minimum 15  $T_{BIT}$  delay. After T1 has expired, the autocalibration period T2 equal to 40  $T_{BIT}$  begins. After T2, the programmable delay T3 is inserted before the first valid word appears at the output.

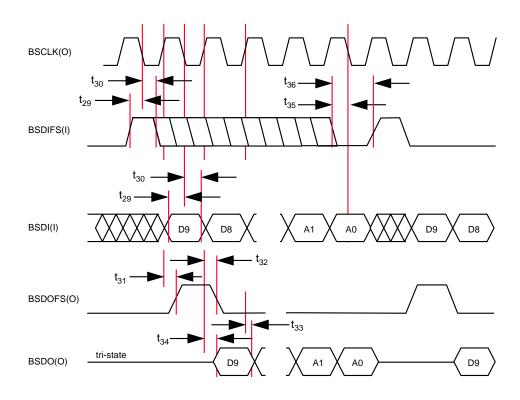

#### **Output Timing**

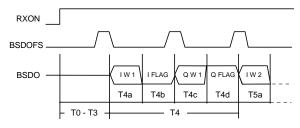

After the receive section is activated by the RXON bit or RXON pin and the calibration procedure has been performed, Rx data is automatically output on the BSDO pin.

Figure 12. Output Format of Rx Data

The data format is I followed by Q. The AD6421 will output 16 bits of data, the 15-bit I or Q word, which is in two's complement format, and a flag bit. This flag bit (LSB) distinguishes between I and Q words, the bit being 0 for an I word and 1 for a Q word.

| Period  | Function    | T <sub>BIT</sub> | μS    | Transf. Bits<br>(13Mbit/s) |

|---------|-------------|------------------|-------|----------------------------|

| T0 - T3 | see Table 9 |                  |       | none                       |

| T4a     | I Word      | 1/3              | 1.231 | 16 (15+1)                  |

| T4b     | I Flag      | 1/6              | 0.615 | 8                          |

| T4c     | Q Word      | 1/3              | 1.231 | 16 (15+1)                  |

| T4d     | Q Flag      | 1/6              | 0.615 | 8                          |

| T4      |             | 1                | 3.692 | 48                         |

| T5a     | I Word      | 1/3              | 1.231 | 16                         |

Table 10. Output Timing of Rx Data

The serial clock has a frequency of 13 MHz, irrespective of the value of the clock rate register. When the AD6421 is ready to output Rx data, it generates an output frame synchronization signal (BSDOFS) and the Rx data is outputted automatically on the BSDO pin; see Figure 12 and Table 10 for details. To adapt the data rates of the ADC samples ( $2 \times 270$  k words/sec) to the

data rate of the serial port (13 Mbit/s) the flag bits are extended by 8 bit-periods (13 Mbit/s).

#### **BASEBAND REFERENCE**

The baseband reference of the AD6421 is a bandgap reference, which provides a low noise, temperature compensated reference for the converters in the baseband as well as in the auxiliary section. The reference voltage has a nominal value of 1.2V and is referred to as  $V_{BREFCAP}$  in the description of the baseband and auxiliary section. This internal reference is connected to the pin BREFCAP, where a bypass capacitor of  $0.1\mu$ F should be connected.

Additionally, the AD6421 provides a buffered copy of the internal baseband reference, which is connected to pin BREFOUT. Also here, a bypass capacitor of  $0.1\mu$ F should be connected. The output voltage of this pin is referred to as  $V_{BREFOUT}$  and can be used as a bias voltage for other analog circuitry in the radio section. The output buffer which drives the BREFOUT pin can be disabled by setting bit BRU in the control register BCRB to 0.

In order to provide more flexibility, the voltage  $V_{BREFOUT}$  is selectable between two values depending on bit 1 of control register BCRB (BCRB1). If BCRB1 is equal to 0,  $V_{BREFOUT}$  is 1.2V; if BCRB1 is equal to 1,  $V_{BREFOUT}$  is 1.35V.

The baseband reference output pin (BREFOUT) can be disabled by setting the bit REFOUTDIS in BCRB to 1. After disabling BREFOUT, it becomes an input pin and an external reference can be connected to this pin. The input resistance is in the range of 10 k $\alpha$  to 20 k $\alpha$ . Note however, that the external reference changes only the value of  $V_{BREFCAP}$  and not the value of  $V_{BREFCAP}$  remain unchanged.

When all baseband and auxiliary converters in the AD6421 are powered down, the reference will automatically power down also. Once any one of the baseband or auxiliary converters is powered up, the baseband reference will also power up automatically. Alternatively, by setting bit 3 of control register BCRB (BLP) to 1, the reference always remains powered up. This is useful when external circuitry requires a continuously active reference. Also, the power up time for the converters is reduced since the reference does not require time to power up and settle.

The baseband reference can further be placed in a low power standby mode by setting bit 1 (BREFSB) of control register ACRB to 1. In this mode, only the AFC-DAC may drive an output.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

#### AUXILIARY SECTION

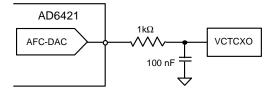

The AD6421 contains three auxiliary DACs which may be used to generate analog control signals for Automatic Gain Control (AGC) of the IF receive section, for Automatic Frequency Control (AFC) of the master clock oscillator, and for RF power amplifier control (RAMP). Additionally, it contains a universal ADC with four multiplexed input channels for monitoring analog values in the mobile radio.

#### **Auxiliary Control Register**

The auxiliary section of the AD6421 has two control registers as shown in Table 11 and Table 12.

ACRA contains the control bits to power on the auxiliary ADC and all three auxiliary DACs, as well as the start convert signal for the auxiliary ADC and its channel selection.

ACRB contains the reset control bit for all auxiliary converters. All control bits reset to 0. The "Reserved" bits must never be changed to 1 for proper operation.

#### **RAMP** Control

To avoid the emission of unwanted spectral components during the transmission of a burst, the envelope of the burst must follow a precisely defined curve with particular care placed on the up and down ramps. In addition, GSM allows the reduction of the RF output power depending on the quality of the air interface. Both functions are supported by the RAMP-DAC with a 4X interpolator and an associated RAMP-RAM.

| Table 11. | Auxiliary | Control | Reaister | (ACRA) |

|-----------|-----------|---------|----------|--------|

|           | лилінаі у | CONTROL | Negister |        |

| Bit   | Name      | Function                                                                        |

|-------|-----------|---------------------------------------------------------------------------------|

| ACRA0 | AUXADCON  | Power on for Auxiliary<br>ADC when set to 1                                     |

| ACRA1 | RAMPDACON | Power on for RAMPDAC when set to 1                                              |

| ACRA2 | AGCDACON  | Power on for AGCDAC when set to 1                                               |

| ACRA3 | AFCDACON  | Power on for AFCDAC when set to 1                                               |

| ACRA4 |           | Reserved (0)                                                                    |

| ACRA5 |           | Reserved (0)                                                                    |

| ACRA6 | AFCDACLP  | AFC-DAC Low Power<br>when set to 1                                              |

| ACRA7 | AUXADCCS  | Auxiliary ADC start con-<br>vert. Writing a 1 to this bit<br>starts conversion. |

| ACRA8 | AUXADCCS0 | Auxiliary ADC channel select bit 0                                              |

| ACRA9 | AUXADCCS1 | Auxiliary ADC channel select bit 1                                              |

Table 12. Auxiliary Control Register B (ACRB)

| Bit   | Name   | Function                                                                                                       |

|-------|--------|----------------------------------------------------------------------------------------------------------------|

| ACRB0 | ARESET | Resets all Auxiliary Converters when set to 1                                                                  |

| ACRB1 | BREFSB | BREFCAP Standby.<br>When set to 1, the baseband<br>reference is in low power<br>standby mode.                  |

| ACRB2 | AFCUPD | AFC-DAC update<br>When set to 1, the Main- and<br>Sub-DAC are updated simulta-<br>neously after a SUBDAC write |

| ACRB3 |        | Reserved (0)                                                                                                   |

| ACRB4 |        | Reserved (0)                                                                                                   |

| ACRB5 |        | Reserved (0)                                                                                                   |

| ACRB6 |        | Reserved (0)                                                                                                   |

| ACRB7 |        | Reserved (0)                                                                                                   |

| ACRB8 |        | Reserved (0)                                                                                                   |

| ACRB9 |        | Reserved (0)                                                                                                   |

#### RAMP-RAM

The AD6421 has a  $32 \times 10$  bit wide RAM, which holds the ramping coefficients - 16 words are used for ramp-up and 16 for ramp-down.

Writing to the RAMP-RAM is performed by making 32 consecutive writes to address 11 of the control register. The first 16 words must define the ramp up envelope and the second 16 must define the ramp down envelope. At a 540 kHz update rate, this corresponds to 8  $T_{BTT}$  of ramp up and 8  $T_{BTT}$  of ramp down. It is possible to write to the RAMP-RAM at any time other than T3, T4 and T5. The contents of the RAMP-RAM will be retained under all circumstances - even during RESET. The RAMP-RAM can be bypassed by setting bit 4 in the control register BCRA to 1. In this case, data written to address 11 of the AD6421 control register goes directly to the RAMP-DAC for conversion.

#### **RAMP-DAC and Interpolator**

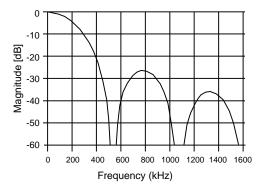

The 10-bit RAMP-DAC fetches new values from the RAMP-RAM with a rate of 540 kHz. To reduce the high frequency components of the analog output signal, the output of the RAMP-DAC is interpolated between each update increasing the effective output rate to 4 x 540 kHz = 2.16 MHz. I.e. every N+4th output sample is determined by the RAMP-RAM, while the three output samples in between (N+1, N+2 and N+3) are interpolated between the Nth and N+4th value. The frequency response of the interpolated output can be seen in Figure 13. For smoothing, a single-pole RC filter with a corner frequency of 300 kHz should be placed at the DAC output - recommended values 10K/50pF.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

The output voltage of the RAMP-DAC for a 10-bit word (W) can be calculated by the formula:

$$V_{OUT} = 2 \times V_{BREFCAP} \times (1/32 + W/1024)$$

For W = 0x000 this gives an output voltage of  $2/32 \times V_{BREFCAP}$ ; for W = 0x3FF this gives an output voltage of approximately  $(2+2/32) \times V_{BREFCAP}$  (75 mV to 2.473V).

Figure 13. Interpolator Frequency Response

#### **RAMP** Timing

The timing of the RAMP-DAC output can be seen in relation to the timing of the baseband DAC output described in Table 5 and Figure 4. Note however, that the period T3 (TXDELAY3) in Table 13 and Figure 14 is set equal to Ramp Up, or  $32 Q_{BIT}$ .

Table 13. RAMP Timing

|    | Name            | Q <sub>BIT</sub> | μS        |

|----|-----------------|------------------|-----------|

| T1 | TAUTOCALIBRATE  | 340              | 313.8     |

| T2 | TXDELAY1        | 0 - 1023         | 0 - 944.2 |

| Т3 | Ramp Up         | 32               | 29.5      |

| T4 | TXDELAY2        | 0 - 1023         | 0 - 944.2 |

| T5 | Ramp Down       | 32               | 29.5      |

| T6 | depends on TXON | 0 - ∞            | 0 - ∞     |

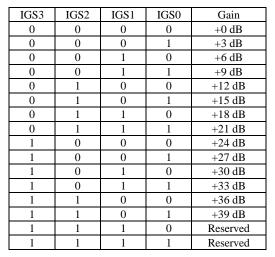

Figure 14. Ramp Timing