## CMOS Continuous Edge Graphics RAM-DACs (CEG/DACs)

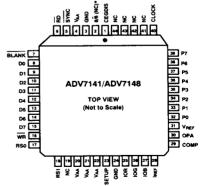

## ADV7141/ADV7146/ADV7148\*

## **FEATURES**

Proprietary Antialiasing Function

Dejagging of Lines, Arcs, Circles, Fonts, etc.

Effective 24-Bit True Color Performance

Dynamic Palette Load (DPL) Function

Plug-in Upgrade for Standard VGA RAM-DACs

ADV478/ADV471, ADV476 (ADV\*) & Inmos 171/176†

Fully PS/27, VGA† and 8514/A† Compatible

66 MHz Pipelined Operation

Triple 8-Bit/6-Bit D/A Converters

256 × 24 (18) Color Palette RAM

On-Board Gamma-Correction

On-Board Antisparkle Circuit

RS-343A/RS-170 Compatible Outputs

External Voltage or Current Reference

APPLICATIONS

High Resolution Color Graphics

True Color Graphics

Digital Typography (Smooth Fonts)

Scientific Visualization

3-D Solids Modeling

CAE/CAD/CAM Applications

Image Processing

+5 V CMOS Monolithic Construction

Image Processing Instrumentation Desktop Publishing

Standard MPU Interface

**AVAILABLE CLOCK RATES**

66 MHz

50 MHz

35 MHz

## **GENERAL DESCRIPTION**

The Analog Devices' Continuous Edge Graphics† RAM-DAC (CEG†/DAC) dramatically improves image quality of standard analog color systems, by eliminating the jagged edges of computer generated images (antialiasing) and by providing an extended color palette for 3D modeling. This increased performance is achieved while at the same time maintaining full pin and functional compatibility with existing video RAM-DACs and color palettes used in VGA graphics systems.

The CEG/DAC implements a proprietary antialiasing or "dejagging" function. This is used to smooth the jagged edges associated with lines, circles and other nonrectangular objects displayed on a regular CRT screen. The part also allows for the effective display of 24-bit true color images on a standard 8-bit system, without the requirement of increased memory. More than 740,000 colors can be simultaneously displayed on an 8-bit/pixel system as against the 256 colors normally associated with 8-bit/pixel systems. This is achieved by a combination of the antialiasing function and a unique dynamic palette load

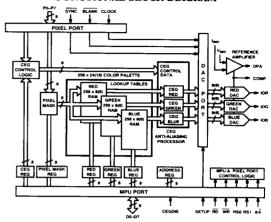

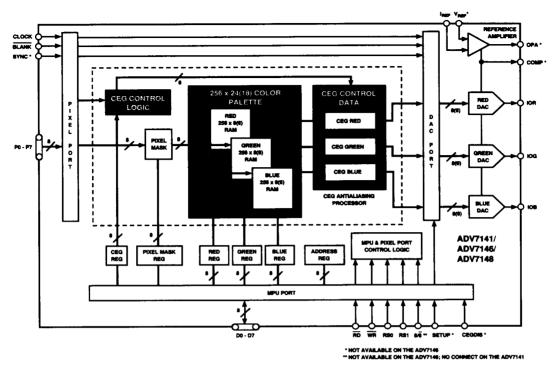

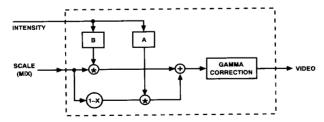

## FUNCTIONAL BLOCK DIAGRAM

(DPL) feature. DPL allows for color palette writes (color alterations) during a single frame image.

The CEG/DAC combines a color lookup table (CLUT), three matched video speed computational units and associated control logic as well as three digital-to-analog converters (DACs). These all combine to significantly enhance the video image display quality of standard 8-bit/pixel graphics systems.

The ADV7148 and ADV7141 are pin and functional compatible with the ADV478 and ADV471, with the exception that the ADV7148 and the ADV7141 do not contain the overlay palette. The ADV7146 is pin and functional compatible with the ADV476 and the Inmos IMSG171/176.

CEG requires two closely connected components—the CEG/DAC chip and the software driver. Conventional antialiasing schemes are implemented entirely in software and operate on the pixel data in the graphics pipeline, resulting in a significant speed performance penalty. In contrast, the CEG software driver takes application software information and encodes the frame buffer with a sequence of data and commands for the CEG/DAC. The CEG/DAC hardware performs all of the antialiasing calculations. In this way, the visual benefits of antialiased graphics are provided with a minimal increase in software overhead.

\*Protected by U.S. Patent Nos. 4,482,893 and 4,704,605.

†Inmos is a trademark of Inmos Ltd.

Personal System/2, VGA and 8514/A are trademarks of International Business Machines Corp.

Edsun Continuous Edge Graphics and CEG are registered trademarks of Edsun Laboratories, Inc.

ADV is a registered trademark of Analog Devices, Inc.

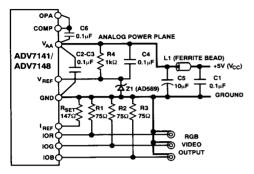

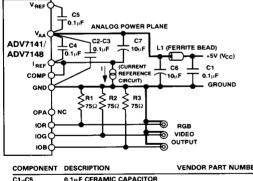

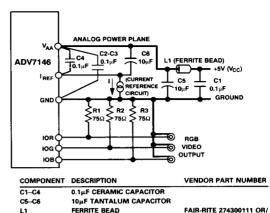

# $\begin{array}{l} \textbf{ADV7141/ADV7146/ADV7148} - \textbf{SPECIFICATIONS} \text{ } (\textbf{V}_{\textbf{AL}}^{1} = 5 \text{ } \textbf{V}; \text{ } \textbf{SETUP} = 8/6 = \textbf{V}_{\textbf{AL}}; \\ \textbf{I}_{\textbf{REF}} = -8.39 \text{ mA (ADV7146)}; \text{ } \textbf{R}_{\textbf{L}} = 37.5 \text{ } \Omega, \text{ } \textbf{C}_{\textbf{L}} = 10 \text{ pF}; \text{ } \textbf{R}_{\textbf{SET}} = 147 \text{ } \Omega. \text{ } \textbf{All Specifications } \textbf{T}_{\textbf{min}} \text{ } \textbf{to } \textbf{T}_{\textbf{max}^{2}} \text{ unless otherwise noted.} \\ \end{array}$

| Parameter                                          | All Versions        | Units            | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------|---------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STATIC PERFORMANCE                                 |                     |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Resolution (Each DAC)                              | 8                   | Bits             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Accuracy (Each DAC)                                |                     |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Integral Nonlinearity <sup>3</sup>                 | $\pm 1 (\pm 1/2)$   | LSB max          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Differential Nonlinearity                          | ± 1                 | LSB max          | Guaranteed Monotonic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Gray Scale Error                                   | ±5                  | % Gray Scale     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Coding                                             |                     | Binary           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DIGITAL INPUTS                                     |                     |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Input High Voltage, VINH                           | 2                   | V min            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Input Low Voltage, VINL                            | 0.8                 | V max            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Input Current, I <sub>IN</sub>                     | ±1                  | μA max           | $V_{IN} = 0.4 \text{ V or } 2.4 \text{ V}$<br>$f = 1 \text{ MHz}, V_{IN} = 2.4 \text{ V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Input Capacitance, CIN                             | 7                   | pF max           | $f = 1 \text{ MHz}, V_{IN} = 2.4 \text{ V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DIGITAL OUTPUTS                                    |                     |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Output High Voltage, VOH                           | 2.4                 | V min            | $I_{SOURCF} = 400 \mu A$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Output Low Voltage, Vol                            | 0.4                 | V max            | $I_{SINK} = 3.2 \text{ mA}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Floating-State Leakage Current                     | 50                  | μA max           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Floating-State Leakage Capacitance                 | 7                   | pF max           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ANALOG OUTPUTS                                     |                     |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Gray Scale Current Range                           | 20                  | mA max           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Output Current                                     | 20                  |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| White Level Relative to Blank/Black                | 17.4/20.40          | mA min/mA max    | Typically 19.05 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| White Level Relative to Black <sup>4</sup>         | 16.5/18.50          | mA min/mA max    | Typically 17.62 mA, SETUP = $V_{AA}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Black Level Relative to Blank <sup>4</sup>         | 0.95                | mA min           | Typically 1.44 mA, SETUP = VAA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                    | 1.90                | mA max           | a y promis, and a second a second and a second a second and a second a second and a second and a second and a |

| (Pedestal = 7.5 IRE) Black Level Relative to Blank | 0                   | μA min           | Typically 5 μA, SETUP = GNP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                    | 50                  | μA max           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| (Pedestal = 0 IRE)                                 | 6.29                | mA min           | Typically 7.62 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Blank Level <sup>4</sup>                           | 8.96                | mA max           | Typically 7.02 IIII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| (Sync Enabled)                                     | 0                   | μA min           | Typically 5 μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Blank Level                                        | 50                  | μA max           | Typically 5 pm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| (Sync Disabled)                                    | 0                   | μA min           | Typically 5 μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Sync Level <sup>4</sup>                            | 50                  | μA max           | 1 J picary 5 pri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ron :                                              | 69.1                | μA typ           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LSB size                                           | 5                   | μα typ<br>% max  | Typically 2%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |