# **MFR4200**

**Data Sheet**

FlexRay Communication Controllers

MFR4200 Rev. 0 8/2005

# **MFR4200 Data Sheet**

MFR4200 Rev. 0 8/2005

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify that you have the latest information available, refer to <a href="http://www.freescale.com">http://www.freescale.com</a>

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

## **Revision History**

| Date    | Revision<br>Level | Description      | Page<br>Number(s) |

|---------|-------------------|------------------|-------------------|

| 08/2005 | 0                 | Initial release. | N/A               |

Introduction

**Device Overview**

MFR4200 FlexRay Communication Controller

**Dual Output Voltage Regulator (VREG3V3V2)**

**Clocks and Reset Generator**

**Oscillator (OSCV2)**

**Electrical Characteristics**

**Package Information**

**Printed Circuit Board Layout Recommendations**

**MFR4200 Protocol Implementation Document**

**Index of Registers**

# **Contents**

| Sed | ction N | Number Title                            | Page |

|-----|---------|-----------------------------------------|------|

|     |         | Chapter 1 Introduction                  |      |

| 1.1 | Audien  | nce                                     | 21   |

| 1.2 | Additio | onal Reading                            | 21   |

| 1.3 | Termin  | nology                                  | 22   |

| 1.4 | Part Nu | Sumber Coding                           | 23   |

|     |         | Chapter 2                               |      |

|     |         | Device Overview                         |      |

| 2.1 | Introdu | uction                                  | 25   |

|     | 2.1.1   |                                         |      |

|     | 2.1.2   | 1                                       |      |

|     | 2.1.3   | L L                                     |      |

|     | 2.1.4   | $oldsymbol{c}$                          |      |

|     | 2.1.5   | <b>√</b> 1                              |      |

|     | 2.1.6   |                                         |      |

| 2.2 | _       | Descriptions                            |      |

|     | 2.2.1   |                                         |      |

|     | 2.2.2   | 8 · · · · · · · · · · · · · · · · · · · |      |

|     | 2.2.3   | $\mathcal{E}$                           |      |

|     | 2.2.4   | 11 2                                    |      |

| 2.3 | •       | m Clock Description                     |      |

| 2.4 |         | s of Operation                          |      |

|     | 2.4.1   |                                         |      |

|     | 2.4.2   | 1                                       |      |

|     | 2.4.3   |                                         |      |

|     | 2.4.4   |                                         |      |

|     | 2.4.5   | → · · · · · · · · · · · · · · · · · · · |      |

|     | 2.4.6   |                                         |      |

| 2.5 |         | s and Interrupts                        |      |

|     | 2.5.1   |                                         |      |

|     | 2.5.2   |                                         |      |

|     | 2.5.3   | Interrupt Sources                       | 51   |

| Sec  | tion N         | umber Title                                                      | Page  |

|------|----------------|------------------------------------------------------------------|-------|

|      |                | Chapter 3                                                        |       |

|      |                | MFR4200 FlexRay Communication Contr                              | oller |

| 3.1  | Introduc       | ction                                                            | 53    |

|      | 3.1.1          | MFR4200 Features                                                 |       |

|      | 3.1.2          | MFR4200 Implementation Parameters and Constraints                |       |

| 3.2  | Memory         | y Map and Registers                                              |       |

|      | 3.2.1          | Introduction                                                     |       |

|      | 3.2.2          | Register Map Summary                                             |       |

|      | 3.2.3          | Register Descriptions                                            |       |

| 3.3  | _              | e Buffer                                                         |       |

|      | 3.3.1          | Message Buffer Layout                                            |       |

|      | 3.3.2          | Message Buffer Field Descriptions                                |       |

|      | 3.3.3          | Message Buffer Slot Status Vector                                |       |

|      | 3.3.4          | Message ID                                                       |       |

|      | 3.3.5          | NMVector Fields                                                  |       |

|      | 3.3.6          | Data[0:31] — Data Fields                                         |       |

| 3.4  | _              | e Buffer Control, Configuration, Status and Filtering Register S |       |

|      | 3.4.1          | Message Buffer Control, Configuration and Status Register        |       |

|      | 3.4.2          | Message Buffer Filter Registers                                  |       |

| a =  | 3.4.3          | Receive FIFO Filters                                             |       |

| 3.5  | _              | e Buffer Handling and Operations                                 |       |

|      | 3.5.1          | Introduction                                                     |       |

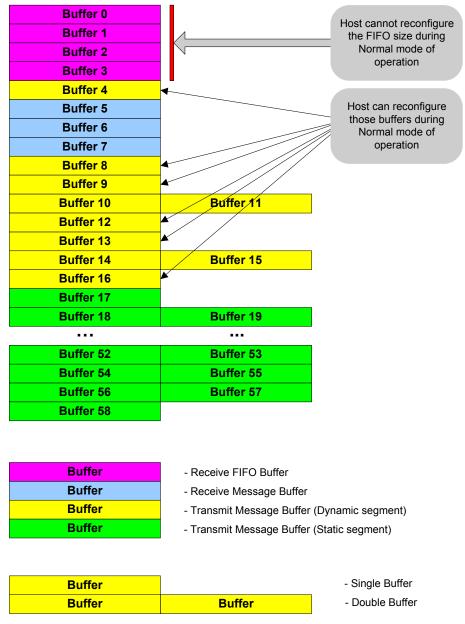

|      | 3.5.2          | Buffer Map                                                       |       |

|      | 3.5.3          | Active Message Buffers                                           |       |

|      | 3.5.4          | Buffer Configuration                                             |       |

|      | 3.5.5          | Buffer Reconfiguration in the Normal State of Operation          |       |

| 2.6  | 3.5.6          | Message Buffer Operations                                        |       |

| 3.6  |                | FIFO Function                                                    |       |

| 3.7  |                | ontroller Interfaces                                             |       |

|      |                | MFR4200 Asynchronous Memory Interface                            |       |

| 2.0  | 3.7.2          | MFR4200 HCS12 Interface                                          |       |

| 3.8  |                | 1 4/10 MHz Output Clock                                          |       |

| 3.9  |                | Inication Controller States                                      |       |

|      | 3.9.1          | Hard Reset State                                                 |       |

|      | 3.9.2          | Configuration State                                              |       |

|      | 3.9.3<br>3.9.4 | Diagnosis Stop State                                             |       |

|      |                |                                                                  |       |

| 2 10 | 3.9.5          | Normal Passive State                                             |       |

| 3.10 | _              | Port                                                             |       |

|      |                | Debug Port Overview                                              |       |

|      |                | Debug Port Functions                                             |       |

|      | 5.10.3         | Debug Port Function Timing                                       |       |

| Sec      | ction N  | lumber Title                                                                  | Page       |

|----------|----------|-------------------------------------------------------------------------------|------------|

|          |          | Chapter 4 Dual Output Voltage Regulator (VREG3V3V                             | <b>(2)</b> |

| 4.1      | Introdu  |                                                                               | •          |

|          | 4.1.1    | Features                                                                      |            |

|          | 4.1.2    | Modes of Operation                                                            | 207        |

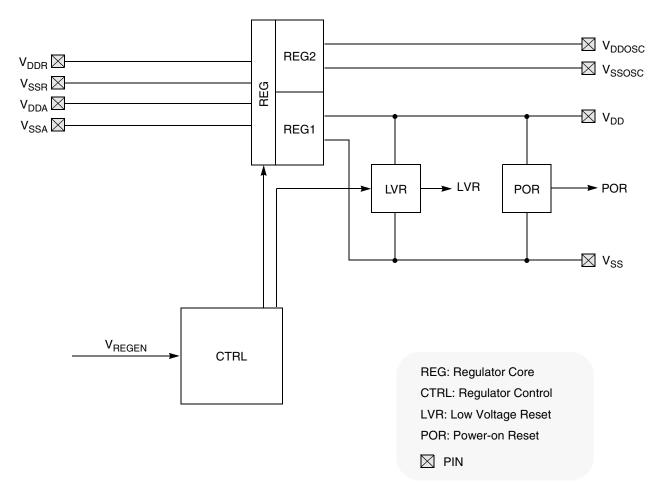

|          | 4.1.3    | Block Diagram                                                                 | 207        |

| 4.2      | Externa  | al Signal Description                                                         | 209        |

|          | 4.2.1    | V <sub>DDR</sub> , V <sub>SSR</sub> — Regulator Power Input                   |            |

|          | 4.2.2    | V <sub>DDA</sub> , V <sub>SSA</sub> — Regulator Reference Supply              | 209        |

|          | 4.2.3    | V <sub>DD</sub> , V <sub>SS</sub> — Regulator Output1 (Core Logic)            | 210        |

|          | 4.2.4    | V <sub>DDOSC</sub> , V <sub>SSOSC</sub> — Regulator Output2 (OSC)             |            |

|          | 4.2.5    | V <sub>REGEN</sub> — Optional Regulator Enable                                |            |

| 4.3      |          | onal Description                                                              |            |

|          | 4.3.1    | REG — Regulator Core                                                          |            |

|          | 4.3.2    | Full-performance Mode                                                         |            |

|          | 4.3.3    | POR — Power On Reset                                                          |            |

|          | 4.3.4    | LVR — Low Voltage Reset                                                       |            |

| 4.4      | 4.3.5    | CTRL — Regulator Control                                                      |            |

| 4.4      |          |                                                                               |            |

|          | 4.4.1    | Power On Reset                                                                |            |

|          | 4.4.2    | Low Voltage Reset                                                             |            |

|          |          | Chapter 5                                                                     |            |

|          |          | Clocks and Reset Generator                                                    |            |

| 5.1      | Introdu  | action                                                                        |            |

|          | 5.1.1    | Features                                                                      |            |

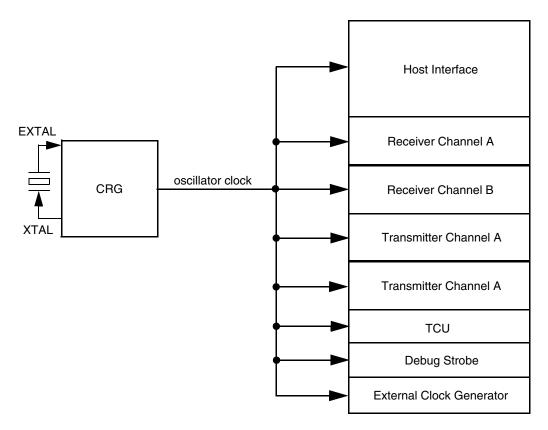

| 5.2      | Function | onal Description                                                              | 214        |

|          | 5.2.1    | MFR4200 Pins Relevant to the CRG                                              |            |

|          | 5.2.2    | Reset Generation and CLKOUT Control                                           |            |

|          |          | Chapter 6                                                                     |            |

|          |          | Oscillator (OSCV2)                                                            |            |

| 6.1      | Introdu  |                                                                               |            |

|          | 6.1.1    | Features                                                                      |            |

| <i>c</i> | 6.1.2    | Modes of Operation                                                            |            |

| 6.2      |          | al Signal Description                                                         |            |

|          | 6.2.1    | V <sub>DDOSC</sub> and V <sub>SSOSC</sub> — OSC Operating Voltage, OSC Ground |            |

| (2       | 6.2.2    | EXTAL and XTAL — Clock/Crystal Source Pins                                    |            |

| 6.3      | Functio  | onal Description                                                              | 218        |

9

| Sec         | ction Number                   | Title                              | Page   |

|-------------|--------------------------------|------------------------------------|--------|

|             | Ele                            | Appendix A ctrical Characteristics |        |

| <b>A.</b> 1 | General                        |                                    | 219    |

|             | A.1.1 Parameter Classification |                                    | 219    |

|             | A.1.2 Power Supply             |                                    |        |

|             | A.1.3 Pins                     |                                    |        |

|             | •                              |                                    |        |

|             |                                | ings                               |        |

|             |                                | ch-up Immunity                     |        |

|             | 1 0                            |                                    |        |

|             |                                | hermal Characteristics             |        |

|             |                                |                                    |        |

|             | 11 •                           |                                    |        |

| A.2         |                                |                                    |        |

|             |                                |                                    |        |

|             | 1 1                            | age Drops                          |        |

| A 2         | *                              |                                    |        |

| A.3         |                                |                                    |        |

|             | 1                              |                                    |        |

| A.4         |                                |                                    |        |

| A.4<br>A.5  |                                | 1                                  |        |

|             |                                | Appendix B                         |        |

|             | P                              | Package Information                |        |

| <b>B</b> .1 | 64-pin LQFP package            |                                    |        |

|             | Duinted Civersit               | Appendix C                         |        |

|             | Printed Circuit                | Board Layout Recommenda            | ations |

|             |                                | Appendix C                         |        |

|             | MFR4200 Pro                    | tocol Implementation Docun         | nent   |

| <b>C</b> .1 | Introduction                   |                                    | 245    |

|             | C.1.1 Purpose                  |                                    | 245    |

|             | C.1.2 Structure                |                                    | 245    |

|             |                                |                                    |        |

| C.2         |                                |                                    |        |

| C.3         |                                |                                    |        |

|             |                                |                                    |        |

|             |                                |                                    |        |

|             | C.3.3 NRZ Decoding             |                                    |        |

|             |                                |                                    |        |

MFR4200 Data Sheet, Rev. 0

10 Freescale Semiconductor

| Sec          | tion N  | umber Title                              | Page |

|--------------|---------|------------------------------------------|------|

|              | C.3.4   | Signal Integrity                         | 250  |

| <b>C</b> .4  | Frame F | Format                                   |      |

| C.5          | Media A | Access Control                           |      |

| <b>C</b> .6  | Frame a | and Symbol Processing                    |      |

| <b>C</b> .7  | Wakeup  | o, Startup, and Reintegration            |      |

|              | C.7.1   | Introduction                             |      |

|              | C.7.2   | Cluster Wakeup                           |      |

|              | C.7.3   | Communication Startup and Reintegration  |      |

| <b>C</b> .8  | Clock S | Synchronization                          |      |

|              | C.8.1   | Introduction                             |      |

|              | C.8.2   | Time Representation                      |      |

|              | C.8.3   | Synchronization Process                  |      |

|              | C.8.4   | Clock Startup                            |      |

|              | C.8.5   | Time Measurement                         |      |

|              | C.8.6   | Correction Term Calculation              | 252  |

|              | C.8.7   | Clock Correction                         |      |

|              | C.8.8   | Sync Frame Configuration Rules           |      |

| <b>C</b> .9  | Control | ler Host Interface                       | 253  |

| <b>C</b> .10 | Device  | Specific Power Modes                     | 253  |

|              |         | ardian Schedule Monitoring               |      |

|              |         | Parameters and Configuration Constraints |      |

|              | •       | System Parameters                        |      |

|              |         | Configuration Constraints                | 254  |

# Appendix D Index of Registers

Section Number Title Page

# **List of Figures**

| Figure Nu    | mber Title                                                           | Page |

|--------------|----------------------------------------------------------------------|------|

| Figure 1-1.  | Order Part Number Coding                                             | 23   |

| Figure 2-1.  | MFR4200 Block Diagram                                                | 29   |

| Figure 2-2.  | Pin Assignments for MFR4200 in 64-pin LQFP                           | 32   |

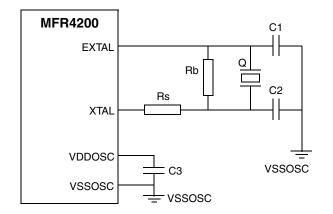

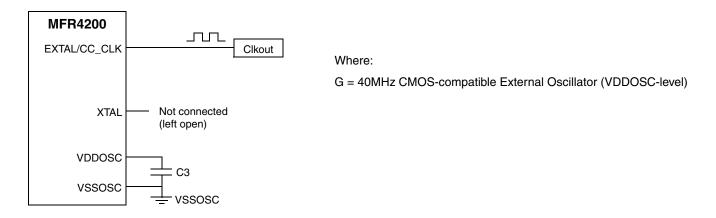

| Figure 2-3.  | Pierce Oscillator Connections                                        | 42   |

| Figure 2-4.  | External Clock Connections                                           | 43   |

| Figure 2-5.  | Clock Connections                                                    | 45   |

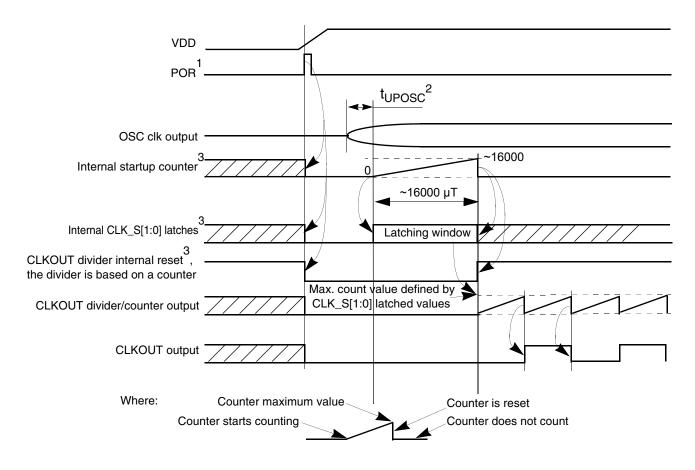

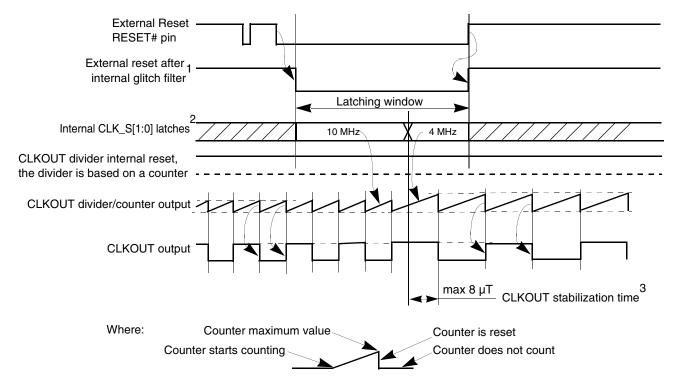

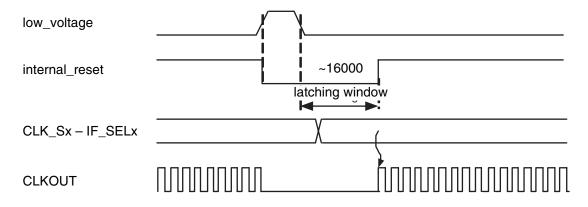

| Figure 2-6.  | CLKOUT Generation During Power-on Reset                              | 47   |

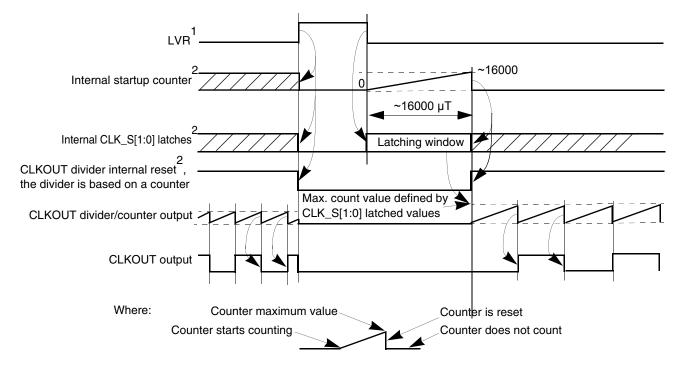

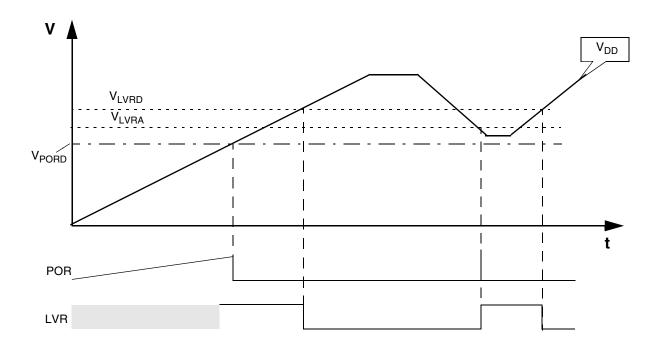

| Figure 2-7.  | CLKOUT Generation during Low Voltage Reset                           | 48   |

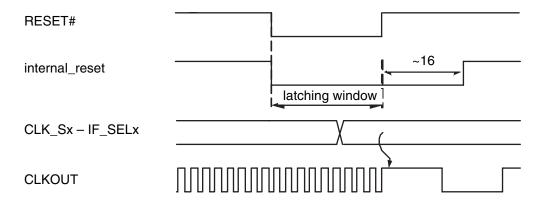

| Figure 2-8.  | CLKOUT Generation During External Hard Reset                         | 49   |

| Figure 2-9.  | Example: Connecting a FlexRay Optical/Electrical PHY to the MFR4200. | 50   |

| Figure 2-10. | Example: Connecting an RS485 PHY to the MFR4200                      | 50   |

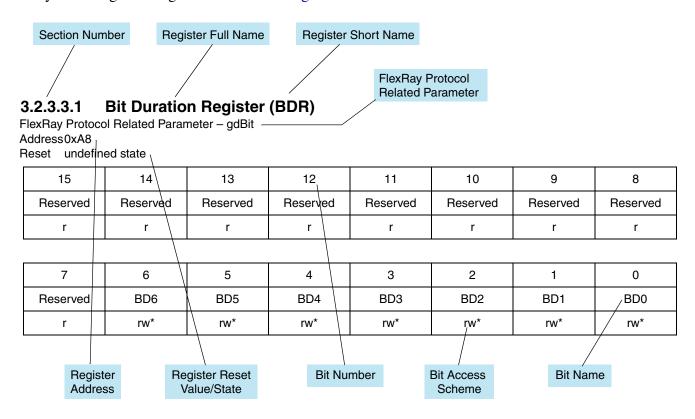

| Figure 3-1.  | Key to Register Diagrams                                             | 61   |

| Figure 3-2.  | Module Version Register 0                                            | 62   |

| Figure 3-3.  | Module Version Register 1                                            | 62   |

| Figure 3-4.  | Magic Number Register                                                | 63   |

| Figure 3-5.  | Module Configuration Register 0                                      | 64   |

| Figure 3-6.  | Module Configuration Register 1                                      | 66   |

| Figure 3-7.  | Host Interface Pins Drive Strength Register                          | 67   |

| Figure 3-8.  | Physical Layer Pins Drive Strength Register                          | 68   |

| Figure 3-9.  | Host Interface Pins Pullup/down Enable Register                      | 68   |

| Figure 3-10. | Host Interface Pins Pullup/down Control Register                     | 69   |

| Figure 3-11. | Physical Layer Pins Pullup/down Enable Register                      | 69   |

| Figure 3-12. | Physical Layer Pins Pullup/down Control Register                     | 70   |

| Figure 3-13. | Voltage Regulator Status Register                                    | 70   |

| Figure 3-14. | Bit Duration Register                                                | 71   |

| Figure 3-15. | Delay Compensation Channel A Register                                | 72   |

| Figure 3-16. | Delay Compensation Channel B Register                                | 72   |

| Figure 3-17. | Cluster Drift Damping Register                                       | 73   |

| Figure 3-18. | Maximum Sync Frames Register                                         | 73   |

| Figure 3-19. | Nominal Macrotick Length Register                                    | 74   |

| Figure 3-20. | Microticks Per Cycle Low Register                                    | 74   |

| Figure 3-21. | Microticks Per Cycle High Register                                   | 75   |

| Figure Nu    | umber Title                                    | Page |

|--------------|------------------------------------------------|------|

| Figure 3-22. | Static Slot Length Register                    | 75   |

| Figure 3-23. | Number of Static Slots Register                | 76   |

| Figure 3-24. | Static Payload Length Register                 | 76   |

| Figure 3-25. | Minislot Length Register                       |      |

| Figure 3-26. | Minislot Action Point Offset Register          |      |

| Figure 3-27. | Static Slot Action Point Offset Register       |      |

| Figure 3-28. | Latest Dynamic Transmission Start Register     |      |

| Figure 3-29. | Maximum Payload Length Dynamic Register        | 79   |

| Figure 3-30. | Symbol Window Configuration Register           | 79   |

| Figure 3-31. | Network Idle Time Configuration Register       | 80   |

| Figure 3-32. | Cycle Length Register                          | 80   |

| Figure 3-33. | Maximum Cycle Length Deviation Register        | 81   |

| Figure 3-34. | External Offset Correction Register            | 81   |

| Figure 3-35. | External Rate Correction Register              | 82   |

| Figure 3-36. | External Correction Control Register           | 82   |

| Figure 3-37. | Maximum Offset Correction Register             | 83   |

| Figure 3-38. | Maximum Rate Correction Register               | 84   |

| Figure 3-39. | Coldstart Maximum Register                     | 84   |

| Figure 3-40. | Transmit Start Sequence Length Register        |      |

| Figure 3-41. | Network Management Vector Length Register      |      |

| Figure 3-42. | Sync Frame Register                            | 86   |

| Figure 3-43. | Sync Frame Header Register                     | 86   |

| Figure 3-44. | Bus Guardian Tick Register                     | 87   |

| Figure 3-45. | Delay Counter Register                         | 87   |

| Figure 3-46. | Debug Port Control Register.                   |      |

| Figure 3-47. | Start of Offset Correction Cycle Time Register |      |

| Figure 3-48. | Idle Detection Length Register                 | 90   |

| Figure 3-49. | Symbol Window Control Register                 | 90   |

| Figure 3-50. | Wakeup Mechanism Control Register              | 91   |

| Figure 3-51. | Wakeup Symbol TX Idle Register                 | 91   |

| Figure 3-52. | Wakeup Symbol TX Low Register                  | 92   |

| Figure 3-53. | Listen Timeout With Noise Length Register      | 92   |

| Figure 3-54. | Protocol State Register                        | 93   |

| Figure 3-55. | Current Cycle Counter Value Register           | 94   |

| Figure 3-56. | Current Macrotick Counter Value Register       | 94   |

|              |                                                |      |

| Figure Nu    | imber Title                                                                     | Page |

|--------------|---------------------------------------------------------------------------------|------|

| Figure 3-57. | Offset Correction Value Register                                                | 95   |

| Figure 3-58. | Rate Correction Value Register                                                  | 95   |

| Figure 3-59. | Global Network Management Vector n Register, n = [0:5]                          | 96   |

| Figure 3-60. | Symbol Window Status Channel A Register                                         | 97   |

| Figure 3-61. | Symbol Window Status Channel B Register                                         | 98   |

| Figure 3-62. | Bus Guardian Status Register                                                    | 99   |

| Figure 3-63. | Startup Interrupt Enable Register                                               | 100  |

| Figure 3-64. | Maximum Odd Cycles Without Clock Correction Fatal Register                      | 101  |

| Figure 3-65. | Maximum Odd Cycles Without Clock Correction Passive Register                    | 101  |

| Figure 3-66. | Channel Status Error Counter n Register, n = [0:1]                              | 102  |

| Figure 3-67. | Interrupt Enable Register 0                                                     | 103  |

| Figure 3-68. | Slot Status Selection n Register, n = [0:3]                                     | 103  |

| Figure 3-69. | Slot Status Counter n Register, $n = [0:7]$                                     | 104  |

| Figure 3-70. | Slot Status Counter Condition n Register, n = [0:7]                             | 105  |

| Figure 3-71. | Slot Status Counter Incrementation Register                                     |      |

| Figure 3-72. | Slot Status Counter Interrupt Mask Register                                     | 107  |

| Figure 3-73. | Receive Buffer Interrupt Vector Register                                        | 108  |

| Figure 3-74. | Transmit Buffer Interrupt Vector Register                                       | 109  |

| Figure 3-75. | CHI Error Register                                                              | 109  |

| Figure 3-76. | Clock Correction Failed Counter Register                                        | 113  |

| Figure 3-77. | Error Handling Level Register                                                   | 113  |

| Figure 3-78. | Interrupt Status Register 0                                                     | 114  |

| Figure 3-79. | Startup Interrupt Status Register                                               | 118  |

| Figure 3-80. | Slot Status n Register, $n = [0:7]$                                             | 119  |

| Figure 3-81. | Odd Sync Frame ID n Register, n = [0:15]                                        | 120  |

| Figure 3-82. | Even Sync Frame ID n Register, n = [0:15]                                       |      |

| Figure 3-83. | Odd Measurement Channel A n Register, n = [0:15]                                | 121  |

| Figure 3-84. | Odd Measurement Channel B n Register, n = [0:15]                                |      |

| Figure 3-85. | Even Measurement Channel A n Register, n = [0:15]                               | 122  |

| Figure 3-86. | Even Measurement Channel B n Register, n = [0:15]                               |      |

| Figure 3-87. | Even Measurement Counter Register                                               | 124  |

| Figure 3-88. | Odd Measurement Counter Register                                                |      |

| Figure 3-89. | FIFO Size Register                                                              |      |

| Figure 3-90. | Message Buffer Control, Configuration and Status n Register, $n = [0.58] \dots$ |      |

| Figure 3-91. | Active Transmit Buffer Frame ID Register                                        |      |

| -            |                                                                                 |      |

| Figure Nu     | mber Title                                                                                   | Page  |

|---------------|----------------------------------------------------------------------------------------------|-------|

| Figure 3-92.  | Active Transmit Buffer Cycle Counter and Payload Length Register                             | 127   |

| Figure 3-93.  | Active Transmit Buffer Header CRC Register                                                   | 127   |

| Figure 3-94.  | Active Transmit Buffer Data n Register, n = [0:15]                                           | 128   |

| Figure 3-95.  | Active Transmit Buffer Message Buffer Slot Status Vector Register                            | 128   |

| Figure 3-96.  | Active Receive Buffer Frame ID Register                                                      | 129   |

| Figure 3-97.  | Active Receive Buffer Cycle Counter and Payload Length Register                              | 129   |

| Figure 3-98.  | Active Receive Buffer Header CRC Register                                                    |       |

| Figure 3-99.  | Active Receive Buffer Data n Register, $n = [0:15]$                                          | 130   |

| Figure 3-100. | Active Receive Buffer Message Buffer Slot Status Vector Register                             | 131   |

| Figure 3-101. | Active FIFO Buffer Frame ID Register                                                         | 131   |

| Figure 3-102. | Active FIFO Buffer Cycle Counter and Payload Length Register                                 | 132   |

| Figure 3-103. | Active FIFO Buffer Header CRC Register                                                       | 132   |

| Figure 3-104. | Active FIFO Buffer Data n Register, n = [0:15]                                               | 133   |

| Figure 3-105. | Active FIFO Buffer Message Buffer Slot Status Vector Register                                | 133   |

| Figure 3-106. | Sync Frame Acceptance Filter Value Register                                                  | 134   |

| Figure 3-107. | Sync Frame Acceptance Filter Mask Register                                                   | 134   |

| Figure 3-108. | Sync Frame Rejection Filter Register                                                         | 135   |

| Figure 3-109. | Cycle Counter Filter n Register, $n = [0.58]$                                                | 135   |

| Figure 3-110. | FIFO Acceptance Filter Message ID Value Register                                             | 136   |

| Figure 3-111. | FIFO Acceptance Filter Message ID Mask Register                                              |       |

| Figure 3-112. | FIFO Acceptance/Rejection Filter Channel Register                                            | 137   |

| Figure 3-113. | FIFO Rejection Filter Frame ID Value Register                                                | 138   |

| Figure 3-114. | FIFO Rejection Filter Frame ID Mask Register                                                 | 138   |

| Figure 3-115. | Timer Interrupt Configuration Register 0 Cycle Set                                           | 139   |

| Figure 3-116. | Timer Interrupt Configuration Register 0 Macrotick Offset                                    | 140   |

| Figure 3-117. | Timer Interrupt Configuration Register 1 Cycle Set                                           | 140   |

| Figure 3-118. | Timer Interrupt Configuration Register 1 High                                                | 141   |

| Figure 3-119. | Transmit Message Buffer Slot Status Vector                                                   | 146   |

| Figure 3-120. | Receive and Receive FIFO Message Buffer Slot Status Vector                                   | 147   |

| Figure 3-121. | BUFCSnR of a Receive Message Buffer                                                          |       |

| Figure 3-122. | BUFCSnR of a Transmit Message Single Buffer for the Dynamic Segmen                           | t 150 |

| Figure 3-123. | BUFCSnR of a Host Part Transmit Message Buffer of a Double Tx Buffer for the Dynamic Segment |       |

| Figure 3-124. | BUFCSnR of a Host Part Transmit Message Buffer of a Double Tx Buffer for the Static Segment  |       |

| Figure Nu     | mber little Pa                                                                                             | age   |

|---------------|------------------------------------------------------------------------------------------------------------|-------|

| Figure 3-125. | BUFCSnR of a Single Transmit Message Buffer for the Static Segment                                         | . 151 |

| Figure 3-126. | BUFCSnR of a CC Part Transmit Message Buffer of a Double Tx Buffer for Dynamic and Static Segment          | . 152 |

| Figure 3-127. | BUFCSnR of FIFO Buffer                                                                                     | . 152 |

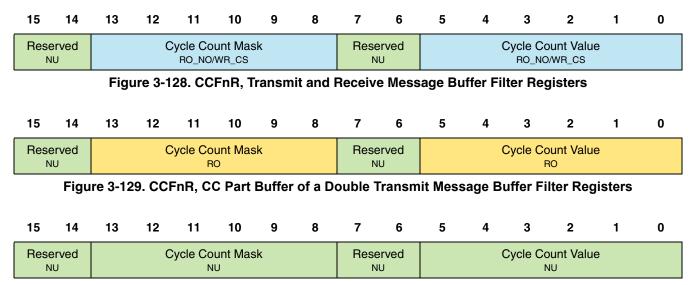

|               | CCFnR, Transmit and Receive Message Buffer Filter Registers                                                |       |

| Figure 3-129. | CCFnR, CC Part Buffer of a Double Transmit Message Buffer Filter Registers                                 | . 158 |

| Figure 3-130. | CCFnR, FIFO Buffer Filter Registers                                                                        | . 158 |

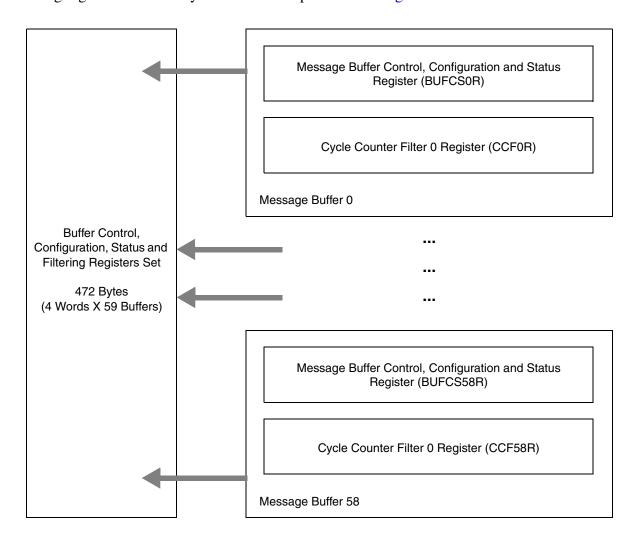

| Figure 3-131. | Buffer Control, Configuration, Status/Filtering Register Set for Transmit/Receive Buffers                  | . 161 |

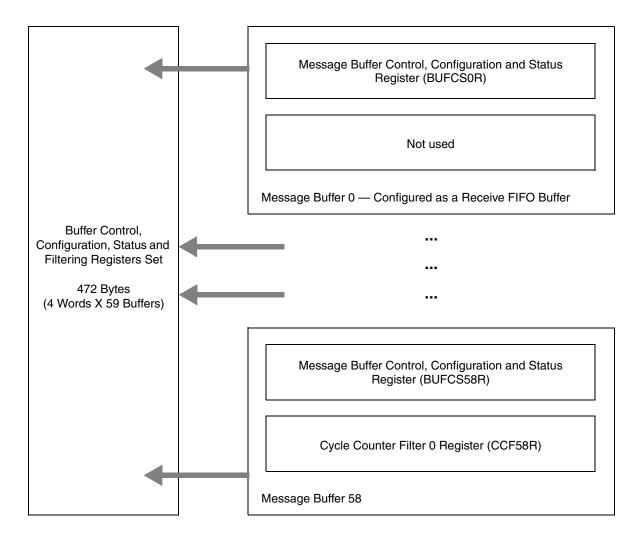

| Figure 3-132. | Buffer Control, Configuration, Status/Filtering Register Set for Receive FIFO Buffers                      | s 163 |

| Figure 3-133. | Buffer Busy Bit Timing for a Transmit Message Buffer                                                       | . 165 |

| Figure 3-134. | Example of a Buffer Configuration                                                                          | . 170 |

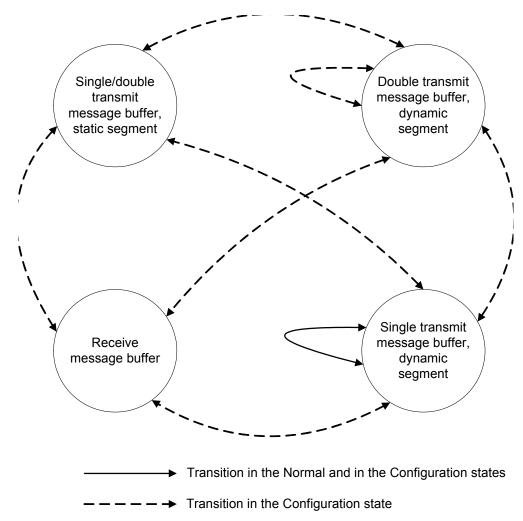

| Figure 3-135. | Transition Scheme Between Different Buffer Types Depending on Operational Mode of CC                       | . 173 |

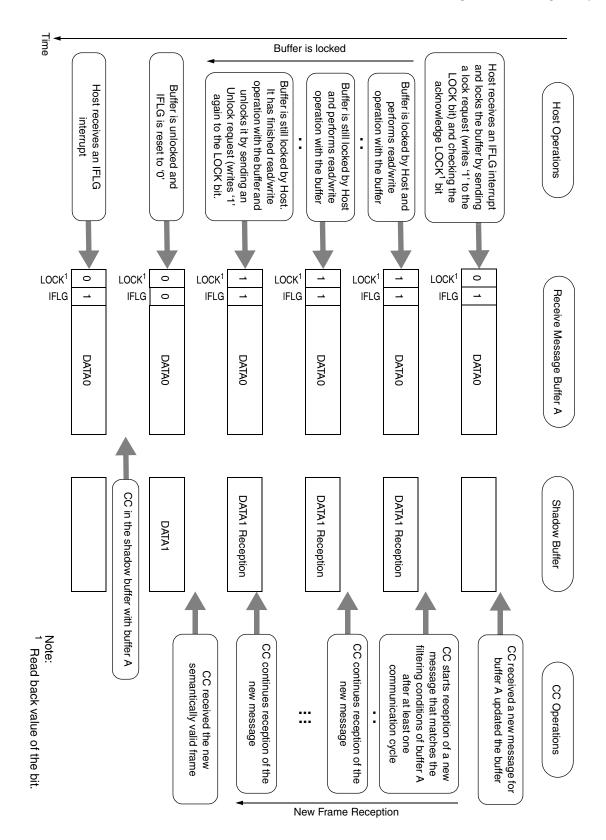

| Figure 3-136. | Operations During a Frame Reception                                                                        | . 175 |

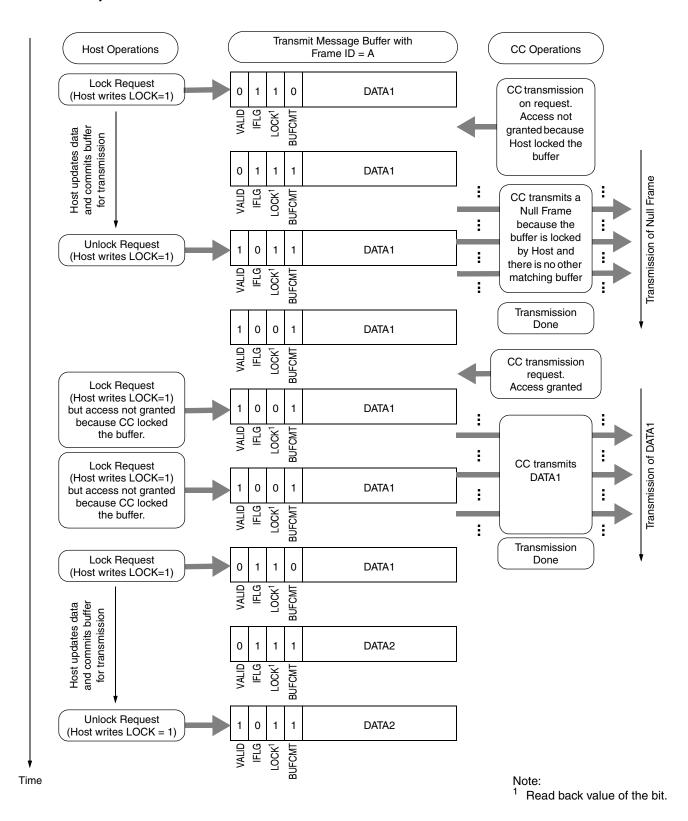

| Figure 3-137. | Operations with a Single Transmit Message Buffer during an Event Type of Transmission for a Static Segment | . 180 |

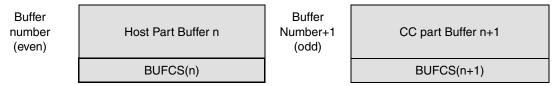

| Figure 3-138. | Double Transmit Message Buffer Structure                                                                   | . 181 |

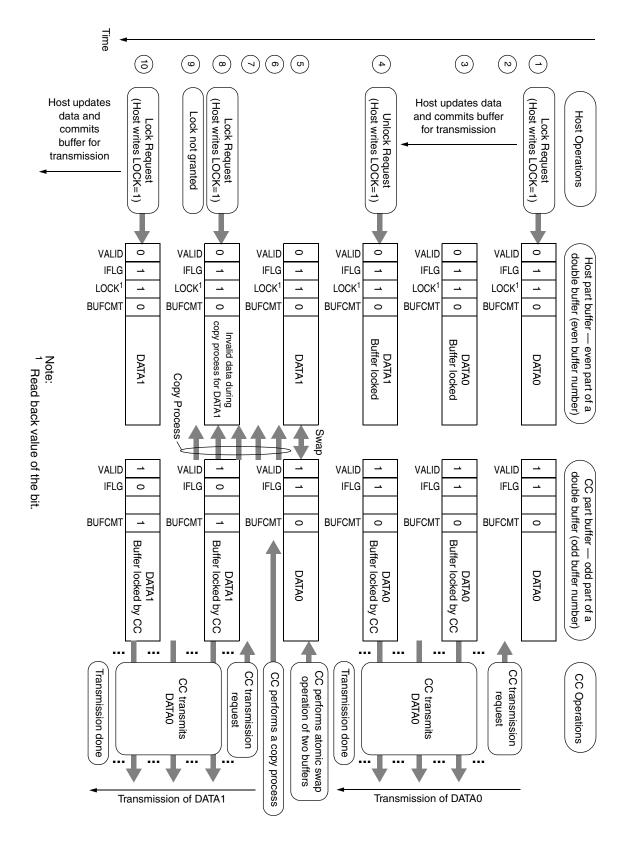

| Figure 3-139. | Doubled Buffer Data Collection with State Driven Transmit Operation                                        | . 184 |

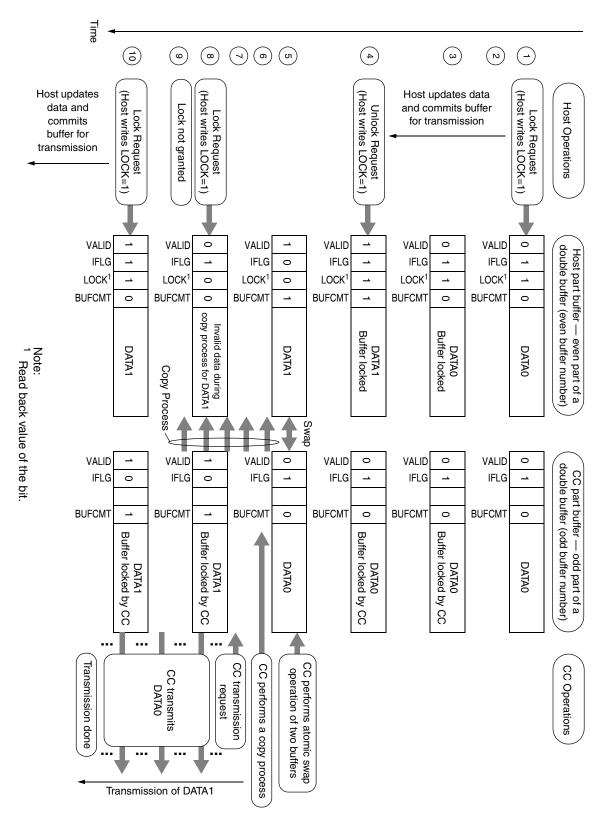

| Figure 3-140. | Doubled Buffer Data collection with Event Driven Transmit Operation                                        | . 185 |

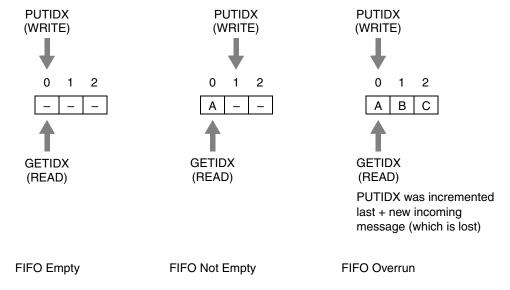

| Figure 3-141. | FIFO Status (Empty, Not Empty, Overrun) — Example of FIFO with Three Message Buffers                       | . 187 |

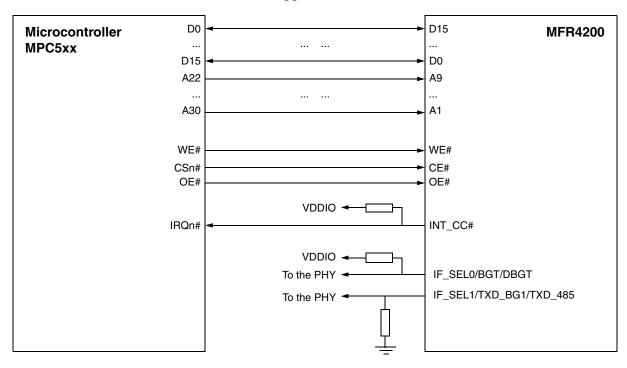

| Figure 3-142. | Connecting MFR4200 to MPC5xx Using the AMI (Example)                                                       | . 190 |

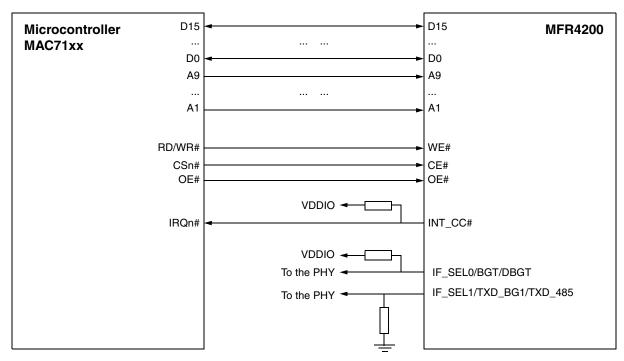

| Figure 3-143. | Connecting MFR4200 to MAC71xx Using the AMI (Example)                                                      | . 191 |

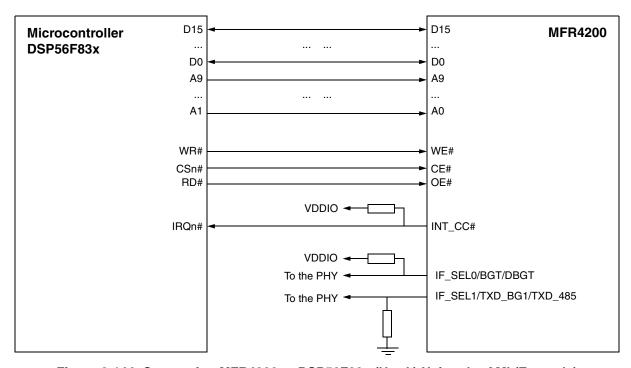

| Figure 3-144. | Connecting MFR4200 to DSP56F83x (Hawk) Using the AMI (Example)                                             | . 191 |

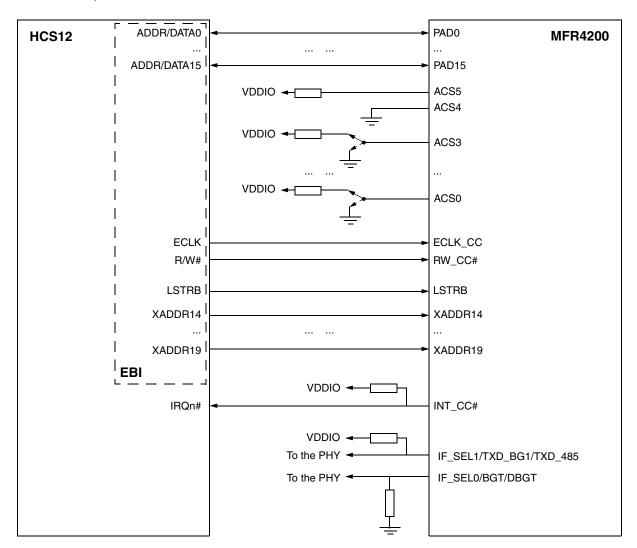

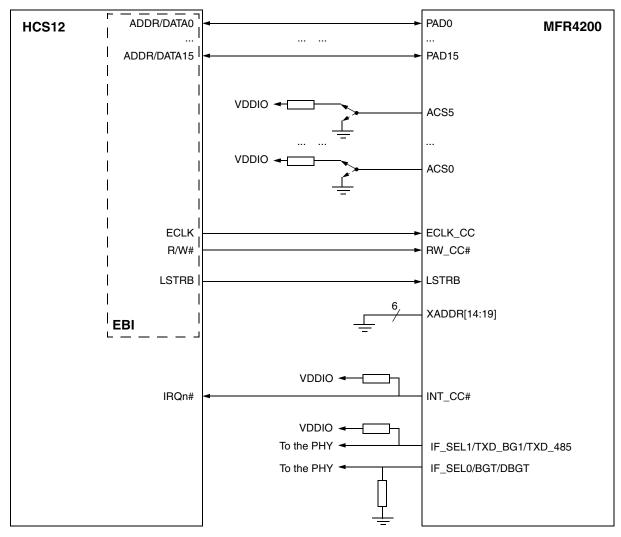

| Figure 3-145. | FlexRay CC to HCS12 Device Connection with HCS12 EBI Paged Mode Support                                    | . 193 |

| Figure 3-146. | FlexRay CC to HCS12 Device Connection with HCS12 EBI Unpaged Mode Support                                  | 194   |

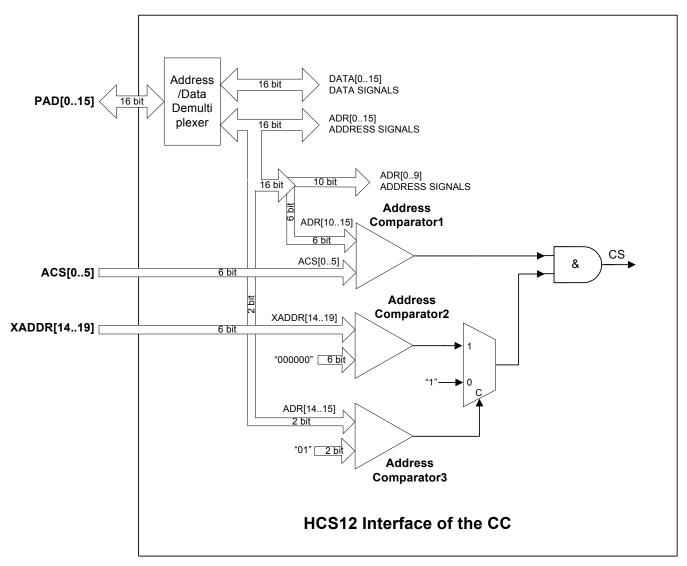

| Figure 3-147. | HCS12 interface Address Decoding and Internal CS Signal Generation                                         | . 195 |

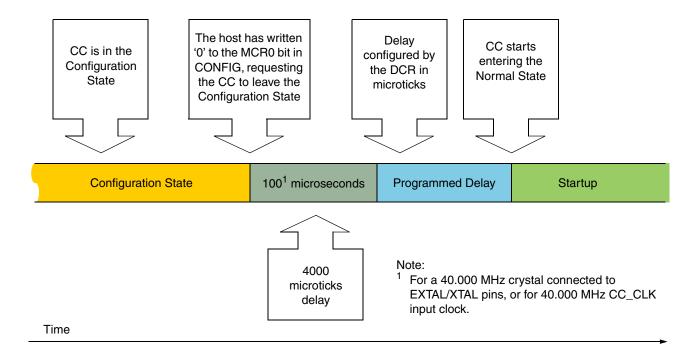

| Figure 3-148. | Timing Diagram of CC State Transition from Configuration State to Normal State                             | . 200 |

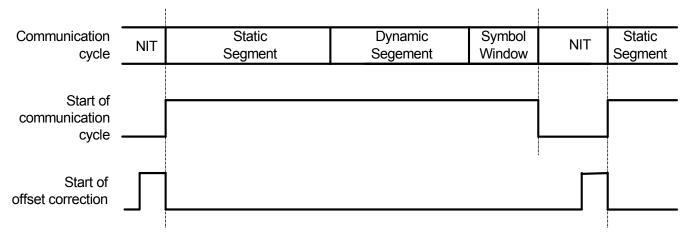

| Figure 3-149. | Start of Communication Cycle and Start of Offset Correction Functions Timing                               | . 204 |

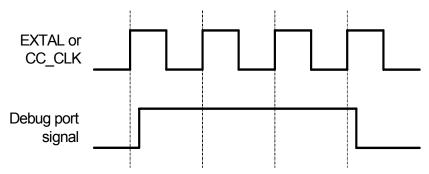

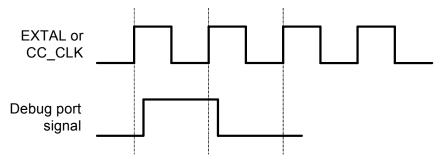

|               | Timing for Debug Functions with Three EXTAL or CC_CLK Clock Cycles of High State (Logic "1")               |       |

| Figure 3-151. | Slot Start in Static Segment Function Timing                                                               | . 205 |

| Figure 4-1.   | VREG3V3 Block Diagram                                                                                      | . 208 |

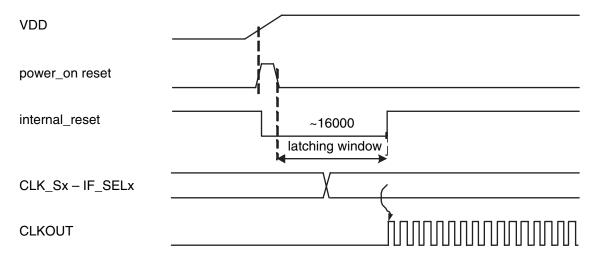

| Figure 5-1.   | Power-on Reset                                                                                             | . 215 |

| Figure 5-2.   | Low Voltage Reset                                                                                          | . 215 |

| Figure 5-3.   | External Reset                                                                                             | . 216 |

|               |                                                                                                            |       |

| Figure Num  | nber Title                                                               | Page |  |

|-------------|--------------------------------------------------------------------------|------|--|

| Figure A-1. | Voltage Regulator — Chip Power-up and Voltage Drops (not scaled)         | 230  |  |

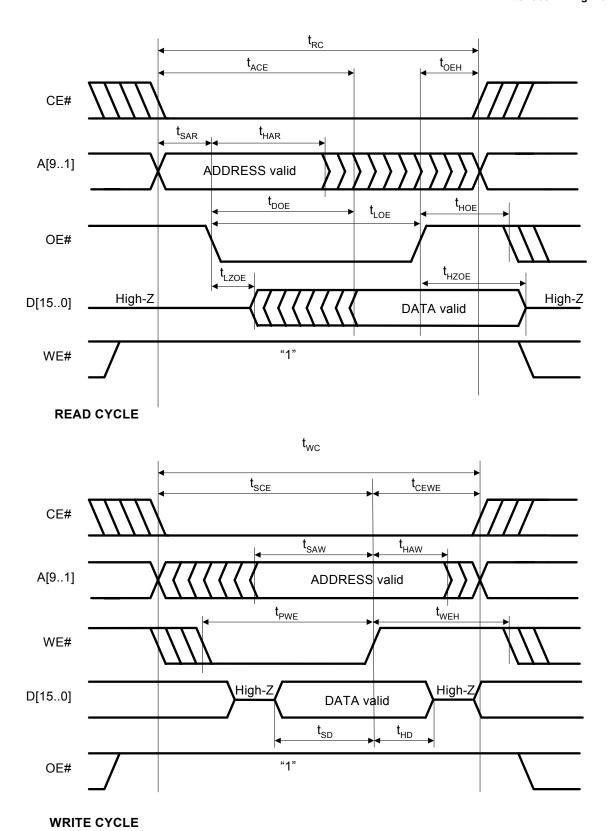

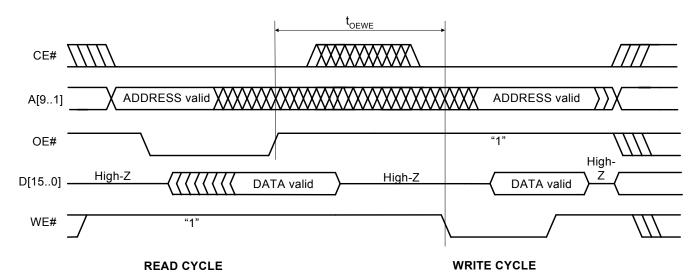

| Figure A-2. | AMI Interface Read and Write Timing Diagrams                             | 233  |  |

| Figure A-3. | AMI Interface Write-after-Read Transactions Timing Diagram               | 234  |  |

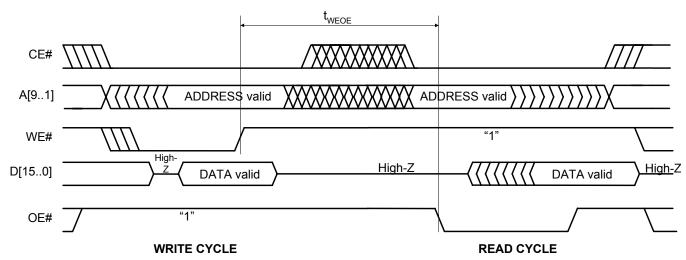

| Figure A-4. | AMI Interface Read-after-Write Transactions Timing Diagram               | 234  |  |

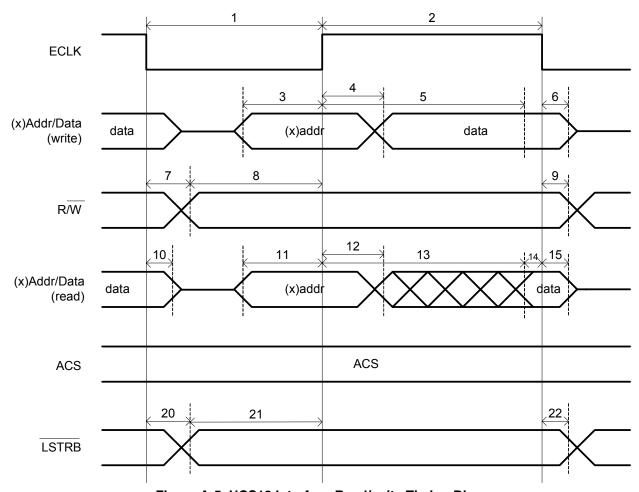

| Figure A-5. | HCS12 Interface Read/write Timing Diagram                                | 236  |  |

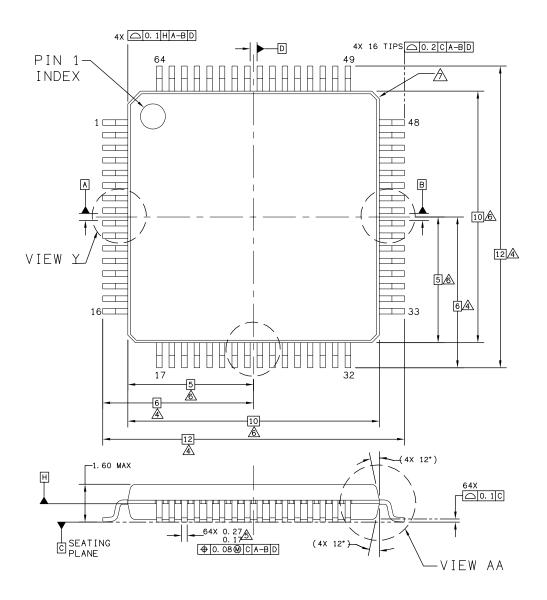

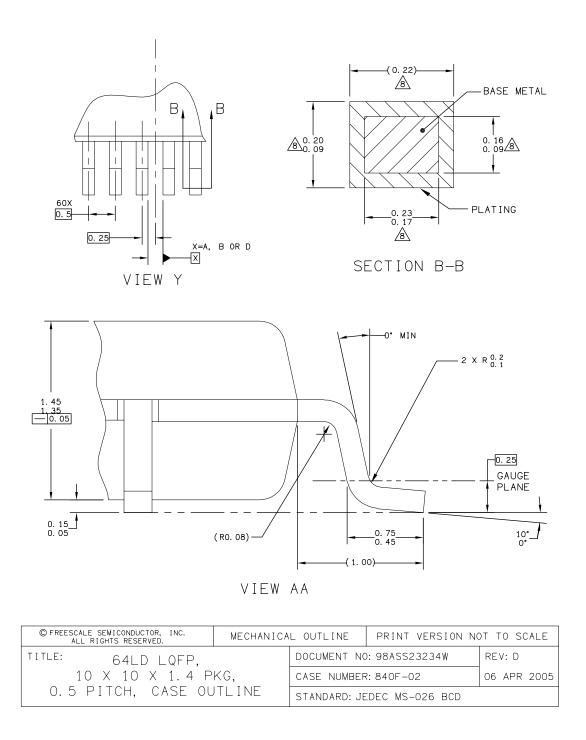

| Figure B-1. | 64-pin LQFP Mechanical Dimensions (Case N 840F-02) (Page 1)              | 239  |  |

| Figure B-2. | 64-pin LQFP Mechanical Dimensions (Case N 840F-02) (Page 2)              | 240  |  |

| Figure B-3. | 64-pin LQFP Mechanical Dimensions (Case N 840F-02) (Page 3)              | 241  |  |

| Figure C-1. | Recommended PCB Layout (64-pin LQFP) for Standard Pierce Oscillator Mode | 244  |  |

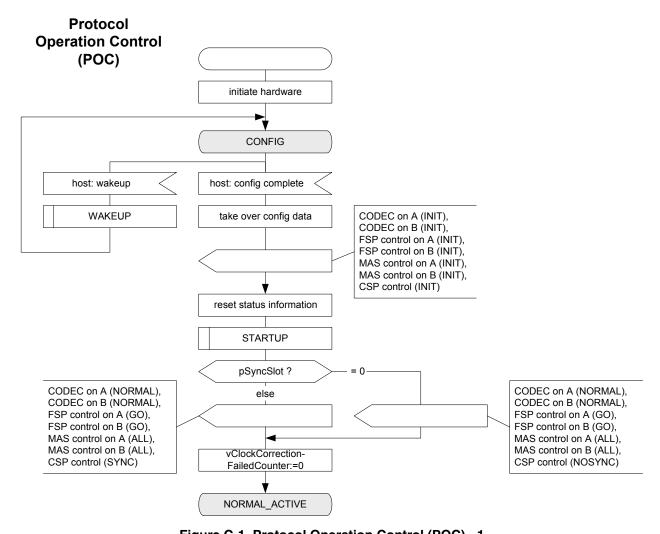

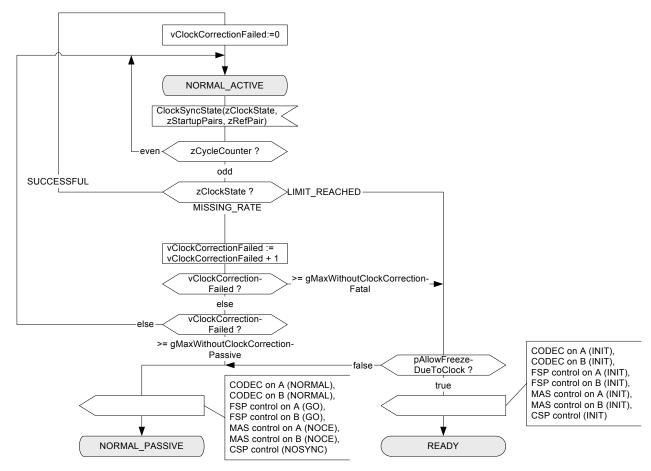

| Figure C-1. | Protocol Operation Control (POC) - 1                                     | 246  |  |

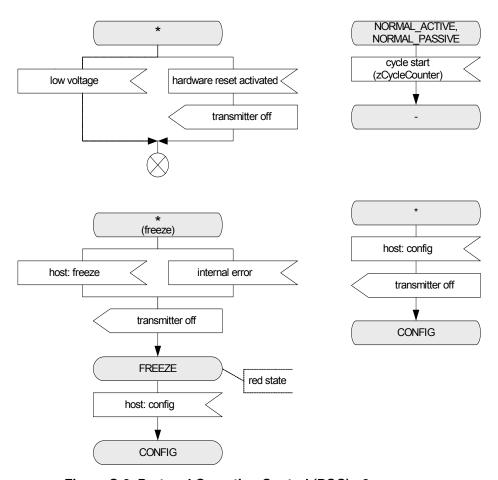

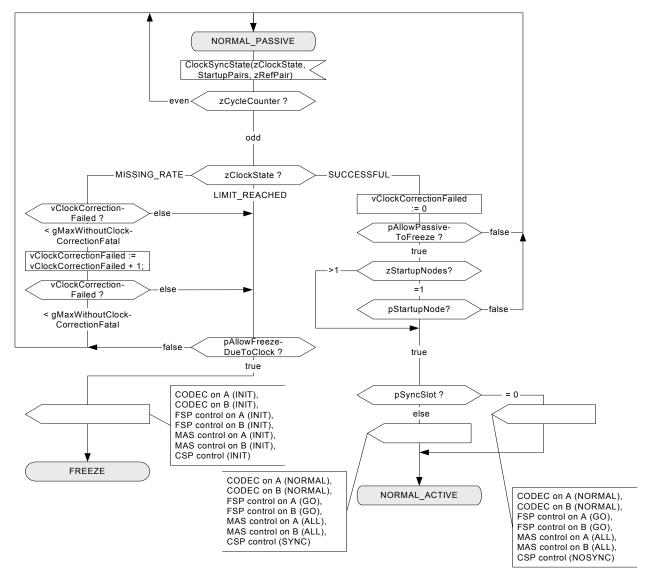

| Figure C-2. | Protocol Operation Control (POC) - 2                                     | 247  |  |

|             | POC — Normal Operation                                                   |      |  |

|             | POC — Passive Operation                                                  |      |  |

# **List of Tables**

| Table Nu    | ımber Title Pa                                                                      | age  |

|-------------|-------------------------------------------------------------------------------------|------|

| Table 1-1.  | Acronyms and Abbreviations                                                          | . 22 |

| Table 1-2.  | Notational Conventions                                                              | . 22 |

| Table 2-1.  | Interface Selection                                                                 | . 26 |

| Table 2-2.  | Clockout Selection                                                                  | . 27 |

| Table 2-3.  | Bus Driver Type Selection                                                           | . 27 |

| Table 2-4.  | Voltage Regulator VDDR Connection                                                   | . 28 |

| Table 2-5.  | Device Memory Map                                                                   | . 30 |

| Table 2-6.  | Assigned Part ID Numbers                                                            | . 31 |

| Table 2-7.  | Pin Functions and Signal Properties                                                 | . 33 |

| Table 2-8.  | MFR4200 Power and Ground Connection Summary                                         | . 43 |

| Table 2-9.  | Recommended Pullup/down Resistor Values for IF_SEL[0:1] and CLK_S[0:1] Inputs .     | . 46 |

| Table 3-1.  | Register Map Summary                                                                | . 55 |

| Table 3-2.  | Bus Driver Type Selection                                                           | . 64 |

| Table 3-3.  | Encoding of Debug Port Control Fields CNTRL[7:4] and CNTRL[3:0]                     | . 88 |

| Table 3-4.  | CC State Coding                                                                     | . 93 |

| Table 3-5.  | Mapping between Receive Message Buffer Payload Bytes and GNMVnR Registers           | . 96 |

| Table 3-6.  | Channel Configuration for SSCCnR                                                    | 106  |

| Table 3-7.  | Error Handling Level Coding                                                         | 114  |

| Table 3-8.  | Mapping between SSSnR and SSnR                                                      | 120  |

| Table 3-9.  | FIFO Size                                                                           | 125  |

| Table 3-10. | FIFO Channel Filtering Configuration                                                | 137  |

| Table 3-11. | Receive Message Buffer Layout                                                       | 141  |

| Table 3-12. | Receive FIFO Message Buffer Layout                                                  | 142  |

| Table 3-13. | Transmit Message Buffer Layout                                                      | 142  |

| Table 3-14. | Mapping between Buffer Layout and Active Receive/Transmit/FIFO Message Buffers.     | 143  |

| Table 3-15. | Channel Filtering Configuration                                                     | 156  |

| Table 3-16. | CC Buffer Fields Accessibility                                                      | 167  |

| Table 3-17. | Double Transmit Message Buffer Data Collection with State Driven Transmit Operation | 183  |

| Table 3-18. | Double Transmit Message Buffer Data Collection with Event Driven Transmit Operation | 186  |

| Table 3-19. | FlexRay CC MCU Interface Configuration                                              | 189  |

| Table 3-20. | AMI Interface Signals and Pins Description                                          | 192  |

| Table Nun   | nber Title                                                          | Page |

|-------------|---------------------------------------------------------------------|------|

| Table 3-21. | HCS12 Interface Signal and Pin Descriptions                         | 196  |

| Table 3-22. | CLKOUT Frequency Selection                                          | 197  |

| Table 3-23. | Debug Port Functions Description                                    | 203  |

| Table 4-1.  | VREG3V3V2 — Signal Properties                                       | 209  |

| Table 4-2.  | VREG3V3V2 — Reset Sources                                           | 211  |

| Table 5-1.  | MFR4200 Pins Relevant to the CRG                                    | 214  |

| Table A-1.  | Absolute Maximum Ratings                                            | 221  |

| Table A-2.  | ESD and Latch-up Test Conditions                                    | 222  |

| Table A-3.  | ESD and Latch-up Protection Characteristics                         | 222  |

| Table A-4.  | Operating Conditions                                                | 223  |

| Table A-5.  | Thermal Package Simulation Details                                  | 225  |

| Table A-6.  | 5V I/O Characteristics (VDD5 = 5V)                                  | 226  |

| Table A-7.  | 3.3V I/O Characteristics (VDD5 = 3.3V)                              | 227  |

| Table A-8.  | Supply Current Characteristics                                      | 228  |

| Table A-9.  | Voltage Regulator - Operating Conditions                            | 229  |

| Table A-10. | Voltage Regulator Recommended Capacitive Loads                      | 230  |

| Table A-11. | Startup Characteristics                                             | 231  |

| Table A-12. | Oscillator Characteristics                                          | 232  |

| Table A-13. | AMI Interface AC Switching Characteristics over the Operating Range | 235  |

| Table A-14. | HCS12 Interface Timing Parameters                                   | 237  |

| Table C-1.  | Suggested External Component Values                                 | 243  |

# Chapter 1 Introduction

This data sheet provides information on a system that includes the MFR4200 FlexRay Communication Controller Module.

#### 1.1 Audience

This data sheet is intended for application and system hardware developers who wish to develop products for the FlexRay MFR4200. It is assumed that the reader understands FlexRay protocol functionality and microcontroller system design.

## 1.2 Additional Reading

For additional reading that provides background to, or supplements, the information in this manual:

- Appendix C, "MFR4200 Protocol Implementation Document"

- For more information about the FlexRay protocol, refer to the following document:

- FlexRay Communications System Protocol Specification V1.1, FlexRay Consortium, 2004.

- For more information about Philips Bus Guardian and Bus Driver devices, refer to the following documents:

- FlexRay Electrical Physical Layer Specification, v1.5, FlexRay Consortium, 2004,

- FlexRay Bus Guardian Preliminary Functional Specification, v1.9, FlexRay Consortium, June 2004.

- For more information about RS485 transceivers:

- About the MAX3078 transceiver (IDLE state coded as "1") http://pdfserv.maxim-ic.com/en/ds/MAX3070E-MAX3079E.pdf

- About the MAX3485 transceiver (IDLE state coded as "0") http://pdfserv.maxim-ic.com/en/ds/MAX3483-MAX3491.pdf

- For more information about the Power PC interface, refer to the Freescale products section at www.freescale.com.

- For more information about M9HCS12 Family devices and M9HCS12 programming, refer to the Freescale Products section at www.freescale.com.

# 1.3 Terminology

Table 1-1. Acronyms and Abbreviations

| Term               | Meaning                                                                 |  |  |  |

|--------------------|-------------------------------------------------------------------------|--|--|--|

| AMI                | Asynchronous memory interface                                           |  |  |  |

| BG                 | Bus guardian                                                            |  |  |  |

| cc                 | Communication controller (an alternative term for the MFR4200)          |  |  |  |

| ceil               | Function ceil(x) returns the nearest integer greater than or equal to x |  |  |  |

| Cycle length in µT | The actual length of a cycle in μT for the ideal controller (± 0 ppm)   |  |  |  |

| EBI                | External bus interface                                                  |  |  |  |

| FSS                | Frame start sequence                                                    |  |  |  |

| Host               | The FlexRay CC host MCU                                                 |  |  |  |

| LSB                | Less/least significant bit                                              |  |  |  |

| MCU                | Microcontroller                                                         |  |  |  |

| MSB                | More/most significant bit                                               |  |  |  |

| MT                 | Macrotick                                                               |  |  |  |

| μТ                 | Microtick                                                               |  |  |  |

| NIT                | Network idle time                                                       |  |  |  |

| PHY                | Physical interface                                                      |  |  |  |

| PS                 | FlexRay Communications System Protocol Specification                    |  |  |  |

| PWD                | Protocol working document                                               |  |  |  |

| RX                 | Reception                                                               |  |  |  |

| TCU                | Time control unit                                                       |  |  |  |

| TX                 | Transmission                                                            |  |  |  |

| TDMA               | Time division multiplex access                                          |  |  |  |

**Table 1-2. Notational Conventions**

| active-high | Names of signals that are active-high are shown in upper case text, without a '#' symbol at the end. Active-high signals are asserted (active) when they are high and negated when they are low.                   |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| active-low  | -low A '#' symbol at the end of a signal name indicates that the signal is active-low.  An active-low signal is asserted (active) when it is at the logic low level and is negated when it is at logic high level. |  |  |

| asserted    | A signal that is asserted is in its active logic state. An active-low signal changes from high to low when asserted; an active-high signal changes from low to high when asserted.                                 |  |  |

| negated     | A signal that is negated is in its inactive logic state. An active-low signal changes from low tohigh whe negated; an active-high signal changes fromhigh to low when negated.                                     |  |  |

| set         | To set a bit means to establish logic level one on the bit.                                                                                                                                                        |  |  |

| clear       | To clear a bit means to establish logic level zero on the bit.                                                                                                                                                     |  |  |

MFR4200 Data Sheet, Rev. 0

**Table 1-2. Notational Conventions (continued)**

| 0x0F   | The prefix "0x" denotes a hexadecimal number.                                                                                                                              |  |  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0b0011 | The prefix "0x" denotes a binary number.                                                                                                                                   |  |  |

| х      | In certain contexts, such as a signal encoding, this indicates "don't care". For example, if a field is binary encoded 0bx001, the state of the first bit is "don't care". |  |  |

| ==     | Used in equations, this symbol signifies comparison.                                                                                                                       |  |  |

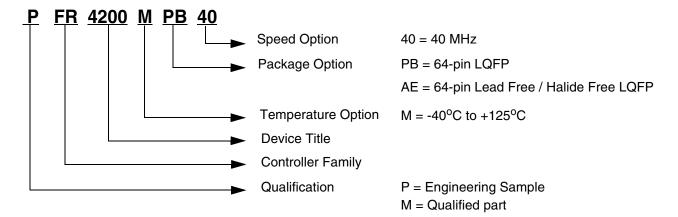

# 1.4 Part Number Coding

Figure 1-1. Order Part Number Coding

Introduction

MFR4200 Data Sheet, Rev. 0

# Chapter 2 Device Overview

#### 2.1 Introduction

The FlexRay Communication Controller MFR4200 implements the FlexRay protocol in accordance with Appendix C, "MFR4200 Protocol Implementation Document". This appendix refers to FlexRay Communications System Protocol Specification V1.1 for most protocol mechanisms, and complements the protocol specification where necessary.

The controller host interface (CHI) of the FlexRay Communication Controller MFR4200 is implemented in accordance with Chapter 3, "MFR4200 FlexRay Communication Controller".

#### 2.1.1 Features

The following list of features is not comprehensive, but is a selection of the most important features. Detailed descriptions of the protocol and the CHI features are provided in the following.

- Chapter 3, "MFR4200 FlexRay Communication Controller"

- Appendix C, "MFR4200 Protocol Implementation Document"

The most important features are:

- Bit rate up to a maximum of 10 Mbit/sec on each of two channels.

- 59 message buffers, each with a payload of up to 32 bytes of data.

- FlexRay frames with up to 254 payload data bytes. Padding is used for FlexRay payload data that exceeds the 32-byte data size boundary.

- One configurable receive FIFO.

- Each message buffer configurable as a receive message buffer, or as a transmit message buffer (single or double), or as part of the receive FIFO.

- Two receive shadow message buffers available to each channel.

- Message buffer configurable with state or event semantics.

- Flexible error signaling mechanism providing eight configurable counters, slot status indicators and interrupts.

- Internal measured time difference values used for clock synchronization can be read via the CHI.

- The status of up to four slots can be observed independently of the communication controller receive buffers.

- The host accesses all message buffers by means of three active message buffers (active transmit message buffer, active message receive buffer, and active receive FIFO buffer) in the CHI.

- Configurable message filtering based on frame ID, cycle counter, and channel, for transmit and receive message buffers.

- Configurable message filtering based on frame ID, channel, and message ID, for the receive FIFO.

- Duration of the communication cycle configurable in microticks.

### 2.1.2 Implementation Details and Constraints

- The MFR4200 provides two hardware selectable host interfaces:

- HCS12 interface, for direct connection to Freescale's HCS12 family of microcontrollers.

The HCS12 interface clock signal used to synchronize data transfer can run at a maximum rate of 8 MHz.

- Asynchronous memory interface (AMI), for asynchronous connection to microcontrollers.

- Internal 40 MHz quartz oscillator.

- Internal voltage regulator for the digital logic and the oscillator.

- Hardware selectable clock output to drive external host devices: Disabled/4/10/40 MHz.

- Maskable interrupt sources available over one interrupt output line.

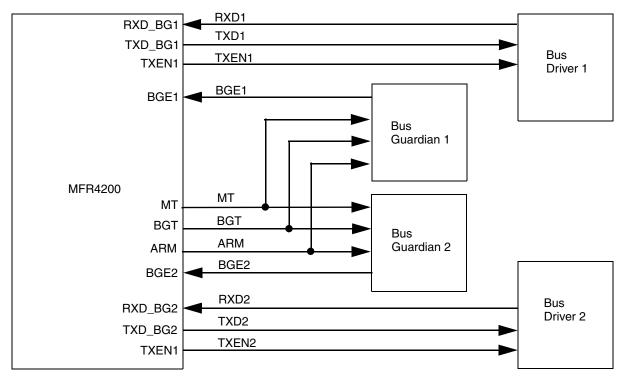

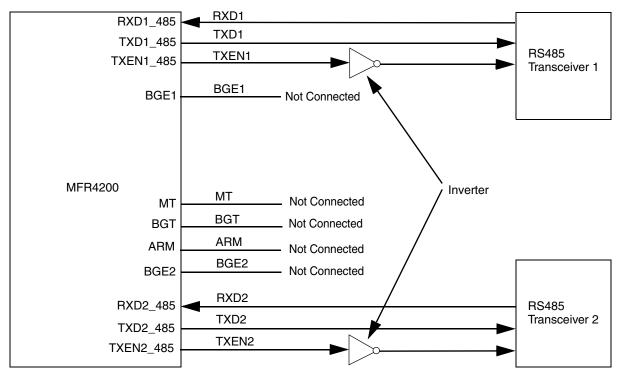

- Glueless electrical physical layer interface compatible with dedicated FlexRay physical layer. Industry standard RS485 physical layer device can be used with additional glue logic.

- Two pins have multiplexed strobe functions.

#### NOTE

Refer to Chapter 3, "MFR4200 FlexRay Communication Controller" for more implementation details and constraints.

### 2.1.3 Modes of Operation

#### NOTE

This section depicts only the MFR4200 device modes, not the FlexRay protocol operating modes of the MFR4200 FlexRay module. Refer to Chapter 3, "MFR4200 FlexRay Communication Controller for more information on the FlexRay module operating modes.

Only one user mode is available on the MFR4200 — normal operating mode.

In normal operating mode, the selections described below are possible.

#### 2.1.3.1 Interface Selection

The external interface is selected by means of the IF\_SEL[0:1] pins, as shown in Table 2-1.

Pin Interface IF\_SEL0 IF\_SEL1 0 0 Reserved 0 1 HCS12 synchronous interface 1 0 Asynchronous Memory Interface 1 1 Reserved

**Table 2-1. Interface Selection**

MFR4200 Data Sheet, Rev. 0

#### NOTE

As the IF\_SEL[0:1] signals share pins with physical layer interface signals, the interface type must be selected using either pullup or pulldown resistors.

IF\_SEL[0:1] signals are inputs during the internal reset sequence and are latched by the internal reset signal level. Refer to Chapter 5, "Clocks and Reset Generator" for more information.

#### 2.1.3.2 Clockout Selection

The CLK\_S[0:1] pins select the CLKOUT pin output clock frequency or disable the output clock.

| Р      | in     | CLKOUT Function                 |  |  |  |

|--------|--------|---------------------------------|--|--|--|

| CLK_S0 | CLK_S1 | OLNOO! I diletion               |  |  |  |

| 0      | 0      | 4 MHz output                    |  |  |  |

| 1      | 0      | 10 MHz output                   |  |  |  |

| 0      | 1      | 40 MHz output                   |  |  |  |

| 1      | 1      | Disabled (CLKOUT output is "0") |  |  |  |

**Table 2-2. Clockout Selection**

#### NOTE

As CLK\_S[0:1] signals share pins with physical layer interface signals, the CLKOUT function must be selected using either pullup or pulldown resistors.

CLK\_S[0:1] signals are inputs during the internal reset sequence and are latched by the internal reset signal level. Refer to Chapter 5, "Clocks and Reset Generator for more information.

### 2.1.3.3 Bus Driver Type Selection

The SCM[0:1] bits of the MCR0 register (see Chapter 3, "MFR4200 FlexRay Communication Controller) select the bus driver type.

| Driver Type                                  | SCM1 | SCM0 |

|----------------------------------------------|------|------|

| RS485 (IDLE state coded as '0') <sup>1</sup> | 0    | 0    |

| Optical/Electrical PHY                       | 0    | 1    |

| Reserved                                     | 1    | 0    |

| RS485 (IDLE state coded as '1') <sup>1</sup> | 1    | 1    |

**Table 2-3. Bus Driver Type Selection**

<sup>&</sup>lt;sup>1</sup> Refer to Section 1.2, "Additional Reading" for more information on RS485.

#### **NOTE**

It is not possible to mix in a cluster or per channel:

- Different RS485;

- RS485 and Optical/Electrical PHY.

#### 2.1.3.4 Internal VREG Enable/Disable Selection

**Table 2-4. Voltage Regulator VDDR Connection**

| VDDR                                        | Description                         |

|---------------------------------------------|-------------------------------------|

| Supplied with V <sub>DD5</sub> <sup>1</sup> | Internal Voltage Regulator enabled  |

| Tied to ground                              | Internal Voltage Regulator disabled |

<sup>&</sup>lt;sup>1</sup> Refer to Section A.1.7, "Operating Conditions" for the V<sub>DD5</sub>

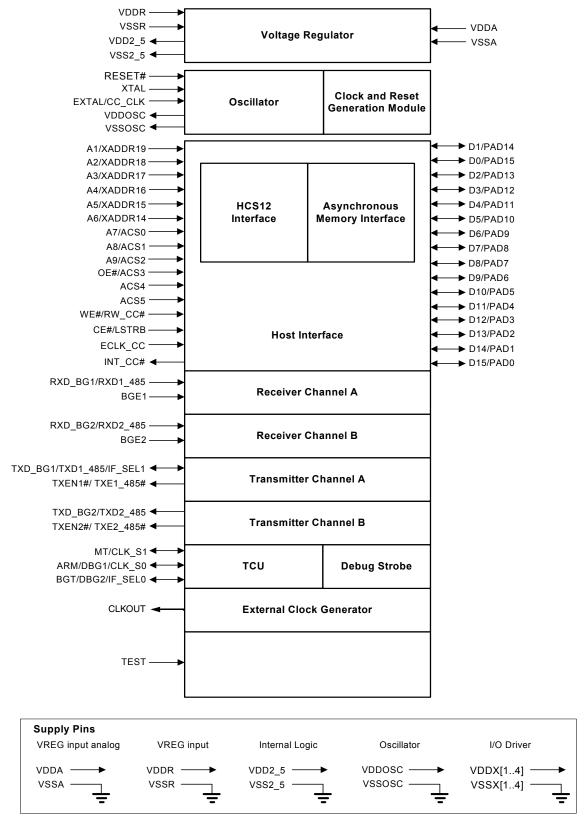

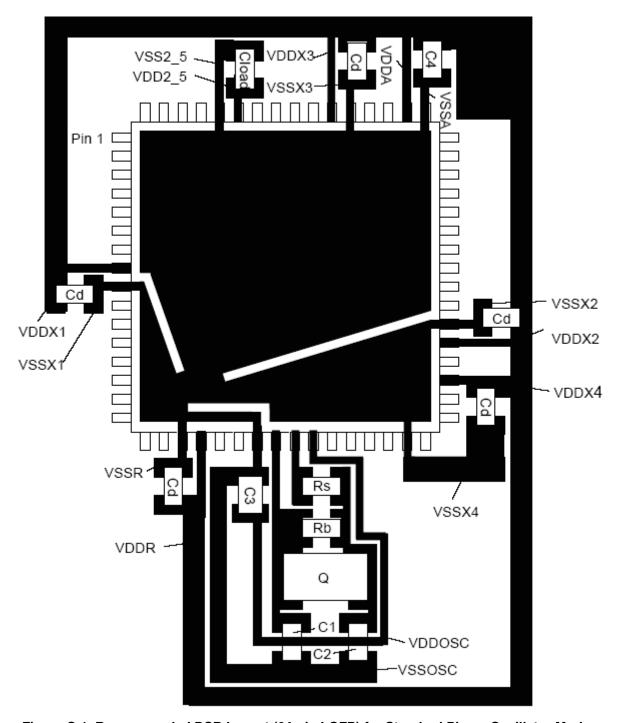

# 2.1.4 Block Diagram

Figure 2-1 shows a block diagram of the MFR4200 device.

Figure 2-1. MFR4200 Block Diagram

**Device Overview**

# 2.1.5 Memory Map

Table 2-5 shows the device memory map of the MFR4200 after a hard reset.

**Table 2-5. Device Memory Map**

| Address (Hex) | Module                                                                                 | Size (bytes) |

|---------------|----------------------------------------------------------------------------------------|--------------|

| 0x000-0x018   | General Control Registers                                                              | 26           |

| 0x01A-0x01E   | Acceptance Filter Registers                                                            | 6            |

| 0x024-0x04A   | General Control Registers                                                              | 40           |

| 0x04C-0x082   | Slot Status Registers                                                                  | 56           |

| 0x084-0x0FE   | General Control Registers                                                              | 124          |

| 0x100-0x126   | Active Receive FIFO Buffer                                                             | 40           |

| 0x128-0x13E   | Reserved, read-only location                                                           | 24           |

| 0x140-0x166   | Active Receive Message Buffer                                                          | 40           |

| 0x168-0x17E   | Reserved, read-only location                                                           | 24           |

| 0x180-0x1A6   | Active Transmit Message Buffer                                                         | 40           |

| 0x1A8-0x1FE   | Reserved, read-only location                                                           | 88           |

| 0x200-0x2FE   | Buffer Control, Configuration and Status Registers,<br>Cycle Counter Filters Registers | 256          |

| 0x300-0x31E   | Reserved, read-only location                                                           | 32           |

| 0x320-0x3FE   | General Status Registers                                                               | 224          |

The FlexRay block defines the MFR4200 address memory map. Refer to Chapter 3, "MFR4200 FlexRay Communication Controller for the detailed register map.

### 2.1.6 Part ID Assignments

The part ID is located in two 16-bit registers, MVR0 and MVR1, at addresses 0x002 and 0x098 (see Chapter 3, "MFR4200 FlexRay Communication Controller). This read-only value is a unique part ID for each revision of the chip. Table 2-6 shows the assigned part ID number.

**Table 2-6. Assigned Part ID Numbers**

| Device  | Mask Set Number   | Part ID <sup>1</sup> |        |  |

|---------|-------------------|----------------------|--------|--|

| Device  | Wask Set Nulliber | MVR0                 | MVR1   |  |

| MFR4200 | 0L60X             | 0x9042               | 0x0000 |  |

| MFR4200 | 1L60X             | 0x9042               | 0x0001 |  |

The coding is as follows (see also the MVR0 and MVR1 register descriptions in Chapter 3, "MFR4200 FlexRay Communication Controller):

#### MVR0:

Bit 15-12: Major release of the FlexRay block in the MFR4200 device

Bit 11-08: Minor release of the FlexRay block in the MFR4200 device

Bit 07-00: Device Part ID1

#### MVR1:

Bit 15-08: Device Part ID2.

Bit 07-04: Major release of the MFR4200 device.

Bit 03-00: Minor release of the MFR4200 device.

## 2.2 Signal Descriptions

This section describes the signals that connect off-chip. It includes a pinout diagram, a table of signal properties, and a detailed discussion of each signal.

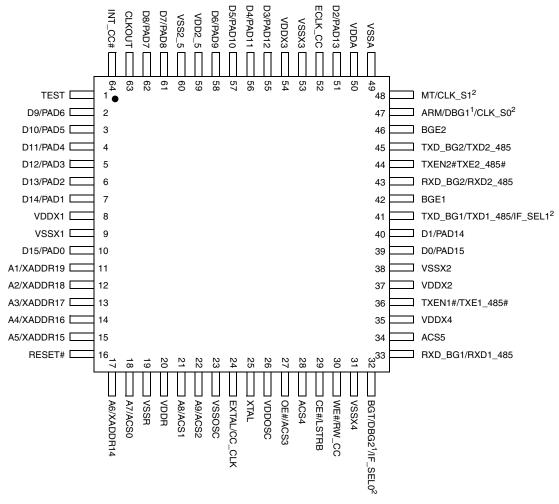

## 2.2.1 System Pinout

The MFR4200 is available in a 64-pin low profile quad flat package (LQFP). Most pins perform two or more functions, as described in Section 2.2.2, "Pin Functions and Signal Properties". Figure 2-2 shows the pin assignments.

#### Notes:

- One of the following internal signals can be output through the DBG1 or DBG2 pin: PCS, SSS, RAGFB, MSS, DSSB, SFB, RCFB, SCC, RAGFA, MTS, SOC, DSSA, SFA, RCFA. (See Table 3-3 and Table 3-23.)

- <sup>2</sup> CLK\_S[1:0] and IF\_SEL[1:0] are inputs during the internal reset sequence, and are latched by the internal reset signal level.

Figure 2-2. Pin Assignments for MFR4200 in 64-pin LQFP

## 2.2.2 Pin Functions and Signal Properties

Table 2-7 provides a summary of all pin functions and signal properties shown in Figure 2-2.

**Table 2-7. Pin Functions and Signal Properties**

| Pin<br>N | Pin <sup>1</sup><br>Function1 | Pin <sup>1</sup><br>Function2 | Pin <sup>1</sup><br>Function3 | Powered by | In/<br>Out | Pin<br>type <sup>2,3</sup> | Re<br>set | Functional Description                                                                            |

|----------|-------------------------------|-------------------------------|-------------------------------|------------|------------|----------------------------|-----------|---------------------------------------------------------------------------------------------------|

|          | Host Interface Pins           |                               |                               |            |            |                            |           |                                                                                                   |

| 11       | A1                            | XADDR19                       | -                             | VDDX       | I          | PC                         | -         | AMI address bus / HCS12 expanded address lines. A1= LSB of the AMI address bus.                   |

| 12       | A2                            | XADDR18                       | -                             | VDDX       | I          | PC                         | -         | AMI address bus / HCS12 expanded address lines.                                                   |

| 13       | А3                            | XADDR17                       | -                             | VDDX       | I          | PC                         | -         | AMI address bus / HCS12 expanded address lines.                                                   |

| 14       | A4                            | XADDR16                       | -                             | VDDX       | I          | PC                         | -         | AMI address bus / HCS12 expanded address lines.                                                   |

| 15       | <b>A</b> 5                    | XADDR15                       | -                             | VDDX       | I          | PC                         | -         | AMI address bus / HCS12 expanded address lines.                                                   |

| 17       | A6                            | XADDR14                       | -                             | VDDX       | I          | PC                         | -         | AMI address bus / HCS12 expanded address lines. XADDR14 = LSB of the HCS12 expanded address lines |

| 18       | A7                            | ACS0                          | -                             | VDDX       | I          | PC                         | -         | AMI address bus / HCS12 address select inputs.                                                    |

| 21       | A8                            | ACS1                          | -                             | VDDX       | I          | PC                         | 1         | AMI address bus / HCS12 address select inputs.                                                    |

| 22       | A9                            | ACS2                          | -                             | VDDX       | I          | PC                         | -         | AMI address bus / HCS12 address select inputs.                                                    |

| 27       | OE# <sup>4</sup>              | ACS3                          | -                             | VDDX       | I          | PC                         | -         | AMI read output enable signal / HCS12 address select input.                                       |

| 28       | ACS4                          | -                             | -                             | VDDX       | ı          | PC                         | -         | HCS12 address select inputs.                                                                      |

| 34       | ACS5                          | -                             | -                             | VDDX       | I          | PC                         | -         | HCS12 address select inputs. MSB of the address select inputs.                                    |

| 10       | D15                           | PAD0                          | -                             | VDDX       | I/O        | Z/DC/PC                    | Z         | AMI data bus / HCS12 multiplexed address/data bus. PAD0 is the LSB of the HCS12 address/data bus. |

| 7        | D14                           | PAD1                          | -                             | VDDX       | I/O        | Z/DC/PC                    | Z         | AMI data bus / HCS12 multiplexed address/data bus.                                                |

| 6        | D13                           | PAD2                          | -                             | VDDX       | I/O        | Z/DC/PC                    | Z         | AMI data bus / HCS12 multiplexed address/data bus.                                                |

| 5        | D12                           | PAD3                          | -                             | VDDX       | I/O        | Z/DC/PC                    | Z         | AMI data bus / HCS12 multiplexed address/data bus.                                                |

| 4        | D11                           | PAD4                          | -                             | VDDX       | I/O        | Z/DC/PC                    | Z         | AMI data bus / HCS12 multiplexed address/data bus.                                                |

| 3        | D10                           | PAD5                          | -                             | VDDX       | I/O        | Z/DC/PC                    | Z         | AMI data bus / HCS12 multiplexed address/data bus.                                                |

| 2        | D9                            | PAD6                          | -                             | VDDX       | I/O        | Z/DC/PC                    | Z         | AMI data bus / HCS12 multiplexed address/data bus.                                                |

#### **Device Overview**

Table 2-7. Pin Functions and Signal Properties (continued)

| Pin<br>N | Pin <sup>1</sup><br>Function1 | Pin <sup>1</sup><br>Function2 | Pin <sup>1</sup><br>Function3 | Powered by | In/<br>Out | Pin<br>type <sup>2,3</sup> | Re<br>set | Functional Description                                                                       |  |

|----------|-------------------------------|-------------------------------|-------------------------------|------------|------------|----------------------------|-----------|----------------------------------------------------------------------------------------------|--|

| 62       | D8                            | PAD7                          | -                             | VDDX       | I/O        | Z/DC/PC                    | Z         | AMI data bus / HCS12 multiplexed address/data bus.                                           |  |

| 61       | D7                            | PAD8                          | •                             | VDDX       | I/O        | Z/DC/PC                    | Z         | AMI data bus / HCS12 multiplexed address/data bus.                                           |  |

| 58       | D6                            | PAD9                          |                               | VDDX       | I/O        | Z/DC/PC                    | Z         | AMI data bus / HCS12 multiplexed address/data bus.                                           |  |

| 57       | D5                            | PAD10                         | -                             | VDDX       | I/O        | Z/DC/PC                    | Z         | AMI data bus / HCS12 multiplexed address/data bus.                                           |  |

| 56       | D4                            | PAD11                         | -                             | VDDX       | I/O        | Z/DC/PC                    | Z         | AMI data bus / HCS12 multiplexed address/data bus.                                           |  |

| 55       | D3                            | PAD12                         | -                             | VDDX       | I/O        | Z/DC/PC                    | Z         | AMI data bus / HCS12 multiplexed address/data bus.                                           |  |

| 51       | D2                            | PAD13                         | -                             | VDDX       | I/O        | Z/DC/PC                    | Z         | AMI data bus / HCS12 multiplexed address/data bus.                                           |  |

| 40       | D1                            | PAD14                         | -                             | VDDX       | I/O        | Z/DC/PC                    | Z         | AMI data bus / HCS12 multiplexed address/data bus.                                           |  |

| 39       | D0                            | PAD15                         | -                             | VDDX       | I/O        | Z/DC/PC                    | Z         | AMI data bus / HCS12 multiplexed address/data bus. D0 is the LSB of the AMI data bus         |  |

| 29       | CE#                           | LSTRB                         | -                             | VDDX       | I          | PC                         | -         | AMI chip select signal / HCS12 low-byte strobe signal                                        |  |

| 30       | WE#                           | RW_CC#                        | -                             | VDDX       | I          | PC                         | -         | AMI write enable signal/ HCS12 read/write select signal                                      |  |

| 52       | ECLK_CC                       | -                             | -                             | VDDX       | I          | PC                         | -         | HCS12 clock input                                                                            |  |

|          | Physical Layer Interface      |                               |                               |            |            |                            |           |                                                                                              |  |

| 32       | BGT                           | DBG2                          | IF_SEL0                       | VDDX       | I/O        | DC/PD                      | 1         | Bus Guardian Tick / Debug strobe point signal 2/Host interface selection 0                   |  |

| 48       | MT                            | CLK_S1                        |                               | VDDX       | I/O        | DC/PD                      | -         | Bus Guardian Macrotick/Controller clock output select signal 1                               |  |

| 47       | ARM                           | DBG1                          | CLK_S0                        | VDDX       | I/O        | DC/PD                      | -         | Bus Guardian ARM signal / Debug strobe point signal1/Controller clock output select signal 0 |  |

| 33       | RXD_BG1                       | RXD2_485                      | -                             | VDDX       | I          | PC                         | -         | PHY Data receiver input / RS485 Data receiver input                                          |  |

| 43       | RXD_BG2                       | RXD2_485                      | -                             | VDDX       | I          | PC                         | -         | PHY Data receiver input / RS485 Data receiver input                                          |  |

| 36       | TXEN1#                        | TXE1_485#                     | -                             | VDDX       | 0          | DC                         | 1         | Transmit enable for PHY / Transmit enable for RS485                                          |  |

| 44       | TXEN2#                        | TXE2_485#                     | -                             | VDDX       | 0          | DC                         | 1         | Transmit enable for PHY / Transmit enable for RS485                                          |  |

MFR4200 Data Sheet, Rev. 0

Table 2-7. Pin Functions and Signal Properties (continued)

| Pin<br>N      | Pin <sup>1</sup><br>Function1 | Pin <sup>1</sup><br>Function2 | Pin <sup>1</sup><br>Function3 | Powered by | In/<br>Out | Pin<br>type <sup>2,3</sup> | Re<br>set | Functional Description                                                                   |  |  |

|---------------|-------------------------------|-------------------------------|-------------------------------|------------|------------|----------------------------|-----------|------------------------------------------------------------------------------------------|--|--|

| 41            | TXD_BG1                       | TXD1_485                      | IF_SEL1                       | VDDX       | I/O        | DC/PD                      | -         | PHY Data transmitter output / RS485 Data transmitter output / Host interface selection 1 |  |  |

| 45            | TXD_BG2                       | TXD2_485                      | -                             | VDDX       | 0          | DC                         | 0         | PHY Data transmitter output / RS485 Data transmitter output                              |  |  |