# MC33696

# PLL Tuned UHF Transceiver for Data Transfer Applications

## 1 Overview

The MC33696 is a highly integrated transceiver designed for low-voltage applications. It includes a programmable PLL for multi-channel applications, an RSSI circuit, a strobe oscillator that periodically wakes up the receiver while a data manager checks the content of incoming messages. A configuration switching feature allows automatic changing of the configuration between two programmable settings without the need of an MCU.

## 2 Features

### General:

- 304 MHz, 315 MHz, 426 MHz, 434 MHz, 868 MHz, and 915 MHz ISM bands

- Choice of temperature ranges:

- $-40^{\circ}$ C to  $+85^{\circ}$ C

- $--20^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}$

- OOK and FSK transmission and reception

- 20 kbps maximum data rate using Manchester coding

- 2.1 V to 3.6 V or 5 V supply voltage

- Programmable via SPI

- 6 kHz PLL frequency step

#### **Features**

- Current consumption:

- 13.5 mA in TX mode

- 10.3 mA in RX mode

- Less then 1 mA in RX mode with strobe ratio = 1/10

- 260 nA standby and 24 μA off currents

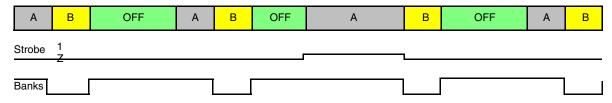

- Configuration switching allows fast switching of two register banks

### Receiver:

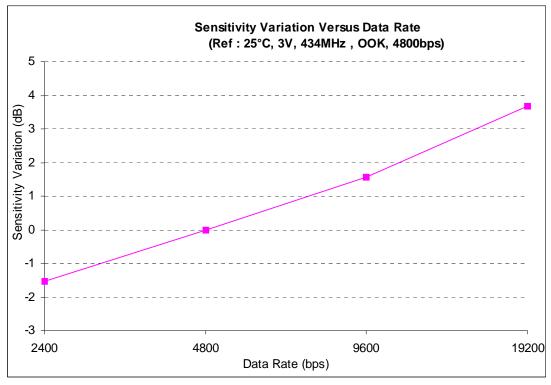

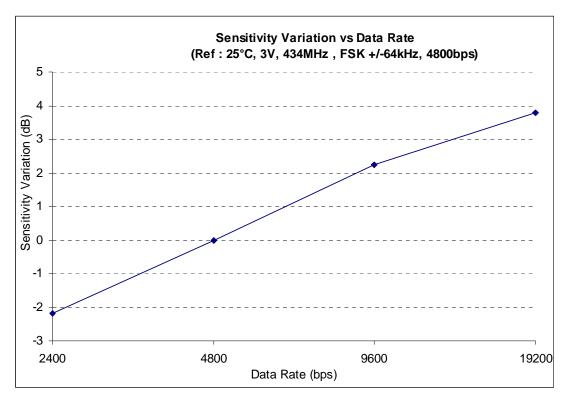

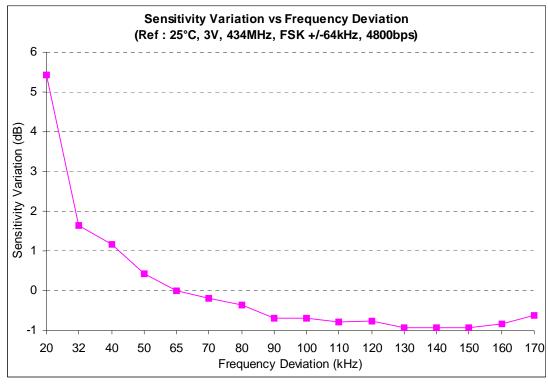

- -106.5 dBm sensitivity, up to -108 dBm in FSK 2.4 kbps

- Digital and analog RSSI (received signal strength indicator)

- Automatic wakeup function (strobe oscillator)

- Embedded data processor with programmable word recognition

- Image cancelling mixer

- 380 kHz IF filter bandwidth

- Fast wakeup time

### Transmitter:

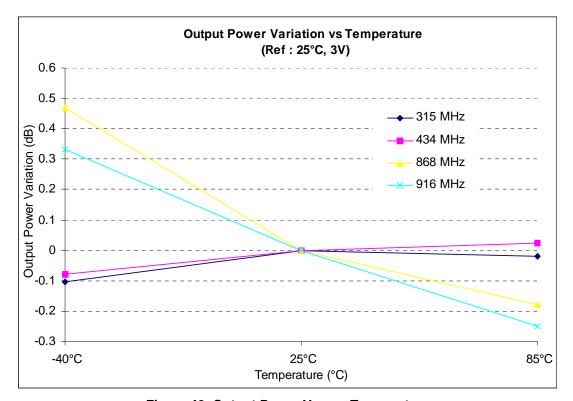

- Up to 7.25 dBm output power

- Programmable output power

- FSK done by PLL programming

### Ordering information

| Temperature Range | QFN Package    | LQFP Package   |

|-------------------|----------------|----------------|

| -40°C to +85°C    | MC33696FCE/R2  | MC33696FJE/R2  |

| -20°C to +85°C    | MC33696FCAE/R2 | MC33696FJAE/R2 |

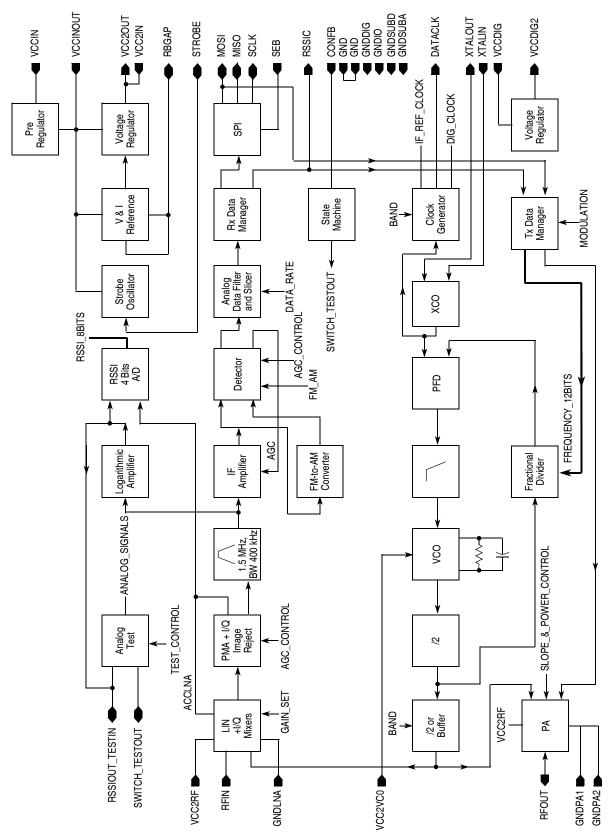

Figure 1. Block Diagram

MC33696 Data Sheet, Rev. 9

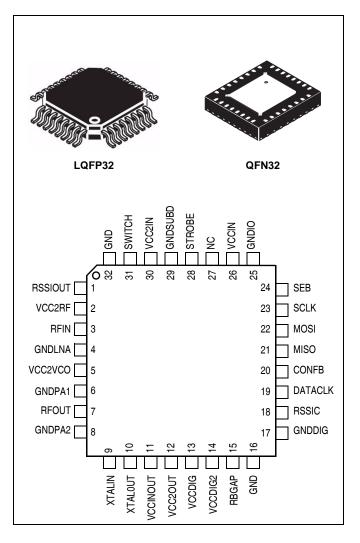

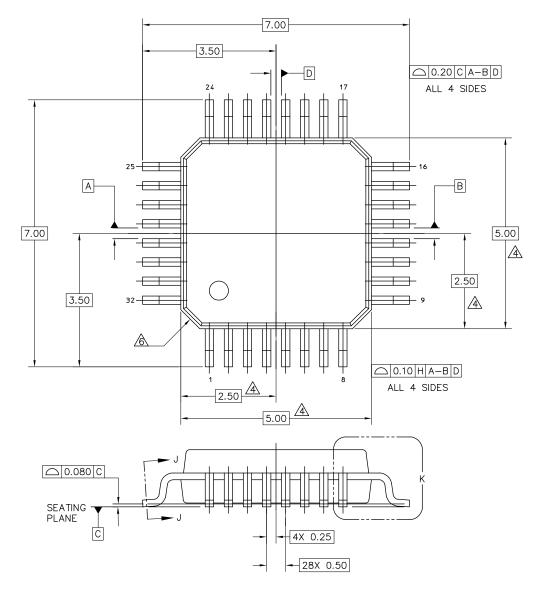

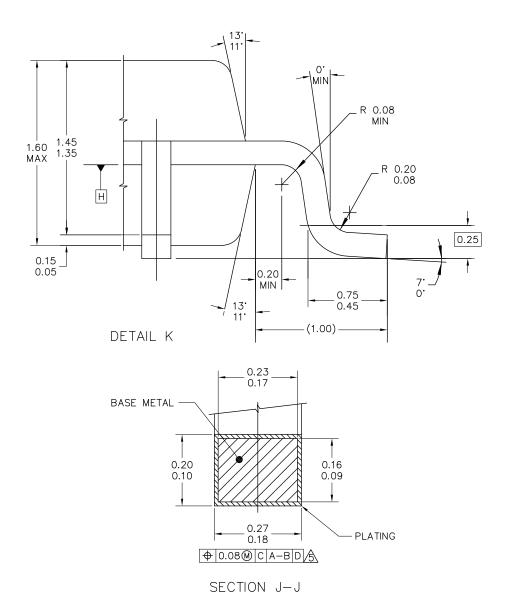

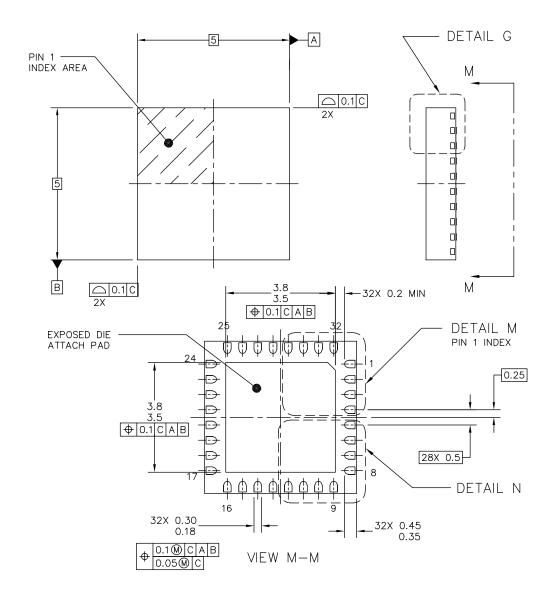

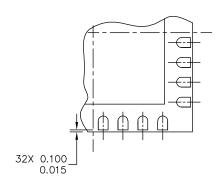

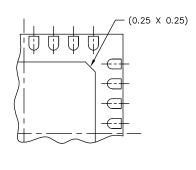

# 3 Pin Functions

**Table 1. Pin Functions**

| Pin | Name     | Description                                                             |  |  |

|-----|----------|-------------------------------------------------------------------------|--|--|

| 1   | RSSIOUT  | RSSI analog output                                                      |  |  |

| 2   | VCC2RF   | 2.1 V to 2.7 V internal supply for LNA                                  |  |  |

| 3   | RFIN     | RF input                                                                |  |  |

| 4   | GNDLNA   | Ground for LNA (low noise amplifier)                                    |  |  |

| 5   | VCC2VCO  | 2.1 V to 2.7 V internal supply for VCO                                  |  |  |

| 6   | GNDPA1   | PA ground                                                               |  |  |

| 7   | RFOUT    | RF output                                                               |  |  |

| 8   | GNDPA2   | PA ground                                                               |  |  |

| 9   | XTALIN   | Crystal oscillator input                                                |  |  |

| 10  | XTALOUT  | Crystal oscillator output                                               |  |  |

| 11  | VCCINOUT | 2.1 V to 3.6 V power supply/regulator output                            |  |  |

| 12  | VCC2OUT  | 2.1 V to 2.7 V voltage regulator output for analog and RF modules       |  |  |

| 13  | VCCDIG   | 2.1 V to 3.6 V power supply for voltage limiter                         |  |  |

| 14  | VCCDIG2  | 1.5 V voltage limiter output for digital module                         |  |  |

| 15  | RBGAP    | Reference voltage load resistance                                       |  |  |

| 16  | GND      | General ground                                                          |  |  |

| 17  | GNDDIG   | Digital module ground                                                   |  |  |

| 18  | RSSIC    | RSSI control input                                                      |  |  |

| 19  | DATACLK  | Data clock output to microcontroller                                    |  |  |

| 20  | CONFB    | Configuration mode selection input                                      |  |  |

| 21  | MISO     | Digital interface I/O                                                   |  |  |

| 22  | MOSI     | Digital interface I/O                                                   |  |  |

| 23  | SCLK     | Digital interface clock I/O                                             |  |  |

| 24  | SEB      | Digital interface enable input                                          |  |  |

| 25  | GNDIO    | Digital I/O ground                                                      |  |  |

| 26  | VCCIN    | 2.1 V to 3.6 V or 5.5 V input                                           |  |  |

| 27  | NC       | No connection                                                           |  |  |

| 28  | STROBE   | Strobe oscillator capacitor or external control input                   |  |  |

| 29  | GNDSUBD  | Ground                                                                  |  |  |

| 30  | VCC2IN   | 2.1 V to 2.7 V power supply for analog modules for decoupling capacitor |  |  |

| 31  | SWITCH   | RF switch control output                                                |  |  |

| 32  | GND      | General ground                                                          |  |  |

# 4 Silicon Version

This data sheet describes the functional features of silicon version ES4.1.

# 5 Maximum Ratings

**Table 2. Maximum Ratings**

| Parameter                                                                             | Symbol            | Value                                            | Unit |

|---------------------------------------------------------------------------------------|-------------------|--------------------------------------------------|------|

| Supply voltage on pin: VCCIN                                                          | V <sub>CCIN</sub> | V <sub>GND</sub> -0.3 to 5.5                     | V    |

| Supply voltage on pins: VCCINOUT, VCCDIG                                              | V <sub>CC</sub>   | V <sub>GND</sub> -0.3 to 3.6                     | V    |

| Supply voltage on pins: VCC2IN, VCC2RF, VCC2VCO                                       | V <sub>CC2</sub>  | V <sub>GND</sub> -0.3 to 2.7                     | V    |

| Voltage allowed on each pin (except RFOUT and digital pins)                           | _                 | V <sub>GND</sub> -0.3 to V <sub>CC2</sub>        | V    |

| Voltage allowed on pin: RFOUT                                                         | V <sub>CCPA</sub> | V <sub>GND</sub> -0.3 to V <sub>CCINOUT</sub> +2 | V    |

| Voltage allowed on digital pins: SEB, SCLK, MISO, MOSI, CONFB, DATACLK, RSSIC, STROBE | V <sub>CCIO</sub> | V <sub>GND</sub> -0.3 to V <sub>CCIN</sub> +0.3  | V    |

| ESD HBM voltage capability on each pin <sup>1</sup>                                   | _                 | ±2000                                            | V    |

| ESD MM voltage capability on each pin <sup>2</sup>                                    | _                 | ±200                                             | V    |

| Solder heat resistance test (10 s)                                                    | _                 | 260                                              | °C   |

| Storage temperature                                                                   | T <sub>S</sub>    | -65 to +150                                      | °C   |

| Junction temperature                                                                  | T <sub>J</sub>    | 150                                              | °C   |

### NOTES:

Human body model, AEC-Q100-002 rev. C.

<sup>&</sup>lt;sup>2</sup> Machine model, AEC-Q100-003 rev. C.

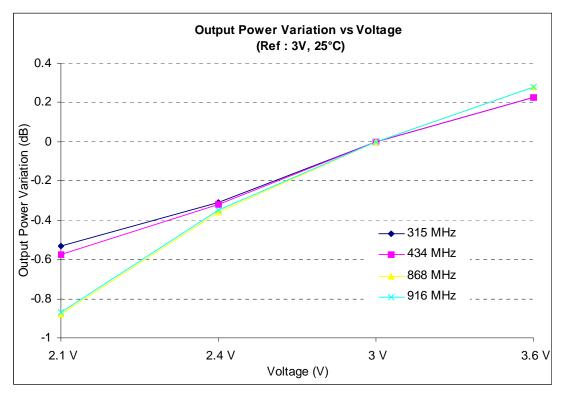

**Power Supply**

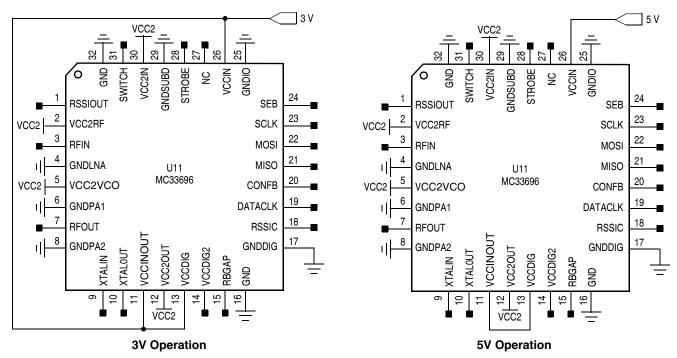

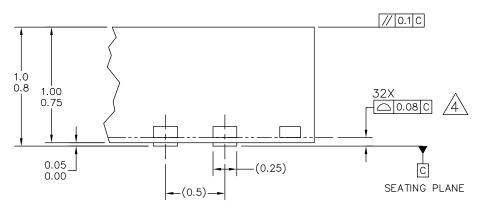

# 6 Power Supply

**Table 3. Supply Voltage Range Versus Ambient Temperature**

| Parameter                                                   | Symbol            | Temperatu      | Unit           |      |

|-------------------------------------------------------------|-------------------|----------------|----------------|------|

| Farameter                                                   | Syllibol          | -40°C to +85°C | -20°C to +85°C | Oill |

| Supply voltage on VCCIN, VCCINOUT, VCCDIG for 3 V operation | V <sub>CC3V</sub> | 2.7 to 3.6     | 2.1 to 3.6     | V    |

| Supply voltage on VCCIN for 5 V operation                   | V <sub>CC5V</sub> | 4.5 to 5.5     | 4.5 to 5.5     | V    |

| Supply voltage on VCCPA for 3 V or 5 V operation            | V <sub>CCPA</sub> | 3.0 to 3.6     | 3.0 to 3.6     | V    |

#### NOTES:

6

The circuit can be supplied from a 3 V voltage regulator or battery cell by connecting VCCIN and VCCINOUT. It is also possible to use a 5 V power supply connected to VCCIN; in this case VCCINOUT should not be connected to VCCIN.

The RFOUT pin cannot be biased with a voltage higher than 3.6 V. For 5 V operation, biasing voltage is available on VCCINOUT.

An on-chip low drop-out voltage regulator supplies the RF and analog modules (except the strobe oscillator and the low voltage detector, which are directly supplied from VCCINOUT). This voltage regulator is supplied from pin VCCINOUT and its output is connected to VCC2OUT. An external capacitor must be inserted between VCC2OUT and GND for stabilization and decoupling. The analog and RF modules must be supplied by VCC2 by externally wiring VCC2OUT to VCC2IN, VCC2RF and VCC2VCO.

MC33696 Data Sheet, Rev. 9

<sup>-40°</sup>C to +85°C: MC33696FCE/FJE. -20°C to +85°C: MC33696FCAE/FJAE.

Figure 2. Wiring Diagrams

A second voltage regulator supplies the digital part. This regulator is powered from pin VCCDIG and its output is connected to VCCDIG2. An external capacitor must be inserted between VCCDIG2 and GNDDIG, for decoupling. The supply voltage VCCDIG2 is equal to 1.6 V. In standby mode, this voltage regulator goes into an ultra-low-power mode, but VCCDIG2 =  $0.7 \times V_{CCDIG}$ . This enables the internal registers to be supplied, allowing configuration data to be saved.

# 7 Supply Voltage Monitoring and Reset

At power-on, an internal reset signal is generated. All registers are reset.

When the LVDE bit is set, the low-voltage detection module is enabled. This block compares the supply voltage on VCCINOUT with a reference level of about 1.8 V. If the voltage on VCCINOUT drops below 1.8 V, status bit LVDS is set. The information in status bit LVDS is latched and reset after a read access.

#### NOTE

If LVDE = 1, the LVD module remains enabled. The circuit cannot be put in standby mode, but remains in LVD mode with a higher quiescent current, due to the monitoring circuitry. LVD function is not accurate in standby mode.

# 8 Receiver Functional Description

The receiver is based on a superheterodyne architecture with an intermediate frequency (IF) of 1.5 MHz (see Figure 1). Its input is connected to the RFIN pin. Frequency down conversion is done by a high-side

#### **Transmitter Functional Description**

injection I/Q mixer driven by the frequency synthesizer. An integrated poly-phase filter performs rejection of the image frequency.

The low intermediate frequency allows integration of the IF filter providing the selectivity. The center frequency is tuned by automatic frequency control (AFC) referenced to the crystal oscillator frequency.

Sensitivity is met by an overall amplification of approximately 96 dB, distributed over the reception chain, comprising low-noise amplifier (LNA), mixer, post-mixer amplifier, and IF amplifier. Automatic gain control (AGC), on the LNA and the IF amplifier, maintains linearity and prevents internal saturation. Sensitivity can be reduced using four programmable steps on the LNA gain.

Amplitude demodulation is achieved by peak detection and comparison with a fixed or adaptive voltage reference selected during configuration. Frequency demodulation is achieved in two steps: the IF amplifier AGC is disabled and acts as an amplitude limiter; a filter performs a frequency-to-voltage conversion. The resulting signal is then amplitude demodulated in the same way as in the case of amplitude modulation with an adaptive voltage reference.

A low-pass filter improves the signal-to-noise ratio.

Shaped data are available if the integrated data manager is not used.

If used, the data manager performs clock recovery and decoding of Manchester coded data. Data and clock are then available on the serial peripheral interface (SPI). The configuration sets the data rate range managed by the data manager and the bandwidth of the low-pass filter.

An internal low-frequency oscillator can be used as a strobe oscillator to perform an automatic wakeup sequence.

It is also possible to define two different configurations for the receiver (frequency, data rate, data manager, modulation, etc.) that are automatically loaded during wakeup or under MCU control.

If the PLL goes out of lock, received data are ignored.

# 9 Transmitter Functional Description

The single-ended power amplifier is connected to the RFOUT pin.

In the case of amplitude modulation, coded data sent by the microcontroller unit (MCU) are used for on/off keying (OOK) the RF carrier. Rise and fall times of the RF signal are controlled to minimize spurious emission.

In the case of frequency modulation, coded data sent by the MCU are used for frequency shift keying (FSK) the RF carrier. RF output power can be reduced using four programmable steps.

Out-of-lock detection prevents any out-of-band emission, by stopping the transmission.

The logic output SWITCH enables control of an external RF switch for isolating the two RF pins. Its output toggles when the circuit changes from receive to transmit, and vice versa.

# 10 Frequency Planning

## 10.1 Clock Generator

All clocks running in the circuit are derived from the reference frequency provided by the crystal oscillator (frequency  $f_{ref}$ , period  $t_{ref}$ ). The crystal frequency is chosen in relation to the band in which the MC33696 has to operate. Table 4 shows the value of the CF bits.

| RF<br>Frequency<br>(MHz) | CF1 | CF0 | LOF1 | LOF0 | F <sub>REF</sub> (Crystal<br>Frequency)<br>(MHz) | F <sub>IF</sub> (IF<br>Frequency)<br>(MHz) | Datacik<br>Divider | F <sub>datacik</sub><br>(kHz) | Digclk<br>Divider | F <sub>digclk</sub><br>(kHz) | Τ <sub>digclk</sub><br>(μs) |

|--------------------------|-----|-----|------|------|--------------------------------------------------|--------------------------------------------|--------------------|-------------------------------|-------------------|------------------------------|-----------------------------|

| 304                      | 0   | 0   | 0    | 0    | 16.96745                                         | 1.414                                      | 60                 | 282.791                       | 30                | 565.582                      | 1.77                        |

| 315                      | 0   | 0   | 1    | 0    | 17.58140                                         | 1.465                                      | 60                 | 293.023                       | 30                | 586.047                      | 1.71                        |

| 426                      | 0   | 1   | 0    | 1    | 23.74913                                         | 1.484                                      | 80                 | 296.864                       | 40                | 593.728                      | 1.68                        |

| 433.92                   | 0   | 1   | 0    | 1    | 24.19066                                         | 1.512                                      | 80                 | 302.383                       | 40                | 604.767                      | 1.65                        |

| 868.3                    | 1   | 1   | 0    | 1    | 24.16139                                         | 1.510                                      | 80                 | 302.017                       | 40                | 604.035                      | 1.66                        |

| 916.5                    | 1   | 1   | 1    | 1    | 25.50261                                         | 1.594                                      | 80                 | 318.783                       | 40                | 637.565                      | 1.57                        |

Table 4. Crystal Frequency and CF Values Versus Frequency Band

# 10.2 Intermediate Frequency

The IF filter is controlled by the crystal oscillator to guarantee the frequency over temperature and voltage range. The IF filter center frequency, FIF, can be computed using the crystal frequency  $f_{ref}$  and the value of the CF bits:

- If CF[0] = 0:  $FIF = f_{ref}/9*1.5/2$

- If  $CF[0] = 1 : FIF = f_{ref}/12*1.5/2$

The cut-off frequency given in the parametric section can be computed by scaling to the FIF.

#### **Example 1. Cut-off Frequency Computation**

Compute the low cut-off frequency of the IF filter for a 16.9683 MHz crystal oscillator. For this reference frequency, FIF = 1.414 MHz.

So, the  $1.375^1$  MHz low cut-off frequency specified for a 1.5 MHz IF frequency becomes  $1.375^{1}*1.414/1.5 = 1.296$  MHz

## 10.3 Frequency Synthesizer Description

The frequency synthesizer consists of a local oscillator (LO) driven by a fractional N phase locked loop (PLL).

The LO is an integrated LC voltage controlled oscillator (VCO) operating at twice the RF frequency (for the 868 MHz frequency band) or four times the RF frequency (for the 434 MHz and 315 MHz frequency bands). This allows the I/Q signals driving the mixer to be generated by division.

<sup>1.</sup> Refer to parameter 3.3 found in Section 19.1, "General Parameters."

MC33696 Data Sheet, Rev. 9

#### **Register Access through SPI**

The fractional divider offers high flexibility in the frequency generation for:

- Switching between transmit and receive modes.

- Achieving frequency modulation in FSK modulation transmission.

- Performing multi-channel links.

- Trimming the RF carrier.

Frequencies are controlled by means of registers. To allow for user preference, two programming access methods are offered (see Section 17.3, "Frequency Registers").

- In friendly access, all frequencies are computed internally from the contents of the carrier frequency and deviation frequency registers.

- In direct access, the user programs direct all three frequency registers.

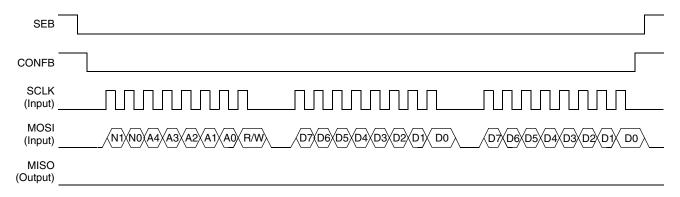

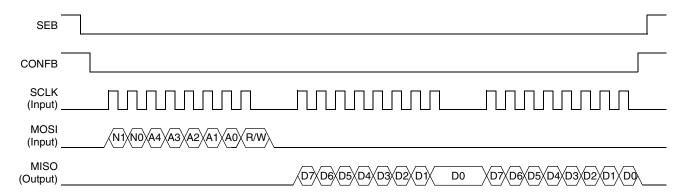

# 11 Register Access through SPI

## 11.1 SPI Interface

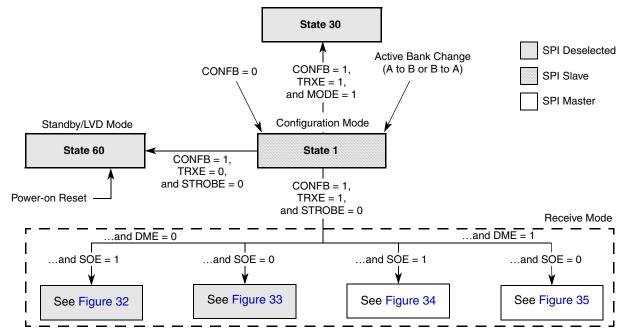

the MC33696 and the MCU communicate via a bidirectional serial digital interface. According to the selected mode, the MC33696 or the MCU manages the data transfer. The MC33696's digital interface can be used as a standard SPI (master/slave) or as a simple interface (SPI deselected). In the latter case, the interface's pins are used as standard I/O pins. However, the MCU has the highest priority, as it can control the MC33696 by setting CONFB pin to the low level.

The interface is operated by four I/O pins.

• SEB — Serial interface Enable

When SEB is set high, pins SCLK, MOSI, and MISO are set to high impedance. This allows individual selection in a multiple device system, where all devices are connected via the same bus. The rest of the circuit remains in the current state, enabling fast recovery times, but the power amplifier is disabled to prevent any uncontrolled RF transmission.

• SCLK — Serial Clock

Synchronizes data movement in and out of the device through its MOSI and MISO lines. The master and slave devices can exchange a byte of information during a sequence of eight clock cycles. Since SCLK is generated by the master device, this line is an input on a slave device.

• MOSI — Master Output Slave Input

Transmits bytes when master, and receives bytes when slave, with the most significant bit first. When no data are output, SCLK and MOSI force a low level.

• MISO — (Master Input) Slave Output

Transmits data when slave, with the MSB first. There is no master function. Data are valid on falling edges of SCLK. This means that the clock phase and polarity control bits of the microcontroller SPI have to be CPOL = 0 and CPHA = 1 (using Freescale acronyms).

Table 5 summarizes the serial digital interface feature versus the selected mode.

| Selected Mode |         | MC33696 Digital Interface Use                                   |  |

|---------------|---------|-----------------------------------------------------------------|--|

| Configuration |         | SPI slave, data received on MOSI, SCLK from MCU, MISO is output |  |

| Transmit      |         | SPI deselected, MOSI receives encoded data from MCU             |  |

| Receive       | DME = 1 | SPI master, data sent on MOSI with clock on SCLK                |  |

| DME = 0       |         | SPI deselected, received data are directly sent to MOSI         |  |

| Standby / I   | _VD     | SPI deselected, all I/O are high impedance                      |  |

Table 5. Serial Digital Interface Feature versus Selected Mode (SEB = 1)

The data transfer protocol for each mode is described in the following sections.

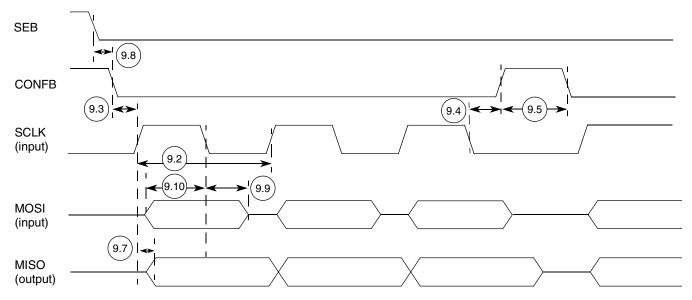

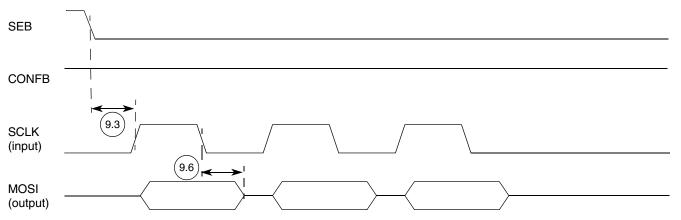

## 11.2 Configuration Mode

This mode is used to write or read the internal registers of the MC33696.

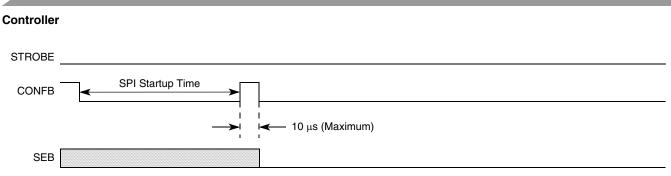

As long as a low level is applied to CONFB (see Figure 29), the MCU is the master node driving the SCLK input, the MOSI line input, and the MISO line output. Whatever the direction, SPI transfers are 8-bit based and always begin with a command byte, which is supplied by the MCU on MOSI. To be considered as a command byte, this byte must come after a falling edge on CONFB. Figure 3 shows the content of the command byte.

|          | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|----------|-------|-------|-------|-------|-------|-------|-------|-------|--|

| Bit Name | N1    | N0    | A4    | А3    | A2    | A1    | A0    | R/W   |  |

Figure 3. Command Byte

Bits N[1:0] specify the number of accessed registers, as defined in Table 6.

N[1:0]

Number N of Accessed Registers

00

1

01

2

10

4

11

8

**Table 6. Number N of Accessed Registers**

Bits A[4:0] specify the address of the first register to access. This address is then incremented internally by N after each data byte transfer.

R/W specifies the type of operation:

0 = Read

1 = Write

Thus, this bit is associated with the presence of information on MOSI (when writing) or MISO (when reading).

#### **Register Access through SPI**

Figure 4 and Figure 5 show write and read operations in a typical SPI transfer. In both cases, the SPI is a slave. A received byte is considered internally on the eighth falling edge of SCLK. Consequently, the last received bits, which do not form a complete byte, are lost.

#### NOTE

A low level applied to CONFB does not affect the configuration register contents.

Figure 4. Write Operation in Configuration Mode (N[1:0] = 01)

Figure 5. Read Operation in Configuration Mode (N[1:0] = 01)

# 11.3 Configuration Switching

This feature allows for defining two different configurations using two different banks, and for switching them automatically during wakeup when using a strobe oscillator, or by means of the strobe pin actuation by the MCU. This automatic feature may be used only in receiver mode; however, if one of the register banks is related to a transmitter configuration, it may be accessed directly by programing some bits to define the active bank, thus allowing fast switching between receiver mode and transmitter mode, or between any different possible configurations.

### 11.3.1 Bit Definition

Dit Name

Two sets of configuration registers are available. They are grouped in two different banks: Bank A and Bank B. Two bits are used to define which bank represents the state of the component.

| Bit Name | Direction | Location |  |

|----------|-----------|----------|--|

| BANKA    | R/W       | Bank A   |  |

| BANKB    | R/W       | Bank B   |  |

|          |           |          |  |

Divoction

| BANKA | BANKB | Actions                                                                     |

|-------|-------|-----------------------------------------------------------------------------|

| Χ     | 0     | Bank A is active (TX or RX)                                                 |

| 0     | 1     | Bank B is active (TX or RX)                                                 |

| 1     | 1     | Bank A and Bank B are active and will be used one after the other (RX only) |

At any time, it is possible to know what is the active bank by reading the status bit BANKS.

| Bit Name | Direction | Location | Comment                                                           |

|----------|-----------|----------|-------------------------------------------------------------------|

| BANKS    | R         | A & B    | Bank status: indicates which register bank is active.             |

|          |           |          | This bit, available in Bank A and Bank B, returns the same value. |

## 11.3.2 Bank Access and Register Mapping

Lacation

Registers are physically mapped following a byte organization. The possible address space is 32 bytes. The base address is specified in the command byte. This is then incremented internally to address each register, up to the number of registers specified by N[1:0], also specified by this command byte. All registers can then be scanned, whatever the type of transmission (read or write); however, writing to read-only bits or registers has no effect. When the last implemented address is reached, the internal address counter automatically loops back to the first mapped address (\$00).

At any time, it is possible to write or read the content of any register of Bank A and Bank B. Register access is defined as follows:

| R/W    | Bit can be read and written.                                                            |

|--------|-----------------------------------------------------------------------------------------|

| R      | Bit can be read. Write has no effect on bit value.                                      |

| RR     | Bit can be read. Read or write resets the value.                                        |

| R [A]  | Bit can be read, this returns the same value as Bank A.                                 |

| RR [A] | Bit can be read, this returns the same value as Bank A. Read or write resets the value. |

|        |                                                                                         |

**Table 7. Access to Specific Bits**

| Bit   | Bank | Byte    | Access   | Comment                                                                                                   |

|-------|------|---------|----------|-----------------------------------------------------------------------------------------------------------|

| RESET | Α    | CONFIG1 | R/W      | Available in BANKA.                                                                                       |

| OLS   | A, B | CONFIG3 | R-R[A]   | Bit value is the real time status of the PLL, BANKA, and BANKB access reflect the same value.             |

| LDVS  | A, B | CONFIG3 | RR-RR[A} | Bit value is the latched value of the low-voltage detector. Read or write from any bank resets value.     |

| SOE   | A, B | CONFIG2 | R/W-R[A} | SOE can be modified in BANKA. Access from BANKB reflects BANKA value.                                     |

| RSSIx | A, B | RSSI    | R-R[A}   | RSSI value is directly read from RSSI converter.<br>Reflected value is the same whatever the active byte. |

MC33696 Data Sheet, Rev. 9

4

| 00h CONFI   | G1-A             | 91 h      |          |          |           |         |          |         | 0Dh CONFI   | G1-B      | 91 h      |          |          |           |         |          |         |

|-------------|------------------|-----------|----------|----------|-----------|---------|----------|---------|-------------|-----------|-----------|----------|----------|-----------|---------|----------|---------|

|             | Bit 7            | Bit 6     | Bit 5    | Bit 4    | Bit 3     | Bit 2   | Bit 1    | Bit 0   |             | Bit 7     | Bit 6     | Bit 5    | Bit 4    | Bit 3     | Bit 2   | Bit 1    | Bit 0   |

| Bit Name    | LOF1             | LOF0      | CF1      | CF0      | RESET     | SL      | LVDE     | CLKE    | Bit Name    | LOF1      | LOF0      | CF1      | CF0      | _         | SL      | LVDE     | CLKE    |

| Reset Value | 1                | 0         | 0        | 1        | 0         | 0       | 0        | 1       | Reset Value | 1         | 0         | 0        | 1        | 0         | 0       | 0        | 1       |

|             | R/W              | R/W       | R/W      | R/W      | R/W       | R/W     | R/W      | R/W     |             | R/W       | R/W       | R/W      | R/W      | R         | R/W     | R/W      | R/W     |

| 0 =         | 304-434          | 304–315   | 315-434  | 314      | No        | T/R     | No       | No      | 0 =         | 304-434   | 304–315   | 315-434  | 314      | _         | T/R     | No       | No      |

| 1 =         | 315–916          | 434–916   | 868      | 434-868  | Yes       | R/T     | Yes      | Yes     | 1 =         | 315–916   | 434–916   | 868      | 434-868  | _         | R/T     | Yes      | Yes     |

| 01h CONFIG  | G2-A             | 10 h      |          |          |           |         |          |         | 0Eh CONFI   | G2-B      | 10 h      |          |          |           |         |          |         |

|             | Bit 7            | Bit 6     | Bit 5    | Bit 4    | Bit 3     | Bit 2   | Bit 1    | Bit 0   |             | Bit 7     | Bit 6     | Bit 5    | Bit 4    | Bit 3     | Bit 2   | Bit 1    | Bit 0   |

| Bit Name    | DSREF            | FRM       | MODU     | DR1      | DR0       | TRXE    | DME      | SOE     | Bit Name    | DSREF     | FRM       | MODU     | DR1      | DR0       | TRXE    | DME      | SOE     |

| Reset Value | 0                | 0         | 0        | 1        | 0         | 0       | 0        | 0       | Reset Value | 0         | 0         | 0        | 1        | 0         | 0       | 0        | 0       |

|             | R/W              | R/W       | R/W      | R/W      | R/W       | R/W     | R/W      | R/W     |             | R/W       | R/W       | R/W      | R/W      | R/W       | R/W     | R/W      | R[A]    |

| 0 =         | Fixed            | Friendly  | OOK      | 2.4-4.8  | 2.4-9.6   | Standby | No       | No      | 0 =         | Fixed     | Friendly  | OOK      | 2.4-4.8  | 2.4-9.6   | Standby | No       | No      |

| 1 =         | Adaptive         | Direct    | FSK      | 9.6-19.2 | 4.8-19.2  | Enable  | Yes      | Yes     | 1 =         | Adaptive  | Direct    | FSK      | 9.6-19.2 | 4.8-19.2  | Enable  | Yes      | Yes     |

| 02h CONFIG  | G3-A             | 30 h      |          |          |           |         |          |         | 0Fh CONFI   | G3-B      | 30 h      |          |          |           |         |          |         |

|             | Bit 7            | Bit 6     | Bit 5    | Bit 4    | Bit 3     | Bit 2   | Bit 1    | Bit 0   |             | Bit 7     | Bit 6     | Bit 5    | Bit 4    | Bit 3     | Bit 2   | Bit 1    | Bit 0   |

| Bit Name    | AFF1             | AFF0      | OLS      | LVDS     | ILA1      | ILA0    | OLA1     | OLA0    | Bit Name    | AFF1      | AFF0      | OLS      | LVDS     | ILA1      | ILA0    | OLA1     | OLA0    |

| Reset Value | 0                | 0         | 1        | 1        | 0         | 0       | 0        | 0       | Reset Value | 0         | 0         | 1        | 1        | 0         | 0       | 0        | 0       |

|             | R/W              | R/W       | R        | RR       | R/W       | R/W     | R/W      | R/W     |             | R/W       | R/W       | R[A]     | RR[A]    | R/W       | R/W     | R/W      | R/W     |

| 0 =         | 0.5–1 kHz        | 0.5–2 kHz | RAS      | RAS      | 0-8 dB    | 0–14 dB | 0-8 dB   | 0-14 dB | 0 =         | 0.5-1 kHz | 0.5–2 kHz | RAS      | RAS      | 0-8 dB    | 0–14 dB | 0-8 dB   | 0-14 dB |

| 1 =         | 2–4 kHz          | 1–4 kHz   | Unlocked | Low V    | 14-24 dB  | 8-24 dB | 14-24 dB | 8-24 dB | 1 =         | 2–4 kHz   | 1–4 kHz   | Unlocked | Low V    | 14-24 dB  | 8-24 dB | 14-24 dB | 8-24 dB |

| 03h COMM    | AND-A            | 9 h       |          |          |           |         |          |         | 10h COMM    | AND-B     | 9 h       |          |          |           |         |          |         |

|             | Bit 7            | Bit 6     | Bit 5    | Bit 4    | Bit 3     | Bit 2   | Bit 1    | Bit 0   |             | Bit 7     | Bit 6     | Bit 5    | Bit 4    | Bit 3     | Bit 2   | Bit 1    | Bit 0   |

| Bit Name    | AFFC             | IFLA      | MODE     | RSSIE    | EDD       | RAGC    | FAGC     | BANKS   | Bit Name    | AFFC      | IFLA      | MODE     | RSSIE    | EDD       | RAGC    | FAGC     | BANKS   |

| Reset Value | 0                | 0         | 0        | 0        | 1         | 0       | 0        | 1       | Reset Value | 0         | 0         | 0        | 0        | 1         | 0       | 0        | 1       |

|             | R/W              | R/W       | R/W      | R/W      | R/W       | R/W     | R/W      | R       |             | R/W       | R/W       | R/W      | R/W      | R/W       | R/W     | R/W      | R[A]    |

| 0 =         | AFFx OFF         | No        | RX       | No       | Slow dec. | No      | No       | B Bank  | 0 =         | AFFx OFF  | No        | RX       | No       | Slow dec. | No      | No       | B Bank  |

| 1 =         | AFFx ON          | –20 dB    | TX       | Yes      | Fast dec. | Yes     | Yes      | A Bank  | 1 =         | AFFx ON   | -20 dB    | TX       | Yes      | Fast dec. | Yes     | Yes      | A Bank  |

| 04h F1-A    |                  | 48 h      |          |          |           |         |          |         | 11h F1-B    |           | 4800 h    |          |          |           |         |          |         |

|             | Bit 7            | Bit 6     | Bit 5    | Bit 4    | Bit 3     | Bit 2   | Bit 1    | Bit 0   |             | Bit 7     | Bit 6     | Bit 5    | Bit 4    | Bit 3     | Bit 2   | Bit 1    | Bit 0   |

| Bit Name    | FSK3             | FSK2      | FSK1     | FSK0     | F11       | F10     | F9       | F8      | Bit Name    | FSK3      | FSK2      | FSK1     | FSK0     | F11       | F10     | F9       | F8      |

| Reset Value | 0                | 1         | 0        | 0        | 1         | 0       | 0        | 0       | Reset Value | 0         | 1         | 0        | 0        | 1         | 0       | 0        | 0       |

|             | R/W              | R/W       | R/W      | R/W      | R/W       | R/W     | R/W      | R/W     |             | R/W       | R/W       | R/W      | R/W      | R/W       | R/W     | R/W      | R/W     |

| 05h F2-A    |                  | 0 h       |          |          |           |         |          |         | 12h F2-B    |           | 0 h       |          |          |           |         |          |         |

|             | Bit 7            | Bit 6     | Bit 5    | Bit 4    | Bit 3     | Bit 2   | Bit 1    | Bit 0   |             | Bit 7     | Bit 6     | Bit 5    | Bit 4    | Bit 3     | Bit 2   | Bit 1    | Bit 0   |

| Bit Name    | F7               | F6        | F5       | F4       | F3        | F1      | F1       | F0      | Bit Name    | F7        | F6        | F5       | F4       | F3        | F1      | F1       | F0      |

| Reset Value | 0                | 0         | 0        | 0        | 0         | 0       | 0        | 0       | Reset Value | 0         | 0         | 0        | 0        | 0         | 0       | 0        | 0       |

|             | R/W              | R/W       | R/W      | R/W      | R/W       | R/W     | R/W      | R/W     |             | R/W       | R/W       | R/W      | R/W      | R/W       | R/W     | R/W      | R/W     |

|             | Bank A Registers |           |          |          |           |         |          |         |             |           | Bank      | B Regis  | ters     |           |         |          |         |

| Figure 6. Bank Registers

MC33696 Data Sheet, Rev. 9

| 06h FT1-A        |                       | 700701 h      |          |                      |         |         |         |               | 13h FT1-B     |                     | 700701 h      |          |               |         |         |          |              |

|------------------|-----------------------|---------------|----------|----------------------|---------|---------|---------|---------------|---------------|---------------------|---------------|----------|---------------|---------|---------|----------|--------------|

|                  | Bit 7                 | Bit 6         | Bit 5    | Bit 4                | Bit 3   | Bit 2   | Bit 1   | Bit 0         |               | Bit 7               | Bit 6         | Bit 5    | Bit 4         | Bit 3   | Bit 2   | Bit 1    | Bit 0        |

| Bit Name         | FTA11                 | FTA10         | FTA9     | FTA8                 | FTA7    | FTA6    | FTA5    | FTA4          | Bit Name      | FTA11               | FTA10         | FTA9     | FTA8          | FTA7    | FTA6    | FTA5     | FTA4         |

| Reset Value      | 0                     | 1             | 1        | 1                    | 0       | 0       | 0       | 0             | Reset Value   | 0                   | 1             | 1        | 1             | 0       | 0       | 0        | 0            |

|                  | R/W                   | R/W           | R/W      | R/W                  | R/W     | R/W     | R/W     | R/W           |               | R/W                 | R/W           | R/W      | R/W           | R/W     | R/W     | R/W      | R/W          |

| 07h FT2-A        |                       | 7 h           |          |                      |         |         |         |               | 14h FT2-B     |                     | 7 h           |          |               |         |         |          |              |

|                  | Bit 7                 | Bit 6         | Bit 5    | Bit 4                | Bit 3   | Bit 2   | Bit 1   | Bit 0         |               | Bit 7               | Bit 6         | Bit 5    | Bit 4         | Bit 3   | Bit 2   | Bit 1    | Bit 0        |

| Bit Name         | FTA3                  | FTA2          | FTA1     | FTA0                 | FTB11   | FTB10   | FTB9    | FTB8          | Bit Name      | FTA3                | FTA2          | FTA1     | FTA0          | FTB11   | FTB10   | FTB9     | FTB8         |

| Reset Value      | 0                     | 0             | 0        | 0                    | 0       | 1       | 1       | 1             | Reset Value   | 0                   | 0             | 0        | 0             | 0       | 1       | 1        | 1            |

|                  | R/W                   | R/W           | R/W      | R/W                  | R/W     | R/W     | R/W     | R/W           |               | R/W                 | R/W           | R/W      | R/W           | R/W     | R/W     | R/W      | R/W          |

| 08h FT3-A        |                       | 1 h           |          |                      |         |         |         |               | 15h FT3-B     |                     | 1 h           |          |               |         |         |          |              |

|                  | Bit 7                 | Bit 6         | Bit 5    | Bit 4                | Bit 3   | Bit 2   | Bit 1   | Bit 0         |               | Bit 7               | Bit 6         | Bit 5    | Bit 4         | Bit 3   | Bit 2   | Bit 1    | Bit 0        |

| Bit Name         | FTB7                  | FTB6          | FTB5     | FTB4                 | FTB3    | FTB2    | FTB1    | FTB0          | Bit Name      | FTB7                | FTB6          | FTB5     | FTB4          | FTB3    | FTB2    | FTB1     | FTB0         |

| Reset Value      | 0                     | 0             | 0        | 0                    | 0       | 0       | 0       | 1             | Reset Value   | 0                   | 0             | 0        | 0             | 0       | 0       | 0        | 1            |

|                  | R/W                   | R/W           | R/W      | R/W                  | R/W     | R/W     | R/W     | R/W           |               | R/W                 | R/W           | R/W      | R/W           | R/W     | R/W     | R/W      | R/W          |

| 09h RXONO        |                       | 75 h          |          |                      |         |         |         |               | 16h RXONO     |                     | 75 h          |          |               |         |         |          |              |

|                  | Bit 7                 | Bit 6         | Bit 5    | Bit 4                | Bit 3   | Bit 2   | Bit 1   | Bit 0         |               | Bit 7               | Bit 6         | Bit 5    | Bit 4         | Bit 3   | Bit 2   | Bit 1    | Bit 0        |

| Bit Name         | BANKA                 | RON3          | RON2     | RON1                 | RON0    | ROFF2   | ROFF1   | ROFF0         | Bit Name      | BANKB               | RON3          | RON2     | RON1          | RON0    | ROFF2   | ROFF1    | ROFF0        |

| Reset Value      | 0                     | 1             | 1        | 1                    | 1       | 1       | 1       | 1             | Reset Value   | 0                   | 1             | 1        | 1             | 1       | 1       | 1        | 1            |

|                  | R/W                   | R/W           | R/W      | R/W                  | R/W     | R/W     | R/W     | R/W           |               | R/W                 | R/W           | R/W      | R/W           | R/W     | R/W     | R/W      | R/W          |

| 0Ah ID-A         |                       | C0 h          |          |                      | <b></b> | <b></b> | <b></b> | <b>5</b> 11.6 | 17h ID-B      |                     | C0 h          | <b>-</b> | <b>5</b> 1. 4 | <b></b> | <b></b> | <b>-</b> | <b></b>      |

| <b>5</b> 11. A1  | Bit 7                 | Bit 6         | Bit 5    | Bit 4                | Bit 3   | Bit 2   | Bit 1   | Bit 0         | 50.00         | Bit 7               | Bit 6         | Bit 5    | Bit 4         | Bit 3   | Bit 2   | Bit 1    | Bit 0        |

| Bit Name         | IDL1                  | IDL0          | ID5      | ID4                  | ID3     | ID2     | ID1     | ID0           | Bit Name      | IDL1                | IDL0          | ID5      | ID4           | ID3     | ID2     | ID1      | ID0          |

| Reset Value      | 1                     | 1             | 0        | 0                    | 0       | 0       | 0       | 0             | Reset Value   | 1                   | 1             | 0        | 0             | 0       | 0       | 0        | 0            |

| ODL HEADE        | R/W                   | R/W           | R/W      | R/W                  | R/W     | R/W     | R/W     | R/W           | 18h HEADE     | R/W                 | R/W<br>80 h   | R/W      | R/W           | R/W     | R/W     | R/W      | R/W          |

| 0Bh HEADE        | : <b>H-A</b><br>Bit 7 | 80 h          | Bit 5    | Bit 4                | Bit 3   | Bit 2   | Bit 1   | Bit 0         | ION HEADE     | <b>н-в</b><br>Bit 7 |               | Bit 5    | Bit 4         | Bit 3   | Bit 2   | Bit 1    | Bit 0        |

| Bit Name         | HDL1                  | Bit 6<br>HDL0 | HD5      | HD4                  | HD3     | HD2     | HD1     | HD0           | Bit Name      | HDL1                | Bit 6<br>HDL0 | HD5      | HD4           | HD3     | HD2     | HD1      | HD0          |

| Reset Value      | 1                     | 0             | 0        | пD <del>4</del><br>0 | пD3     | 0       | 0<br>0  | 0             | Reset Value   | 1                   | 0             | 0        | пD4<br>0      | 0       | 0       | 0<br>0   | 0<br>0       |

| neset value      | R/W                   | R/W           | R/W      | R/W                  | R/W     | R/W     | R/W     | R/W           | nesel value   | R/W                 | R/W           | R/W      | R/W           | R/W     | R/W     | R/W      | R/W          |

| 0Ch RSSI-A       |                       | 80 h          | I 7/ V V | □/ <b>V V</b>        | □/ VV   | □/ VV   | □/ VV   | □/ <b>V V</b> | 19h RSSI-B    |                     | 80 h          | Π/ ۷ ۷   | Π/ <b>V V</b> | □/ VV   | IT/VV   | IT/VV    | □/ <b>VV</b> |

| OCH HOOFA        | Bit 7                 | Bit 6         | Bit 5    | Bit 4                | Bit 3   | Bit 2   | Bit 1   | Bit 0         | 1311 11331-0  | Bit 7               | Bit 6         | Bit 5    | Bit 4         | Bit 3   | Bit 2   | Bit 1    | Bit 0        |

| Bit Name         | RSSI7                 | RSSI6         | RSSI5    | RSSI4                | RSSI3   | RSSI2   | RSSI1   | RSSI0         | Bit Name      | RSSI7               | RSSI6         | RSSI5    | RSSI4         | RSSI3   | RSSI2   | RSSI1    | RSSI0        |

| Reset Value      | 0                     | 0             | 0        | 0                    | 0       | 0       | 0       | 0             | Reset Value   | 0                   | 0             | 0        | 0             | 0       | 0       | 0        | 0            |

| 1 1000t Value    | R                     | R             | R        | R                    | R       | R       | R       | R             | . 1000t Value | R[A]                | R[A]          | R[A]     | R[A]          | R[A]    | R[A]    | R[A]     | R[A]         |

| Bank A Registers |                       |               |          |                      |         |         |         |               | נייויי        | נייויי              |               | B Regist |               | , 1, 1  | ניקיי   | ן יוןיי  |              |

|                  |                       |               | Dank     | A negisi             | C12     |         |         |               |               |                     |               | Dank     | negisi        | ICI S   |         |          |              |

Figure 6. Bank Registers (continued)

### 11.3.3 Direct Switch Control

The conditions to enter direct switch control are:

- Strobe pin =  $V_{CC}$

- SOE bit = 0

By simply writing BANKA and BANKB, the active bank will be defined:

#### BANKA BANKB

X 0 Bank A is active (TX or RX)

0 1 Bank B is active (TX or RX)

1 Not allowed in direct switch control

Defined bank is active after exiting the configuration mode, i.e., CONFB line goes high.

The direct switch control should be used when:

- One or both banks are in transmitter configuration (MODE = 1)

- When the strobe oscillator cannot be used to define the switch timing (for example, not periodic)

- When strobe pin use is not possible (no sleep mode between the two configurations)

- No automatic switching is required and MCU SPI access is possible

### 11.3.4 Strobe Pin Switch Control

The conditions to enter strobe pin switch control are:

- Strobe pin: controlled by MCU I/O port

- SOE bit = 0

By simply writing BANKA and BANKB, the active banks will be defined.

#### BANKA BANKB

X 0 Bank A is active (TX or RX)

0 1 Bank B is active (TX or RX)

1 Bank A and Bank B are both active, configuration will toggle at each wakeup, not allowed with MODE = 1

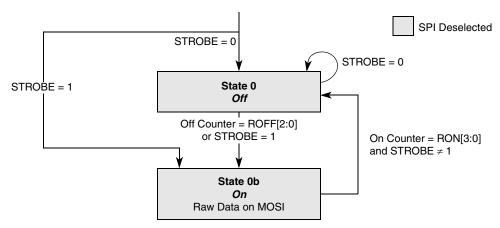

The strobe pin will control the OFF/ON state of the MC33696. The various available sequences are described in the following subsections.

## 11.3.4.1 BANKA = X, BANKB = 0

If strobe pin is 1, configuration is defined by Bank A, BANKS = 1

If strobe pin is 0, MC33696 configuration is OFF.

If a message is received during State A, current state remains State A up to end of message.

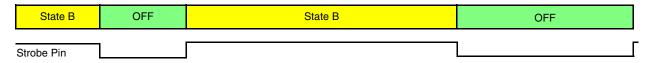

### 11.3.4.2 BANKA = 0, BANKB = 1

If strobe pin is 1, configuration is defined by Bank B, BANKS = 0.

If strobe pin is 0, MC33696 configuration is OFF.

If a message is received during State B, current state remains State B up to end of message.

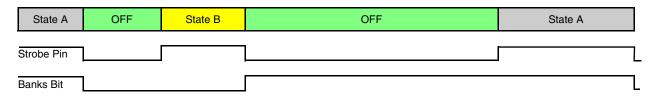

### 11.3.4.3 BANKA = 1, BANK B = 1

If strobe pin is 1, configuration is defined by BANKS. BANKS is toggled at each falling edge of the strobe pin.

If strobe pin is 0, MC33696 configuration is OFF.

If a message is received during state A or state B, current state remains the same up to end of message.

If a read or write access is done using SPI, the next sequence will begin with state A whatever was the active state before SPI access by MCU.

## 11.3.5 Strobe Oscillator Switch Control

The conditions to enter strobe oscillator switch control are:

- Strobe pin connected to an external capacitor to define timing (see Section 14, "Receiver On/Off Control")

- Strobe pin can also be connected to the MCU I/O port

- SOE bit = 1

By simply writing BANKA and BANKB, the active banks will be defined.

### BANKA BANKB

- X 0 Bank A is active (TX or RX) 0 1 Bank B is active (TX or RX)

- 1 Bank A and Bank B are both active, configuration will toggle at each wakeup, not allowed with MODE = 1

MCU can override strobe oscillator control by controlling strobe pin level. If MCU I/O port is in high impedance, strobe oscillator will control the OFF/ON state of the MC33696. The various available sequences are described in the following subsections.

**Register Access through SPI**

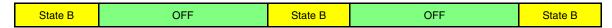

### 11.3.5.1 BANKA = X, BANKB = 0

If strobe pin is 1, configuration is defined by Bank A, BANKS = 1.

If strobe pin is 0, MC33696 configuration is OFF.

If a message is received during State A, current state remains State A up to end of message.

### 11.3.5.2 BANKA = 0, BANKB = 1

If strobe pin is 1, configuration is defined by Bank B, BANKS = 0.

If strobe pin is 0, MC33696 configuration is OFF.

If a message is received during State B, current state remains State B up to end of message.

### 11.3.5.3 BANKA = 1, BANK B = 1

BANKS toggles at the end of each state A or state B.

If strobe is forced to 1, configuration is frozen according to BANKS value.

If a read or write access is done using SPI, the next sequence will begin with state A in whatever was the active state before SPI access by MCU.

For all available sequences:

- State A and State B are defined by Bank A and Bank B.

- State A duration, TonA is defined by Bank A RON[3–0].

- State B duration, TonB is defined by Bank B RON[3–0].

- OFF duration, TonB is defined by Bank A ROFF[2–0].

- If strobe pin is 1, the state is ON and defined by BANKS at that time and remains this state up to the release of strobe and end of message if a message is being received.

- If a message is being received during State A or B, current state remains State A or B up to end of message.

- If strobe pin is 0 the state is OFF.

- If strobe pin is released from 0 while state is OFF, the initial OFF period is completed.

- Whenever is the change of duration of one state due to STROBE pin level or a message being received, this has no influence on the timing of the following states (A, B, or OFF).

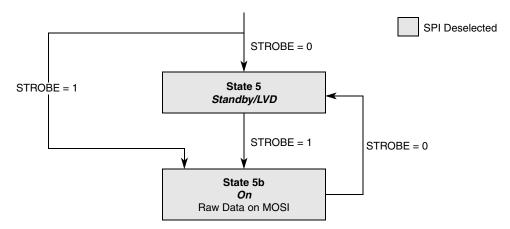

## 11.4 Standby: LVD Mode

The SPI is deselected. Nothing is sent and all incoming data are ignored until CONFB and SEB go low to switch back to configuration mode.

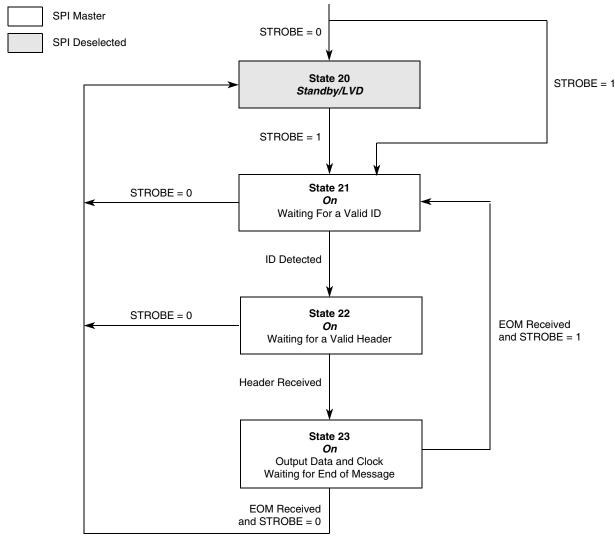

## 12 Communication Protocol

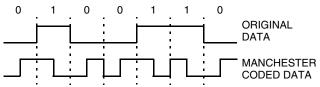

## 12.1 Manchester Coding Description

The MC33696 data manager is able to decode Manchester coded messages. For other codings, the data manager should be disabled (DME=0) for RAW data to be available on MOSI.

Manchester coding is defined as follows: data is sent during the first half-bit; and the complement of the data is sent during the second half-bit.

Figure 7. Example of Manchester Coding

The signal average value is constant. This allows clock recovery from the data stream itself. To achieve correct clock recovery, Manchester coded data must have a duty cycle between 47% and 53%.

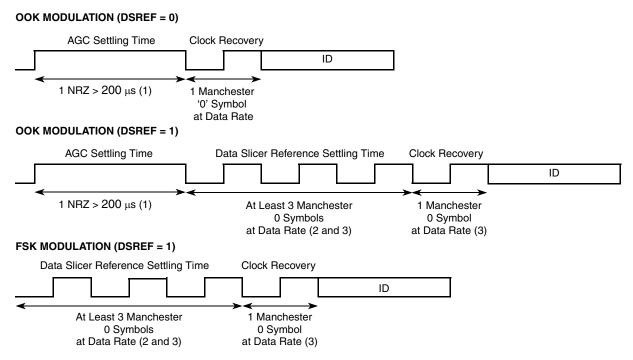

## 12.2 Preamble, Identifier, Header, and Message

The following description applies if the data manager is enabled (DME = 1).

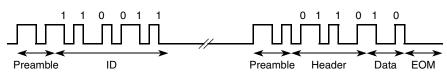

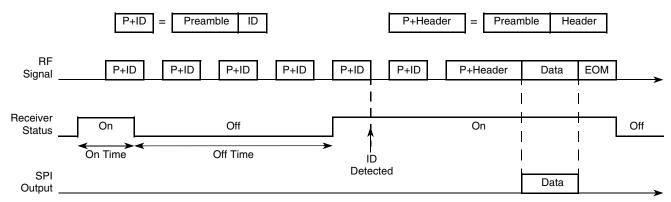

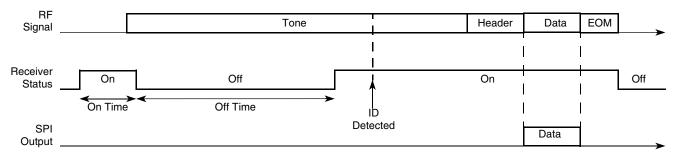

A complete telegram includes the following sequences: a preamble, an identifier (ID), the preamble again, a header, the message, and an end-of-message (EOM). These bit sequences are described below.

- Preamble: A preamble is required before the ID and before the header. It enables:

- In the case of OOK modulation, the AGC to settle, and the data slicer reference voltage to settle if DSREF = 1

- In the case of FSK modulation, the data slicer reference voltage to settle

- Clock recovery

The preamble content must be defined carefully, to ensure that it will not be decoded as the ID or the header. Figure 8 defines the preamble in OOK and FSK modulation.

#### **Communication Protocol**

- ID: The ID allows selection of the correct device in an RF transmission, as the content has been loaded previously in the ID register. Its length is variable, defined by the IDL[1:0] bits. The complement of the ID is also recognized as the identifier.

- Header: The header specifies the beginning of the message, as it is compared with the HEADER register. Its length is variable, defined by the HDL[1:0] bits. The complement of the header is also recognized as the header, in this case, output data are complemented.

- The ID and the header are sent at the same data rate as data.

- Message: Data must follow the header, with no delay.

- EOM: The message is completed with an end-of-message, consisting of two consecutive NRZ ones or zeroes (i.e., a Manchester code violation). Even in the case of FSK modulation, data must conclude with an EOM, and not simply by stopping the RF telegram.

Figure 9 shows a complete message comprising a 6-bit ID and a 4-bit header, followed by two data bits.

#### NOTES:

- 1. The AGC settling time pulse can be split over different pulses as long as the overall duration is at least 200 µs.

- 2. Table 15 defines the minimum number of Manchester symbols required for the data slicer operation versus the data and average filters cut-off frequencies.

- 3. The Manchester 0 symbol can be replaced by a 1.

Figure 8. Preamble Definition

Figure 9. Complete Message Example

MC33696 Data Sheet, Rev. 9

#### **NOTE**

It is possible to build a tone to form the detection sequence by programming the ID register with a full sequence of ones or zeroes. In this case, the header (or its complement) must not be found in this tone (i.e., it must not be a full sequence of ones or zeroes).

## 12.3 Message Protocol

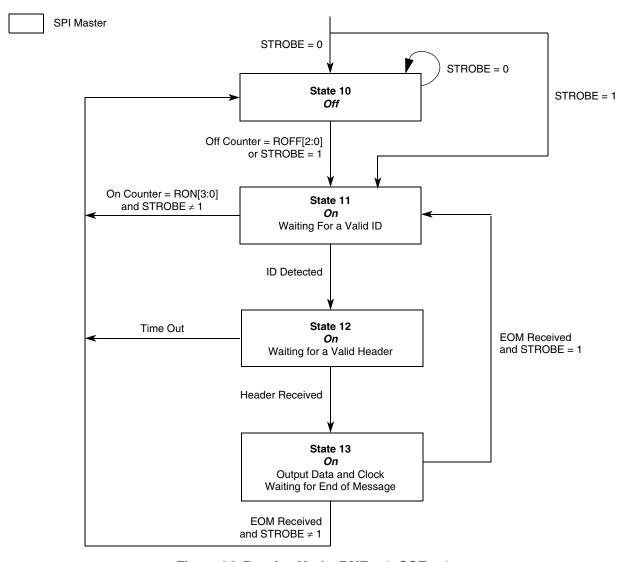

When the strobe oscillator is enabled (SOE = 1), the receiver is continuously on/off cycling. The ID must be recognized for the receiver to stay on. Consequently, the transmitted ID burst must be long enough to include two consecutive receiver On cycles.

When the strobe oscillator is not enabled (SOE = 0), these timing constraints must be respected by the external control applied to pin STROBE.

Figure 10. Complete Telegram with ID Detection

Figure 11. Complete Telegram with Tone Detection

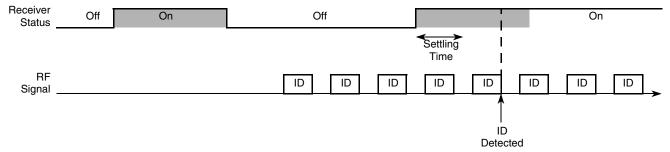

## 12.4 Receiver Startup Delay

As shown in Figure 12, a settling time is required when entering the on state.

#### **Data Manager**

Figure 12. Receiver Usable Window

# 13 Data Manager

In receive mode, Manchester coded data can be processed internally by the data manager. After decoding, the data are output on the digital interface, in SPI format. This minimizes the load on the MCU.

The data manager, when enabled (DME = 1), has five purposes:

- ID detection: The received identifier is compared with the identifier stored in the ID register.

- Header recognition: The received header is compared with the one stored in the HEADER register.

- Clock recovery: The clock is recovered during reception of the preamble and is computed from the shortest received pulse. During the reception of the telegram, the recovered clock is constantly updated to the data rate of the incoming signal.

- Output data and recovered clock on digital interface: See Section 15.2, "Receive Mode."

- End-of-message detection: An EOM consists of two consecutive NRZ ones or zeroes.

Table 8 details some MC33696 features versus DME values.

**DME Digital Interface Use Data Format** Output MOSI 0 SPI deselected Bit stream No clock SPI master Data bytes MOSI 1 when CONFB = 1 Recovered clock **SCLK**

Table 8. the MC33696 Features versus DME

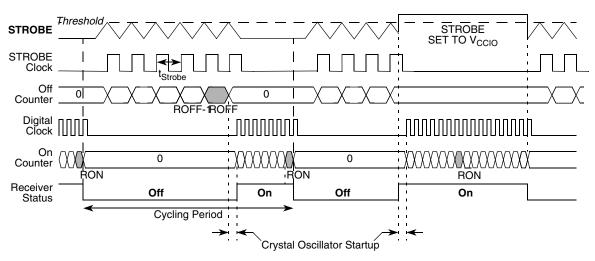

## 14 Receiver On/Off Control

In receive mode, on/off sequencing can be controlled internally, or managed externally by the MCU through the input pin STROBE.

If the internal timer is selected (SOE = 1),

- Off time is clocked by the strobe oscillator,

- On time is clocked by the crystal oscillator, enabling accurate control of the on time and, therefore, the current consumption of the whole system.

Each time is defined with the associated value found in the RXONOFF register.

- On time =  $RON[3:0] \times 512 \times T_{digclk}$  (see Table 20; begins after the crystal oscillator has started),

- Off time = receiver OFF time = N x T<sub>Strobe</sub> + MIN (T<sub>Strobe</sub> / 2, receiver On time), with N decoded from ROFF[2:0] (see Table 21).

The strobe oscillator is a relaxation oscillator in which an external capacitor C3 is charged by an internal current source (see Figure 47). When the threshold is reached, C3 is discharged and the cycle restarts. The strobe frequency is  $F_{Strobe} = 1/T_{Strobe}$  with  $T_{Strobe} = 10^6$  x C3.

In receive mode, setting the STROBE pin to  $V_{CCIO}$  at any time forces the circuit on. As  $V_{CCIO}$  is above the oscillator threshold voltage, the condition on which the STROBE pin is set to  $V_{CCIO}$  is detected internally, and the oscillator pulldown circuitry is disabled. This limits the current consumption. After a strobe forced at "1", the external driver should pass via a "0" state to discharge the capacitor before going to high impedance state (otherwise, the ON time would last a long time after the driver release).

When the strobe oscillator is running (i.e., during an off time), forcing the STROBE pin to  $V_{GND}$  stops the strobe clock and, therefore, maintains the circuit off.

Figure 13 shows the associated timings.

Figure 13. Receiver On/Off Sequence

## 15 Communication in Transmit and Receive Mode

## 15.1 Transmit Mode

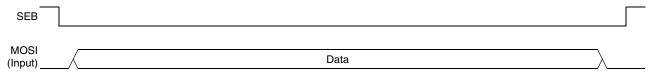

The SPI is deselected. The MC33696 receives the telegram to transmit on the MOSI line (see Figure 14).

Figure 14. Transfer in Transmit Mode

Freescale Semiconductor 23

MC33696 Data Sheet, Rev. 9

#### **Received Signal Strength Indicator (RSSI)**

In OOK modulation (MODU=0), modulation is performed by switching on and off the RF output stage.

MOSI = 0: output stage off MOSI = 1: output stage on

In FSK modulation (MODU = 1), modulation is performed by switching the RF carrier between two values.

MOSI = 0:  $f_{carrier0}$  corresponding to a logical 0 MOSI = 1:  $f_{carrier1}$  corresponding to a logical 1

See the FRM bit description (Figure 20) and Section 17.3, "Frequency Registers," for more details about setting carrier frequencies.

## 15.2 Receive Mode

The MC33696 is master and drives the digital interface in one of two ways, depending on the selection of the data manager.

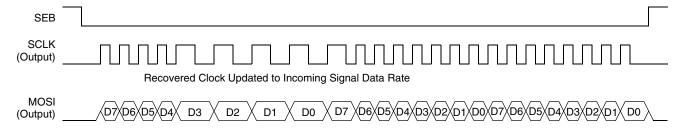

1. DME = 1: The data manager is enabled. The SPI is master. The MC33696 sends the recovered clock on SCLK and the received data on the MOSI line. Data are valid on falling edges of SCLK. If an entire number of bytes is received, the data manager may add an extra byte. The content of this extra byte is random. If the data received do not fill an entire number of bytes, the data manager will fill the last byte randomly. Figure 15 shows a typical transfer.

Figure 15. Typical Transfer in Receive Mode with Data Manager

2. DME = 0: The data manager is disabled. The SPI is deselected. Raw data are sent directly on the MOSI line, while SCLK remains at the low level.

# 16 Received Signal Strength Indicator (RSSI)

## 16.1 Module Description

In receive mode, a received signal strength indicator can be activated by setting bit RSSIE.

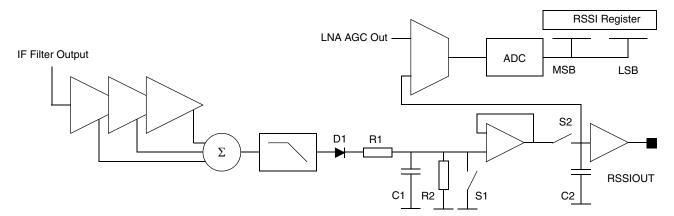

The input signal is measured at two different points in the receiver chain by two different means, as follows.

• At the IF filter output, a progressive compression logarithmic amplifier measures the input signal, ranging from the sensitivity level up to -50 dBm.

At the LNA output, the LNA AGC control voltage is used to monitor input signals in the range -50 dBm to -20 dBm.

Therefore, the logarithmic amplifier provides information relative to the in-band signal, whereas the LNA AGC voltage senses the input signal over a wider band.

The RSSI information given by the logarithmic amplifier is available in:

- Analog form on pin RSSIOUT

- Digital form in the four least significant bits of the status register RSSI

The information from the LNA AGC is available in digital form in the four most significant bits of status register RSSI.

The whole content of status register RSSI provides 2 x 4 bits of RSSI information about the incoming signal (see Section 17.6, "RSSI Register").

Figure 16 shows a simplified block diagram of the RSSI function.

The quasi peak detector (D1, R1, C1) has a charge time of about 20 µs to avoid sensitivity to spikes.

R2 controls the decay time constant of about 5 ms to allow efficient smoothing of the OOK modulated signal at low data rates. This time constant is useful in continuous mode when S2 is permanently closed.

To allow high-speed RSSI updating in peak pulse measurement, a discharge circuit (S1) is required to reset the measured voltage and to allow new peak detection.

Figure 16. RSSI Simplified Block Diagram

S2 is used to sample the RSSI voltage to allow peak pulse measurement (S2 used as sample and hold), or to allow continuous transparent measurement (S2 continuously closed).

The 4-bit analog-to-digital convertor (ADC) is based on a flash architecture. The conversion time is  $16 \times T_{diglck}$ . As a single convertor is used for the two analog signals, the RSSI register content is updated on a  $32 \times T_{digclk}$  timebase.

If RSSIE is reset, the whole RSSI module is switched off, reducing the current consumption. The output buffer connected to RSSIOUT is set to high impedance.

**Received Signal Strength Indicator (RSSI)**

## 16.2 Operation

Two modes of operation are available: sample mode and continuous mode.

## 16.2.1 Sample Mode

Sample mode allows the peak power of a specific pulse in an incoming frame to be measured.

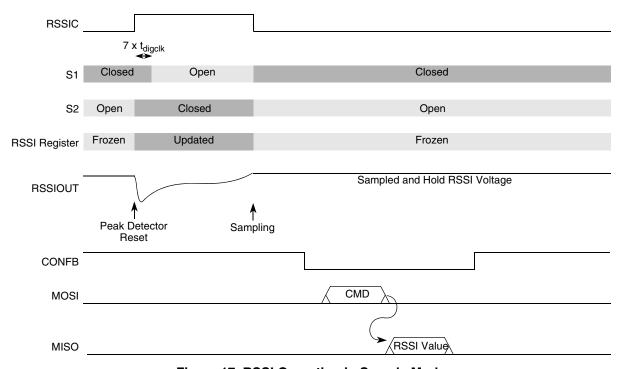

The quasi peak detector is reset by closing S1. After 7 x T<sub>digclk</sub>, S1 is released. S2 is closed when RSSIC is set high. On the falling edge of RSSIC, S2 is opened. The voltage on RSSIOUT is sampled and held. The last RSSI conversion results are stored in the RSSI register and no further conversion is done.

The RSSI register is updated every 32 x  $T_{digclk}$ . Therefore, the minimum duration of the high pulse on RSSIC is 32 x  $T_{digclk}$ .

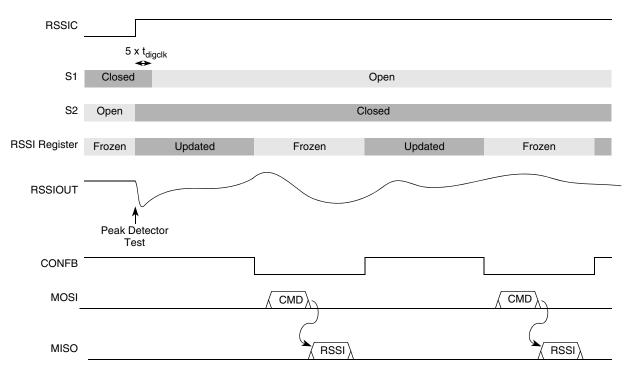

Figure 17. RSSI Operation in Sample Mode

### 16.2.2 Continuous Mode

Continuous mode is used to make a peak measurement on an incoming frame, without having to select a specific pulse to be measured.

The quasi peak detector is reset by closing S1. After 7 x  $T_{digclk}$ , S1 is opened. S2 is closed when RSSIC is set high. As long as RSSIC is kept high, S2 is closed, and RSSIOUT follows the peak value with a decay time constant of 5 ms.

The ADC runs continuously, and continually updates the RSSI register. Thus, reading this register gives the most recent conversion value, prior to the register being read. The minimum duration of the high pulse on CONFB is  $32 \times T_{digclk}$ .

Figure 18. RSSI Operation in Continuous Mode

# 17 Configuration, Command, and Status Registers

This section discusses the internal registers, which are composed of two classes of bits.

- Configuration and command bits allow the MC33696 to operate in a suitable configuration.

- Status bits report the current state of the system.

All registers can be accessed by the SPI; these registers are described below.

At power-on, the POR resets all registers to a known value (in the shaded rows in the following tables). This defines the MC33696's default configuration.

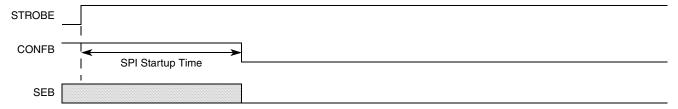

After POR, CONFB forces a low level. Therefore, an external pullup resistor is required to avoid entering configuration mode.

## 17.1 Configuration Registers

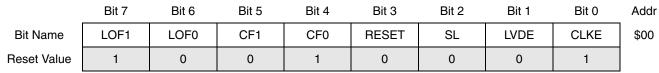

Figure 19 describes configuration register 1, CONFIG1.

Figure 19. CONFIG1 Register

Table 9. LOF[1:0] and CF[1:0] Setting Versus Carrier Frequency

| Carrier Frequency | LOF1 | LOF0 | CF1 | CF0 |

|-------------------|------|------|-----|-----|

| 304 MHz           | 0    | 0    | 0   | 0   |

| 315 MHz           | 1    | 0    | 0   | 0   |

| 426 MHz           | 0    | 1    | 0   | 1   |

| 434 MHz           | 0    | 1    | 0   | 1   |

| 868 MHz           | 0    | 1    | 1   | 1   |

| 915 MHz           | 1    | 1    | 1   | 1   |

RESET is a global reset. The bit is cleared internally, after use.

0 =no action

1 = reset all registers and counters

SL (Switch Level) selects the active level of the SWITCH output pin.

Table 10. Active Level of SWITCH Output Pin

| SL | Transceiver Function | Level on SWITCH |

|----|----------------------|-----------------|

| 0  | Receiving            | Low             |

|    | Transmitting         | High            |

| 1  | Transmitting         | Low             |

|    | Receiving            | High            |

LVDE (Low Voltage Detection Enable) enables the low voltage detection function.

0 = disabled

1 = enabled

#### NOTE

This bit is cleared by POR. In the event of a complete loss of the supply voltage, LVD is disabled at power-up, but the information is not lost as the status bit LVDS is set by POR.

CLKE (Clock Enable) controls the DATACLK output buffer.

0 = DATACLK remains low

1 = DATACLK outputs  $F_{dataclk}$

Figure 20 describes configuration register 2, CONFIG2.

|             | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Addr |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Bit Name    | DSREF | FRM   | MODU  | DR1   | DR0   | TRXE  | DME   | SOE   | \$01 |

| Reset Value | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 0     |      |

Figure 20. CONFIG2 Register

DSREF (Data Slicer Reference) selects the data slicer reference.

- 0 = Fixed reference (cannot be used in FSK)

- 1 = Adaptive reference (recommended for maximum sensitivity in OOK and FSK)

In the case of FSK modulation (MODU = 1), DSREF must be set.

FRM (Frequency Register Manager) enables either a user friendly access to one frequency register or a direct access to the two frequency registers.

- 0 = The carrier frequency and the FSK deviation are defined by the F register

- 1 = The local oscillator frequency and the two carrier frequencies are defined by two frequency registers, F and FT.

MODU (Modulation) sets the data modulation type.

- 0 = On/Off Keying (OOK) modulation

- 1 = Frequency Shift Keying (FSK) modulation

DR[1:0] (Data Rate) configure the receiver blocks operating in base band.

- Low-pass data filter

- Low-pass average filter generating the data slicer reference, if DSREF is set

- Data manager

Table 11. Base Band Parameter Configuration

| DR1 | DR0 | Data Filter<br>Cut-off Frequency | Average Filter<br>Cut-off Frequency | Data Manager<br>Data Rate Range |

|-----|-----|----------------------------------|-------------------------------------|---------------------------------|

| 0   | 0   | 6 kHz                            | 0.5 kHz                             | 2–2.8 kBd                       |

| 0   | 1   | 12 kHz                           | 1 kHz                               | 4–5.6 kBd                       |

| 1   | 0   | 24 kHz                           | 2 kHz                               | 8–10.6 kBd                      |

| 1   | 1   | 48 kHz                           | 4 kHz                               | 16-22.4 kBd                     |

If the data manager is disabled, the incoming signal data rate must be lower than or equal to the data manager maximum data rate.

TRXE (Transceiver Enable) enables the whole transceiver.

0 = standby mode

1 = other modes can be activated

DME (Data Manager Enable) enables the data manager.

0 = disabled

1 = enabled

MC33696 Data Sheet, Rev. 9

### Configuration, Command, and Status Registers

SOE (Strobe Oscillator Enable) enables the strobe oscillator.

0 = disabled

1 = enabled

Figure 21 describes configuration register 3, CONFIG3.

|             | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Addr |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Bit Name    | AFF1  | AFF0  | OLS   | LVDS  | ILA1  | ILA0  | OLA1  | OLA0  | \$02 |

| Reset Value | 0     | 0     | 1     | 1     | 0     | 0     | 0     | 0     |      |

Figure 21. CONFIG3 Register

OLS (Out of Lock Status) indicates the current status of the PLL.

0 =The PLL is in lock-in range

1 = The PLL is out of lock-in range

LVDS (Low Voltage Detection Status) indicates that a low voltage event has occurred when LVDE = 1. This bit is read-only and is cleared after a read access.

0 = No low voltage detected

1 = Low voltage detected

ILA[1:0] (Input Level Attenuation) define the RF input level attenuation.

**Table 12. RF Input Level Attenuation**

| ILA1 | ILA0 | RF Input Level<br>Attenuation | See Parameter<br>Number |

|------|------|-------------------------------|-------------------------|

| 0    | 0    | 0 dB                          | 2.5                     |

| 0    | 1    | 8 dB                          | 2.6                     |

| 1    | 0    | 16 dB                         | 2.7                     |

| 1    | 1    | 30 dB                         | 2.8                     |

Values in Table 12 assume the LNA gain is not reduced by the AGC.

OLA[1:0] (Output Level Attenuation) define the RF output level attenuation.

**Table 13. RF Output Level Attenuation**

| OLA1 | OLA0 | RF Output Level<br>Attenuation | See Parameter<br>Number |

|------|------|--------------------------------|-------------------------|

| 0    | 0    | 0 dB                           | 4.20                    |

| 0    | 1    | 6 dB                           | 4.3                     |

| 1    | 0    | 12 dB                          | 4.4                     |

| 1    | 1    | 25 dB                          | 4.5                     |

AFF[1:0] (Average Filter Frequency) define the average filter cut-off frequency if the AFFC bit is set.

| AFF1 | AFF0 | Average Filter Cut-off Frequency |

|------|------|----------------------------------|

| 0    | 0    | 0.5 kHz                          |

| 0    | 1    | 1 kHz                            |

| 1    | 0    | 2 kHz                            |

| 1    | 1    | 4 kHz                            |

Table 14. Average Filter Cut-off Frequency

If AFFC is reset, the average filter frequency is directly defined by bits DR[1:0], as shown in Table 11.

If AFFC is set, AFF[1:0] allow the overall receiver sensitivity to be improved by reducing the average filter cut-off frequency. The typical preamble duration of three Manchester zeroes or ones at the data rate must then be increased, as shown in Table 15.

Table 15. Minimum Number of Manchester Symbols in Preamble versus DR[1:0] and AFF[1:0]

|                 |    | DR[1:0] |    |    |    |  |  |  |  |

|-----------------|----|---------|----|----|----|--|--|--|--|

|                 |    | 00      | 01 | 10 | 11 |  |  |  |  |

|                 | 00 | 3       | 6  | 12 | 24 |  |  |  |  |

| A E E [ 1 . 0 ] | 01 | _       | 3  | 6  | 12 |  |  |  |  |

| AFF[1:0]        | 10 | _       | _  | 3  | 6  |  |  |  |  |

|                 | 11 | _       | _  | _  | 3  |  |  |  |  |

# 17.2 Command Register

Figure 22 describes the Command register, COMMAND.

|             | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Addr |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Bit Name    | AFFC  | IFLA  | MODE  | RSSIE | EDD   | RAGC  | FAGC  | _     | \$03 |

| Reset Value | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 1     |      |

Figure 22. COMMAND Register

AFFC (Average Filter Frequency Control) enables direct control of the average filter cut-off frequency.

- 0 = Average filter cut-off frequency is defined by DR[1:0]

- 1 = Average filter cut-off frequency is defined by AFF[1:0]

IFLA (IF Level Attenuation) controls the maximum gain of the IF amplifier in OOK modulation.

- 0 = No effect

- 1 = Decreases by 20 dB (typical) the maximum gain of the IF amplifier, in OOK modulation only The reduction in gain can be observed if the IF amplifier AGC system is disabled (by setting RAGC = 1). MODE selects the mode.

MC33696 Data Sheet, Rev. 9

### Configuration, Command, and Status Registers

0 =Receive mode

1 = Transmit mode

RSSIE (RSSI Enable) enables the RSSI function.

0 = Disabled

1 = Enabled

EDD (Envelop Detector Decay) controls the envelop detector decay.

0 =Slow decay for minimum ripple

1 = Fast decay

RAGC (Reset Automatic Gain Control) resets both receiver internal AGCs.

0 = No action

1 =Sets the gain to its maximum value

A first SPI access allows RAGC to be set; a second SPI access is required to reset it.

FAGC (Freeze Automatic Gain Control) freezes both receiver AGC levels.

0 = No action

1 = Holds the gain at its current value

# 17.3 Frequency Registers

Figure 23 and Figure 24 define the Frequency registers, F and FT.

|             | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Addr |

|-------------|--------|--------|--------|--------|--------|--------|-------|-------|------|

| Bit Name    | FSK3   | FSK2   | FSK1   | FSK0   | F11    | F10    | F9    | F8    | \$04 |

| Reset Value | 0      | 1      | 0      | 0      | 1      | 0      | 0     | 0     |      |

|             | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |      |

| Bit Name    | F7     | F6     | F5     | F4     | F3     | F2     | F1    | F0    | \$05 |

| Reset Value | 0      | 0      | 0      | 0      | 0      | 0      | 0     | 0     |      |

Figure 23. F Register

|             | Bit 23 | Bit 22 | Bit 21 | Bit 20 | Bit 19 | Bit 18 | Bit 17 | Bit 16 | Addr |

|-------------|--------|--------|--------|--------|--------|--------|--------|--------|------|

| Bit Name    | FTA11  | FTA10  | FTA9   | FTA8   | FTA7   | FTA6   | FTA5   | FTA4   | \$06 |

| Reset Value | 0      | 1      | 1      | 1      | 0      | 0      | 0      | 0      |      |

| ·           | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  |      |

| Bit Name    | FTA3   | FTA2   | FTA1   | FTA0   | FTB11  | FTB10  | FTB9   | FTB8   | \$07 |

| Reset Value | 0      | 0      | 0      | 0      | 0      | 1      | 1      | 1      |      |

| ·           | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |      |

| Bit Name    | FTB7   | FTB6   | FTB5   | FTB4   | FTB3   | FTB2   | FTB1   | FTB0   | \$08 |

| Reset Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 1      |      |

Figure 24. FT Register

How these registers are used is determined by the FRM bit, which is described below.

### FRM = 0 (User Friendly Access)

Whatever type of modulation is used (OOK or FSK), bits F[11:0] define the carrier frequency  $F_{carrier}$  The local oscillator frequency  $F_{LO}$  is then set automatically to  $F_{carrier} + F_{IF}$  (with  $F_{IF} =$  intermediate frequency). In addition,

- in the case of OOK modulation (MODU = 0):

- FSK[3:0], FTA[11:0], and FTB[11:0] are not used.

- in the case of FSK modulation (MODU = 1):

- FSK[3:0] sets the frequency deviation Df as defined in Table 16.

**Table 16. Frequency Deviation Definition**

| CF[1:0] | Frequency Deviation ∆f               |

|---------|--------------------------------------|

| 00, 01  | F <sub>ref</sub> x(FSK[3:0]+1)/ 2048 |

| 11      | F <sub>ref</sub> x(FSK[3:0]+1)/ 1024 |

Table 17 gives a numerical example in the 434 MHz band (CF[1:0] = 01).

**Table 17. Frequency Numerical Example (434 MHz Band)**

| FSK[3:0] | Frequency Deviation ∆f |

|----------|------------------------|

| 0000     | ± 12 kHz               |

| 0001     | ± 24 kHz               |

| 0010     | ± 36 kHz               |

|          |                        |