# Freescale Semiconductor

**Technical Data**

Document Number: MC33794 Rev 9, 11/2006

**√RoHS**

MC33794

ELECTRIC FIELD IMAGING DEVICE

EK SUFFIX 54-LEAD SOICW-EP CASE 1390-02

# **Electric Field Imaging Device**

The MC33794 is intended for applications where noncontact sensing of objects is desired. When connected to external electrodes, an electric field is created., The MC33794 is intended for use in detecting objects in this electric field. The IC generates a low-frequency sine wave. The frequency is adjustable by using an external resistor and is optimized for 120 kHz. The sine wave has very low harmonic content to reduce harmonic interference.

The MC33794 also contains support circuits for a microcontroller unit (MCU) to allow the construction of a two-chip E-field system.

#### Features

- · Supports up to 9 Electrodes and 2 References or Electrodes

- · Shield Driver for Driving Remote Electrodes Through Coaxial Cables

- +5.0 V Regulator to Power External Circuit

- · ISO-9141 Physical Layer Interface

- · Lamp Driver Output

- · Watchdog and Power-ON Reset Timer

- · Critical Internal Nodes Scaled and Selectable for Measurement

- · High-Purity Sine Wave Generator Tunable with External Resistor

#### **Typical Applications**

- · Occupant Detection Systems

- Appliance Control Panels and Touch Sensors

- · Linear and Rotational Sliders

- Spill Over Flow Sensing Measurement

- · Refrigeration Frost Sensing

- · Industrial Control and Safety Systems Security

- · Proximity Detection for Wake-Up Features

- · Touch Screens

- Garage Door Safety Sensing

- · Liquid Level Sensing

| ORDERING INFORMATION                                                    |               |         |             |  |

|-------------------------------------------------------------------------|---------------|---------|-------------|--|

| Device Name Temperature Range (T <sub>A</sub> ) Package Drawing Package |               |         |             |  |

| MC33794EK/R2                                                            | -40°C to 85°C | 1390-02 | 54 SOICW-EP |  |

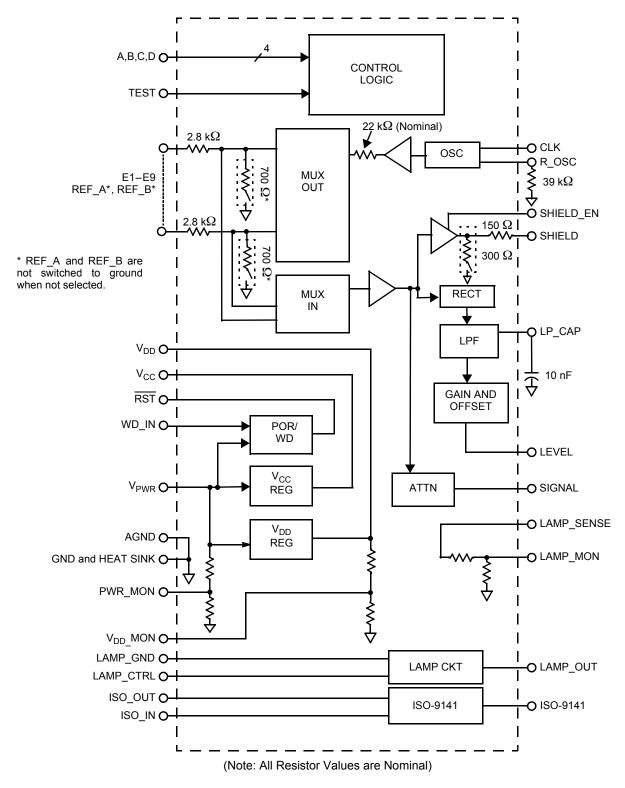

# INTERNAL BLOCK DIAGRAM

Figure 1. Simplified Functional Block Diagram

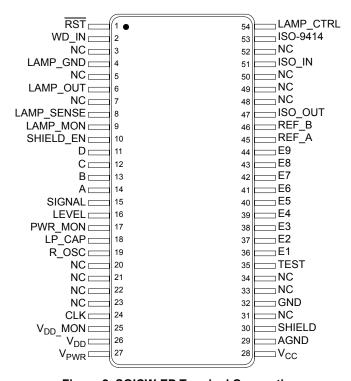

# **SOICW-EP TERMINAL CONNECTIONS**

Figure 2. SOICW-EP Terminal Connections

Table 1. SOICW-EP TERMINAL FUNCTION DESCRIPTION

| Terminal                                       | Terminal<br>Name | Formal Name | Definition                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                              | RST              | Reset       | This output is intended to generate the reset function of a typical MCU. It has a delay for Power-ON Reset, level detectors to force a reset when V <sub>CC</sub> REG is out-of-range high or low, and a watchdog timer that will force a reset if WD_IN is not asserted at regular intervals. Timing is derived from the oscillator and will change with changes in the resistor attached to R_OSC.                                |

| 2                                              | WD_IN            | Watchdog In | This terminal must be asserted and deserted at regular interval in order to prevent RST from being asserted. By having the MCU program perform this operation more often the allowed time, a check that the MCU is running and executing its program is assured. If this doesn't occur, the MCU will be reset. If the watchdog function is not desired, this terminal may be connected to CLK to prevent a reset from being issued. |

| 3, 5, 7,<br>20–23, 31,<br>33, 34,<br>48–50, 52 | NC               | No connect  | These terminals may be used at some future date and should be left open.                                                                                                                                                                                                                                                                                                                                                            |

| 4                                              | LAMP_GND         | Lamp Ground | This is the ground for the current from the lamp. The current into LAMP_OUT flows out through this terminal.                                                                                                                                                                                                                                                                                                                        |

| 6                                              | LAMP_OUT         | Lamp Driver | This is an active low output capable of sinking current of a typical indicator lamp. One end of the lamp should be connected to a positive supply (for example, battery voltage) and the other side to this terminal. The current is limited to prevent damage to the IC in the case of a short or surge during lamp turn-on or burn-out.                                                                                           |

Table 1. SOICW-EP TERMINAL FUNCTION DESCRIPTION (continued)

| Terminal | Terminal<br>Name     | Formal Name               | Definition                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|----------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8        | LAMP_SENSE           | Lamp Sense                | This terminal is normally connected to the LAMP_OUT terminal. The voltage at this terminal is reduced and sent to LAMP_MON so the voltage at the lamp terminal is brought into the range of the analog-to-digital converter (ADC) in the MCU.                                                                                                                                                                        |

| 9        | LAMP_MON             | Lamp Monitor              | This terminal is connected through a voltage divider to the LAMP_SENSE terminal. The voltage divider scales the voltage at this terminal so that battery voltage present when the lamp is off is scaled to the range of the MCU ADC. With the lamp off, this terminal will be very close to battery voltage if the lamp is not burned out and the terminal is not shorted to ground. This is useful as a lamp check. |

| 10       | SHIELD_EN            | Shield Driver             | This terminal is used to enable the shield signal. The shield is disabled when SHIELD_EN is a logic low (ground)                                                                                                                                                                                                                                                                                                     |

| 11–14    | A, B, C, D           | Selector Inputs           | These input terminals control which electrode or reference is active. Selection values are shown in Table 5, Electrode Selection, page 10. These are logic level inputs.                                                                                                                                                                                                                                             |

| 15       | SIGNAL               | Undetected Signal         | This is the undetected signal being applied to the detector. It has a DC level with the low radio frequency signal superimposed on it. Care must be taken to minimize DC loading of this signal. A shift of DC will change the center point of the signal and adversely affect the detection of the signal.                                                                                                          |

| 16       | LEVEL                | Detected Level            | This is the detected, amplified, and offset representation of the signal voltage on the selected electrode. Filtering of the rectified signal is performed by a capacitor attached to LP_CAP.                                                                                                                                                                                                                        |

| 17       | PWR_MON              | Power Monitor             | This is connected through a voltage divider to $V_{PWR}$ . It allows reduction of the voltage so it will fall within the range of the ADC on the MCU.                                                                                                                                                                                                                                                                |

| 18       | LP_CAP               | Low-Pass Filter Capacitor | A capacitor on this terminal forms a low pass filter with the internal series resistance from the detector to this terminal. This terminal can be used to determine the detected level before amplification or offset is applied. A 10 nF capacitor connected to this terminal will smooth the rectified signal. More capacitance will increase the response time.                                                   |

| 19       | R_OSC                | Oscillator Resistor       | A resistor from this terminal to circuit ground determines the operating frequency of the oscillator. The MC33794 is optimized for operation around 120 kHz.                                                                                                                                                                                                                                                         |

| 24       | CLK                  | Clock                     | This terminal provides a square wave output at the same frequency as the internal oscillator. The edges of the square wave coincide with the peaks (positive and negative) of the sine wave.                                                                                                                                                                                                                         |

| 25       | V <sub>DD</sub> _MON | V <sub>DD</sub> Monitor   | This is connected through an internal voltage divider to $V_{DD}$ REG. It allows reduction of the voltage so it will fall within the range of the ADC on the MCU.                                                                                                                                                                                                                                                    |

| 26       | V <sub>DD</sub>      | V <sub>DD</sub> Capacitor | A capacitor is connected to this terminal to filter the internal analog regulated supply. This supply is derived from $V_{PWR}$ through internal $V_{DD}$ REG.                                                                                                                                                                                                                                                       |

| 27       | V <sub>PWR</sub>     | Positive Power Supply     | 12 V power applied to this terminal will be converted to the regulated voltages needed to operate the part. It is also converted to 5.0 V (internal $V_{CC}$ REG) and 8.5 V (internal $V_{DD}$ REG) to power the MCU and external devices.                                                                                                                                                                           |

| 28       | V <sub>CC</sub>      | 5.0 V Regulator Output    | This output terminal requires a 47 $\mu$ F capacitor and internal V <sub>CC</sub> REG provides a regulated 5.0 V for the MCU and for internal needs of the MC33794.                                                                                                                                                                                                                                                  |

| 29       | AGND                 | Analog Ground             | This terminal is connected to the ground return of the analog circuitry. This ground should be kept free of transient electrical noise like that from logic switching. Its path to the electrical current return point should be kept separate from the return for GND.                                                                                                                                              |

| 30       | SHIELD               | Shield Driver             | This terminal connects to cable shields to cancel cable capacitance.                                                                                                                                                                                                                                                                                                                                                 |

Table 1. SOICW-EP TERMINAL FUNCTION DESCRIPTION (continued)

| Terminal | Terminal<br>Name              | Formal Name                                            | Definition                                                                                                                                                                                                         |

|----------|-------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32       | GND                           | Ground                                                 | This terminal and metal backing is the IC power return and thermal radiator/conductor.                                                                                                                             |

| 35       | TEST                          | Test Mode Control                                      | This terminal is normally connected to circuit ground. There are special operating modes associated with this terminal when it is not at ground.                                                                   |

| 36-44    | E1-E9                         | Electrode Connections                                  | These are the electrode terminals. They are connected either directly or through coaxial cables to the electrodes for measurements. When not selected, these outputs are grounded through the internal resistance. |

| 45, 46   | REF_A,<br>REF_B<br>(E10, E11) | Reference Connections<br>(Or as additional electrodes) | These terminals can be individually selected to measure a known capacitance value. Unlike E1-E9, these two inputs are not grounded when not selected.                                                              |

| 47       | ISO_OUT                       | ISO-9141 Output                                        | This terminal translates ISO-9141 receive levels to 5.0 V logic levels for the MCU.                                                                                                                                |

| 51       | ISO_IN                        | ISO-9141 Input                                         | This terminal accepts data from the MCU to be sent over the ISO-9141 communications interface. It translates the 5.0 V logic levels from the MCU to transmit levels on the ISO-9141 bus.                           |

| 53       | ISO-9141                      | ISO-9141 Bus                                           | This terminal connects to the ISO-9141 bus. It provides the drive and detects signaling on the bus and translates it from the bus level to logic levels for the MCU.                                               |

| 54       | LAMP_CTRL                     | Lamp Control                                           | This signal is used to control the lamp driver. A high logic level turns on the lamp.                                                                                                                              |

### **MAXIMUM RATINGS**

### Table 2. Maximum Ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Rating                                                                                   | Symbol                                                   | Value            | Unit |

|------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------|------|

| Peak VPWR Voltage                                                                        | V <sub>PWRPK</sub>                                       | 40               | V    |

| Double Battery  1 Minute Maximum T <sub>A</sub> = 30°C                                   | V <sub>DBLBAT</sub>                                      | 26.5             | V    |

| ESD Voltage  Human Body Model (1)  Machine Model (2)                                     | V <sub>ESD1</sub><br>V <sub>ESD2</sub>                   | ±2000<br>±200    | V    |

| Storage Temperature                                                                      | T <sub>STG</sub>                                         | -55 to 150       | °C   |

| Operating Ambient Temperature                                                            | T <sub>A</sub>                                           | -40 to 85        | °C   |

| Operating Junction Temperature                                                           | T <sub>J</sub>                                           | -40 to 150       | °C   |

| Thermal Resistance  Junction-to-Ambient (3)  Junction-to-Case (4)  Junction-to-Board (5) | R <sub>θJA</sub><br>R <sub>θJC</sub><br>R <sub>θJB</sub> | 41<br>0.2<br>3.0 | °C/W |

| Lead Soldering Temperature (for 10 Seconds)                                              | T <sub>SOLDER</sub>                                      | 260              | °C   |

#### Notes

- 1. ESD1 performed in accordance with the Human Body Model ( $C_{ZAP}$  = 100 pF,  $R_{ZAP}$  = 1500  $\Omega$ ).

- 2. ESD2 performed in accordance with the Machine Model ( $C_{ZAP}$  = 200 pF,  $R_{ZAP}$  = 0  $\Omega$ ).

- 3. Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance. In accordance with SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- 4. Indicates the average thermal resistance between the die and the case top surface as measured by the cold plate method (MILSPEC 883 Method 1012.1) with the cold plate temperature used for the case temperature.

- Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

# STATIC ELECTRICAL CHARACTERISTICS

### **Table 3. Static Electrical Characteristics**

Characteristics noted under conditions 9.0 V  $\leq$  VPWR  $\leq$  18 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under normal conditions unless otherwise noted. Voltages are relative to GND unless otherwise noted.

| Characteristic                                                                                                                                | Symbol               | Min   | Тур  | Max   | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------|------|-------|------|

| Voltage Regulators                                                                                                                            |                      |       | l    | 1     | l    |

| 5.0 V Regulator Voltage 7.0 V $\leq$ V <sub>PWR</sub> $\leq$ 18 V, 1.0 mA $\leq$ I <sub>L</sub> $\leq$ 75 mA, C <sub>FILT</sub> = 47 $\mu$ F  | V <sub>CC</sub>      | 4.75  | 5.0  | 5.25  | V    |

| Analog Regulator Voltage<br>9.0 V ≤ V <sub>PWR</sub> ≤ 18 V, C <sub>FILT</sub> = 47 μF                                                        | V <sub>ANALOG</sub>  | 8.075 | 8.5  | 8.925 | V    |

| Out-of-Range Voltage Detector (Terminal name V <sub>CC</sub> )                                                                                |                      |       | •    |       |      |

| 5.0 V Low Voltage Detector                                                                                                                    | $V_{LV5}$            | 4.0   | 4.52 | 4.72  | V    |

| 5.0 V High Voltage Detector                                                                                                                   | V <sub>HV5</sub>     | 5.26  | 5.55 | 5.83  | V    |

| 5.0 V Out-of-Range Voltage Detector Hysteresis                                                                                                | V <sub>HYS5</sub>    | -     | 0.05 | _     | V    |

| ISO-9141 Communications Interface                                                                                                             |                      |       | •    |       |      |

| Input Low Level <sup>(6)</sup>                                                                                                                | VIF <sub>INLO</sub>  | 0.30  | 0.33 | _     | V/V  |

| Input High Level <sup>(6)</sup>                                                                                                               | VIF <sub>INHI</sub>  | -     | 0.53 | 0.7   | V/V  |

| Input Hysteresis <sup>(6)</sup>                                                                                                               | VIF <sub>INHYS</sub> | -     | 0.2  | _     | V/V  |

| Output Low <sup>(6)</sup>                                                                                                                     | VIF <sub>OLO</sub>   | -     | -    | 0.2   | V/V  |

| Output High <sup>(6)</sup>                                                                                                                    | VIF <sub>OHI</sub>   | 0.8   | -    | _     | V/V  |

| Output Breakdown I <sub>OUT</sub> = 20 mA                                                                                                     | VIFZ                 | 40    | _    | _     | V    |

| Output Resistance I <sub>OUT</sub> = 40 mA                                                                                                    | RIF <sub>ON</sub>    | -     | 58   | _     | Ω    |

| Current Limit Sinking Current with V <sub>OUT</sub> < 0.3 V <sub>PWR IN</sub>                                                                 | IIF <sub>LIM</sub>   | 60    | 90   | 120   | mA   |

| Output Propagation Delay Out to ISO-9141, C <sub>LOAD</sub> = 20 pF                                                                           | TIF <sub>DLY</sub>   | _     | _    | 8.0   | μS   |

| ISO In                                                                                                                                        |                      |       | •    |       |      |

| Logic Output Low I <sub>SINK</sub> = 1.0 mA                                                                                                   | VIF <sub>OLO</sub>   | -     | _    | 1.0   | V    |

| Logic Output Pull-Up Current VOUT = 0 V                                                                                                       | IIF <sub>PU</sub>    | 100   | _    | _     | μΑ   |

| Input to Output Propagation Delay ISO-9141 to ISO_IN, R <sub>L</sub> = 10 k $\Omega$ , C <sub>L</sub> = 470 pF, 7.0 V $\leq$ VPWR $\leq$ 18 V | TIF <sub>DLY</sub>   | -     | -    | 5.4   | μs   |

Notes

6. Ratio to V<sub>PWR</sub>

# Table 3. Static Electrical Characteristics (continued)

Characteristics noted under conditions 9.0 V  $\leq$  VPWR  $\leq$  18 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under normal conditions unless otherwise noted. Voltages are relative to GND unless otherwise noted.

| Characteristic                                                                                               | Symbol              | Min        | Тур    | Max       | Unit            |

|--------------------------------------------------------------------------------------------------------------|---------------------|------------|--------|-----------|-----------------|

| Electrode Signals                                                                                            | <b>-</b>            |            |        | 1         | 1               |

| Total Variance Between Electrode Measurements $^{(7)}$<br>All $C_{LOAD}$ = 15 pF                             | ELV <sub>VAR</sub>  | _          | _      | 3.0       | %               |

| Electrode Maximum Harmonic Level Below Fundamental $^{(8)}$<br>5.0 pF $\leq$ C <sub>LOAD</sub> $\leq$ 100 pF | EL <sub>HARM</sub>  | _          | -20    | -         | dB              |

| Electrode Transmit Output Range<br>5.0 pF ≤ C <sub>LOAD</sub> ≤ 100 pF                                       | EL <sub>TXV</sub>   | 1.0        | _      | 8.0       | V               |

| Receive Input Voltage Range                                                                                  | $RX_V$              | 0          | -      | 9.0       | V               |

| Grounding Switch on Voltage  I <sub>SW</sub> = 1.0 mA                                                        | SW <sub>VON</sub>   | _          | -      | 5.0       | V               |

| Shield Driver                                                                                                | <b>-</b>            |            |        | 1         | 1               |

| Shield Driver Output Level $0 \text{ pF} \leq C_{\text{LOAD}} \leq 500 \text{ pF}$                           | SD <sub>TXV</sub>   | 1.0        | _      | 8.0       | V               |

| Shield Driver Input Range                                                                                    | SD <sub>IN</sub>    | 0          | _      | 9.0       | V               |

| Grounding Switch on Voltage <sup>(9)</sup>                                                                   | SW <sub>VON</sub>   | -          | _      | 1.5       | V               |

| Logic I/O                                                                                                    |                     |            |        |           | 1               |

| CMOS Logic Input Low Threshold                                                                               | V <sub>THL</sub>    | 0.3        | _      | _         | V <sub>CC</sub> |

| Logic Input High Threshold                                                                                   | V <sub>THH</sub>    | _          | _      | 0.7       | V <sub>CC</sub> |

| Voltage Hysteresis                                                                                           | V <sub>HYS</sub>    | -          | 0.06   | _         | V <sub>CC</sub> |

| Input Current $V_{IN} = V_{CC}$ $V_{IN} = 0 V$                                                               | I <sub>IN</sub>     | 10<br>-5.0 | -<br>- | 50<br>5.0 | μА              |

| Signal Detector                                                                                              | •                   |            | •      | •         | •               |

| Detector Output Resistance                                                                                   | DET <sub>RO</sub>   | _          | 50     | _         | kΩ              |

| LP_CAP to LEVEL Gain                                                                                         | A <sub>REC</sub>    | 3.6        | 4.0    | 4.4       | A <sub>V</sub>  |

| LP_CAP to LEVEL Offset                                                                                       | V <sub>RECOFF</sub> | -3.3       | -3.0   | -2.7      | V               |

#### Notes

- 7. Verified by design. Not tested in production.

- 8. Verified by design and characterization. Not tested in production.

- 9. Current into grounded terminal under test = 1.0 mA.

# Table 3. Static Electrical Characteristics (continued)

Characteristics noted under conditions 9.0 V  $\leq$  VPWR  $\leq$  18 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under normal conditions unless otherwise noted. Voltages are relative to GND unless otherwise noted.

| Characteristic                                           | Symbol              | Min    | Тур     | Max    | Unit |

|----------------------------------------------------------|---------------------|--------|---------|--------|------|

| Lamp Driver                                              |                     |        |         |        |      |

| On Resistance<br>I <sub>IN</sub> = 400 mA                | RLD <sub>DSON</sub> | _      | 1.75    | 3.5    | Ω    |

| Current Limit V <sub>OUT</sub> = 1.0 V                   | ILD <sub>LIM</sub>  | 0.7    | -       | 1.7    | А    |

| On-Voltage<br>I <sub>OUT</sub> = 400 mA                  | VLD <sub>ON</sub>   | -      | -       | 1.4    | V    |

| Breakdown Voltage<br>I <sub>OUT</sub> = 100 μA, Lamp Off | VLD <sub>Z</sub>    | 40     | -       | -      | V    |

| Voltage Monitors                                         |                     |        | 1       | •      | 1    |

| LAMP_MON to LAMP_SENSE Ratio                             | LMP <sub>MON</sub>  | 0.1950 | 0.20524 | 0.2155 | V/V  |

| PWR_MON to V <sub>PWR</sub> Ratio                        | PWR <sub>MON</sub>  | 0.2200 | 0.2444  | 0.2688 | V/V  |

| V <sub>DD</sub> MON to V <sub>DD</sub> Ratio             | V <sub>DD_MON</sub> | 0.45   | 0.5     | 0.55   | V/V  |

| Supply                                                   |                     |        |         |        |      |

| Quiescent supply current (11) $V_{PWR} = 14 \ V^{(10)}$  | I <sub>pwr</sub>    | -      | 7.0     | _      | mA   |

#### Notes

- 10. Verified by design and characterization. Not tested in production.

- 11. No external devices connected to internal voltage regulators.

# DYNAMIC ELECTRICAL CHARACTERISTICS

# **Table 4. Dynamic Electrical Characteristics**

Characteristics noted under conditions 9.0 V  $\leq$  VPWR  $\leq$  18 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under normal conditions unless otherwise noted. Voltages are relative to GND unless otherwise noted.

| Characteristic                                              | Symbol              | Min | Тур | Max | Unit |

|-------------------------------------------------------------|---------------------|-----|-----|-----|------|

| osc                                                         |                     |     | 1   | •   | •    |

| OSC Frequency Stability <sup>(12), (13)</sup>               | f <sub>STAB</sub>   | -   | _   | 10  | %    |

| OSC Center Frequency                                        | f <sub>OSC</sub>    |     |     |     | kHz  |

| $R_OSC = 39 \text{ k}\Omega$                                |                     | _   | 120 | _   |      |

| Harmonic Content (12)                                       | OSCH <sub>ARM</sub> |     |     |     | dB   |

| 2nd through 4th Harmonic Level                              |                     | _   | _   | -20 |      |

| 5th and Higher                                              |                     | _   | _   | -60 |      |

| Shield Driver                                               |                     |     |     |     |      |

| Shield Driver Maximum Harmonic level below Fundamental (12) | SD <sub>HARM</sub>  |     |     |     | dB   |

| 10 pF ≤ C <sub>LOAD</sub> ≤ 500 pF                          |                     | -   | -20 | _   |      |

| Shield Driver Gain Bandwidth Product (12)                   | SD <sub>GBW</sub>   |     |     |     | MHz  |

| Measured at 120 kHz                                         |                     | _   | 4.5 | _   |      |

| POR                                                         |                     |     |     |     |      |

| POR Time-Out Period                                         | t <sub>PER</sub>    | 9.0 | _   | 50  | ms   |

| Watchdog                                                    |                     |     |     |     |      |

| Watchdog Time-Out Period                                    | t <sub>WDPER</sub>  | 50  | 68  | 250 | ms   |

| Watchdog Reset Hold Time                                    | t <sub>WDHLD</sub>  | 9.0 | _   | 50  | ms   |

| Lamp Driver                                                 |                     |     |     |     | •    |

| Short Circuit to Battery Survival Time                      | t <sub>SCB</sub>    | 3.0 | -   | _   | ms   |

### Notes

- 12. Verified by design and characterization. Not tested in production.

- 13. Does not include errors in external reference parts.

## **ELECTRODE SELECTION**

Table 5. Electrode Selection

| TERMINAL/SIGNAL   | D | С | В | Α |

|-------------------|---|---|---|---|

| Source (internal) | 0 | 0 | 0 | 0 |

| E1                | 0 | 0 | 0 | 1 |

| E2                | 0 | 0 | 1 | 0 |

| E3                | 0 | 0 | 1 | 1 |

| E4                | 0 | 1 | 0 | 0 |

| E5                | 0 | 1 | 0 | 1 |

| E6                | 0 | 1 | 1 | 0 |

| E7                | 0 | 1 | 1 | 1 |

Table 5. Electrode Selection (continued)

| TERMINAL/SIGNAL          | D | С | В | Α |

|--------------------------|---|---|---|---|

| E8                       | 1 | 0 | 0 | 0 |

| E9                       | 1 | 0 | 0 | 1 |

| REF_A                    | 1 | 0 | 1 | 0 |

| REF_B                    | 1 | 0 | 1 | 1 |

| Internal OSC             | 1 | 1 | 0 | 0 |

| Internal OSC after 22 kΩ | 1 | 1 | 0 | 1 |

| Internal Ground          | 1 | 1 | 1 | 0 |

| Reserved                 | 1 | 1 | 1 | 1 |

### **FUNCTIONAL DESCRIPTION**

#### **INTRODUCTION**

The MC33794 is intended for use in detecting objects using an electric field. The IC generates a low radio frequency sine wave. The frequency is set by an external resistor and is optimized for 120 kHz. The sine wave has very low harmonic content to reduce potential interference at higher harmonically related frequencies. The internal generator produces a nominal 5.0 V peak-to-peak output that is passed through an internal resistor of about 22 k $\Omega$ . An internal multiplexer routes the signal to one of 11 terminals under control of the ABCD input terminals. A receiver multiplexer simultaneously connected to the selected electrode routes its signal to a detector, which converts the sine wave to a DC level. This DC level is filtered by an external capacitor and is multiplied and offset to increase sensitivity. All of the unselected electrode outputs are grounded by the device. The current flowing between the selected electrode and the other grounded electrodes plus other grounded objects around the electrode causes a

voltage drop across the internal resistance. Objects brought into or out of the electric field change the current and resulting voltage at the IC terminal, which in turn reduces the voltage at LP CAP and LEVEL.

A shield driver is included to minimize the effect of capacitance caused by using coaxial cables to connect to remote electrodes. By driving the coax shield with this signal, the shield voltage follows that of the center conductor, significantly reducing the effective capacitance of the coax and maintaining sensitivity to the capacitance at the electrode.

The MC33794 is made to work with and support a microcontroller. It provides two voltage regulators, a Power-ON-reset/out-of-range voltage detector, watchdog circuit, lamp driver and sense circuit, and a physical layer ISO-9141 communications interface.

#### **BLOCK DIAGRAM COMPONENTS**

Refer to Figure 1, MC33794 Internal Block Diagram, page 2, for a graphic representation of the block diagram information in this section.

#### osc

This section generates a high purity sine wave. The center frequency is controlled by a resistor attached to R\_OSC. The normal operating frequency is around 120 kHz. A square wave version of the frequency output is available at CLK. Timing for the Power-ON Reset and watchdog (POR/WD) circuit are derived from this oscillator's frequency.

#### **MUX OUT**

This circuit directs the output of the sine wave to one of nine possible electrode outputs or two reference terminals. All unused terminals are automatically grounded (except the two reference terminals). The selected output is controlled by the ABCD inputs.

### **ELECTRODES E1-E9**

These are the electrode terminals. They are connected either directly or through coaxial cables to the electrodes for measurements. Every electrode has a 2.8K ( $\pm$  20%) resistor in series with the external pad and the internal electronics. Only one of these electrodes can be selected at a time for capacitance measurement. All of the other unselected electrodes are switched to ground by an internal switch that has an internal on-resistance of approximately  $700~\Omega.$  The signal at the selected electrode terminal is routed to the shield driver amplifier by an internal switch. All of the coaxial cable shields should be isolated from ground and connected SHIELD.

# **REF\_A & REF\_B ELECTRODES**

These terminals can be individually selected like E1 through E9. Unlike E1 through E9, these terminals are not grounded when not selected. Both terminals have a 2.8K (± 20%) resistor in series with the external pad and the internal electronics. The purpose of these terminals is to allow known capacitors to be measured. By using capacitors at the low and high end of the expected range, absolute values for the capacitance on the electrodes can be computed. These terminals can be used for electrodes E10 and E11 with the only difference is that these two electrodes will not be grounded when not selected.

### **SHIELD DRIVE**

This circuit provides a buffered version of the returned AC signal from the electrode. Since it nearly has the same amplitude and phase as the electrode signal, there is little or no potential difference between the two signals thereby cancelling out any electric field. In effect, the shield drives and isolates the electrode signal from external virtual grounds. A common application is to connect the Shield Drive to the shield of a coax cable used to connect an electrode to the corresponding electrode terminal. Another typical use is to drive a ground plane that is used behind an array of touch sensor electrodes in order to cancel out any virtual grounds that could attenuate the AC signal.

# **MUX IN**

This circuit connects the selected electrode, reference, or one of two internal nodes to an amplifier/detector. The selection is controlled by the ABCD inputs and follows the driven electrode/reference when one is selected.

#### **RECT**

The rectifier circuit detects the level from MUX IN by offsetting the midpoint of the sine wave to zero volts and inverting the waveform when it is below the midpoint. It is important to avoid DC loading of the signal, which would cause a shift in the midpoint voltage of the signal.

#### **LPF**

The rectified sine wave is filtered by a low pass function formed by an internal resistance and an external capacitance attached to LP\_CAP. The nominal value of the internal resistance is  $50~\mathrm{k}\Omega$ . The value of the external capacitor is selected to provide filtering of noise while still allowing the desired settling time for the detector output. A 10 nF capacitor would allow 99% settling in less than 5.0 ms. In practice, it is recommended you wait at least 1.5 ms after selecting an electrode before reading LEVEL.

#### **GAIN AND OFFSET**

This circuit multiplies the detected and filtered signal by a gain and offsets the result by a DC level. This results in an output range that covers 1.0 V to 4.0 V for capacitive loading of the field in the range of 10 pF to 100 pF. This allows higher sensitivity for a digital-to-analog converter with a 0 V-to-5.0 V input range.

#### **ATTN**

This circuit passes the undetected signal to SIGNAL for external use.

### SHIELD\_EN

A logic low on this input disables the shield drive. The purpose of doing this is to be able to detect that the shield signal is not working or the connection to the coax shields is broken. If either of these conditions exists, there will be little or no change in the capacitance measured when the SHIELD\_EN is changed. If the SHIELD output is working and properly connected, the capacitance of the coax will not be cancelled when this terminal is asserted and the measured capacitance will appear to change by approximately the capacitance between the center conductor and the shield in the coax.

#### **LAMP CKT**

This section controls the operation of the LAMP\_OUT terminal. When LAMP\_CTRL is asserted, LAMP\_OUT is pulled to LAMP\_GND. If one side of an indicator lamp or LED

(with appropriate current setting resistor) is connected to a positive voltage source and the other is connected to LAMP\_OUT, and LAMP\_GND is connected to ground, the lamp will light. This circuit provides current limiting to prevent damage to itself in the case of a shorted lamp or during a high-surge condition typical of an incandescent lamp burnout.

LAMP\_GND should always be connected to ground even if the lamp circuit is not used.

#### ISO-9141

This circuit connects to an ISO-9141 bus to allow remote communications. ISO\_IN is data from the bus to the MCU and ISO\_OUT is data to drive onto the bus from the MCU.

#### POR/WD

This circuit is a combined Power-ON Reset and watchdog timer. The  $\overline{RST}$  output is held low until a certain amount of time after the  $V_{CC}$  REG output ( $V_{CC}$ ) has remained above a minimum operating threshold. If  $V_{CC}$  falls below the level at any time,  $\overline{RST}$  is pulled low again and held until the required time after  $V_{CC}$  has returned high. An over voltage circuit is also included, which will force a reset if  $V_{CC}$  rises above a maximum voltage. The watchdog function also can force  $\overline{RST}$  low if too long an interval is allowed to pass between positive transitions on WD IN.

### INTERNAL V<sub>CC</sub> REGULATOR

This circuit converts an unregulated voltage from VIN to a regulated 5.0 V source, which is used internally and available for other components requiring a regulated voltage source.

# INTERNAL V<sub>DD</sub> REGULATOR

This is a regulator for analog devices that require more than 5.0 V. This is used by the device and some current is available to operate op-amps and other devices. By having this higher voltage available, some applications can avoid the need for a rail-to-rail output amplifier and still achieve the 0 V-to-5.0 V output for a digital-to-analog converter input.  $V_{\rm DD\_MON}$  is a divided output from internal  $V_{\rm DD}$  REG, which allows a 0.0 V-to-5.0 V ADC to measure  $V_{\rm DD}$ . Normal value for  $V_{\rm DD}$  is 8.5 Volts.

#### **CONTROL LOGIC**

This contains the logic that decodes and controls the MUXes and some of the test modes

### **APPLICATION INFORMATION**

The MC33794 is intended to be used where an object's size and proximity are to be determined. This is done by placing electrodes in the area where the object will be. The proximity of an object to an electrode can be determined by the increase in effective capacitance as the object gets closer to the electrode and modifies the electric field between the

electrode and surrounding electrically common objects. The shape and size of an object can be determined by using multiple electrodes over an area and observing the capacitance change on each of the electrodes. Those that don't change have nothing near them, and those that do change have part of the object near them.

A "capacitor" can be formed between the driving electrode and the object, each forming a "plate" that holds the electric charge. Capacitance is directly proportional to the area of the electrode plates. Doubling the area doubles the capacitance. Capacitance is also directly proportional to the *dielectric constant* of the material between the plates. Air typically has a dielectric constant of 1 (unity) whereas water can have a dielectric constant of 80 (which means the capacitance is roughly 80 times larger). Plastics and glass that are commonly used in touch panel applications have dielectric constants greater than unity. A third consideration is that capacitance is *inversely proportional* to the distance between the plates. Doubling the distance between the two plates will reduce capacitance by four. This property can be exploited in cases where small distances need to be measured.

From the above, it can be seen that increased detection sensitivity is a function of the plate size, the dielectric constant of the material between the plates, and the distance between them.

The voltage measured at LEVEL is an inverse function of the capacitance between the electrode being measured and the surrounding electrodes and other objects in the electric field surrounding the electrode. Increasing capacitance results in decreasing voltage. The value of series resistance (22 k $\Omega$ ) was chosen to provide a nearly linear relationship at 120 kHz over a range of 10 pF to 100 pF.

The measured value may change with any change in frequency, series resistance, driving voltage, the dielectric constant of the capacitor, or detector sensitivity. These can change with temperature and time. There are several ways to compensate for these changes. One method uses the REF\_A and REF\_B capacitors. Another method may use long term averages to set a baseline value.

Using REF\_A and REF\_B, a typical measurement algorithm would start by measuring the voltage for two known value capacitors (attached to REF\_A and REF\_B). The value of these capacitors would be chosen to be near the minimum and maximum values of capacitance expected to be seen at the electrodes. These reference voltages and the known capacitance values are then used with the electrode

measurement voltage to determine the capacitance seen by the electrode. This method can be used to detect short- and long-term changes due to objects in the electric field and significantly reduce the effect of temperature-and timeinduced changes.

Another approach is to run long term averaging of the electrode values. Long term, in this case, may mean several seconds. These long term averages are then used as a set point so that short term changes in the field intensity can be reliably determined. This is typically the method used for touch panel applications.

The MC33794 does not contain an ADC. It is intended to be used with an MCU that contains one. Offset and gain have been added to the MC33794 to maximize the sensitivity over the range of 0 pF to 100 pF. An 8-bit ADC can resolve around 0.4 pF of change and a 10-bit converter around 0.1 pF. Higher resolution results in more distant detection of smaller objects. Due to the relatively slow data access requirements (approximately 2 ms per electrode), digital over-sampling techniques can be used to extend the resolution of 8- or 10-bit converters by 2 or 3 bits.

DC loading on the electrodes should be avoided. A typical situation where this might occur is if moisture gets in direct contact between electrodes, or between an electrode and ground or shield drive. The signal is generated with a DC offset that is more than half the peak-to-peak level. This keeps the signal positive above ground at all times. The detector uses this voltage level as the midpoint for detection. All signals below this level are inverted and added to all signals above this level. Loading of the DC level will cause some of the positive half of the signal to be inverted and added and will change the measurement.

If it is not possible to assure that the electrodes will always have a high DC resistance to ground source, a series capacitor of about 10 nF should be connected between the IC electrode terminals and the electrodes. This capacitor will block DC bias voltages to the detector. Note that it is also advisable to add a DC blocking capacitor in series with the Shield Driver output as well.

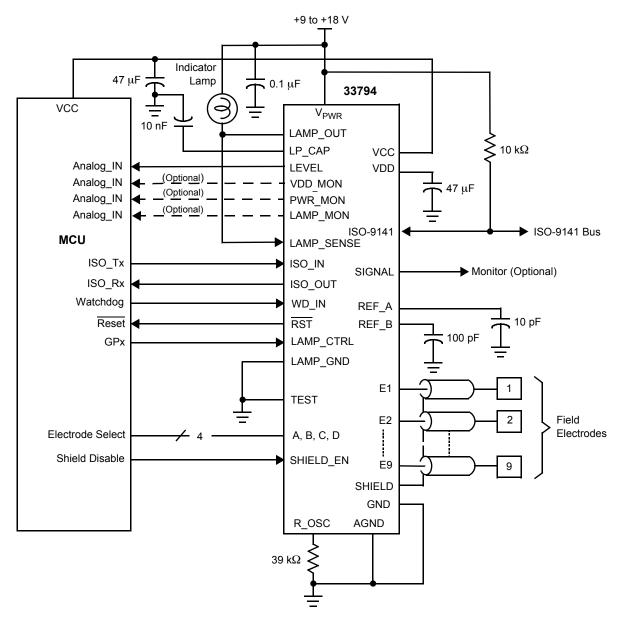

### **EXAMPLE APPLICATION DIAGRAM**

Figure 3. Example Application Diagram

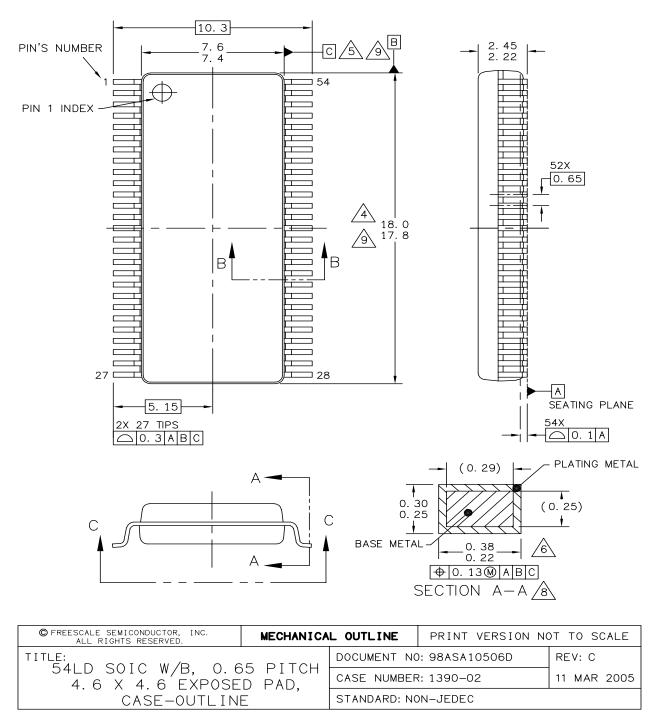

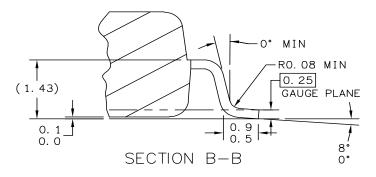

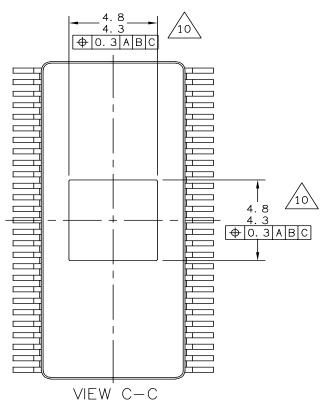

### **PACKAGE DIMENSIONS**

PAGE 1 OF 3

EK SUFFIX CASE 1390-02 ISSUE C

# **PACKAGE DIMENSIONS**

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE    | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE:                                               | SE DITOU  | DOCUMENT NO  | ): 98ASA10506D   | REV: C      |

| 54LD SOIC W/B, 0.65 PITCH<br>4.6 X 4.6 EXPOSED PAD,  |           | CASE NUMBER  | R: 1390–02       | 11 MAR 2005 |

| CASE-OUTLIN                                          | ·         | STANDARD: NO | N-JEDEC          |             |

PAGE 2 OF 3

EK SUFFIX CASE 1390-02 ISSUE C

#### **PACKAGE DIMENSIONS**

#### NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. DATUMS B AND C TO BE DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

- THIS DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURRS. MOLD FLASH, PROTRUSION OR GATE BURRS SHALL NOT EXCEED 0.15 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

- THIS DIMENSION DOES NOT INCLUDE INTER-LEAD FLASH OR PROTRUSIONS. INTER-LEAD FLASH AND PROTRUSIONS SHALL NOT EXCEED 0.25 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

- THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.46 mm. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD SHALL NOT BE LESS THAN 0.07 mm.

- EXACT SHAPE OF EACH CORNER IS OPTIONAL.

THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.1 mm AND

- 0.3 mm from the lead tip.

PAGE 1 OF 3

THE PACKAGE TOP MAY BE SMALLER THAN THE PACKAGE BOTTOM. THIS DIMENSION IS DETERMINED AT THE OUTERMOST EXTREMES OF THE PLASTIC BODY EXCLUSIVE OF MOLD FLASH, TIE BAR BURRS, GATE BURRS AND INTER—LEAD FLASH, BUT INCLUDING ANY MISMATCH BETWEEN THE TOP AND BOTTOM OF THE PLASTIC BODY.

- THESE DIMENSIONS DEFINE THE PRIMARY SOLDERABLE SURFACE AREA.

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.                          | MECHANICAL OUTLINE |                          | PRINT VERSION NOT TO SCALE |             |

|-------------------------------------------------------------------------------|--------------------|--------------------------|----------------------------|-------------|

| TITLE:<br>54LD SOIC W/B, 0.65 PITCH<br>4.6 X 4.6 EXPOSED PAD,<br>CASE-OUTLINE |                    | DOCUMENT NO: 98ASA10506D |                            | REV: C      |

|                                                                               |                    | CASE NUMBER: 1390-02     |                            | 11 MAR 2005 |

|                                                                               |                    | STANDARD: NON-JEDEC      |                            |             |

PAGE 3 OF 3

EK SUFFIX CASE 1390-02 ISSUE C

### How to Reach Us:

#### Home Page:

www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of. directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale ™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2006. All rights reserved.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.