## SERIALLY PROGRAMMABLE CLOCK SOURCE

## **Description**

The ICS307-01 and ICS307-02 are versatile serially programmable clock sources which take up very little board space. They can generate any frequency from 6 to 200 MHz and have a second configurable output. The outputs can be reprogrammed on the fly and will lock to a new frequency in 10 ms or less. Smooth transitions (in which the clock duty cycle remains near 50%) are guaranteed if the output divider is not changed.

The devices includes a PDTS pin which tri-states the output clocks and powers down the entire chip.

# The ICS307-02 features a default clock output at start-up and is recommended for all new designs.

This product is intended for clock generation. It has low output jitter (variation in the output period), but input to output skew and jitter are not defined nor guaranteed. For applications which require defined input to output skew, use the ICS527-01.

#### **Features**

- Packaged in 16 pin (150 mil wide) SOIC

- Highly accurate frequency generation

- Serially programmable: user determines the output frequency via a 3 wire interface

- Eliminates need for custom quartz

- Input crystal frequency of 5 27 MHz

- Output clock frequencies up to 200 MHz

- Power down tri-state mode

- · Very low jitter

- Operating voltage of 3.3 V or 5 V

- 25 mA drive capability at TTL levels

- Industrial temperature version available

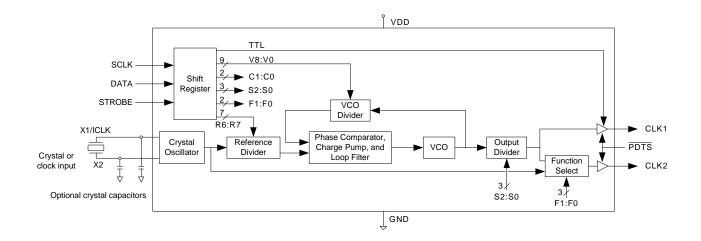

## **Block Diagram**

## **Pin Assignment**

|         |   |    | , |        |

|---------|---|----|---|--------|

| X1/ICLK | 1 | 16 |   | X2     |

| NC      | 2 | 15 |   | NC     |

| VDD     | 3 | 14 |   | NC     |

| NC      | 4 | 13 |   | PDTS   |

| GND     | 5 | 12 |   | DATA   |

| CLK2    | 6 | 11 |   | CLK1   |

| NC      | 7 | 10 |   | NC     |

| SCLK    | 8 | 9  |   | STROBE |

|         |   |    |   |        |

16 pin (150 mil) SOIC

## **Pin Descriptions**

| Pin<br>Number | Pin<br>Name | Pin<br>Type | Pin Description                                                                               |

|---------------|-------------|-------------|-----------------------------------------------------------------------------------------------|

| 1             | X1/ICLK     | XI          | Crystal connection (REF frequency). Connect to a parallel resonant crystal or an input clock. |

| 2             | NC          | -           | No connect. Do not connect anything to this pin.                                              |

| 3             | VDD         | Power       | Connect to 3.3V or 5V.                                                                        |

| 4             | NC          | -           | No connect. Do not connect anything to this pin.                                              |

| 5             | GND         | Power       | Connect to ground.                                                                            |

| 6             | CLK2        | Output      | Output clock 2, determined by F0 - F1. Can be reference, REF/2, CLK1/2, or off.               |

| 7             | NC          | -           | No connect. Do not connect anything to this pin.                                              |

| 8             | SCLK        | Input       | Serial clock. See timing diagram.                                                             |

| 9             | STROBE      | Input       | Strobe to load data. See timing diagram.                                                      |

| 10            | NC          | -           | No connect. Do not connect anything to this pin.                                              |

| 11            | CLK1        | Output      | Output clock 1, determined by R0 - R6, V0 - V8, S0 - S2, and input frequency.                 |

| 12            | DATA        | Input       | Data input. Serial input for three words which set the output clock(s).                       |

| 13            | PDTS        | Input       | Powers down entire chip, tri states CLK1 and CLK2 outputs when low. Internal pull-up.         |

| 14            | NC          | -           | No connect. Do not connect anything to this pin.                                              |

| 15            | NC          | -           | No connect. Do not connect anything to this pin.                                              |

| 16            | X2          | ХО          | Input crystal connection. Connect to a crystal or leave unconnected for clock input.          |

## **Determining the Output Frequency**

On power-up, the ICS307-01 on-chip registers can have random values so almost any frequency may be output from the part. CLK1 will always have some clock signal present, but CLK2 could possibly be OFF (low).

The ICS307-02 on-chip registers are initially configured to provide a x1 output clock on both the CLK1 and CLK2 outputs. The output frequency will be the same as the input clock or crystal. This is useful if the ICS307 will provide the initial system clock as power-up. Since this feature is an advantage in most systems, the ICS307-02 is recommended for new designs.

With programming, the user has full control in changing the desired output frequency to any value over the range shown in Table 1 on page 4. The output of the ICS307 can be determined by the following equation:

$$CLK1Frequency = InputFrequency \cdot 2 \cdot \frac{VDW + 8}{(RDW + 2) \cdot OD}$$

Where:

VCO Divider Word (VDW) = 4 to 511 (0, 1, 2, 3) are not permitted)

Reference Divider Word (RDW) = 1 to 127 (0 is not permitted)

Output Divider = values on page 4

Also, the following operating ranges should be observed. For the commercial temperature range:

$$55MHz < InputFrequency \cdot 2 \cdot \frac{VDW + 8}{RDW + 2} < 400MHz$$

And for the industrial temperature range:

$$60kHz < \frac{Input Frequency}{RDW + 2} < 360MHz$$

To determine the best combination of VCO, reference, and output dividers, see the online calculator at http://www.icst.com/products/ics307inputForm.html or contact ICS by sending an e-mail to ics-mk@icst.com with the desired input crystal or clock and the desired output frequency.

## **Setting the Device Characteristics**

The tables below show the settings which can be configured, as well as the VCO and Reference dividers.

**Table 1. Output Divide and Maximum Output Frequency**

| <b>S2</b> | <b>S</b> 1 | S0 | CLK1 Output<br>Divide | Max.<br>Frequency<br>5V or 3.3V<br>(MHz) | Max.<br>Frequency<br>Industrial<br>Temp. Version |

|-----------|------------|----|-----------------------|------------------------------------------|--------------------------------------------------|

| 0         | 0          | 0  | 10                    | 40                                       | 36                                               |

| 0         | 0          | 1  | 2                     | 200                                      | 180                                              |

| 0         | 1          | 0  | 8                     | 50                                       | 45                                               |

| 0         | 1          | 1  | 4                     | 100                                      | 90                                               |

| 1         | 0          | 0  | 5                     | 80                                       | 72                                               |

| 1         | 0          | 1  | 7                     | 55                                       | 50                                               |

| 1         | 1          | 0  | 3                     | 135                                      | 120                                              |

| 1         | 1          | 1  | 6                     | 67                                       | 60                                               |

#### Table 2. CLK2 Output

| S2 | S1 | CLK2                 |

|----|----|----------------------|

| 0  | 0  | REF                  |

| 0  | 1  | F <sub>REF</sub> /2  |

| 1  | 0  | OFF (Low)            |

| 1  | 1  | F <sub>CLK1</sub> /2 |

#### **Table 3. Output Duty Cycle Configuration**

| TTL | Duty Cycle Measured At | Recommended VDD |

|-----|------------------------|-----------------|

| 0   | 1.4 V                  | 5 V             |

| 1   | VDD/2                  | 3.3 V           |

Note: The TTL bit optimizes the duty cycle at different VDD. When VDD is 5V, set to 0 for a near-50% duty cycle with TTL levels. When VDD is 3.3V, set this bit to 1 so the 50% duty cycle is achieved at VDD/2.

**Table 4. Crystal Load Capacitance**

| C1 | C0 | VDD = 5V       | VDD = 3.3V      |

|----|----|----------------|-----------------|

| 0  | 0  | 22.3 - 0.083 f | 22.1 - 0.0094 f |

| 0  | 1  | 23.1 - 0.093 f | 22.9 - 0.108 f  |

| 1  | 0  | 23.7 - 0.106 f | 23.5 - 0.120 f  |

| 1  | 1  | 24.4 - 0.120 f | 24.2 - 0.135 f  |

Note: f is the crystal frequency in MHz between 10 and 27 MHz. Effective load capacitance will be higher for crystal frequencies lower than 10 Mhz. If a clock input is used, set C1 = 0 and C0 = 0.

## **Bypass Mode**

If R6:0 is programmed to 0000000, the PLL is powered down and bypassed; the reference frequency will come from both CLK1 and CLK2. It is possible to generate gltiches going into and out of this mode.

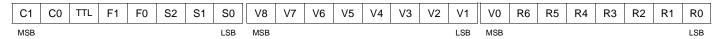

## Configuring the ICS307

The ICS307 can be programmed to set the output functions and frequencies. The three data bytes are written in DATA pin in this order:

C1 is loaded into the port first and R0 last.

R6:R0 Reference Divder Word (RDW)

V8:V0 VCO Divider Word (VDW)

S2:S0 Output Divider Select (OD)

F1:F0 Function of CLK2 Output

TTL Duty Cycle Settings

C1:C0 Internal Load Capacitance for Crystal

The ICS307 can be reprogrammed at any time during operation. If R6:0, V8:0, TTL, or C1:0 are changed, the frequency will transition smoothly to the new value over about 1 ms, without glitches or short cycles. If S2:0 is

changed, it is possible to generate glitches on CLK1 and also on CLK2 for F1:0 = 1 1.

Changing F1:0 will generate glitches on CLK2.

### Power up default values for ICS307-02

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

The input frequency will come from both outputs.

#### A warning about using the default configuration with input frequencies lower than 13.75 MHz

The VCO will run only as low as its minimum frequency, which is guaranteed to be no more than 55 MHz. So, in the powerup default condition, the PLL is guaranteed to lock to the input frequency down to 55/4 = 13.75 MHz. However, the part will typically run much slower. The typical minimum VCO frequency is about 30 - 40 MHz, depending on voltage, temperature, and lot variation; so in the powerup default setting, the CLK2 output will be a minimum of 7.5 - 10 MHz even if the input frequency is lower than that. The output is not locked to the reference input and so the frequency is not very stable and the phase noise is higher. In this condition, the CLK2 output will accurately provide the reference frequency down to 0 Hz because this signal path bypasses the PLL.

## **Programming Example**

To generate 66.66 MHz from a 14.31818 MHz input, the RDW should be 59, the VDW should be 276, and the Output Divide is 2. Selecting the minimum internal load capacitance, CMOS duty cycle, and CLK2 to be OFF means that the following three bytes are sent to the ICS307:

00110001 10001010 00111011 Byte 1 Byte 2 Byte 3

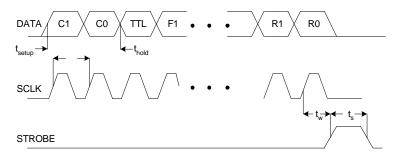

As show in Figure 2, after these 24 bits are clocked into the ICS307, taking STROBE high will send this data to the internal latch and the CLK output will lock within 10 ms.

**Note**: If STROBE is in the high state and SCLK is pulsed, DATA is clocked directly to the internal latch and the output conditions will change accordingly. Although this will not damage the ICS307, it is recommended that STROBE be kept low while DATA is being clocked into the ICS307 in order to avoid unintended changes on the output clocks.

## **AC Parameters for Writing to the ICS307**

| Parameter          | Condition            | Min. | Max. | Units |

|--------------------|----------------------|------|------|-------|

| t <sub>SETUP</sub> | Setup time           | 10   |      | ns    |

| t <sub>HOLD</sub>  | Hold time after SCLK | 10   |      | ns    |

| t <sub>W</sub>     | Data wait time       | 10   |      | ns    |

| t <sub>S</sub>     | Strobe pulse width   | 40   |      | ns    |

|                    | SCLK Frequency       |      | 50   | MHz   |

Figure 2. Timing Diagram for Programming the ICS307

## **External Components/Crystal Selection**

The ICS307 requires a  $0.01\mu F$  decoupling capacitor to be connected between VDD and GND. It must be connected close to the ICS307 to minimize lead inductance. A  $33\Omega$  terminating resistor can be used in series with CLK1 and CLK2 outputs. A parallel resonant, fundamental mode crystal with a load (correlation) capacitance of C should be used, where C is the value calculated from Table 4. For crystals with a specified load capacitance greater than C, additional crystal capacitors may be connected from each of the pins X1 and X2 to ground as shown in the Block Diagram on page 1. The value (in pF) of these crystal caps should be =  $(C_L-C)^*2$ , where  $C_L$  is the crystal load capacitance in pF and C is the capacitance value from Table 4. These external capacitors are only required for applications where the exact frequency is crtical. For a clock input, connect to X1 and leave X2 unconnected (no capacitors on either pin).

### **Absolute Maximum Ratings**

Stresses above the ratings listed below can cause permanent damage to the ICS307. These ratings, which are standard values for ICS commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| Item                                      | Rating            |

|-------------------------------------------|-------------------|

| Supply Voltage, VDD                       | 7V                |

| All Inputs and Outputs                    | -0.5V to VDD+0.5V |

| Ambient Operating Temperature             | 0 to +70°C        |

| Ambient Operating Temperature, Industrial | -40 to +85°C      |

| Storage Temperature                       | -65 to +150°C     |

| Soldering Temperature                     | 260°C             |

## **Recommended Operation Conditions**

| Parameter                                         | Min. | Тур. | Max. | Units |

|---------------------------------------------------|------|------|------|-------|

| Ambient Operating Temperature                     | 0    |      | +70  | °C    |

| Power Supply Voltage (measured in respect to GND) | +3.0 |      | +5.5 | V     |

MDS 307 E 6 Revision 031003

### **DC Electrical Characteristics**

**VDD=3.3V** ±5%, Ambient temperature 0 to +70°C, unless stated otherwise

| Parameter                          | Symbol          | Conditions                             | Min.      | Тур.  | Max.      | Units |

|------------------------------------|-----------------|----------------------------------------|-----------|-------|-----------|-------|

| Operating Voltage                  | VDD             |                                        | 3.0       |       | 5.5       | V     |

| Input High Voltage                 | V <sub>IH</sub> | X1/ICLK only                           | (VDD/2)+1 | VDD/2 |           | V     |

| Input Low Voltage                  | $V_{IL}$        | X1/ICLK only                           |           | VDD/2 | (VDD/2)-1 | V     |

| Input High Voltage                 | $V_{IH}$        |                                        | 2         |       |           | V     |

| Input Low Voltage                  | V <sub>IL</sub> | PDTS on ICS307-01                      |           |       | 0.4       | V     |

|                                    |                 | All other inputs,<br>ICS307-01/02      |           |       | 0.8       | V     |

| Output High Voltage                | V <sub>OH</sub> | I <sub>OH</sub> = -25 mA               | 2.4       |       |           | V     |

| Output Low Voltage                 | V <sub>OL</sub> | I <sub>OL</sub> = 25 mA                |           |       | 0.4       | V     |

| Output High Voltage,<br>CMOS level | V <sub>OH</sub> | I <sub>OH</sub> = -4 mA                | VDD-0.4   |       |           | V     |

| Operating Supply Current           | IDD             | 20 MHz crystal<br>No load, 100 MHz out |           | 26    |           | mA    |

|                                    |                 | 100 MHz out, 3.3V                      |           | 13    |           | mA    |

| Short Circuit Current              |                 | CLK outputs                            |           | ±70   |           | mA    |

| Input Capacitance                  | C <sub>IN</sub> |                                        |           | 4     |           | pF    |

| On-Chip Pullup Resistor            | R <sub>PU</sub> | Pin 13                                 |           | 270   |           | kΩ    |

## **AC Electrical Characteristics**

**VDD = 3.3V ±5%**, Ambient Temperature 0 to +70° C, unless stated otherwise

| Parameter                      | Symbol          | Conditions           | Min. | Тур.  | Max. | Units |

|--------------------------------|-----------------|----------------------|------|-------|------|-------|

| Input Frequency                | F <sub>IN</sub> | Fundamental crystal  | 5    |       | 27   | MHz   |

|                                |                 | Clock                | 2    |       | 50   | MHz   |

| Output Frequency (see Table 1) |                 |                      | 6    |       | 200  | MHz   |

|                                |                 | I-temp version       | 6    |       | 180  | MHz   |

| Output Clock Rise Time         | t <sub>OR</sub> | 0.8 to 2.0 V, Note 1 |      | 1     |      | ns    |

| Output Clock Fall Time         | t <sub>OF</sub> | 2.0 to 8.0 V, Note 1 |      | 1     |      | ns    |

| Output Clock Duty Cycle        |                 | even output divides  | 45   | 49-51 | 55   | %     |

|                                |                 | odd output divides   | 40   |       | 60   | %     |

| Parameter                     | Symbol          | Conditions                     | Min. | Тур. | Max. | Units |

|-------------------------------|-----------------|--------------------------------|------|------|------|-------|

| Power-up time                 |                 | STROBE goes high until CLK out |      | 3    | 10   | ms    |

| One Sigma Clock Period Jitter |                 |                                |      | 50   |      | ps    |

| Maximum Absolute Jitter       | t <sub>ja</sub> | Deviation from mean            |      | ±120 |      | ps    |

Note 1: Measured with 15 pF load.

## **Thermal Characteristics**

| Parameter                              | Symbol            | Conditions     | Min. | Тур. | Max. | Units |

|----------------------------------------|-------------------|----------------|------|------|------|-------|

| Thermal Resistance Junction to Ambient | $\theta_{JA}$     | Still air      |      | 120  |      | °C/W  |

|                                        | $\theta_{JA}$     | 1 m/s air flow |      | 115  |      | °C/W  |

|                                        | $\theta_{JA}$     | 3 m/s air flow |      | 105  |      | °C/W  |

| Thermal Resistance Junction to Case    | $\theta_{\sf JC}$ |                |      | 58   |      | °C/W  |

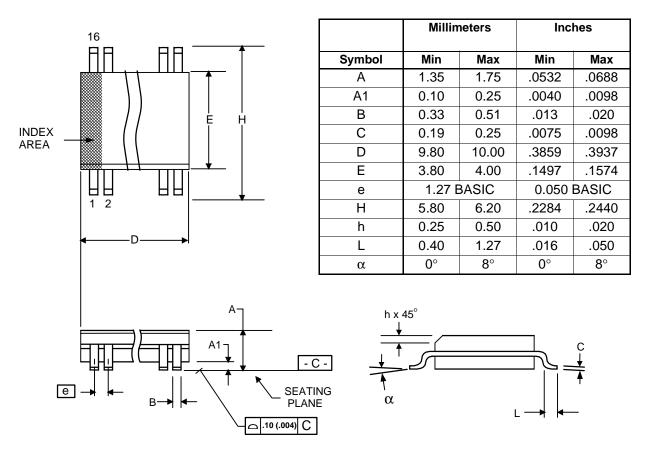

## Package Outline and Package Dimensions (16 pin SOIC, 150 Mil. Narrow Body)

Package dimensions are kept current with JEDEC Publication No. 95

## **Ordering Information**

| Part / Order Number | Marking     | Shipping packaging | Package     | Temperature   |

|---------------------|-------------|--------------------|-------------|---------------|

| ICS307M-01          | ICS307M-01  | Tubes              | 16 pin SOIC | 0 to +70° C   |

| ICS307M-01T         | ICS307M-01  | Tape and Reel      | 16 pin SOIC | 0 to +70° C   |

| ICS307M-01I         | ICS307M-01I | Tubes              | 16 pin SOIC | -40 to +85° C |

| ICS307M-01IT        | ICS307M-01I | Tape and Reel      | 16 pin SOIC | -40 to +85° C |

| ICS307M-02          | ICS307M-02  | Tubes              | 16 pin SOIC | 0 to +70° C   |

| ICS307M-02T         | ICS307M-02  | Tape and Reel      | 16 pin SOIC | 0 to +70° C   |

| ICS307M-02I         | ICS307M-02I | Tubes              | 16 pin SOIC | -40 to +85° C |

| ICS307M-02IT        | ICS307M-02I | Tape and Reel      | 16 pin SOIC | -40 to +85° C |

While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems (ICS) assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial applications. Any other applications such as those requiring extended temperature range, high reliability, or other extraordinary environmental requirements are not recommended without additional processing by ICS. ICS reserves the right to change any circuitry or specifications without notice. ICS does not authorize or warrant any ICS product for use in life support devices or critical medical instruments.