### 16-BIT CMOS CASCADABLE ALU

### FEATURES:

- High-performance 16-bit Arithmetic Logic Unit (ALU)

- 25ns to 55ns clocked ALU operations

- Ideal for radar, sonar or image processing applications

- 74S381 instruction set (8 functions)

- Replaces Gould S614381 or Logic Devices L4C381

- Cascadable with or without carry look-ahead

- Pipeline or flow-through modes

- Internal feedback path for accumulation

- Three-state outputs

- TTL-compatible

- Produced with advanced submicron CMOS technology

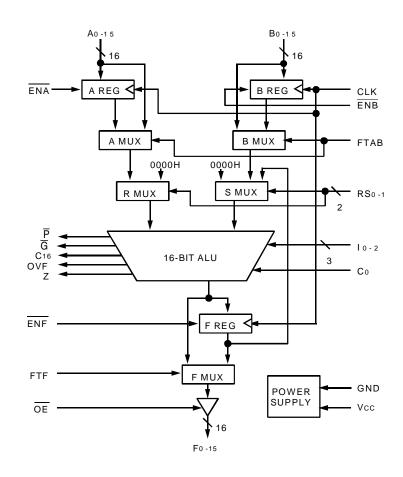

FUNCTIONAL BLOCK DIAGRAM

- Available in PLCC

- Speeds available: L/25/30/40/55

### **DESCRIPTION:**

The IDT7381 is a high-speed cascadable Arithmetic Logic Unit (ALU). These three-bus devices have two input registers, an ultra-fast 16-bit ALU and 16-bit output register. With IDT's high-performance CMOS technology, the IDT7381 can do arithmetic or logic operations in 25ns. The IDT7381 functionally replaces four 54/74S381 four-bit ALUs in a 68-pin package.

The two input operands, A and B, can be clocked or fed through for flexible pipelining. The F output can also be set into clocked or flow-through mode. An output enable is provided for three-state control of the output port on a bus.

The IDT7381 has three function pins to select 1 of 8 arithmetic or logic operations. The two R and S selection pins determine whether A, B, F or 0 are fed into the ALU. This ALU has carry-out, propagate and generate outputs for cascading using carry look-ahead.

### COMMERCIAL TEMPERATURE RANGE

### **APRIL 2001**

#### IDT7381 16-BITCASCADABLEALU

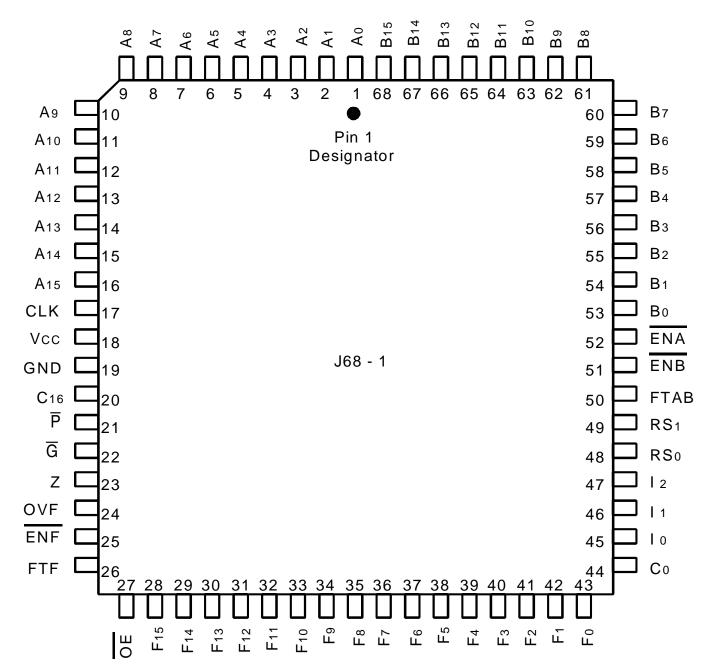

### **PIN CONFIGURATION**

PLCC TOP VIEW

# **PIN DESCRIPTION**

| Pin Name  | I/O | Description                                                                                                                              |

|-----------|-----|------------------------------------------------------------------------------------------------------------------------------------------|

| A0 - A15  | Ι   | Sixteen-bit data input port.                                                                                                             |

| B0 - B15  | Ι   | Sixteen-bit data input port.                                                                                                             |

| ĒNĀ       | Ι   | Register enable for the A input port; active low pin.                                                                                    |

| ĒNB       | Ι   | Register enable for the B input port; active low pin.                                                                                    |

| FTAB      | I   | Flow-through control pin. When this pin is high, both register A and B are transparent.                                                  |

| F0 – F15  | 0   | Sixteen-bit data output port.                                                                                                            |

| ENF       | I   | Register enable for the F output port; active low pin.                                                                                   |

| FTF       | Ι   | Flow-through control pin. When this pin is high, the F register is transparent.                                                          |

| CLK       | I   | Clock input.                                                                                                                             |

| ŌĒ        | I   | Output enable control pin. When this pin is high, the output port F is in a high impedance state. When low, the output port F is active. |

| Co        | I   | Carry input. This pin receives arithmetic carries from less significant ALU components in a cascade configuration.                       |

| C16       | 0   | Carry output. This pin produces arithmetic carries to more significant ALU components in a cascaded configuration.                       |

| OVF       | 0   | This pin indicates a two's complement arithmetic overflow, when high.                                                                    |

| Z         | 0   | This pin indicates a zero output result, when high.                                                                                      |

| RS0 – RS1 | I   | Two control pins used to select input operands for the R and S multiplexers.                                                             |

| lo - l2   |     | Three control pins to select the ALU function performed.                                                                                 |

| Р         | 0   | Indicates the carry propagate output state to the ALU.                                                                                   |

| G         | 0   | Indicates the carry generate output state to the ALU.                                                                                    |

| Vcc       |     | Power supply pin, 5V.                                                                                                                    |

| GND       |     | Ground pin, 0V.                                                                                                                          |

# **R AND S MUX TABLE**

| RS1 | RS0 | R Mux | S Mux |

|-----|-----|-------|-------|

| 0   | 0   | А     | F     |

| 0   | 1   | А     | 0     |

| 1   | 0   | 0     | В     |

| 1   | 1   | А     | В     |

# **ALU FUNCTION TABLE**

| l2 | <b>I</b> 1 | lo | Function                     |

|----|------------|----|------------------------------|

| 0  | 0          | 0  | F = 0                        |

| 0  | 0          | 1  | $F = \overline{R} + S + Co$  |

| 0  | 1          | 0  | $F = R + \overline{S} + C_0$ |

| 0  | 1          | 1  | F = R + S + Co               |

| 1  | 0          | 0  | F = R xor S                  |

| 1  | 0          | 1  | F = R or S                   |

| 1  | 1          | 0  | F = R and S                  |

| 1  | 1          | 1  | F = all 1's                  |

#### **COMMERCIAL TEMPERATURE RANGE**

# ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Symbol | Description                                | Max.                 | Unit |

|--------|--------------------------------------------|----------------------|------|

| Vterm  | Terminal Voltage with<br>Respect to Ground | -0.5 to<br>Vcc + 0.5 | V    |

| Vcc    | Power Supply Voltage                       | -0.5 to +7.0         | ۷    |

| Tstg   | Storage Temperature                        | –55 to +125          | °C   |

| Ιουτ   | DC Output Current                          | 50                   | mA   |

#### NOTE:

Stresses greater than those listed under ABSOLUTE MAXIMUM RAT-INGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Under no circumstances should an input of an I/O Pin be greater than Vcc + 0.5V.

# **DC ELECTRICAL CHARACTERISTICS**

#### Commercial: $TA = 0^{\circ}C$ to $+70^{\circ}C$ , $VCC = 5.0V \pm 5\%$

#### Test Conditions<sup>(1)</sup> Typ.(2) Symbol Parameter Unit Min. Max. Input HIGH Level Guaranteed Logic HIGH Level VIH 2 V VIL Input LOW Level Guaranteed Logic LOW Level \_ 0.8 V \_ Ιн Input HIGH Current VCC = Max., VIN = 2.7V 10 μA \_ \_ ١L Input LOW Current VCC = Max., VIN = 0.5V-10 μA \_ $los^{(3)}$ Short Circuit Current Vcc = Max., Vout = GND -20 -100 mΑ loz Off State (High Impedance) Vcc = Max. $V_0 = 0.5V$ \_ -0.1 -20 μA Output Current $V_{0} = 2.7V$ -0.1 20 \_ Vон **Output HIGH Voltage** VCC = Min. IOH = -4mA 2.4 V \_ VIN = VIH or VIL Vol Output LOW Voltage VCC = Min. ٧ IOL = 8mA0.5 VIN = VIH or VIL

#### NOTES:

1. For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.

2. Typical values are at Vcc = 5.0V, +25°C ambient and maximum loading.

3. Not more than one output should be shorted at one time. Duration of the short circuit test should not exceed one second.

### **CAPACITANCE** (TA = +25°C, f = 1.0MHz)

| Symbol | Parameter <sup>(1)</sup> | Conditions | Pkg. | Тур. | Unit |

|--------|--------------------------|------------|------|------|------|

| CIN    | Input Capacitance        | VIN = 0V   | PGA  | 10   | рF   |

|        |                          |            | PLCC | 5    |      |

| Соит   | Output Capacitance       | Vout = 0V  | PGA  | 12   | pF   |

|        |                          |            | PLCC | 7    |      |

NOTE:

1. This parameter is sampled at initial characterization and is not production tested.

# **POWER SUPPLY CHARACTERISTICS**

Commercial:  $TA = 0^{\circ}C$  to  $+70^{\circ}C$ ,  $VCC = 5.0V \pm 5\%$

| Symbol               | Parameter                                        | Test Condit                                                                                                                                                          | ions <sup>(1)</sup>                                                                                                             | Min. | Тур.(2) | Max. | Unit         |

|----------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------|---------|------|--------------|

| Icc                  | Quiescent Power Supply Current                   | Vcc = Max.<br>VIN =GND or Vcc                                                                                                                                        |                                                                                                                                 | _    | 2       | 6    | mA           |

| $\Delta ICC^{(3)}$   | Quiescent Power Supply Current<br>TTL Input HIGH | Vcc = Max.<br>VIN = 3.4V                                                                                                                                             |                                                                                                                                 | -    | 0.5     | 1    | mA/<br>input |

| ICCD <sup>(4)</sup>  | Dynamic Power Supply Current                     | Vcc = Max.<br>Outputs disabled<br>VIN = GND or Vcc<br>Mode: FTAB = FTF = 1                                                                                           | Outputs disabled<br>VIN = GND or Vcc                                                                                            |      | 15      | 48   | μΑ/<br>MHz   |

| ICCD1                | Dynamic Power Supply Current                     | Vcc = Max.<br>Outputs Disabled<br>All Data Inputs Disabled<br>fi = 10MHz, fcP = 10MHz<br>50% Duty Cycle<br>VIL = GND, VIH = Vcc<br>Mode: FTAB = FTF = 1              | Outputs Disabled<br>All Data Inputs Disabled<br>fi = 10MHz, fcp = 10MHz<br>50% Duty Cycle<br>VIL = GND, VIH = Vcc               |      | 20      | 33   | mA           |

| ICCD2 <sup>(6)</sup> | Dynamic Power Supply Current                     | Vcc = Max.<br>Outputs Enabled. (CL = 50pF)<br>All Data Inputs Switching<br>fi = 10MHz, fcP = 10MHz<br>50% Duty Cycle<br>VIL = GND, VIH = Vcc<br>Mode: FTAB = FTF = 1 | Outputs Enabled. (CL = 50pF)<br>All Data Inputs Sw itching<br>fi = 10MHz, fcP = 10MHz<br>50% Duty Cycle<br>VIL = GND, VIH = VCC |      | 40      | 60   | mA           |

| IC <sup>(7)</sup>    | Total Power Supply Current                       | Vcc = Max.<br>VIN = GND or Vcc                                                                                                                                       | Outputs Disabled                                                                                                                | _    | 22      | 39   | mA           |

|                      |                                                  | All Data Inputs Switching<br>fi = 10MHz, fcp = 10MHz<br>50% Duty Cycle                                                                                               | Outputs Enabled                                                                                                                 | _    | 42      | 76   | mA           |

#### NOTES:

- 1. For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.

- 2. Typical values are at Vcc = 5.0V, +25°C ambient.

- 3. Per TTL driven input (VIN = 3.4V); all other inputs at Vcc or GND.

- 4. This parameter is not directly testable, but is derived from IccD1 for use in Total Power Supply calculations.

- 5. Total power supply current is calculated as follows:

- IC = IQUIESCENT + INPUTS + IDYNAMIC

- $IC = ICC + \Delta ICC DHNT + ICCD (fCP + fiNi)$

- Icc = Quiescent Current

- $\Delta$ Icc = Power Supply Current for a TTL High Input (VIN = 3.4V)

- DH = Duty Cycle for TTL Inputs High

- NT = Number of TTL Inputs at DH

- Icco = Dynamic Current Caused by an Output Transition Pair (HLH or LHL)

- fcP = Clock Frequency for Register Devices (Zero for Non-Register Devices)

- fi = Input Frequency

- Ni = Number of Inputs at fi

- All currents are in milliamps and all frequencies are in megahertz.

- 6. This parameter is not production tested but is an indicator of the power dissipated with outputs loaded.

- 7. Values for these conditions are examples of the Ic formula in note 5 above. These are guaranteed but not tested.

# AC ELECTRICAL CHARACTERISTICS (Vcc = $5V \pm 5\%$ , TA = 0°C to +70°C)

| Maximum Combinational P | ropagation Delay | IS         |       |     |            |         |       |     |      |

|-------------------------|------------------|------------|-------|-----|------------|---------|-------|-----|------|

|                         |                  | IDT7381L25 |       |     | IDT7381L30 |         |       |     |      |

| From Input              | F0-15            | P, G, N    | Z,OVF | C16 | F0-15      | P, G, N | Z,OVF | C16 | Unit |

| FTAB = 0, FTF = 0       |                  |            |       |     |            |         |       |     |      |

| CLK                     | 13               | 22         | 26    | 22  | 20         | 28      | 30    | 28  | ns   |

| Co                      | _                | _          | 16    | 16  | —          | _       | 20    | 20  | ns   |

| I0-2, RS0, RS1          | _                | 22         | 22    | 22  | _          | 28      | 28    | 28  | ns   |

| FTAB = 0, FTF = 1       |                  |            |       |     |            |         |       |     |      |

| CLK                     | 27               | 22         | 26    | 22  | 33         | 28      | 30    | 28  | ns   |

| C0                      | 22               | _          | 16    | 16  | 28         | _       | 20    | 20  | ns   |

| I0-2, RS0, RS1          | 22               | 22         | 22    | 22  | 28         | 28      | 28    | 28  | ns   |

| FTAB = 1, FTF = 0       |                  |            |       |     |            |         |       |     |      |

| A0-A15, B0-B15          | _                | 18         | 25    | 22  | _          | 24      | 30    | 28  | ns   |

| CLK                     | 13               | _          | -     | _   | 19         | _       | _     | _   | ns   |

| Co                      | _                | _          | 16    | 16  | _          | _       | 20    | 20  | ns   |

| I0-2, RS0, RS1          | _                | 22         | 22    | 22  | _          | 28      | 28    | 28  | ns   |

| FTAB = 1, FTF = 1       |                  |            |       |     |            |         |       |     |      |

| A0-A15, B0-B15          | 26               | 18         | 25    | 22  | 32         | 24      | 30    | 28  | ns   |

| Co                      | 22               | _          | 16    | 16  | 28         | _       | 20    | 20  | ns   |

| I0-2, RS0, RS1          | 22               | 22         | 22    | 22  | 28         | 28      | 28    | 28  | ns   |

| Maximum Combinational P | ropagation Delay | /s         |       |     |            |         |       |     |      |

|-------------------------|------------------|------------|-------|-----|------------|---------|-------|-----|------|

|                         |                  | IDT7381L40 |       |     | IDT7381L55 |         |       |     |      |

| From Input              | F0-15            | P, G, N    | Z,OVF | C16 | F0-15      | P, G, N | Z,OVF | C16 | Unit |

| FTAB = 0, FTF = 0       |                  |            |       |     |            |         |       |     |      |

| CLK                     | 26               | 30         | 44    | 32  | 32         | 38      | 53    | 36  | ns   |

| C0                      | _                | _          | 28    | 20  | _          | —       | 34    | 22  | ns   |

| I0-2, RS0, RS1          | _                | 32         | 34    | 35  | _          | 42      | 42    | 42  | ns   |

| FTAB = 0, FTF = 1       |                  |            |       |     |            |         |       |     |      |

| CLK                     | 46               | 30         | 44    | 32  | 56         | 38      | 53    | 36  | ns   |

| Co                      | 30               | _          | 28    | 20  | 37         | —       | 34    | 22  | ns   |

| I0-2, RS0, RS1          | 40               | 32         | 34    | 35  | 55         | 42      | 42    | 42  | ns   |

| FTAB = 1, FTF = 0       |                  |            |       |     |            |         |       |     |      |

| A0-A15, B0-B15          | _                | 30         | 40    | 32  | _          | 36      | 46    | 37  | ns   |

| CLK                     | 26               | _          | —     | —   | 32         | —       | —     | —   | ns   |

| Co                      | -                | _          | 28    | 20  | -          | -       | 34    | 22  | ns   |

| I0-2, RS0, RS1          | —                | 32         | 34    | 35  | _          | 42      | 42    | 42  | ns   |

| FTAB = 1, FTF = 1       |                  |            |       |     |            |         |       |     |      |

| A0-A15, B0-B15          | 40               | 30         | 40    | 32  | 55         | 36      | 46    | 37  | ns   |

| Co                      | 30               | _          | 28    | 20  | 37         | _       | 34    | 22  | ns   |

| I0-2, RS0, RS1          | 40               | 32         | 34    | 35  | 55         | 42      | 42    | 42  | ns   |

#### NOTES:

1. Only for FTF = 0.

2. Minimum propagation delays are not production tested but guaranteed to be greater than or equal to 3ns.

# AC ELECTRICAL CHARACTERISTICS (Vcc = 5V ± 5%, TA = 0°C to +70°C) - (Cont'd.)

|                               | IDT73  | 81L25 | IDT73  | IDT7381L30 |        | IDT7381L40 |        | 81L55 |      |

|-------------------------------|--------|-------|--------|------------|--------|------------|--------|-------|------|

| Input                         | Set-up | Hold  | Set-up | Hold       | Set-up | Hold       | Set-up | Hold  | Unit |

| FTAB = 0, FTF = X             |        |       |        |            |        |            |        |       |      |

| A0-A15, B0-B15                | 6      | 0     | 6      | 0          | 6      | 0          | 8      | 0     | ns   |

| C <sub>0</sub> <sup>(1)</sup> | 16     | 0     | 16     | 0          | 16     | 0          | 21     | 0     | ns   |

| I0-2, RS0, RS1 <sup>(1)</sup> | 24     | 0     | 29     | 0          | 32     | 0          | 44     | 0     | ns   |

| ENA, ENB, ENF                 | 6      | 0     | 6      | 0          | 6      | 0          | 8      | 0     | ns   |

| FTAB = 1, FTF = 0             |        |       |        |            |        |            |        |       |      |

| A0-A15, B0-B15                | 16     | 0     | 25     | 0          | 28     | 0          | 35     | 0     | ns   |

| Co                            | 16     | 0     | 16     | 0          | 16     | 0          | 21     | 0     | ns   |

| I0-2, RS0, RS1                | 24     | 0     | 29     | 0          | 32     | 0          | 44     | 0     | ns   |

| ENF                           | 6      | 0     | 6      | 0          | 6      | 0          | 8      | 0     | ns   |

| Parameter       | IDT7381L25 | IDT7381L30 | IDT7381L40 | IDT7381L55 | Unit |

|-----------------|------------|------------|------------|------------|------|

| Clock LOW Time  | 6          | 8          | 10         | 14         | ns   |

| Clock HIGH Time | 6          | 8          | 10         | 14         | ns   |

| Clock Period    | 20         | 25         | 34         | 43         | ns   |

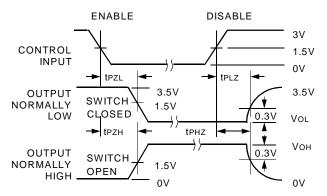

### Maximum Output Enable/Disable Times

| Parameter    | IDT7381L25 | IDT7381L30 | IDT7381L40 | IDT7381L55 | Unit |

|--------------|------------|------------|------------|------------|------|

| Enable Time  | 10         | 15         | 18         | 20         | ns   |

| Disable Time | 10         | 15         | 18         | 20         | ns   |

#### NOTES:

1. Only for FTF = 0.

2. Minimum propagation delays are not production tested but guaranteed to be greater than or equal to 3ns.

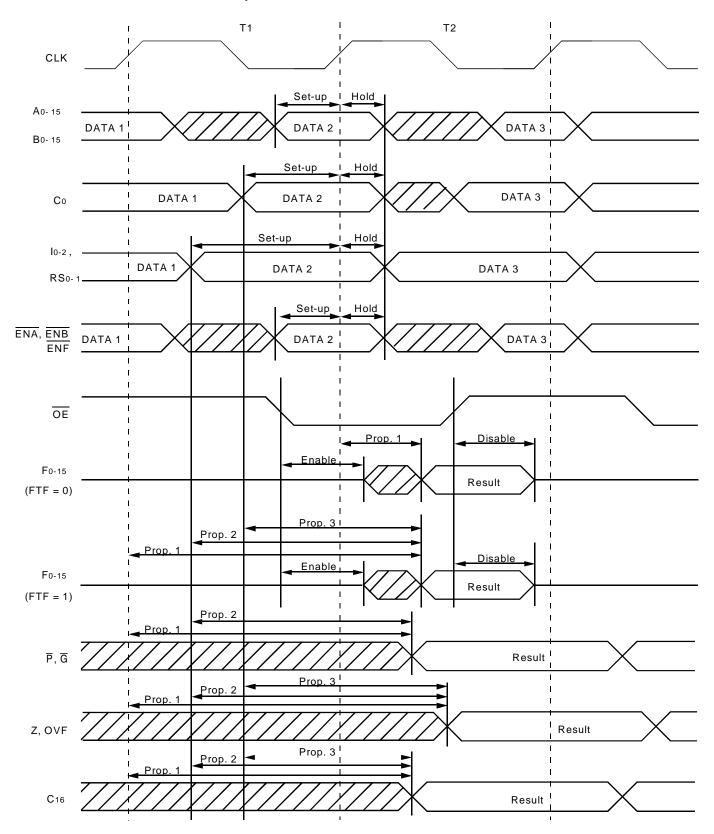

### WAVEFORMS FOR FTAB = 0, FTF = X

- Prop. 1: Propagation delay with respect to the CLK.

- Prop. 2: Propagation delay with respect to I0-2, RS0-2.

- Prop. 3: Propagation delay with respect to C0.

Prop. 4: Propagation delay with respect to A, B.

Prop. 4 Prop. 3

Enable

Prop. 31

Prop

Prop. 4 (for FTF = 1 only)

Prop. 4i(For FTF = 1 only)

Prop. 4 (For FTF = 1 only)

Prop. 2

Prop. 2

Prop. 2

Prop. 2

Disable

Result

Result

ı ı Result

I

Result

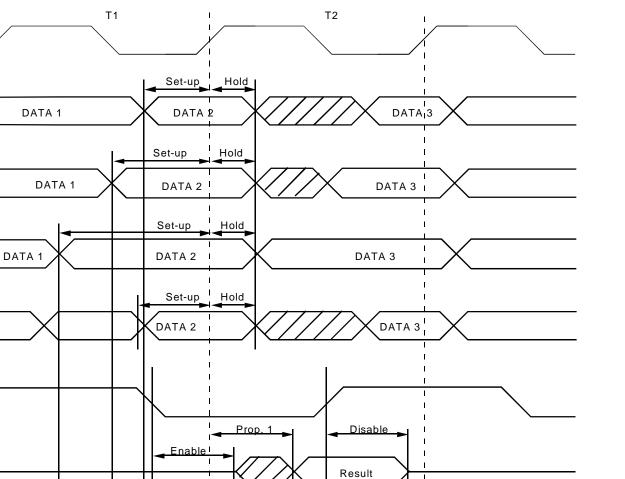

# WAVEFORMS FOR FTAB = 1, FTF = X

T

I.

CLK(FTF = 0)

A0- 15

B0- 15

C0

lo-2,

**RS**0-1

OE

F0-15

F0-15

P.G

Z. OVF

**C**16

(FTF = 1)

(FTF = 0)

ENF DATA 1

# **PROPAGATION DELAY CALCULATIONS FOR TWO IDT7381S**

|                                                                  | To                                                                                                                                                                                                                           | To Output                                                                                                                                                                                                                                 |                                                                                                                                                                                               |  |  |  |

|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| From Input                                                       | F0 – 15                                                                                                                                                                                                                      | Flags <sup>(1)</sup>                                                                                                                                                                                                                      | Relative to Clock (CLK)                                                                                                                                                                       |  |  |  |

| FTAB = 0, FTF = 0                                                |                                                                                                                                                                                                                              |                                                                                                                                                                                                                                           |                                                                                                                                                                                               |  |  |  |

| CLK<br>Co<br>I0 – 2, RS0 – 1<br>A0 – 15, B0 – 15<br>ENA, ENB,ENF | As in 16-bit case<br><br>                                                                                                                                                                                                    | $\begin{array}{l} (Clk \rightarrow C16) + (C0 \rightarrow flag) \\ (C0 \rightarrow C16) + (C0 \rightarrow flag) \\ (l0-2, RS0-1 \rightarrow C16) + (C0 \rightarrow flag) \\ \cdots \\ \cdots \end{array}$                                 | $\begin{array}{l} \dots \\ (C0 \rightarrow C16) + (C0 \text{ set-up time}) \\ (I0-2, RS0-1 \rightarrow C16) + (C0 \text{ set-up time}) \\ As in 16-bit case \\ As in 16-bit case \end{array}$ |  |  |  |

| FTAB = 0, FTF = 1                                                |                                                                                                                                                                                                                              |                                                                                                                                                                                                                                           |                                                                                                                                                                                               |  |  |  |

| CLK<br>Co<br>Io - 2, RSo - 1<br>Ao - 15, Bo - 15<br>ENA, ENB,ENF | $\begin{array}{l} (Clk \to C16) + (C0 \to F0-15) \\ (C_0 \to C16) + (C_0 \to F0-15) \\ (l_{0-2}, RS0-1 \to C16) + (C_0 \to F0-15) \\ \cdots \\ \cdots \\ \cdots \end{array}$                                                 | $\begin{array}{l} (Clk \rightarrow C16) + (C0 \rightarrow flag) \\ (C_0 \rightarrow C16) + (C_0 \rightarrow flag) \\ (l_{0-2}, RS_{0-1} \rightarrow C16) + (C_0 \rightarrow flag) \\ \cdots \\ \cdots \end{array}$                        | <br>$(C_0 \rightarrow C_{16}) + (C_0 \text{ set-up time})$<br>$(I_{0-2}, RS_{0-1} \rightarrow C_{16}) + (C_0 \text{ set-up time})$<br>As in 16-bit case<br>As in 16-bit case                  |  |  |  |

| FTAB = 1, FTF = 0                                                |                                                                                                                                                                                                                              |                                                                                                                                                                                                                                           |                                                                                                                                                                                               |  |  |  |

| CLK<br>Co<br>Io - 2, RS0 - 1<br>Ao - 15, Bo - 15<br>ENA, ENB,ENF | As in 16-bit case                                                                                                                                                                                                            | $\begin{array}{l} \dots \\ (C_0 \rightarrow C_{16}) + (C_0 \rightarrow flag) \\ (l_{0-2}, RS_{0-1} \rightarrow C_{16}) + (C_0 \rightarrow flag) \\ (A_{0-15}, B_{0-15} \rightarrow C_{16}) + (C_0 \rightarrow flag) \\ \dots \end{array}$ | <br>(C0 $\rightarrow$ C16) + (C0 set-up time)<br>(I0-2, RS0-1 $\rightarrow$ C16) + (C0 set-up time)<br>As in 16-bit case<br>As in 16-bit case                                                 |  |  |  |

| FTAB = 0, FTF = 1                                                |                                                                                                                                                                                                                              |                                                                                                                                                                                                                                           |                                                                                                                                                                                               |  |  |  |

| CLK<br>Co<br>Io - 2, RSo - 1<br>Ao - 15, Bo - 15<br>ENA, ENB,ENF | $\begin{array}{l} \text{Don't care condition} \\ (C_0 \to C_{16}) + (C_0 \to F_{0-15}) \\ (I_{0-2}, RS_{0-1} \to C_{16}) + (C_0 \to F_{0-15}) \\ (A_{0-15}, B_{0-15} \to C_{16}) + (C_0 \to F_{0-15}) \\ \cdots \end{array}$ | Don't care condition<br>$(C_0 \rightarrow C_{16}) + (C_0 \rightarrow flag)$<br>$(I_{0-2}, RS_{0-1} \rightarrow C_{16}) + (C_0 \rightarrow flag)$<br>$(A_{0-15}, B_{0-15} \rightarrow C_{16}) + (C_0 \rightarrow flag)$<br>                | ·····<br>·····<br>·····                                                                                                                                                                       |  |  |  |

#### NOTE:

1. Flags are  $\overline{P}$ ,  $\overline{G}$ , OVF, Z and C16.

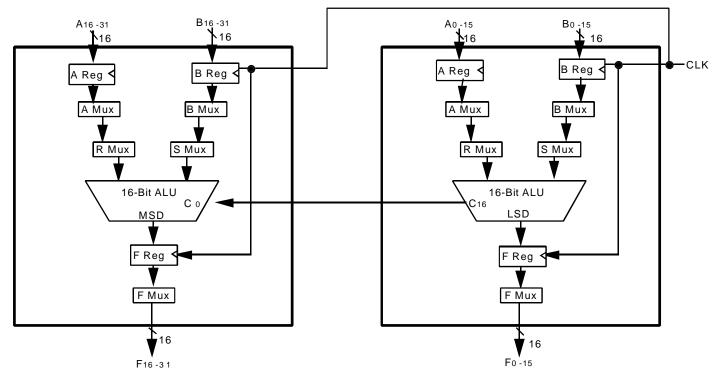

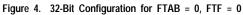

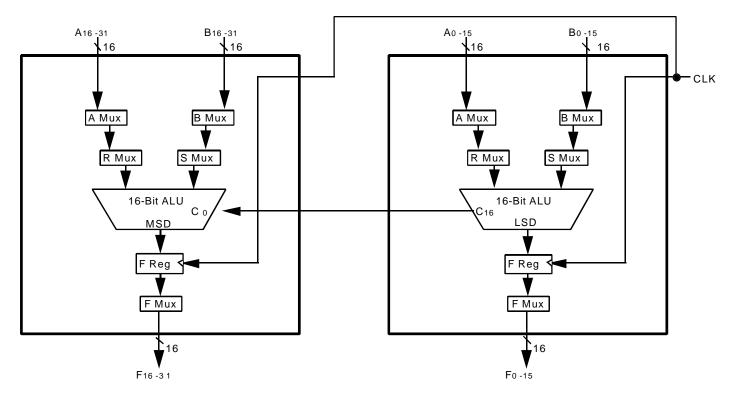

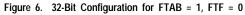

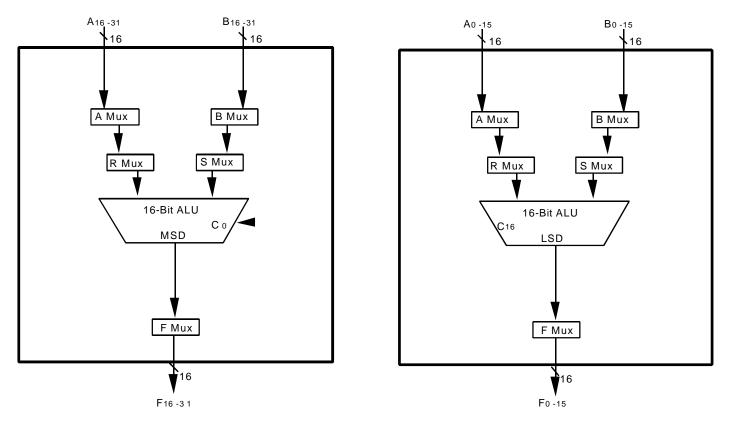

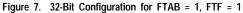

### **CASCADING THE IDT7381**

Some applications require 32-bit or wider input operands. Cascading is the hardware solution. It provides a high speed alternative in handling more than 16-bit wide operands.

#### 1. Cascading the IDT7381

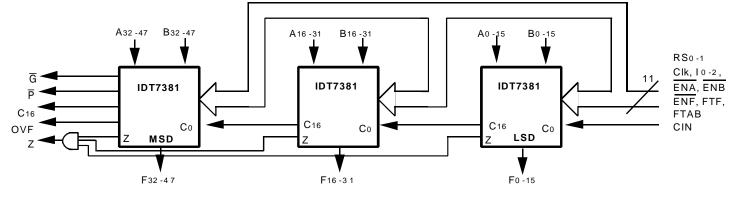

Cascading to 32-bit wide operands takes only two IDT7381s and no external hardware. However, cascading to data widths greater than 32-bit can be done in two ways: without external hardware (slow method) or by using a carry look ahead generator.

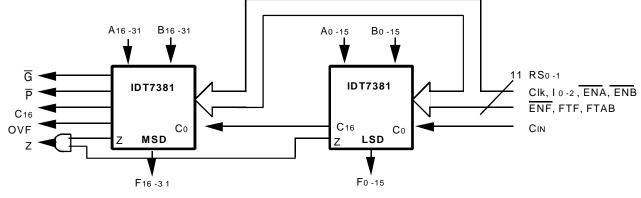

- a) Cascading the IDT7381 without a carry-look-ahead generator: (Figures 1 and 2)

- 1. Connect the C16 output of the least significant device into the C0 input of the next most significant device.

- 2. Common lines to all devices are: RS0-1, I0-2, Clk, FTF, FTAB,  $\overline{ENA}$ ,  $\overline{ENB}$ ,  $\overline{ENF}$ .

- 3. Take OVF, C16,  $\overline{P}$ ,  $\overline{G}$  of the most significant device as valid.

- 4. The system's zero flag (Z) is obtained by ANDing all zero flag results.

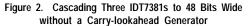

- b) Cascading three or more IDT7381s with carry-look-ahead (CLA) generator: (Figure 3)

- 1. Connect the P and G outputs of each device to the CLA generator's corresponding inputs.

- 2. Take the CLA generator outputs into the Co inputs of each device (except for the least significant one).

- 3. Common lines to all devices are: RS0-1, I0-2, Clk, FTF, FTAB, ENA, ENB, ENF.

- 4. Take OVF, C16,  $\overline{P}$ ,  $\overline{G}$  of the most significant device as valid.

- 5. Carry-in to the system should be connected to the Coinput of the least significant device and also to the CLA generator.

#### 2. Time Delay Considerations

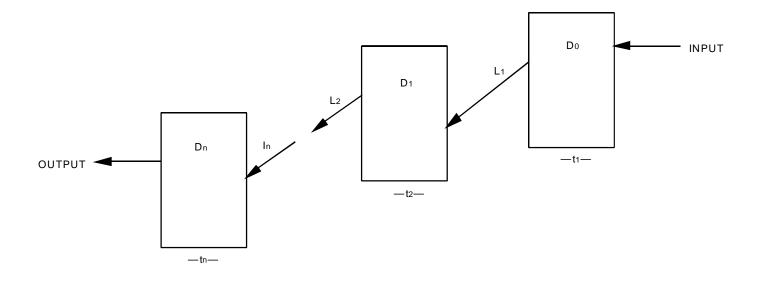

Once cascading has taken place, time delays may become critical in high performance systems. Our main interest here is focused on "propagation delays", i.e. calculating the time required for an input signal to propagate through several cascaded devices up to a specific output in another device within the cascaded system.

#### **Propagation Delay**

The propagation delay *for two devices* between the input and output of interest (input to output delay) is done as follows:

- 1. Calculate delay between the input and C16 in the first device.

- Calculate delay between Co and the output in the second device.

Add both results.

The following table is an example on how to build a propagation delay table for all inputs in a 32-bit IDT7381 cascaded system.

Propagation delay calculations can be extended to *n*-cascaded devices as the sum of the delays in all devices between the input and output of interest. That is:

$$(Input)_1 \rightarrow (C16)_1 = t_1$$

$$(C0)i \rightarrow (C16)i = ti$$

$$(C0)i + 1 \rightarrow (C16)i + 1 = ti + 1$$

$(C_0)n \rightarrow (Output)n = tn$

Where the subscript i denotes the device number and the arrow  $(\rightarrow)$  represents the delay in between. Notice that i + 1 is the immediate upper device from device i. Adding the delays ti we get:

Propagation delay =  $t_1 + t_2 + \dots + t_i + t_i + 1 + \dots + t_n$

#### **Total Delay**

...

As seen from Figure 8, the propagation delay is within the IDT7381 devices only. A complete analysis should also include the delay associated with the transmission line Li (which depends on the line length and its impedance). This line delay should then be added to the propagation delay to obtain the total delay for the cascaded system:

Total delay = Propagation delay + Transmission line delay

Figure 1. Cascading Two IDT7381s to 32 Bits

Figure 3. Cascading Three IDT7381s to 48 Bits Wide with a Carry-lookahead Generator

Figure 8. Propagation Delay = t1 + t2 + . . . + tn N-Cascaded Devices

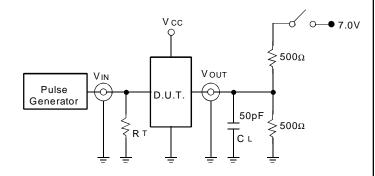

# **AC TEST CONDITIONS**

| Input Rise levels             | GND to 3V |

|-------------------------------|-----------|

| Input Rise/Fall Times         | 3ns       |

| Input Timing Reference Levels | 1.5V      |

| Output Reference Levels       | 1.5V      |

| Output Load                   | Figure 1  |

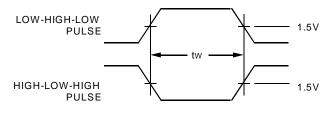

### **TEST WAVEFORMS**

## **TEST CIRCUITS FOR ALL OUTPUTS**

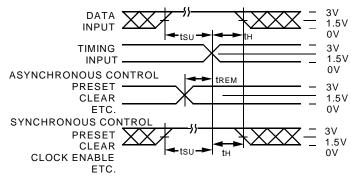

# SET-UP, HOLD, AND RELEASE TIMES

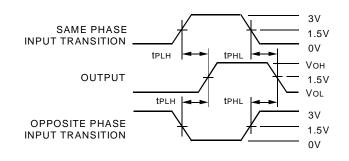

## **PROPAGATION DELAY**

# **SWITCH POSITION**

| Test            | Switch |

|-----------------|--------|

| Open Drain      |        |

| Disable Low     | Closed |

| Enable Low      |        |

| All Other Tests | Open   |

#### **DEFINITIONS:**

CL= Load capacitance: includes jig and probe capacitance.

$R\tau$  = Termination resistance: should be equal to  $Z_{OUT}$  of the Pulse Generator.

# **ENABLE AND DISABLE TIMES**

#### NOTES:

1. Diagram shown for input Control Enable-LOW and input Control Disable-HIGH

2. Pulse Generator for All Pulses: Rate  $\leq$  1.0MHz; tF  $\leq$  2.5ns; tR  $\leq$  2.5ns

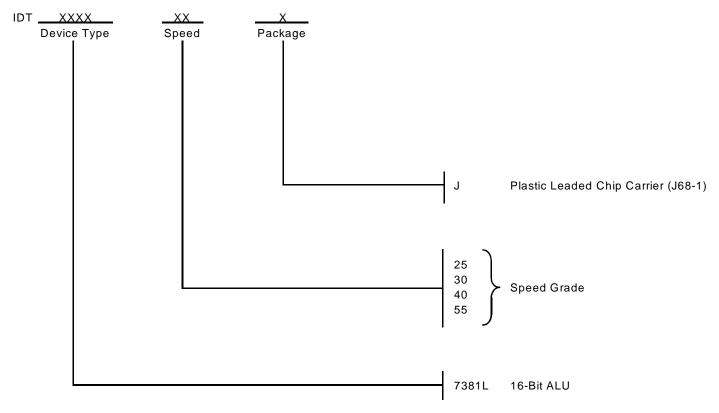

## **ORDERING INFORMATION**

*CORPORATE HEADQUARTERS* 2975 Stender Way Santa Clara, CA 95054 *for SALES:* 800-345-7015 or 408-727-6116 fax: 408-492-8674 www.idt.com\*

\*To search for sales office near you, please click the sales button found on our home page or dial the 800# above and press 2. The IDT logo is a registered trademark of Integrated Device Technology, Inc.