# *HM-6617*

#### March 1997

# 2K x 8 CMOS PROM

#### Features

- Low Power Standby and Operating Power

- ICCSB ......100μA

- Fast Access Time ...... 90/120ns

- Industry Standard Pinout

- Single 5.0V Supply

- CMOS/TTL Compatible Inputs

- High Output Drive ...... 12 LSTTL Loads

- Synchronous Operation

- **On-Chip Address Latches**

- Separate Output Enable

# Ordering Information

| PACKAGE       | TEMP. RANGE                               | 90ns               | 120ns              | PKG.<br>NO. |

|---------------|-------------------------------------------|--------------------|--------------------|-------------|

| SBDIP         | -40°C to +85°C                            | HM1-6617B-<br>9    | HM1-<br>6617-9     | D24.6       |

| SMD#          | -55 <sup>o</sup> C to +125 <sup>o</sup> C | 5962-<br>8954002JA | 5962-<br>8954001JA | D24.6       |

| SLIM<br>SBDIP | -40°C to +85°C                            | HM6-6617B-<br>9    | HM6-<br>6617-9     | D24.3       |

| SMD#          | -55 <sup>0</sup> C to +125 <sup>0</sup> C | 5962-<br>8954002LA | 5962-<br>8954001LA | D24.3       |

| CLCC          | -40°C to +85°C                            | HM4-6617B-<br>9    | HM4-<br>6617-9     | J32.A       |

| SMD#          | -55 <sup>0</sup> C to +125 <sup>0</sup> C | 5962-<br>8954002XA | 5962-<br>8954001XA | J32.A       |

# Description

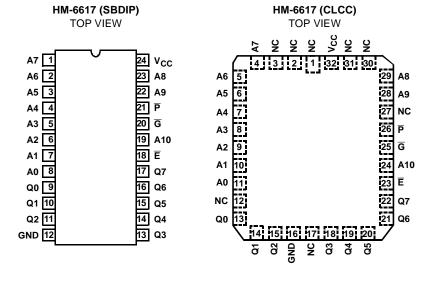

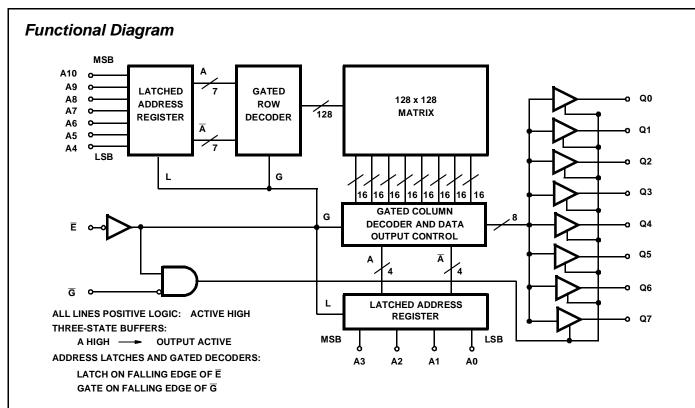

The HM-6617 is a 16,384 bit fuse link CMOS PROM in a 2K word by 8-bit/word format with "Three-State" outputs. This PROM is available in the standard 0.600 inch wide 24 pin SBDIP, the 0.300 inch wide slimline SBDIP, and the JEDEC standard 32 pad CLCC.

The HM-6617 utilizes a synchronous design technique. This includes on-chip address latches and a separate output enable control which makes this device ideal for applications utilizing recent generation microprocessors. This design technique, combined with the Intersil advanced self-aligned silicon gate CMOS process technology offers ultra-low standby current. Low ICCSB is ideal for battery applications or other systems with low power requirements.

The Intersil NiCr fuse link technology is utilized on this and other Intersil CMOS PROMs. This gives the user a PROM with permanent, stable storage characteristics over the full industrial and military temperature voltage ranges. NiCr fuse technology combined with the low power characteristics of CMOS provides an excellent alternative to standard bipolar PROMs or NMOS EPROMs.

All bits are manufactured storing a logical "0" and can be selectively programmed for a logical "1" at any bit location.

### Pinouts

#### **PIN DESCRIPTION**

| PIN             | DESCRIPTION    |  |

|-----------------|----------------|--|

| NC              | No Connect     |  |

| A0-A10          | Address Inputs |  |

| Ē               | Chip Enable    |  |

| Q               | Data Output    |  |

| V <sub>CC</sub> | Power (+5V)    |  |

| G               | Output Enable  |  |

| P (Note)        | Output Enable  |  |

NOTE:  $\overline{P}$  should be hardwired to V<sub>CC</sub> except during programming.

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. 1-888-INTERSIL or 321-724-7143 | Intersil (and design) is a trademark of Intersil Americas Inc. Copyright © Intersil Americas Inc. 2002. All Rights Reserved

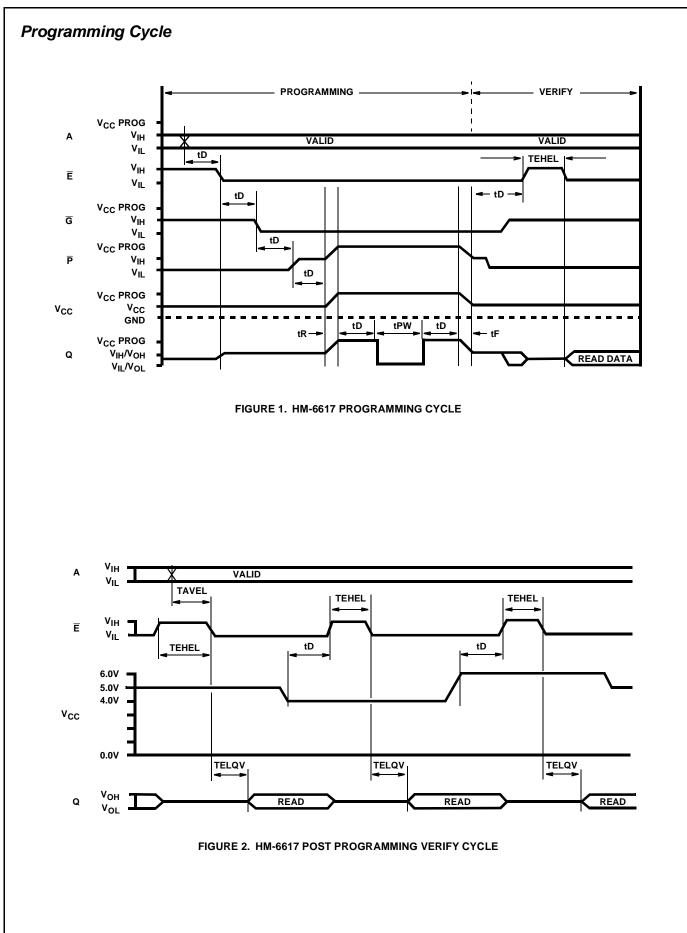

# Background Information Programming Algorithm

The HM-6617 CMOS PROM is manufactured with all bits containing a logical zero (output low). Any bit can be programmed selectively to a logical one (output high) state by following the procedure shown below. To accomplish this, a programmer can be built that meets the specifications shown, or any of the approved commercial programmers can be used.

#### **Programming Sequence Of Events**

- 1. Apply a voltage of  $V_{CC1}$  to  $V_{CC}$  of the PROM.

- 2. Read all fuse locations to verify that the PROM is blank (output low).

- 3. Place the PROM in the initial state for programming:  $\overline{E} = V_{IH}$ ,  $\overline{P} = V_{IH}$ ,  $\overline{G} = V_{IL}$ .

- 4. Apply the correct binary address for the word to be programmed. No inputs should be left open circuit.

- 5. After a delay of tD, apply voltage of V<sub>IL</sub> to  $\overline{E}$  (pin 18) to access the addressed word.

- The address may be held through the cycle, but must be held valid at least for a time equal to tD after the falling edge of E. None of the inputs should be allowed to float to an invalid logic level.

- 7. After a delay of tD, disable the outputs by applying a voltage of V<sub>IH</sub> to  $\overline{G}$  (pin 20).

- 8. After a delay of tD, apply voltage of  $V_{IL}$  to  $\overline{P}$  (pin 21).

- 9. After delay of tD, raise V<sub>CC</sub> (pin 24) to VCCPROG with a rise time of tR. All outputs at V<sub>IH</sub> should track V<sub>CC</sub> with V<sub>CC</sub> -2.0V to V<sub>CC</sub> +0.3V. This could be accomplished by pulling outputs at V<sub>IH</sub> to V<sub>CC</sub> through pull-up resistors of value Rn.

- 10. After a delay of tD, pull the output which corresponds to the bit to be programmed to  $V_{IL}$ . Only one bit should be programmed at a time.

- 11. After a delay of tPW, allow the output to be pulled to V<sub>IH</sub> through pull-up resistor Rn.

- 12. After a delay of tD, reduce V<sub>CC</sub> (pin 24) to V<sub>CC1</sub> with a fall time of tF. All outputs at V<sub>IH</sub> should track V<sub>CC</sub> with V<sub>CC</sub> 2.0V to V<sub>CC</sub> +0.3V. This could be accomplished by pulling outputs at V<sub>IH</sub> to V<sub>CC</sub> through pull-up resistors of value Rn.

- 13. Apply a voltage of  $V_{IH}$  to  $\overline{P}$  (pin 21).

- 14. After a delay of tD, apply a voltage of  $V_{IL}$  to  $\overline{G}$  (pin 20).

- 15. After a delay of tD, examine the outputs for correct data. If any location verifies incorrectly, repeat steps 4 through 14 (attempting to program only those bits in the word which verified incorrectly) up to a maximum of eight attempts for a given word. If a word does not program within eight attempts, it should be considered a programming reject.

- Repeat steps 3 through 15 for all other bits to be programmed in the PROM.

#### **Post-Programming Verification**

- 17. Place the PROM in the post-programming verification mode:  $\overline{E} = V_{IH}$ ,  $\overline{G} = V_{IL}$ ,  $\overline{P} = V_{IH}$ ,  $V_{CC}$  (pin 24) =  $V_{CC1}$ .

- 18. Apply the correct binary address of the word to be verified to the PROM.

- 19. After a delay of tD, apply a voltage of  $V_{IL}$  to  $\overline{E}$  (pin 18).

- 20. After a delay of tD, examine the outputs for correct data. If any location fails to verify correctly, the PROM should be considered a programming reject.

- 21. Repeat steps 17 through 20 for all possible programming locations

#### **Post-Programming Read**

- 22. Apply a voltage of  $V_{CC2}$  = 4.0V to  $V_{CC}$  (pin 24).

- 23. After a delay of tD, apply a voltage of  $V_{IH}$  to  $\overline{E}$  (pin 18).

- 24. Apply the correct binary address of the word to be read.

- 25. After a delay of TAVEL, apply a voltage of  $V_{IL}$  to  $\overline{E}$  (pin 18).

- 26. After a delay of TELQV, examine the outputs for correct data. If any location fails to verify correctly, the PROM should be considered a programming reject.

- 27. Repeat steps 23 through 26 for all address locations.

- 28. Apply a voltage of  $V_{CC2}$  = 6.0V to  $V_{CC}$  (pin 24).

- 29. Repeat steps 23 through 26 for all address locations.

# Background Information HM-6617 Programming

#### **Programming Specifications**

| SYMBOL           | PARAMETER                                            | MIN   | ТҮР             | МАХ     | UNITS |

|------------------|------------------------------------------------------|-------|-----------------|---------|-------|

| VIL              | Input "0"                                            | 0.0   | 0.2             | 0.8     | V     |

| V <sub>IH</sub>  | Voltage "1" (Note 6)                                 | VCC-2 | V <sub>CC</sub> | VCC+0.3 | V     |

| VCCPROG          | Programming V <sub>CC</sub> (Note 2)                 | 12.0  | 12.0            | 12.5    | V     |

| V <sub>CC1</sub> | Operating V <sub>CC</sub>                            | 4.5   | 5.5             | 5.5     | V     |

| V <sub>CC2</sub> | Special Verify V <sub>CC</sub> (Note 3)              | 4.0   | -               | 6.0     | V     |

| tD               | Delay Time                                           | 1.0   | 1.0             | -       | μs    |

| tR               | Rise Time                                            | 1.0   | 10.0            | 10.0    | μs    |

| tF               | Fall Time                                            | 1.0   | 10.0            | 10.0    | μs    |

| TEHEL            | Chip Enable Pulse Width                              | 50    | -               | -       | ns    |

| TAVEL            | Address Valid to Chip Enable Low Time                | 20    | -               | -       | ns    |

| TELQV            | Chip Enable Low to Output Valid Time                 | -     | -               | 120     | ns    |

| tPW              | Programming Pulse Width (Note 4)                     | 90    | 100             | 110     | μs    |

| tIP              | Input Leakage at V <sub>CC</sub> = VCCPROG           | -10   | +1.0            | 10      | μΑ    |

| IOP              | IOP Data Output Current at V <sub>CC</sub> = VCCPROG |       | -5.0            | -10     | mA    |

| Rn               | Output Pull-Up Resistor (Note 5)                     | 5     | 10              | 15      | kΩ    |

| Τ <sub>Α</sub>   | Ambient Temperature                                  | -     | 25              | -       | °C    |

NOTES:

1. All inputs must track  $V_{CC}$  (pin 24) within these limits.

2. VCCPROG must be capable of supplying 500mA.

3. See Steps 22 through 29 of the Programming Algorithm.

4. See Step 11 of the Programming Algorithm.

5. All outputs should be pulled up to  $V_{\mbox{CC}}$  through a resistor of value Rn.

6. Except during programming (See Programming Cycle Waveforms).

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

#### **Absolute Maximum Ratings**

Supply Voltage (All Voltages Reference to Device GND)  $\ldots$  +7.0V Input or Output Voltage Applied for All Grades  $\ldots$  . GND -0.3V to  $V_{CC}$  +0.3V

| <b>Typical Derating Factor</b> | 5mA/MHz Increase in ICCOP |

|--------------------------------|---------------------------|

| ESD Classification             | Class 1                   |

#### **Operating Conditions**

#### **Thermal Information**

| Thermal Resistance (Typical)                                | $\theta_{JA}$       | θJC                                   |  |  |

|-------------------------------------------------------------|---------------------|---------------------------------------|--|--|

| SBDIP Package                                               | 48°C/W              | 9°C/W                                 |  |  |

| Slim SBDIP                                                  | 65 <sup>0</sup> C/W | 14 <sup>0</sup> C/W                   |  |  |

| CLCC Package                                                |                     | 19 <sup>0</sup> C/W                   |  |  |

| Maximum Storage Temperature Range                           | 65                  | <sup>o</sup> C to +150 <sup>o</sup> C |  |  |

| Maximum Junction Temperature                                |                     | +175 <sup>0</sup> C                   |  |  |

| Maximum Lead Temperature (Soldering 10s)+300 <sup>o</sup> C |                     |                                       |  |  |

#### **Die Characteristics**

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

| SYMBOL | PARAMETER                                  | MIN     | MAX     | UNITS | TEST CONDITIONS                                                            |

|--------|--------------------------------------------|---------|---------|-------|----------------------------------------------------------------------------|

| VIH    | Logical One Input Voltage                  | 2.4     | VCC+0.3 | V     | V <sub>CC</sub> = 5.5V                                                     |

| VIL    | Logical Zero Input Voltage                 | -0.3    | 0.8     | V     | $V_{CC} = 4.5V$                                                            |

| VOH1   | Logical One Output Voltage                 | 2.4     | -       | V     | I <sub>OH</sub> = -2.0mA, V <sub>CC</sub> = 4.5V                           |

| VOH2   | Logical One Output Voltage<br>(Note 2)     | VCC-1.0 | -       | V     | $I_{OH} = -100 \mu A, V_{CC} = 4.5 V$                                      |

| VOL    | Logical Zero Output Voltage                | -       | 0.4     | V     | I <sub>OL</sub> = +4.8mA, V <sub>CC</sub> = 4.5V                           |

| II     | Input Leakage                              | -1.0    | +1.0    | μΑ    | $V_{IN} = V_{CC}$ or GND, $V_{CC} = 5.5V$                                  |

| IOZ    | Output Leakage                             | -1.0    | +1.0    | μΑ    | $V_{O} = V_{CC}$ or GND, $\overline{G} = V_{CC}$ , $V_{CC} = 5.5V$         |

| ICCSB  | Standby Power Supply Current               | -       | 100     | μΑ    | $V_{IN} = V_{CC}$ or GND, $V_{CC} = 5.5V$ , $I_O = 0$                      |

| ICCOP  | Operating Power Supply Current<br>(Note 3) | -       | 20      | mA    | $  f = 1 MHz, V_{CC} = 5.5 V, I_O = 0, \\ V_{IN} = V_{CC} \text{ or GND} $ |

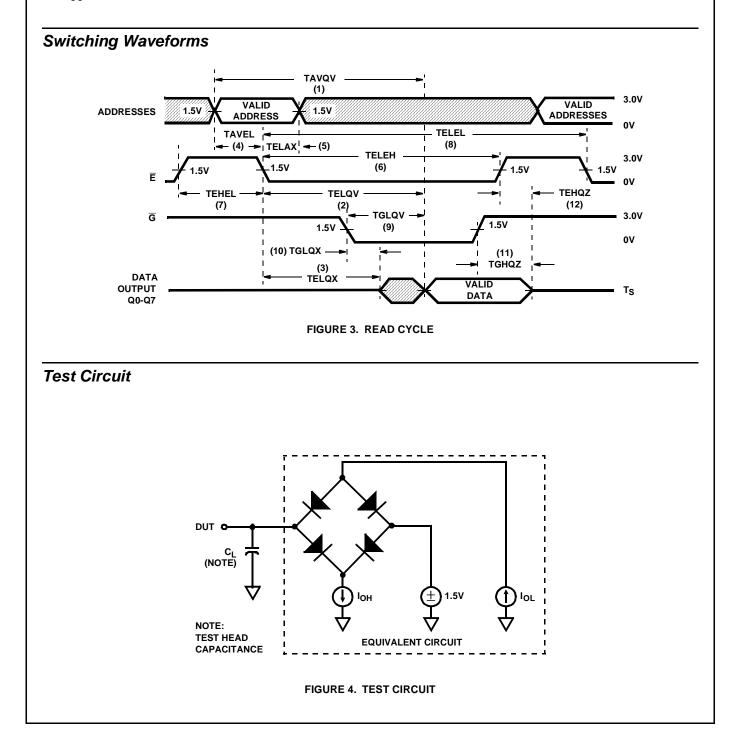

#### **AC Electrical Specifications**

|      |       |                          | HM-6617B-9 |     | HM-6617-9 |     |       |                 |

|------|-------|--------------------------|------------|-----|-----------|-----|-------|-----------------|

| SY   | MBOL  | PARAMETER                | MIN        | MAX | MIN       | MAX | UNITS | TEST CONDITIONS |

| (1)  | TAVQV | Address Access Time      | -          | 105 | -         | 140 | ns    | (Notes 1, 4)    |

| (2)  | TELQV | Chip Enable Access Time  | -          | 90  | -         | 120 | ns    | (Notes 1, 4)    |

| (3)  | TELQX | Chip Enable Time         | 5          | -   | 5         | -   | ns    | (Notes 2, 4)    |

| (4)  | TAVEL | Address Setup Time       | 15         | -   | 20        | -   | ns    | (Notes 1, 4)    |

| (5)  | TELAX | Address Hold Time        | 20         | -   | 25        | -   | ns    | (Notes 1, 4)    |

| (6)  | TELEH | Chip Enable Low Width    | 95         | -   | 120       | -   | ns    | (Notes 1, 4)    |

| (7)  | TEHEL | Chip Enable High Width   | 40         | -   | 40        | -   | ns    | (Notes 1, 4)    |

| (8)  | TELEL | Cycle Time               | 136        | -   | 160       | -   | ns    | (Notes 1, 4)    |

| (9)  | TGLQV | Output Access Time       | -          | 40  | -         | 50  | ns    | (Notes 1, 4)    |

| (10) | TGLQX | Output Enable Time       | 5          | -   | 5         | -   | ns    | (Notes 2, 4)    |

| (11) | TGHQZ | Output Disable Time      | -          | 40  | -         | 50  | ns    | (Notes 2, 4)    |

| (12) | TEHQZ | Chip Enable Disable Time | -          | 45  | -         | 50  | ns    | (Notes 2, 4)    |

| Capacitance T <sub>A</sub> | = +25 <sup>0</sup> C |

|----------------------------|----------------------|

|----------------------------|----------------------|

| SYMBOL | PARAMETER                   | МАХ | UNITS | TEST CONDITIONS                                        |

|--------|-----------------------------|-----|-------|--------------------------------------------------------|

| CIN    | Input Capacitance (Note 2)  | 10  | pF    | f = 1MHz, All Measurement are Referenced to Device GND |

| COUT   | Output Capacitance (Note 2) | 12  | pF    | f = 1MHz, All Measurement are Referenced to Device GND |

NOTES:

1. Input pulse levels: 0 to 3.0V; Input rise and fall times: 5ns (max); Input and output timing reference level: 1.5V; Output load: 1 TTL gate equivalent  $C_L = 50pF$  (min) - for  $C_L$  greater than 50pF, access time is derated by 0.15ns per pF.

2. Tested at initial design and after major design changes.

3. Typical derating 5mA/MHz increase in ICCOP.

4.  $V_{CC} = 4.5V$  and 5.5V.