Data Sheet April 16, 2007 FN6407.1

### Low Jitter Clock Generators for Set-Top Box

The ISL14010 series of devices are general purpose integrated Clock Synthesizers and Generators suited for consumer applications such as Set-top Box, and various other consumer applications.

The selectable reference input accepts 30MHz signal either from crystal or an external source. It is specified to operate with a nominal 3.3V supply and is offered in 16 Ld QFN package.

Contact Factory for other output frequency options.

### **Ordering Information**

| PART<br>NUMBER | PART<br>MARKING | TEMP.<br>RANGE (°C) | PACKAGE   | PKG.<br>DWG.# |

|----------------|-----------------|---------------------|-----------|---------------|

| ISL14010IRZ*   | 10IZ            | -40 to +85          | 16 LD QFN | L16.3x3       |

| ISL14017IRZ*   | 17IZ            | -40 to +85          | 16 LD QFN | L16.3x3       |

<sup>\*</sup>Add "-T" suffix for tape and reel.

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

#### Selection Table

| PART<br>OPTIONS | INPUT<br>FREQUENCY | NUMBER OF<br>OUTPUTS | OUTPUT<br>FREQUENCY | PACKAGE   |

|-----------------|--------------------|----------------------|---------------------|-----------|

| ISL14010        | 30MHz              | 4 LVTTL              | 25, 30, 48, 54      | 16 LD QFN |

| ISL14017        | 30MHz              | 4 LVTTL              | 25, 30, 40, 50      | 16 LD QFN |

#### **Features**

- LVTTL Outputs

- · Selectable Crystal or Ref. Clock for Inputs

- Period Jitter ~50ps RMS

- · Single Supply; 3.3V nominal

- Extended Temperature Range: -40°C to +85°C

- · Available in small foot print package

- 16 Ld QFN 3mmx3mm

- · Pb-Free plus anneal available (RoHS Compliant)

#### **Applications**

· Set-Top Boxes

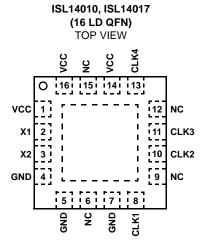

#### **Pinout**

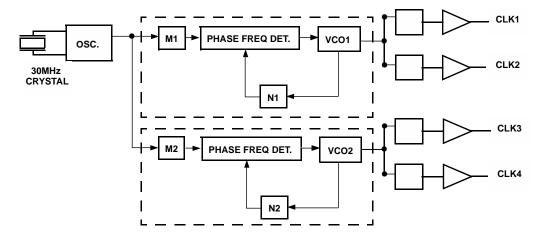

# Functional Block Diagram

## Pin Description

| 16 LD QFN    | SYMBOLS | PIN DESCRIPTION                                                                                        |

|--------------|---------|--------------------------------------------------------------------------------------------------------|

| 1,14,16      | VCC     | Supply Voltage                                                                                         |

| 2            | X1      | The X1 pin is the terminal 1 of an external 30MHz crystal. This pin is grounded for external CK input. |

| 3            | X2      | The X2 pin is the terminal 2 of external 30MHz crystal, or external clock input.                       |

| 4, 5, 7      | GND     | Ground                                                                                                 |

| 8            | CLK1    | CLK1 Output: 25MHz                                                                                     |

| 10           | CLK2    | CLK2 Output: 30MHz                                                                                     |

| 11           | CLK3    | CLK3 Output: 48MHz (40MHz for ISL14017)                                                                |

| 13           | CLK4    | CLK4 Output: 54MHz (50MHz for ISL14017)                                                                |

| 6, 9, 12, 15 | NC      | No Connect                                                                                             |

#### ISL14010, ISL14017

#### **Absolute Maximum Ratings**

###

Machine Model.....>500V

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)    | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (°C/W) |

|-----------------------------------------|----------------------|----------------------|

| 16 Ld QFN Package                       | 58                   | 11                   |

| Storage Temperature                     |                      | °C to +150°C         |

| Pb-free reflow profile                  |                      | ee link below        |

| http://www.intersil.com/pbfree/Pb-Freef | Reflow.asp           |                      |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE

θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

#### **DC Electrical Specifications**

$V_{CC}$  = 3.3V ±10%,  $T_A$  = -40°C to +85°C, Typical values are at  $T_A$  = +25°C and  $V_{CC}$  = 3.3V, Unless otherwise noted

| Chicago dilicimos notos      |                 |                                                    |                       |     |      |      |

|------------------------------|-----------------|----------------------------------------------------|-----------------------|-----|------|------|

| SYMBOL                       | SYMBOL          | CONDITIONS                                         | MIN                   | TYP | MAX  | UNIT |

| Supply Voltage               | V <sub>CC</sub> | Supply Voltage                                     | 3.0                   | 3.3 | 3.6  | V    |

| Supply Current               | lcc             | Supply Current C <sub>L</sub> = 5pF on all outputs |                       | 11  | 15   | mA   |

| CLOCK INPUT X2 (X1 GROUNI    | DED) FOR EXTERN | NAL CLOCK MODE                                     |                       |     | •    |      |

| Input High Level             | V <sub>IH</sub> |                                                    | 1.5                   |     | 2.4  | V    |

| Input Level Low              | V <sub>IL</sub> |                                                    |                       |     | 0.5  | V    |

| Input Current                | IIL, IIH        | V <sub>X2</sub> to Ground                          |                       | 0.5 |      | mA   |

| CLOCK OUTPUTS (CLK)          | 1               |                                                    |                       |     |      | ļ.   |

| Output High Level            | V <sub>OH</sub> | I <sub>OH</sub> = -100μA                           | V <sub>CC</sub> - 0.2 |     |      | V    |

|                              |                 | I <sub>OH</sub> = -4mA                             | 2.4                   |     |      | V    |

|                              |                 | I <sub>OH</sub> = -6mA                             | 2.1                   |     |      | V    |

| Output Low Level             | V <sub>OL</sub> | I <sub>OL</sub> = 100μA                            |                       |     | 0.2  | V    |

|                              |                 | I <sub>OL</sub> = 4mA                              |                       |     | 0.4  | V    |

|                              |                 | I <sub>OL</sub> = 6mA                              |                       |     | 0.75 | V    |

| Output Short Circuit Current | IOSC            | CLK = V <sub>CC</sub> or Gnd                       | 6                     | 13  | 30   | mA   |

|                              |                 | 1                                                  |                       |     |      |      |

### AC Electrical Specifications $C_L = 5pF$ on all outputs

| SYMBOL            | SYMBOL          | CONDITIONS                 | MIN | TYP | MAX | UNIT |

|-------------------|-----------------|----------------------------|-----|-----|-----|------|

| Crystal Frequency | f <sub>IN</sub> |                            |     | 30  |     | MHz  |

| CLOCK OUTPUTS     |                 |                            |     |     |     |      |

| Rise Time         | t <sub>R</sub>  | 20% to 80% V <sub>CC</sub> |     | 1.8 |     | ns   |

| Fall Time         | t <sub>F</sub>  | 80% to 20% V <sub>CC</sub> |     | 1.8 |     | ns   |

| Duty Cycle        |                 |                            | 40  |     | 60  | %    |

| Period Jitter     | J <sub>P</sub>  | RMS                        |     | 50  |     | ps   |

| Power Up Time     | t <sub>PO</sub> | V <sub>CC</sub> >2.7V      |     | 2   |     | ms   |

FN6407.1 April 16, 2007

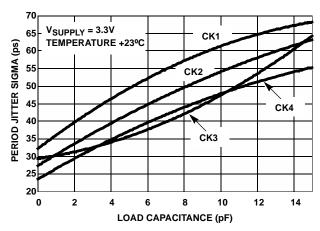

### Typical Performance Curves (Period Jitter)

FIGURE 1. STANDARD DEVIATION vs LOAD CAPACITANCE

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

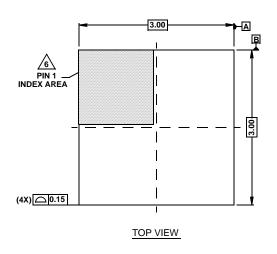

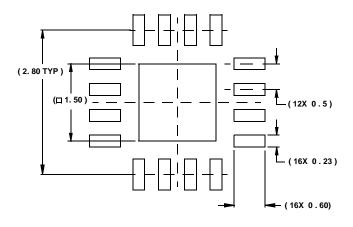

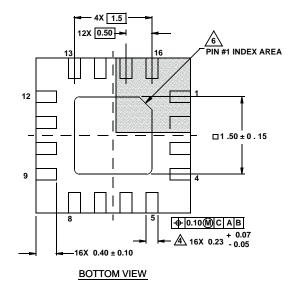

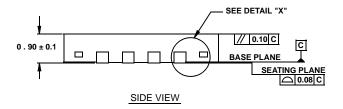

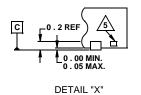

## **Package Outline Drawing**

L16.3x3

16 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE

Rev 2, 4/07

TYPICAL RECOMMENDED LAND PATTERN

5

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- 4. Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 indentifier may be either a mold or mark feature.

FN6407.1 April 16, 2007