# HS-82C08RH

## Radiation Hardened 8-Bit Bus Transceiver

February 1996

## Features

- Devices QML Qualified in Accordance With MIL-PRF-38535

- Detailed Electrical and Screening Requirements are Contained in SMD# 5962-95714 and Intersil' QM Plan

- Radiation Hardened

- Total Dose 1 x 10<sup>5</sup> RAD (Si)

- Latch-Up Immune EPI-CMOS > 1 x 10<sup>12</sup> RAD (Si)/s

- Bidirectional Three-State Input/Outputs

- Low Propagation Delay Time

- Low Power Consumption

- Single Power Supply +5V

- Electrically Equivalent to Sandia SA2997

- Military Temperature Range -55°C to +125°C

## Description

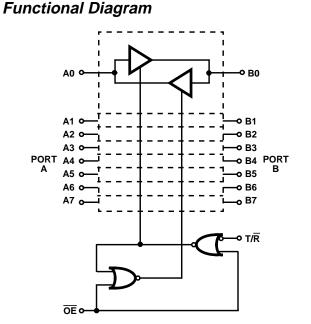

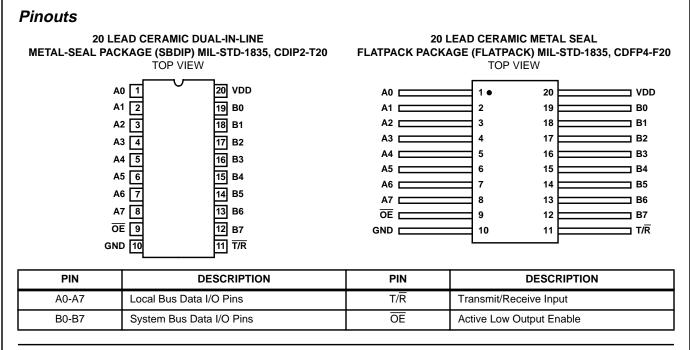

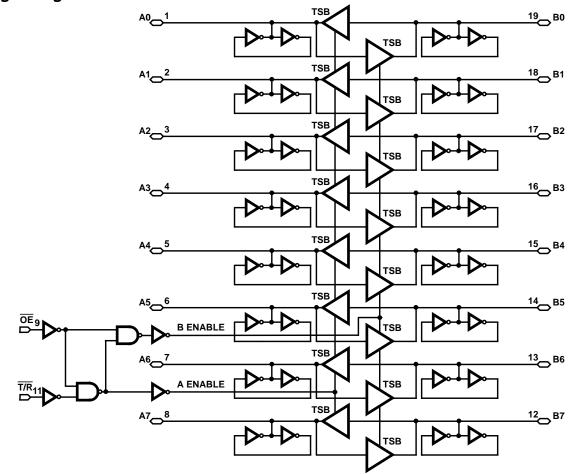

The Intersil HS-82C08RH is a radiation-hardened octal bus transceiver with three-state outputs. It is manufactured using a self-aligned, junction isolated CMOS process and is designed for use with the HS-80C08RH radiation-hardened microprocessor. The HS-82C08RH allows asynchronous two-way communication between data buses. The direction of data flow is determined by the logic level on the transmit/ receive (T/ $\overline{R}$ ) input. A logic high on the T/ $\overline{R}$  input specifies data flow from Port A to Port B of the device. Conversely, a logic low on the T/ $\overline{R}$  input specifies data flow from Port B to Port A. The Output Enable input disables both ports by placing them in the high impedance state.

The HS-82C08RH is ideally suited for a wide variety of buffering applications in radiation-hardened microcomputer systems.

TRUTH TABLE

| IN               | OPERATION            |        |        |

|------------------|----------------------|--------|--------|

| OUTPUT<br>ENABLE | TRANSMIT<br>/RECEIVE | PORT A | PORT B |

| 0                | 0                    | Out    | In     |

| 0                | 1                    | In     | Out    |

| 1                | Х                    | High Z | High Z |

X = Don't Care

| PART NUMBER        | TEMPERATURE RANGE | SCREENING LEVEL       | PACKAGE                  |

|--------------------|-------------------|-----------------------|--------------------------|

| 5962R9571401QRC    | -55°C to +125°C   | MIL-PRF-38535 Level Q | 20 Lead SBDIP            |

| 5962R9571401QXC    | -55°C to +125°C   | MIL-PRF-38535 Level Q | 20 Lead Ceramic Flatpack |

| 5962R9571401VRC    | -55°C to +125°C   | MIL-PRF-38535 Level V | 20 Lead SBDIP            |

| 5962R9571401VXC    | -55°C to +125°C   | MIL-PRF-38535 Level V | 20 Lead Ceramic Flatpack |

| HS1-82C08RH/SAMPLE | +25°C             | SAMPLE                | 20 Lead SBDIP            |

| HS9-82C08RH/SAMPLE | +25°C             | SAMPLE                | 20 Lead Ceramic Flatpack |

## **Ordering Information**

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. http://www.intersil.com or 407-727-9207 | Copyright © Intersil Corporation 1999

NOTE: An Important caveat that is applicable to CMOS devices in general is that unused inputs should never be left floating. This rule applies to inputs connected to a three-state bus. The need for external pull-up resistors during three-state bus conditions is eliminated by the presence of regenerative latches on the following HS-82C08RH pins. A0-7 and B0-7 The functional block diagram depicts one of these pins with the regenerative latch. When the CMOS driver assumes the high impedance state, the latch holds the bus in whatever logic state (high or low) it was before the three-state condition. A transient drive current of ±1.5mA at VDD/2 ±0.5V for 10ns is required to switch the latch. Thus, CMOS device inputs connected to the bus are not allowed to float during three-state conditions.

#### **Absolute Maximum Ratings**

| Supply Voltage                   | +7.0V                |

|----------------------------------|----------------------|

| Input, Output or I/O Voltage     | GND-0.3V to VDD+0.3V |

| Storage Temperature Range        | 65°C to +150°C       |

| Junction Temperature             | +175°C               |

| Lead Temperature (Soldering 10s) | +300°C               |

| ESD Classification               | Class 1              |

|                                  |                      |

### **Reliability Information**

| Thermal Resistance                                   | $\theta_{JA}$           | $\theta_{JC}$ |

|------------------------------------------------------|-------------------------|---------------|

| 20 Lead SBDIP Package                                | 71°C/W                  | 17°C/W        |

| 20 Lead Ceramic Flatpack Package                     | 85°C/W                  | 25°C/W        |

| Maximum Package Power Dissipation at +12             | 5 <sup>o</sup> C Ambier | it            |

| 20 Lead SBDIP Package                                |                         | 0.70W         |

| 20 Lead Ceramic Flatpack Package                     |                         | 0.59W         |

| If device power exceeds package dissipation          | capability, p           | rovide heat   |

| sinking or derate linearly at the following rate:    | :                       |               |

| 20 Lead SBDIP Package                                |                         | 14.1mW/C      |

| 20 Lead Ceramic Flatpack Package                     |                         | 11.8mW/C      |

| was normanant domage to the device. This is a stress |                         | nd an arotion |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

## **Operating Conditions**

| Operating Voltage Range     | +4.75V to +5.25V |

|-----------------------------|------------------|

| Operating Temperature Range | 55°C to +125°C   |

#### TABLE 1. DC ELECTRICAL PERFORMANCE CHARACTERISTICS

All Devices Guaranteed at Worst Case Limits and Conditions.

|                              |        |                                                     | GROUP A   |                         | LIMITS |     |       |

|------------------------------|--------|-----------------------------------------------------|-----------|-------------------------|--------|-----|-------|

| PARAMETER                    | SYMBOL | CONDITIONS                                          | SUBGROUPS | TEMPERATURE             | MIN    | MAX | UNITS |

| Input Leakage Current        | IIL    | VDD = 5.25V, VIN = VDD<br>Pin Under Test = 0V       | 1, 2, 3   | -55°C, +25°C,<br>+125°C | -1.0   | -   | μΑ    |

|                              | IIH    | VDD = 5.25V, VIN = 0V<br>Pin Under Test = 5.25V     | 1, 2, 3   | -55°C, +25°C,<br>+125°C | -      | 1.0 | μΑ    |

| High Level Output<br>Voltage | VOH    | VDD = 4.75V, IOH = -2.0mA                           | 1, 2, 3   | -55°C, +25°C,<br>+125°C | 4.25   | -   | V     |

| Low Level Output<br>Voltage  | VOL    | VDD = 5.25V, IOL = 2.0mA                            | 1, 2, 3   | -55°C, +25°C,<br>+125°C | -      | 0.5 | V     |

| Static Current               | SIDD   | VDD = 5.25V, VIN = GND                              | 1, 2, 3   | -55°C, +25°C,<br>+125°C | -      | 100 | μΑ    |

| Functional Test              | FT     | VDD = 4.75V to 5.25V<br>VIH = VDD -1.0V, VIL = 1.0V | 7, 8A, 8B | -55°C, +25°C,<br>+125°C | -      | -   | -     |

#### TABLE 2. AC ELECTRICAL PERFORMANCE CHARACTERISTICS

|                                                                                    | GROUP A |           | LIMITS               |     |     |       |

|------------------------------------------------------------------------------------|---------|-----------|----------------------|-----|-----|-------|

| PARAMETER                                                                          | SYMBOL  | SUBGROUPS | TEMPERATURE          | MIN | MAX | UNITS |

| PORT DATA/MODE SPECIFICATIONS                                                      |         |           |                      |     |     |       |

| Propagation Delay to Logical "1" from Port<br>A, B to Port B, A                    | TPDLH   | 9, 10, 11 | -55°C, +25°C, +125°C | -   | 65  | ns    |

| Propagation Delay to Logical "0" from Port<br>A, B to Port B, A                    | TPDHL   | 9, 10, 11 | -55°C, +25°C, +125°C | -   | 80  | ns    |

| Propagation Delay from High-Impedance to Logical "1" from $T/\overline{R}$ to Port | TPRTH   | 9, 10, 11 | -55°C, +25°C, +125°C | -   | 75  | ns    |

| Propagation Delay from High-Impedance to Logical "0" from $T/\overline{R}$ to Port | TPRTL   | 9, 10, 11 | -55°C, +25°C, +125°C | -   | 130 | ns    |

| Propagation Delay from High-Impedance to Logical "1" from OE to Port               | TPZH    | 9, 10, 11 | -55°C, +25°C, +125°C | -   | 70  | ns    |

| Propagation Delay from High-Impedance<br>to Logical "0" from OE to Port            | TPZL    | 9, 10, 11 | -55°C, +25°C, +125°C | -   | 130 | ns    |

|                                                                                    |             | (NOTE)                                                         |             | LIMITS |     |       |

|------------------------------------------------------------------------------------|-------------|----------------------------------------------------------------|-------------|--------|-----|-------|

| PARAMETER                                                                          | SYMBOL      | CONDITIONS                                                     | TEMPERATURE | MIN    | MAX | UNITS |

| In/Out Capacitance                                                                 | CI/O        | VDD = Open, f = 1MHz<br>All Measurements Referenced<br>to GND. | +25°C       | -      | 10  | pF    |

| TRANSMIT/RECEIVE MODE SPECIFICA                                                    | FIONS (AC P | arameters)                                                     |             |        |     |       |

| Propagation Delay from Logical "1" to High-Impedance from $T/\overline{R}$ to Port | TPHZTR      |                                                                | +25°C       | -      | 35  | ns    |

| Propagation Delay from Logical "0" to High-Impedance from $T/\overline{R}$ to Port | TPLZTR      |                                                                | +25°C       | -      | 35  | ns    |

| Propagation Delay from Logical "1" to High-Impedance from $\overline{OE}$ to Port  | TPHZ        |                                                                | +25°C       | -      | 35  | ns    |

| Propagation Delay from Logical "0" to High-Impedance from $\overline{OE}$ to Port  | TPLZ        |                                                                | +25°C       | -      | 35  | ns    |

#### TABLE 3. ELECTRICAL PERFORMANCE CHARACTERISTICS

NOTE:

1. The parameters listed are controlled via design or process parameters and are not directly tested. These parameters are characterized upon initial design release and upon design changes which could affect these characteristics.

#### TABLE 4. POST 100K RAD ELECTRICAL PERFORMANCE CHARACTERISTICS

NOTE: The Post Irradiation test conditions and limits are the same as those listed in Table 1 and Table 2.

#### TABLE 5. BURN-IN DELTA PARAMETERS (+25°C; In Accordance With SMD)

#### Switching Time Waveforms TR TF DEVICE VDD INPUT UNDER TEST POINTS 0.5VDD 0.5VDD TEST AN OR BN CL (NOTE) ٥٧ tPLH tPHI VDD OUTPUT .5VDD 0.5VDD **BN OR AN** ov TR = TF ≤ 20ns NOTE: CL includes stray and jig capacitance. 10% to 90% FIGURE 1. PORT TO PORT FIGURE 2. AC TESTING LOAD CIRCUIT VDD TR TR = TF ≤ 20ns TF INPUT OE 0.5VDD 10% to 90% 0.5VDD ٥V 0.1VDD tPZH PORT OUTPUT VOH 0.5VDD 0V tPHZ tPLZ VDD 0.5VDD PORT VOL OUTPUT tPZL 0.1VDD FIGURE 3. DE TO HIGH-IMPEDANCE, DE TO PORT OUTPUT

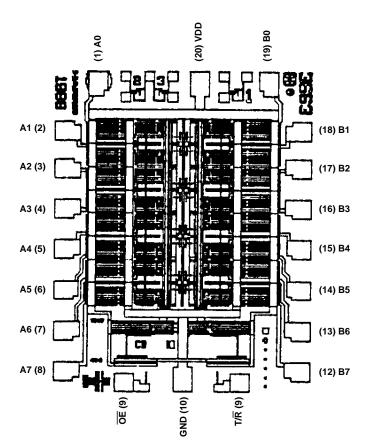

## Metallization Topology

## DIE DIMENSIONS:

76.0 mils x 89.4 mils x 14 mils  $\pm$ 1 mil

## **METALLIZATION:**

Type: Si - Al Thickness: 11kÅ ±2kÅ

## **GLASSIVATION:**

Type: SiO<sub>2</sub> Thickness: 8kÅ ±1kÅ

## Metallization Mask Layout

HS-82C08RH

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com

## Sales Office Headquarters

#### NORTH AMERICA

Intersil Corporation P. O. Box 883, Mail Stop 53-204 Melbourne, FL 32902 TEL: (407) 724-7000 FAX: (407) 724-7240

#### EUROPE

Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05

#### ASIA

Intersil (Taiwan) Ltd. Taiwan Limited 7F-6, No. 101 Fu Hsing North Road Taipei, Taiwan Republic of China TEL: (886) 2 2716 9310 FAX: (886) 2 2715 3029