# HS-54C138RH

Radiation Hardened 3-Line to 8-Line Decoder/Demultiplexer

February 1996

#### Features

- Devices QML Qualified in Accordance With MIL-PRF-38535

- Detailed Electrical and Screening Requirements are Contained in SMD# 5962-95825 and Intersil' QM Plan

- Radiation Hardened EPI-CMOS

- Total Dose 1 x 10<sup>5</sup> RAD (Si)

- Latch-Up Immune > 1 x 10<sup>12</sup> RAD (Si)/s

- Multiple Input Enable for Easy Expansion

- Single Power Supply +5V

- Outputs Active Low

- Low Standby Power (0.5mW Max at +5V)

- · High Noise Immunity

- Equivalent to Sandia SA2995

- Bus Compatible with Intersil Rad-Hard 80C85RH

- Full Military Temperature Range -55°C to +125°C

## Description

The Intersil HS-54C138RH is a radiation hardened 3- to 8-line decoder fabricated using a radiation hardened EPI-CMOS process. It features low power consumption, high noise immunity, and high speed. Also featured are pin and function compatibility with the 54LS138 industry standard part. The HS-54C138RH is ideally suited for high speed memory chip select address decoding. It is intended for use with the Intersil HS-80C85RH radiation hardened microprocessor, but it can also be utilized as a demultiplexer in any low power rad-hard application.

The HS-54C138RH contains a one of eight binary decoder. A three bit binary input is used to select and activate each of the eight outputs, provided the three chip enable inputs are also present (see truth table).

The HS-54C138RH has an on-chip enable gate. The active high (G1) and both active low ( $\overline{G2A}$ ,  $\overline{G2B}$ ) inputs are Anded together to provide a single enable input to the device. The use of both active high and active low inputs minimizes the need for external gates when expanding a system.

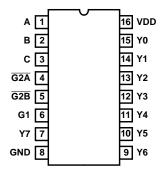

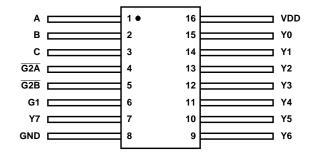

#### **Pinouts**

16 LEAD CERAMIC DUAL-IN-LINE METAL SEAL PACKAGE (SBDIP) MIL-STD-1835 CDIP2-T16 TOP VIEW

16 LEAD CERAMIC METAL SEAL FLATPACK PACKAGE (FLATPACK) MIL-STD-1835 CDFP4-F16 TOP VIEW

## **Ordering Information**

| PART NUMBER         | TEMPERATURE RANGE | SCREENING LEVEL       | PACKAGE                  |

|---------------------|-------------------|-----------------------|--------------------------|

| 5962R9582501QEC     | -55°C to +125°C   | MIL-PRF-38535 Level Q | 16 Lead SBDIP            |

| 5962R9582501QXC     | -55°C to +125°C   | MIL-PRF-38535 Level Q | 16 Lead Ceramic Flatpack |

| 5962R9582501VEC     | -55°C to +125°C   | MIL-PRF-38535 Level V | 16 Lead SBDIP            |

| 5962R9582501VXC     | -55°C to +125°C   | MIL-PRF-38535 Level V | 16 Lead Ceramic Flatpack |

| HS1-54C138RH/SAMPLE | +25°C             | Sample                | 16 Lead SBDIP            |

| HS9-54C138RH/SAMPLE | +25°C             | Sample                | 16 Lead Ceramic Flatpack |

# Specifications HS-54C138RH

## **Absolute Maximum Ratings**

##

## **Reliability Information**

| Thermal Resistance                                | $\theta_{JA}$ | $\theta_{JC}$ |

|---------------------------------------------------|---------------|---------------|

| SBDIP Package                                     | 73°C/W        | 24°C/W        |

| Ceramic Flatpack Package                          | 114°C/W       | 29°C/W        |

| Maximum Package Power Dissipation at +125         | 5°C Ambien    | t             |

| SBDIP Package                                     |               | 0.68W         |

| Ceramic Flatpack Package                          |               | 0.44W         |

| If device power exceeds package dissipation       | capability, p | rovide heat   |

| sinking or derate linearly at the following rate: |               |               |

| SBDIP Package                                     | 1             | 3.7mW/°C      |

| Ceramic Flatpack Package                          |               | 8.8mW/°C      |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

## **Operating Conditions**

| Operating Voltage Range                   | Input Low Voltage                 |

|-------------------------------------------|-----------------------------------|

| Operating Temperature Range55°C to +125°C | Input High VoltageVDD-1.0V to VDD |

#### TABLE 1. DC ELECTRICAL PERFORMANCE CHARACTERISTICS

|                               |        |                                                        | GROUP A   |                         | LIMITS |     |       |

|-------------------------------|--------|--------------------------------------------------------|-----------|-------------------------|--------|-----|-------|

| PARAMETER                     | SYMBOL | CONDITIONS                                             | SUBGROUPS | TEMPERATURE             | MIN    | MAX | UNITS |

| Input Leakage Current<br>High | IIH    | VDD = 5.25V, VIN = 0V,<br>Pin Under Test = VDD         | 1, 2, 3   | -55°C, +25°C,<br>+125°C | -      | 1   | μА    |

| Input Leakage Current<br>Low  | IIL    | VDD = 5.25V, VIN = 5.25V,<br>Pin Under Test = 0V       | 1, 2, 3   | -55°C, +25°C            | -1     | -   | μΑ    |

| High Level Output<br>Voltage  | VOH    | VDD = 4.75V, IIN = -2mA                                | 1, 2, 3   | -55°C, +25°C,<br>+125°C | 4.25   | -   | V     |

| Low Level Output<br>Voltage   | VOL    | VDD = 5.25V, IIN = 2mA                                 | 1, 2, 3   | -55°C, +25°C,<br>+125°C | 0.5    | -   | V     |

| Static Current                | SIDD   | VDD = 5.25V, VIN = GND                                 | 1, 2, 3   | -55°C, +25°C,<br>+125°C | -      | 100 | μА    |

| Functional Tests              | FT     | VDD = 5.25V and 4.75V,<br>VIH = VDD - 1.0V, VIL = 1.0V | 7, 8A, 8B | -55°C, +25°C,<br>+125°C | -      | -   | -     |

NOTE: All devices are guaranteed at worst case limits and conditions.

#### TABLE 2. AC ELECTRICAL PERFORMANCE CHARACTERISTICS

|                                                   |                                         | GROUP A SUB-  |                      | LIMITS |     |       |  |  |  |

|---------------------------------------------------|-----------------------------------------|---------------|----------------------|--------|-----|-------|--|--|--|

| PARAMETER                                         | SYMBOL                                  | GROUPS GROUPS | TEMPERATURE          | MIN    | MAX | UNITS |  |  |  |

| SELECT TO OUTPUT PROPAG                           | SELECT TO OUTPUT PROPAGATION DELAY TIME |               |                      |        |     |       |  |  |  |

| Low to high level input, High to low level output | TPHL11                                  | 9, 10, 11     | -55°C, +25°C, +125°C | -      | 110 | ns    |  |  |  |

| Low to high level input, Low to high level output | TPLH11                                  | 9, 10, 11     | -55°C, +25°C, +125°C | -      | 65  | ns    |  |  |  |

| High to low level input, Low to high level output | TPLH12                                  | 9, 10, 11     | -55°C, +25°C, +125°C | -      | 75  | ns    |  |  |  |

| High to low level input, high to low level output | TPHL12                                  | 9, 10, 11     | -55°C, +25°C, +125°C | -      | 90  | ns    |  |  |  |

| ENABLE TO OUTPUT PROPAGATION DELAY TIME           |                                         |               |                      |        |     |       |  |  |  |

| Low to high level input, Low to high level output | TPLH21                                  | 9, 10, 11     | -55°C, +25°C, +125°C | -      | 70  | ns    |  |  |  |

### HS-54C138RH

TABLE 2. AC ELECTRICAL PERFORMANCE CHARACTERISTICS (Continued)

|                                                   |        | GROUP A SUB- |                      | LIM | IITS |       |

|---------------------------------------------------|--------|--------------|----------------------|-----|------|-------|

| PARAMETER                                         | SYMBOL | GROUPS       | TEMPERATURE          | MIN | MAX  | UNITS |

| Low to high level input, High to low level output | TPHL21 | 9, 10, 11    | -55°C, +25°C, +125°C | -   | 105  | ns    |

| High to low level input, Low to high level output | TPLH22 | 9, 10, 11    | -55°C, +25°C, +125°C | -   | 70   | ns    |

| High to low level input, High to low level output | TPHL22 | 9, 10, 11    | -55°C, +25°C, +125°C | -   | 105  | ns    |

NOTE: Output timings are measured with a capacitive load, CL = 100pF, VIH = 3.75V, and VIL = 1.0V.

**TABLE 3. ELECTRICAL PERFORMANCE CHARACTERISTICS**

|                    |        |                                                                       |             | LIMITS |     |       |

|--------------------|--------|-----------------------------------------------------------------------|-------------|--------|-----|-------|

| PARAMETER          | SYMBOL | CONDITIONS                                                            | TEMPERATURE | MIN    | MAX | UNITS |

| Input Capacitance  | CIN    | VDD = Open, f = 1MHz, All Measurements<br>Referenced to Device Ground | +25°C       | 1      | 10  | pF    |

| Output Capacitance | COUT   | VDD = Open, f = 1MHz, All Measurements<br>Referenced to Device Ground | +25°C       | -      | 10  | pF    |

NOTE: The parameters listed in Table 3 are controlled via design or process parameters and are not directly tested. These parameters are characterized upon initial design release and upon design changes which would affect these characteristics.

#### TABLE 4. POST 100K RAD ELECTRICAL PERFORMANCE CHARACTERISTICS

NOTE: The Post Irradiation test conditions and limits are the same as those listed in Table 1 and Table 2.

TABLE 5. BURN-IN DELTA PARAMETERS (+25°C; In Accordance With SMD)

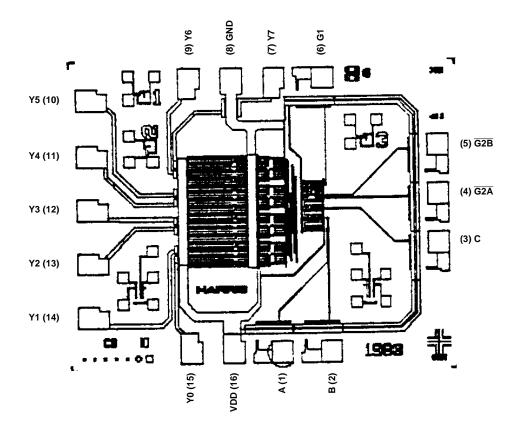

# Metallization Topology

## **DIE DIMENSIONS:**

76 mils x 63 mils x 14 mils  $\pm 1$  mil

## **METALLIZATION:**

Type: AISi

Thickness: 11kÅ ±2kÅ

## **GLASSIVATION:**

Type: SiO2

Thickness: 8kÅ ±1kÅ

# Metallization Mask Layout

#### HS-54C138RH

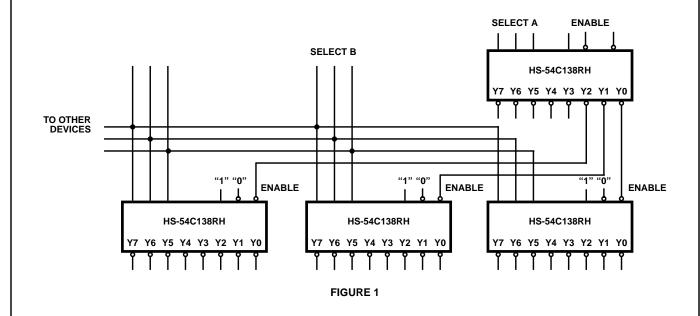

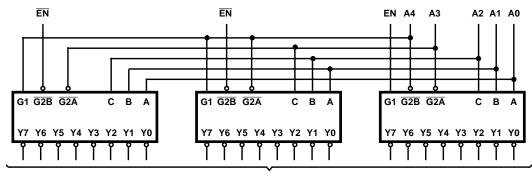

Typical applications include systems which require multiple input/output ports and memories. When the HS-54C138RH is enabled one of the eight outputs will go low. This output can be used to select a particular device or a group of devices. The HS-54C138RH can also be cascaded to provide an enabling scheme for larger systems and allow one decoder to control eight other decoders as in Figure 1.

Figure 2 shows a configuration that can be used to enable multiple I/O ports or memory devices. Up to 24 memory devices or I/O ports can be controlled using this circuit.

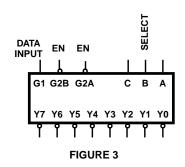

For demultiplexer operation, one of the three enable inputs is used as the data input while the other two inputs are enable. The transmitted data is distributed to the proper output as determined by the 3-line select inputs. See Figure 3.

PORT NUMBERS OR CHIP SELECTS

FIGURE 2

## HS-54C138RH

| All Intersil semiconductor r                                                                                             | oroducts are manufactured, assem                                                                                                                | bled and tested under <b>ISO9000</b> quality systems certification.                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Intersil products are sold by descrip<br>notice. Accordingly, the reader is cau<br>and reliable. However, no responsibil | tion only. Intersil Corporation reserves the utioned to verify that data sheets are current lity is assumed by Intersil or its subsidiaries for | ight to make changes in circuit design and/or specifications at any time without before placing orders. Information furnished by Intersil is believed to be accurate or its use; nor for any infringements of patents or other rights of third parties which by patent or patent rights of Intersil or its subsidiaries. |

|                                                                                                                          |                                                                                                                                                 | s products, see web site http://www.intersil.com                                                                                                                                                                                                                                                                         |

| Sales Office Headq                                                                                                       | uarters                                                                                                                                         |                                                                                                                                                                                                                                                                                                                          |

| NORTH AMERICA<br>Intersil Corporation                                                                                    | EUROPE<br>Intersil SA                                                                                                                           | <b>ASIA</b><br>Intersil (Taiwan) Ltd.                                                                                                                                                                                                                                                                                    |

Intersil Corporation

P. O. Box 883, Mail Stop 53-204

Melbourne, FL 32902

TEL: (407) 724-7000

FAX: (407) 724-7000

Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05

Intersil (Taiwan) Ltd. Taiwan Limited 7F-6, No. 101 Fu Hsing North Road Taipei, Taiwan Republic of China

TEL: (886) 2 2716 9310 FAX: (886) 2 2715 3029