PRELIMINARY

interci

Data Sheet

May 1999 File N

### File Number 4745

## *High Performance Programmable Phase-Locked Loop for LCD Applications*

The HI5634 is a low cost but very high-performance frequency generator for line-locked and genlocked high resolution video applications. Utilizing an advanced low voltage CMOS mixed signal technology, the HI5634 is an effective clock solution for video projectors and displays at resolutions from VGA to beyond UXGA

The HI5634 offers pixel clock outputs in both differential (to 250MHz) and single-ended (to 150MHz) formats. Digital phase adjustment circuitry allows user control of the pixel clock phase relative to the recovered sync signal. A second differential output at half the pixel clock rate enables deMUXing of multiplexed A/D converters. The FUNC pin provides either the regenerated input from the phase-locked loop (PLL) divider chain output or a re-synchronized and sharpened input HSYNC.

The advanced PLL utilizes either its internal programmable feedback divider or an external divider. The device is programmed by a standard I<sup>2</sup>C-bus<sup>®</sup> serial interface.

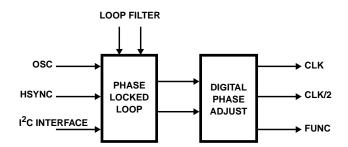

## Simplified Block Diagram

## **Ordering Information**

| PART NUMBER | TEMP.<br>RANGE ( <sup>o</sup> C) | PACKAGE    | PKG.<br>NO. |

|-------------|----------------------------------|------------|-------------|

| HI5634CB    | 0 to 70                          | 24 Ld SOIC | M24.3       |

### Features

- Pixel Clock Frequencies up to 250MHz

- Very Low Jitter

- Digital Phase Adjustment (DPA) for Clock Outputs

- Balanced PECL Differential Outputs

- Single-Ended SSTL\_3 Clock Outputs

- Double-Buffered PLL/DPA Control Registers

- Independent Software Reset for PLL/DPA

- External or Internal Loop Filter Selection

- Uses 3.3V Supply. Inputs are 5V Tolerant.

- I<sup>2</sup>C-bus Serial Interface can Run at Either Low Speed (100kHz) or High Speed (400kHz)

- Lock Detection

## Applications

- LCD Monitors and Video Projectors

- Genlocking Multiple Video Subsystems

- Frequency Synthesis

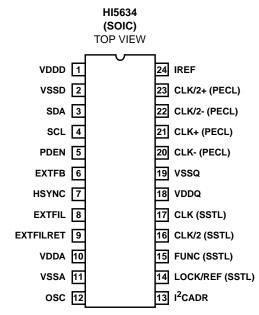

### Pinout

# Pin Descriptions

| PIN NO. | PIN NAME            | TYPE   | DESCRIPTION              | COMMENTS                                                                                        |

|---------|---------------------|--------|--------------------------|-------------------------------------------------------------------------------------------------|

| 1       | VDDD                | PWR    | Digital Supply           | 3.3V to Digital Sections                                                                        |

| 2       | VSSD                | PWR    | Digital Ground           |                                                                                                 |

| 3       | SDA                 | IN/OUT | Serial Data              | I <sup>2</sup> C-Bus (Note 1)                                                                   |

| 4       | SCL                 | IN     | Serial Clock             | I <sup>2</sup> C-Bus (Note 1)                                                                   |

| 5       | PDEN                | IN     | PFD Enable               | Suspends Charge Pump (Note1)                                                                    |

| 6       | EXTFB               | IN     | External Feedback In     | External Divider Input to PFD (Note1)                                                           |

| 7       | HSYNC               | IN     | Horizontal Sync          | Clock Input to PLL (Note1)                                                                      |

| 8       | EXTFIL              | IN     | External Filter          | External PLL Loop Filter                                                                        |

| 9       | EXTFILRET           | IN     | External Filter Return   | External PLL Loop Filter Return                                                                 |

| 10      | VDDA                | PWR    | Analog Supply            | 3.3V for Analog Circuitry                                                                       |

| 11      | VSSA                | PWR    | Analog Ground            | Ground for Analog Circuitry                                                                     |

| 12      | OSC                 | IN     | Oscillator               | Input From Crystal Oscillator Package (Notes 1, 2)                                              |

| 13      | I <sup>2</sup> CADR | IN     | I <sup>2</sup> C Address | Chip I <sup>2</sup> C Address Select<br>Low = 4Dh Read, 4Ch Write<br>High = 4Fh Read, 4Eh Write |

| 14      | LOCK/REF (SSTL)     | OUT    | Lock Indicator/Reference | Displays PLL or DPA Lock or REF Input                                                           |

| 15      | FUNC (SSTL)         | OUT    | Function Output          | SSTL_3 Selectable HSYNC Output                                                                  |

| 16      | CLK/2 (SSTL)        | OUT    | Pixel Clock/2 Out        | SSTL_3 Driver to ADC DeMUX Input                                                                |

| 17      | CLK (SSTL)          | OUT    | Pixel Clock Out          | SSTL_3 Driver to ADC                                                                            |

| 18      | VDDQ                | PWR    | Output Driver Supply     | 3.3V to Output Drivers                                                                          |

| 19      | VSSQ                | PWR    | Output Driver Ground     | Ground for Output Drivers                                                                       |

| 20      | CLK- (PECL)         | OUT    | Pixel Clock Out          | Inverted PECL Driver to ADC. Open Drain Output.                                                 |

| 21      | CLK+ (PECL)         | OUT    | Pixel Clock Out          | PECL Driver to ADC. Open Drain Output.                                                          |

| 22      | CLK/2- (PECL)       | OUT    | Pixel Clock/2 Out        | Inverted PECL Driver to ADC DeMUX Input. Open Drain Output.                                     |

| 23      | CLK/2+ (PECL)       | OUT    | Pixel Clock/2 Out        | PECL Driver to ADC DeMUX Input. Open Drain Output.                                              |

| 24      | IREF                | IN     | Reference Current        | Reference Current for PECL Outputs                                                              |

NOTES:

1. These LVTTL inputs are 5V tolerant.

2. Connect to ground if unused.

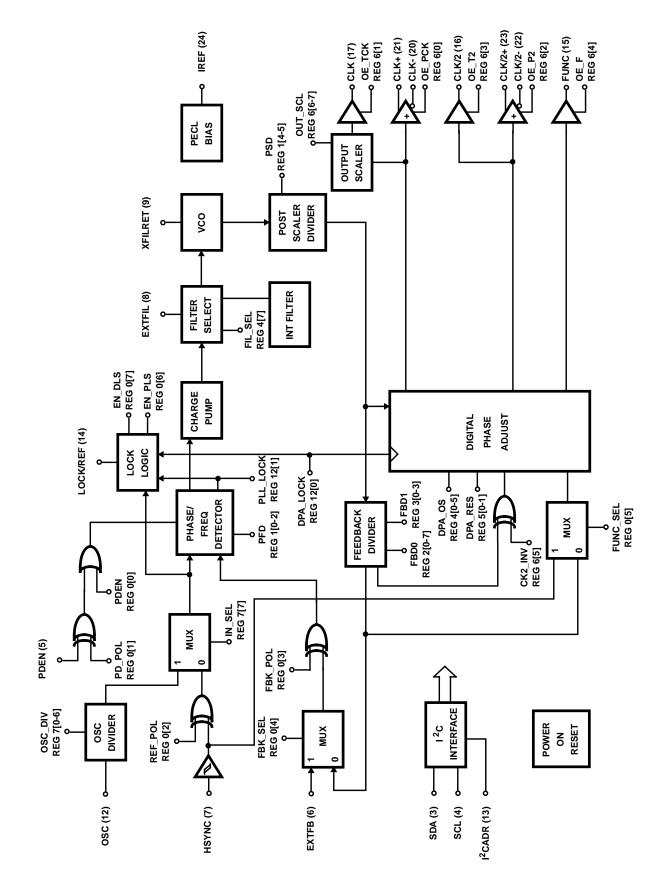

Block Diagram

## **Absolute Maximum Ratings**

### **Operating Conditions**

Temperature Range

0°C to 70°C

Voltage Range (VDDA, VDDD, VDDQ to VSS)

3.0V to 3.6V

### **Thermal Information**

| Thermal Resistance (Typical, Note 3)           | $\theta_{JA}$ (°C/W)                 |

|------------------------------------------------|--------------------------------------|

| SOIC Package                                   | 80                                   |

| Maximum Junction Temperature (Plastic Package) | 150 <sup>0</sup> C                   |

| Maximum Storage Temperature Range              | <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Lead Temperature (Soldering 10s)       | 260 <sup>0</sup> C                   |

| (SOIC - Lead Tips Only)                        |                                      |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

### NOTE:

3.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

| Electrical Specifications Per    | Operating C     | onditions Listed Above, Unless Otherwise Specif                                                            | ied     |         |      |       |

|----------------------------------|-----------------|------------------------------------------------------------------------------------------------------------|---------|---------|------|-------|

| PARAMETER                        | SYMBOL          | TEST CONDITIONS                                                                                            | MIN     | ТҮР     | MAX  | UNITS |

| DC SUPPLY CURRENT                |                 |                                                                                                            |         |         |      |       |

| Supply Current, Digital          | IDDD            | VDDD = 3.6V                                                                                                | -       | -       | 25   | mA    |

| Supply Current, Output Drivers   | IDDQ            | VDDQ = 3.6V, No Output Drivers Enabled                                                                     | -       | -       | 6    | mA    |

| Supply Current, Analog           | IDDA            | VDDA = 3.6V                                                                                                | -       | -       | 5    | mA    |

| DIGITAL INPUTS (SDA, SCL, PDEN,  | EXTFB, HSY      | NC, OSC, I <sup>2</sup> CADR)                                                                              | 1       |         |      |       |

| Input High Voltage               | VIH             |                                                                                                            | 2       | -       | 5.5  | V     |

| Input Low Voltage                | VIL             |                                                                                                            | VSS-0.3 | -       | 0.8  | V     |

| Input Hysteresis                 |                 |                                                                                                            | 0.2     | -       | 0.6  | V     |

| Input High Current               | IIH             | V <sub>IH</sub> = VDD                                                                                      | -       | -       | ±10  | μA    |

| Input Low Current                | ۱ <sub>IL</sub> | $V_{IL} = 0$                                                                                               | -       | -       | ±200 | μA    |

| Input Capacitance                | C <sub>IN</sub> |                                                                                                            | -       | -       | 10   | pF    |

| SDA (IN OUTPUT MODE: SDA IS BIE  | DIRECTIONA      | L)                                                                                                         |         |         |      |       |

| Output Low Voltage               | V <sub>OL</sub> | I <sub>OUT</sub> = 3mA. V <sub>OH</sub> = 6.0V Maximum, as<br>Determined by the External Pull-up Resistor. | -       | -       | 0.4  | V     |

| PECL OUTPUTS (CLK+, CLK-, CLK/2  | 2+, CLK/2-)     |                                                                                                            |         |         |      |       |

| Output High Voltage              | V <sub>OH</sub> | I <sub>OUT</sub> = 0                                                                                       | -       | -       | VDD  | V     |

| Output Low Voltage (Note 4)      | V <sub>OL</sub> | I <sub>OUT</sub> = Programmed Value                                                                        | 1.0     | -       | -    | V     |

| SSTL_3 OUTPUTS (CLK, CLK/2, FUN  | NC, LOCK/RE     | EF)                                                                                                        |         |         |      |       |

| Output Resistance                | R <sub>O</sub>  | 1 < V <sub>O</sub> < 2V                                                                                    | -       | -       | 80   | Ω     |

| AC INPUT CHARACTERISTICS         |                 |                                                                                                            | 1       |         |      |       |

| HSYNC Input Frequency            | <b>f</b> HSYNC  | Reg 7[7] = 0                                                                                               | 0.008   | -       | 10   | MHz   |

| OSC Input Frequency              | fosc            | Reg 7[7] = 1                                                                                               | 0.02    | -       | 100  | MHz   |

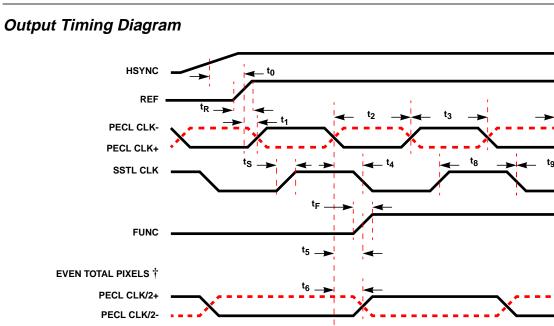

| TIMING CHARACTERISTICS (Note 5   | )               |                                                                                                            | 1       |         |      |       |

| REF Output Transition Times      | t <sub>r</sub>  | Rise Time/Fall Time                                                                                        | -       | 2.8/1.8 | -    | ns    |

| PECL CLK Output Transition Times | t <sub>P</sub>  | Rise Time/Fall Time                                                                                        | -       | 1.0/1.2 | -    | ns    |

| SSTL CLK Output Transition Times | tS              | Rise Time/Fall Time                                                                                        | -       | 1.6/0.7 | -    | ns    |

| FUNC Output Transition Times     | tF              | Rise Time/Fall Time                                                                                        | -       | 1.2/1.0 | -    | ns    |

| HSYNC to REF Delay               | t <sub>O</sub>  |                                                                                                            | 11.3    | 11.5    | 12   | ns    |

| REF to PECL Clock Delay          | t <sub>1</sub>  |                                                                                                            | -1.0    | 0.8     | 2.2  | ns    |

4

| PARAMETER                        | SYMBOL                          | TEST CONDITIONS | MIN | TYP  | MAX | UNITS |

|----------------------------------|---------------------------------|-----------------|-----|------|-----|-------|

| PECL Clock Duty Cycle            | t <sub>2</sub> , t <sub>3</sub> |                 | 45  | 50   | 55  | %     |

| PECL Clock to SSTL Clock Delay   | t <sub>4</sub>                  |                 | 0.2 | 0.75 | 1.2 | ns    |

| PECL Clock to FUNC Delay         | t <sub>5</sub>                  |                 | 1.5 | 1.9  | 2.3 | ns    |

| PECL Clock to PECL Clock/2 Delay | t <sub>6</sub>                  |                 | 1.0 | 1.3  | 1.5 | ns    |

| PECL Clock to SSTL Clock/2 Delay | t <sub>7</sub>                  |                 | 1.1 | 1.4  | 1.8 | ns    |

| SSTL Clock Duty Cycle            | t <sub>8</sub> , t <sub>9</sub> |                 | 45  | 50   | 55  | %     |

**Electrical Specifications** Per Operating Conditions Listed Above, Unless Otherwise Specified (Continued)

NOTES:

4.  $V_{OL}$  must not fall below the minimum specified level or the  $I_{OUT}$  value may not be maintained.

Measured at 3.6V 0<sup>o</sup>C, 135MHz output frequency, PECL Clock lines to 75Ω termination, SSTL Clock lines unterminated, 20pF load. Transition times vary based on termination. See the "Output Timing Diagram" for details.

## Application Information

### Overview

The HI5634 addresses stringent graphics system line locked and genlocked applications and provides the clock signals required by high-performance video A/D converters. Included are a phase locked loop (PLL) with a 500MHz voltage controlled oscillator (VCO), a digital phase adjustment to provide a user programmed pixel clock delay, the means for deMUXing multiplexed A/D Converters, and both balanced programmable (PECL) and single-ended (SSTL\_3) high-speed clock outputs.

### Phase-Locked Loop

The phase-locked loop is optimized for line-locked applications, for which the inputs are horizontal sync signals. A high-performance Schmitt trigger preconditions the HSYNC input, whose pulses can be degraded if they are from a remote source. This preconditioned HSYNC signal is provided as a clean reference signal with a short transition time (in contrast, the signal that a typical PC graphics card provides has a transition time of tens of nanoseconds).

A second high frequency input such as a crystal oscillator and a 7-bit programmable divider can be selected. This selection allows the loop to operate from a local source and is also useful for evaluating intrinsic jitter.

A 12-bit programmable feedback divider completes the loop. Designers can substitute an external divider.

Either the conditioned HSYNC input or the loop output (recovered HSYNC) is available at the FUNC pin, aligned to the edge of the pixel clock.

### Automatic Power-On-Reset Detection

The HI5634 has automatic power-on-reset detection circuitry and it resets itself if the supply voltage drops below threshold values. No external connection to a reset signal is required.

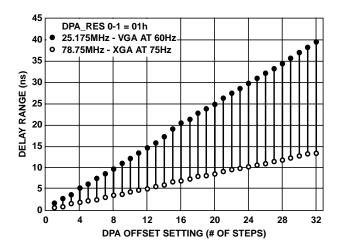

## Digital Phase Adjustment

The digital phase adjustment allows addition of a programmable delay to the pixel clock output, relative to the recovered HSYNC signal. The ability to add delays is particularly useful when multiple video sources must be synchronized. A delay of up to one pixel clock period is selectable in the following increments:

- 1/64 period for pixel clock rates to 40MHz

- 1/32 period for pixel clock rates to 80MHz

- 1/16 period for pixel clock rates to 160MHz

### **Output Drivers and Logic Inputs**

The HI5634 utilizes low voltage TTL (LVTTL) inputs as well as SSTL\_3 (EIA/JESD8-8) and low voltage PECL (pseudo-ECL) outputs, operating at 3.3V supply voltage. The LVTTL inputs are 5V tolerant. The SSTL\_3 and differential PECL output drivers drive resistive terminations or transmission lines. At lower clock frequencies, the SSTL\_3 outputs can be operated unterminated.

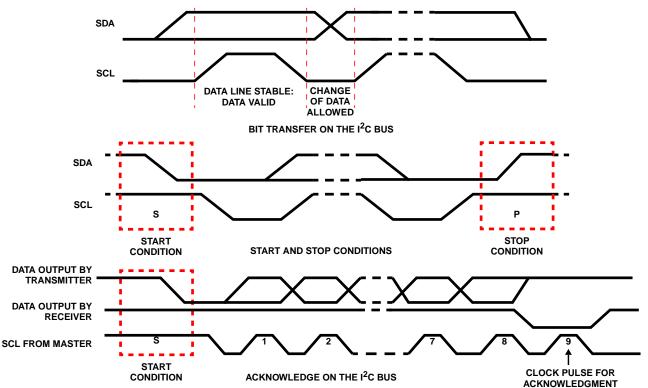

## I<sup>2</sup>C-bus Serial Interface

The HI5634 utilizes the industry standard  $I^2$ C-bus serial interface. The interface uses 12 registers: one write-only, eight read/write, and three read-only. Two HI5634 devices can be addressed, according to the state of the  $I^2$  CADR pin. When the pin is low, the read address is 4Dh, and the write address is 4Ch. When the pin is high, the read address is 4Fh, and the write address is 4Eh. The  $I^2$ C-bus serial interface can run at either low speed (100kHz) or high speed (400kHz) and provides 5V tolerant input.

## PC Board Layout

Use a PC board with at least four layers: one power, one ground, and two signal. No special cutouts are required for power and ground planes. All supply voltages must be supplied from a common source and must ramp up together. Flux and other board surface debris can degrade the performance of the external loop filter. Ensure that the HI5634 area of the board is free of contaminants.

### Specific Layout Guidelines

- 1. **Digital Supply (VDDD)** Bypass pin 1 (VDDD) to pin 2 (VSSD) with  $4.7\mu$ F and  $0.1\mu$ F capacitors, located as close as possible to the pins. Traces must be maximally wide and include multiple surface-etched vias to the appropriate plane.

- 2. External Loop Filter The use of an external loop filter is strongly recommended in all designs. Locate loop filter components as close to pins 8 and 9 (EXTFIL and EX-TFILRET) as possible. Typical loop filter values are  $6.8k\Omega$ for the series resistor, 3300pF RF-type capacitor for the series capacitor, and 150pF for the shunt capacitor.

- 3. Analog PLL Supply (VDDA) Decouple pin 10 (VDDA) with a series ferrite bead. Bypass the supply end of the bead with 4.7μF and 0.1μF capacitors. Bypass pin 10 to pin 11 (VSSA) with a 0.1μF capacitor. Locate these components as close as possible to the pins. Traces must be maximally wide and have multiple surface-etched vias to the power or ground planes.

- PECL Current Set Resistor Locate PECL current set resistor as close as possible to pin 24 (IREF). Bypass pin 24 to ground with a 0.1μF capacitor.

- 5. **PECL Outputs** Implement these outputs as microstrip transmission lines. The trace widths shown are for  $75\Omega$  characteristic impedance, presuming 0.067 in. between layers. Locate the optional series "snubbing" resistors as close as possible to the pins. If the termination resistors are included on-board, locate them as close as possible to the load and connect directly to the power and ground planes (these termination resistors are omitted if the load device implements them internally).

- Output Driver Supply (VDDQ) Bypass pin 18 (VDDQ) to pin 19 (VSSQ) with 4.7μF and 0.1μF capacitors, located as close as possible to the pins. Traces must be maximally wide and include multiple surface-etched vias to the appropriate plane.

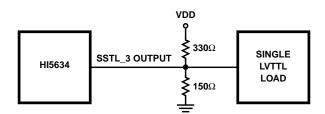

- SSTL\_3 Outputs SSTL\_3 outputs can be used like conventional CMOS rail-to-rail logic or as a terminated transmission line system at higher-output frequencies. With terminated outputs, the considerations of item 5, "PECL Outputs" apply. See JEDEC documents JESD8-A and JESD8-8.

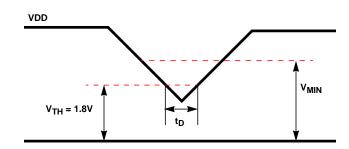

### Power Supply Considerations

The HI5634 incorporates special internal power-on-reset circuitry that requires no external reset signal connection. The supply voltage (VDD) must remain within the recommended operating conditions during normal operation. To reset the HI5634, the supply voltage at the part must be reduced below the threshold voltage (V<sub>TH</sub>) of the power-on-reset circuit. The supply voltage must remain below that threshold voltage such that board power conditioning capacitors are drained and the proper reset state is latched. The amount of time (t<sub>D</sub>) to hold the voltage in a reset state varies with the design. However, a typical value of 10ms should be sufficient.

6

## SSTL\_3 Outputs

## Unterminated Outputs

In the HI5634, unterminated SSTL output pins display exponential transitions similar to those of rectangular pulses presented to RC loads. The 10-90% rise time is typically 1.6ns, and the corresponding fall time is typically 700ps. In turn, this asymmetry contributes to duty cycle asymmetry at higher output frequencies. In the absence of significant load capacitance (which can further increase rise and fall time), this asymmetry is the dominant factor determining high frequency performance of these single-ended outputs. Typically, no termination is required for the LOCK/REF, FUNC, and CLK/2 outputs nor for CLK outputs up to approximately 135MHz.

### **Terminated Outputs**

SSTL\_3 outputs are intended to terminate in low impedances to reduce the effect of external circuit capacitance. Use of transmission line techniques enables use of longer traces between source and driver without increasing ringing due to reflections. Where external capacitance is minimal and substantial voltage swing is required to meet LVTTL V<sub>IH</sub> and V<sub>IL</sub> requirements, the intrinsic rise and fall times of HI5634 SSTL outputs are only slightly improved by termination in a low impedance.

The HI5634 SSTL output source impedance is typically less than 60 $\Omega$ . Termination impedance of 100 $\Omega$  reduces output swing by less than 30% which is more than enough to drive a single load of LVTTL inputs.

# I<sup>2</sup>C Register Map Summary

| REGISTER<br>NUMBER | NAME           | ACCESS   | BIT NAME    | BIT # | RESET<br>VALUE | DESCRIPTION                                                         |

|--------------------|----------------|----------|-------------|-------|----------------|---------------------------------------------------------------------|

| 0h                 | Input Control  | R/W      | PDEN        | 0     | 1              | Phase Detector Enable (0 = External Enable, 1 = Always Enabled)     |

|                    |                |          | PD_POL      | 1     | 0              | Phase Detector Enable Polarity (0 = Not Inverted, 1 = Inverted)     |

|                    |                |          | REF_POL     | 2     | 0              | External Reference Polarity (0 = Positive Edge, 1 = Negative Edge)  |

|                    |                |          | FBK_POL     | 3     | 0              | External Feedback Polarity (0 = Positive Edge, 1 = Negative Edge)   |

|                    |                |          | FBK_SEL     | 4     | 0              | External Feedback Select (0 = Internal Feedback, 1 = External)      |

|                    |                |          | FUNC_SEL    | 5     | 0              | Function Out Select (0 = Recovered HSYNC, 1 = Input HSYNC)          |

|                    |                |          | EN_PLS      | 6     | 1              | Enable PLL Lock/Ref Status Output (0 = Disable, 1 = Enable)         |

|                    |                |          | EN_DLS      | 7     | 0              | Enable DPA Lock/Ref Status Output (0 = Disable, 1 = Enable)         |

| 1h                 | Loop Control   | R/W †    | PFD0-2      | 0-2   | 0              | Phase Detector Gain                                                 |

|                    |                |          | Reserved    | 3     | 0              | Reserved                                                            |

|                    |                |          | PSD0-1      | 4-5   | 0              | Post Scaler Divider (0 = +2, 1 = +4, 2 = +8, 3 = +16)               |

|                    |                |          | Reserved    | 6-7   | 0              | Reserved                                                            |

| 2h                 | FDBK Div 0     | R/W †    | FDB0-7      | 0-7   | FF             | PLL Feedback Divider LSBs (Bits 0-7)                                |

| 3h                 | FDBK Div 1     | R/W †    | FDB8-11     | 0-3   | F              | PLL Feedback Divider MSBs (Bits 8-11)                               |

|                    |                |          | Reserved    | 4-7   | 0              | Reserved                                                            |

| 4h                 | DPA Offset     | R/W      | DPA_OS0-5   | 0-5   | 0              | Digital Phase Adjustment Offset                                     |

|                    |                |          | Reserved    | 6     | 0              | Reserved                                                            |

|                    |                |          | FIL_SEL     | 7     | 0              | Loop Filter Select (0 = External, 1 = Internal)                     |

| 5h                 | DPA Control    | R / W †† | DPA_RES0-1  | 0-1   | 3              | DPA Resolution (0 = 16 Delay Elements, 1 = 32, 2 = Reserved, 3 = 64 |

|                    |                |          | METAL_REV   | 2-7   | 0              | Metal Mask Revision Number                                          |

| 6h                 | Output Enables | R/W      | OE_PCK      | 0     | 0              | Output Enable for PECL PCLK Outputs (0 = High Z, 1 = Enabled)       |

| 1                  |                |          | OE_TCK      | 1     | 0              | Output Enable for STTL_3 CLK Output (0 = High Z, 1 = Enabled)       |

|                    |                |          | OE_P2       | 2     | 0              | Output Enable for PECL CLK/2 Outputs (0 = High Z, 1 = Enabled)      |

|                    |                |          | OE_T2       | 3     | 0              | Output Enable for STTL_3 CLK/2 Output (0 = High Z, 1 = Enabled)     |

|                    |                |          | OE_F        | 4     | 0              | Output Enable for STTL_3 FUNC Output (0 = High Z, 1 = Enabled)      |

|                    |                |          | CK2_INV     | 5     | 0              | CLK/2 Invert (0 = Not Inverted, 1 = Inverted)                       |

|                    |                |          | OUT_SCL     | 6-7   | 0              | SSTL Clock Scaler (0 = ÷1, 1 = ÷2, 2 = ÷4, 3 = ÷8)                  |

| 7h                 | OSC_DIV        | R/W      | OSC_DIV 0-6 | 0-6   | 0              | Osc Divider Modulus                                                 |

|                    |                |          | IN_SEL      | 7     | 1              | Input Select (0 = HSYNC Input, 1 = Osc Divider)                     |

| 8h                 | Reset          | Write    | DPA         | 0-3   | х              | Writing xAh Resets DPA and Loads Working Register 5                 |

|                    |                |          | PLL         | 4-7   | х              | Writing 5xh Resets PLL and Loads Working Registers 1-3              |

| 10h                | Chip Ver       | Read     | CHIP VER    | 0-7   | 17             | Chip Version 23 Decimal (17 Hex)                                    |

| 11h                | Chip Rev       | Read     | CHIP REV    | 0-7   | 01             | Initial Value 01h. Value Increments With Each All Layer Change.     |

| 12h                | RD_REG         | Read     | DPA_LOCK    | 0     | N/A            | DPA Lock Status (0 = Unlocked, 1 = Locked)                          |

|                    |                |          | PLL_LOCK    | 1     | N/A            | PLL Lock Status (0 = Unlocked, 1 = Locked)                          |

|                    |                |          | Reserved    | 2-7   | 0              | Reserved                                                            |

† Identifies Double Buffered Registers. Working Registers are Loaded During Software PLL Reset.

†† Identifies Double Buffered Registers. Working Registers are Loaded During Software DPA Reset.

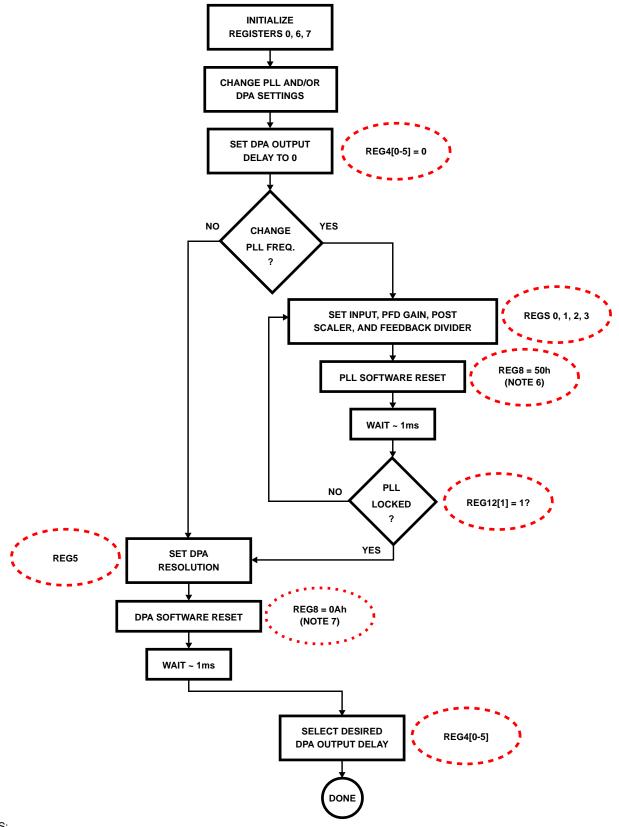

Software Programming Flow

NOTES:

6. Updates working Registers 1-3.

7. Updates working Resister 5.

# Detailed Register Description

| Register: ( | 0h    | Name: Inpu  | ut Control                                                                                                                                                                                        | Acces                                                                                                                                                                                     | s: Read/     | Nrite        |                                              |  |  |  |  |

|-------------|-------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|----------------------------------------------|--|--|--|--|

| BIT NAME    | BIT # | RESET VALUE | DESCRIPTION                                                                                                                                                                                       |                                                                                                                                                                                           |              |              |                                              |  |  |  |  |

| PDEN        | 0     | 1           | Phase/Frequency Detector Enable - 0 = External Enable (Phase/Frequency Detector controlled by PDEN (pin 5) only), 1 = Always Enabled (default).                                                   |                                                                                                                                                                                           |              |              |                                              |  |  |  |  |

| PD_POL      | 1     | 0           |                                                                                                                                                                                                   | Phase/Frequency Detector Enable Polarity - Used only when (Reg0 [0]=0).<br>0 = Not inverted (default, PDEN input (pin 5) is active high),1 = Inverted (PDEN input (pin 5) is active low). |              |              |                                              |  |  |  |  |

| REF_POL     | 2     | 0           | Phase/Frequency Detector External Reference Polarity - Edge of input signal on which Phase Detector riggers. 0 = Rising Edge (default), 1 = Falling Edge.                                         |                                                                                                                                                                                           |              |              |                                              |  |  |  |  |

| FBK_POL     | 3     | 0           | External Feedback Polarity - Edge of EXTFB (pin 6) signal on which Phase/Frequency Detector triggers when external feedback is used (Reg0 [4]=1). 0 = Positive Edge (default), 1 = Negative Edge. |                                                                                                                                                                                           |              |              |                                              |  |  |  |  |

| FBK_SEL     | 4     | 0           | External Feedback Select - 0 = Inter                                                                                                                                                              | nal Feedba                                                                                                                                                                                | ck (default) | , 1 = Exterr | al Feedback.                                 |  |  |  |  |

| FUNC_SEL    | 5     | 0           | Function Output Select - Selects re-<br>0 = Recovered HSYNC (default, reg<br>conditioned input from HSYNC (pin 1                                                                                  | enerated H                                                                                                                                                                                |              | · · ·        | ernal HSYNC (Schmitt-trigger                 |  |  |  |  |

| EN_PLS      | 6     | 1           | Outputs PLL Lock Status (Reg12[1])                                                                                                                                                                | EN_PLS                                                                                                                                                                                    | EN_DLS       | IN_SEL       | LOCK/REF (14)                                |  |  |  |  |

|             |       |             | on LOCK/REF pin.                                                                                                                                                                                  | 0                                                                                                                                                                                         | 0            | N/A          | 0                                            |  |  |  |  |

| EN_DLS      | 7     | 0           | Outputs DPA Lock Status                                                                                                                                                                           | 0                                                                                                                                                                                         | 1            | N/A          | 1 if DPA Locked, 0 Otherwise                 |  |  |  |  |

|             |       |             | (Reg12[0]) on LOCK/REF pin.<br>Bits 6, 7 enable multiple functions at                                                                                                                             | 1                                                                                                                                                                                         | 0            | N/A          | 1 if PLL Locked, 0 Otherwise                 |  |  |  |  |

|             |       |             | LOCK/REF output (pin 14), as shown in table at right.                                                                                                                                             | 1                                                                                                                                                                                         | 1            | 0            | Post Schmitt Trigger HSYNC(7)<br>XOR REF_POL |  |  |  |  |

|             |       |             |                                                                                                                                                                                                   | 1                                                                                                                                                                                         | 1            | 1            | F <sub>OSC</sub> ÷ OSC_DIV                   |  |  |  |  |

## Register: 1h Name: Loop Control Register

## Access: Read/Write (Note 8)

| BIT NAME | BIT #        | RESET VALUE |                                       | DES      | CRIPTIO | N     |                      |

|----------|--------------|-------------|---------------------------------------|----------|---------|-------|----------------------|

| PFD0-2   | PFD0-2 0-2 0 |             | Phase/Frequency Detector Gain.        | BIT 2    | BIT 1   | BIT 0 | PFD GAIN (μΑ/2π RAD) |

|          |              |             |                                       | 0        | 0       | 0     | 1                    |

|          |              |             |                                       | 0        | 0       | 1     | 2                    |

|          |              |             |                                       | 0        | 1       | 0     | 4                    |

|          |              |             | 0                                     | 1        | 1       | 8     |                      |

|          |              |             | 1                                     | 0        | 0       | 16    |                      |

|          |              |             |                                       | 1        | 0       | 1     | 32                   |

|          |              |             | 1                                     | 1        | 0       | 64    |                      |

|          |              |             |                                       | 1        | 1       | 1     | 128                  |

| Reserved | 3            | 0           | Reserved                              |          |         |       |                      |

| PSD0-1   | 4-5          | 0           | Post-Scaler Divider - Divides the out |          | BIT 5   | BIT 4 | PSD DIVIDER          |

|          |              |             | VCO prior to the DPA and Feedback     | Divider. | 0       | 0     | 2 (Default)          |

|          |              |             |                                       |          | 0       | 1     | 4                    |

|          |              |             |                                       |          | 1       | 0     | 8                    |

|          |              |             |                                       | 1        | 1       | 16    |                      |

| Reserved | 6-7          | 0           | Reserved                              |          |         | . I   |                      |

|       | ··· =··, •·· |       |             |                                                                                                                                                  |  |  |  |  |  |  |  |

|-------|--------------|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| REG # | BIT NAME     | BIT # | RESET VALUE | DESCRIPTION                                                                                                                                      |  |  |  |  |  |  |  |

| 2h    | FBD0-7       | 0-7   | FF          | PLL Feedback Divider LSBs (0-7). When Bit $0 = 0$ , the total number of pixels is even.<br>When Bit $0 = 1$ , the total number of pixels is odd. |  |  |  |  |  |  |  |

| 3h    | FBD8-11      | 0-3   | F           | PLL Feedback Divider MSBs (8-11).                                                                                                                |  |  |  |  |  |  |  |

| 3h    | Reserved     | 4-7   |             | Reserved                                                                                                                                         |  |  |  |  |  |  |  |

Register: 2h. 3h Name: Feedback Divider Registers

Access: Read/Write (Note 8, 9)

|                            | REG 3 |   |   |   |   |   | RE | G 2 |   |   | ] |   |    |

|----------------------------|-------|---|---|---|---|---|----|-----|---|---|---|---|----|

|                            | 3     | 2 | 1 | 0 | 7 | 6 | 5  | 4   | 3 | 2 | 1 | 0 | ]  |

| Feedback Divider Modulus = |       |   |   |   |   |   |    |     |   |   |   |   | +8 |

$12 \leq$  Feedback Divider Modulus  $\leq 4103$

### Register: 4h Name: DPA Offset Register

### Access: Read/Write **BIT NAME** BIT # **RESET VALUE** DESCRIPTION DPA\_OS0-5 0-5 0 Digital Phase Adjustment Offset - Selects clock edge offset in discrete steps from zero to one clock period minus one step. Resolution (number of delay elements per clock cycle) is selected by DPA\_RES0-1 (Reg 5[0-1]). Note: Offsets equal to or greater than one clock period are neither recommended nor supported. Example: For DPA\_RES0-1=01h, the clock can be delayed from 0 to 31 steps. Reserved 6 0 Reserved FIL\_SEL 7 0 Selects external loop filter (0) or internal loop filter (1). The use of an external loop filter is strongly recommended for all designs.

### **Register: 5h**

Name: DPA Control Register

### Access: Read/Write (Note 10)

| BIT NAME   | BIT # | RESET VALUE |                                                                                                                                                                    |          | DESC  | RIPTION |              |       |          |       |

|------------|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|---------|--------------|-------|----------|-------|

| DPA_RES0-1 | 0-1   | 3           | Digital Phase Adjustment<br>(DPA) Resolution Select.                                                                                                               | BIT 1    | BIT 0 |         | LAY<br>IENTS | CLK   | RANGE (N | /Hz)  |

|            |       |             | Use of the DPA above<br>160MHz is not                                                                                                                              | 0        | 0     | 1       | 6            |       | 48       | 160   |

|            |       |             | recommended.                                                                                                                                                       | 0        | 1     | 3       | 2            | 24    |          | 80    |

|            |       |             | _                                                                                                                                                                  | 1        | 0     | Rese    | erved        |       |          |       |

|            |       |             | 1                                                                                                                                                                  | 1        | 6     | 4       | 12           | 40    |          |       |

| METAL_REV  | 2-7   | 0           | Metal Mask Revision<br>Number - After power-up,<br>register bits 2-7 must be<br>written with 111111.<br>After this write, a read in-<br>dicates the metal mask re- | REVISION | BIT 7 | BIT 6   | BIT 5        | BIT 4 | BIT 3    | BIT 2 |

|            |       |             |                                                                                                                                                                    | А        | 1     | 1       | 1            | 1     | 1        | 1     |

|            |       |             |                                                                                                                                                                    | В        | 0     | 1       | 1            | 1     | 1        | 1     |

|            |       |             |                                                                                                                                                                    | C1       | 1     | 0       | 1            | 1     | 1        | 1     |

|            |       |             | vision, as shown in the table at right.                                                                                                                            | C2       | 0     | 0       | 1            | 1     | 1        | 1     |

|            |       |             |                                                                                                                                                                    | D        | 1     | 1       | 0            | 1     | 1        | 1     |

|            |       |             |                                                                                                                                                                    | E        | 1     | 1       | 1            | 0     | 1        | 1     |

|            |       |             | F                                                                                                                                                                  | 1        | 1     | 1       | 1            | 0     | 1        |       |

|            |       |             |                                                                                                                                                                    | G        | 1     | 1       | 1            | 1     | 1        | 0     |

### NOTES:

8. Double buffered registers. Actual working registers are loaded during software PLL reset. See Register 8h for details.

9. The value that is programmed into these two registers, plus a value of 8, defines the total number of clock periods that the HI5634 generates between HSYNCs. Program these registers with the total number of horizontal pixels per line minus 8.

10. Double buffered register. Actual working registers are loaded during software DPA reset. See Register 8h for details.

| Register: | 6h    | Name: Outp  | ut Enable Register Access: Read/Write                                        |                                                                             |       |             |  |  |  |  |  |

|-----------|-------|-------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------|-------------|--|--|--|--|--|

| BIT NAME  | BIT # | RESET VALUE | DESCRIPTION                                                                  | DESCRIPTION                                                                 |       |             |  |  |  |  |  |

| OE_PCK    | 0     | 0           | Output Enable for CLK Outputs (PECL) - 0 = High Z (default), 1 =             | Enabled.                                                                    |       |             |  |  |  |  |  |

| OE_TCK    | 1     | 0           | Output Enable for CLK Output (SSTL_3) - 0 = High Z (default), 1              | = Enabled                                                                   |       |             |  |  |  |  |  |

| OE_P2     | 2     | 0           | Output Enable for CLK/2 Outputs (PECL) - 0 = High Z (default), 1             | Dutput Enable for CLK/2 Outputs (PECL) - 0 = High Z (default), 1 = Enabled. |       |             |  |  |  |  |  |

| OE_T2     | 3     | 0           | Output Enable for CLK/2 Output (SSTL_3) - 0 = High Z (default), 1 = Enabled. |                                                                             |       |             |  |  |  |  |  |

| OE_F      | 4     | 0           | Output Enable for FUNC Output (SSTL_3) - 0 = High Z (default), 1 = Enabled.  |                                                                             |       |             |  |  |  |  |  |

| CK2_INV   | 5     | 0           | CLK/2 Invert - 0 = Not Inverted (default), 1 = Inverted.                     |                                                                             |       |             |  |  |  |  |  |

| OUT_SCL   | 6-7   | 0           | Clock (CLK) Scaler.                                                          | BIT 7                                                                       | BIT 6 | CLK DIVIDER |  |  |  |  |  |

|           |       |             |                                                                              | 0                                                                           | 0     | 1           |  |  |  |  |  |

|           |       |             |                                                                              | 0                                                                           | 1     | 2           |  |  |  |  |  |

|           |       |             |                                                                              | 1                                                                           | 0     | 4           |  |  |  |  |  |

|           |       |             |                                                                              | 1                                                                           | 1     | 8           |  |  |  |  |  |

| <b>Register:</b> | 7h |

|------------------|----|

|                  |    |

Name: Oscillator Divider Register

Access: Read/Write

| BIT NAME    | BIT # | RESET VALUE | DESCRIPTION                                                                                                                                                                             |

|-------------|-------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC_DIV0- 6 | 0-6   | 0           | Oscillator Divider Modulus - Divides the input from OSC (pin 12) by the set modulus.<br>The modulus equals the programmed value, plus 2. Therefore, the modulus range is from 3 to 129. |

| IN_SEL      | 7     | 1           | Input Select - Selects the input to the Phase/Frequency Detector<br>0 = HSYNC, 1 = Osc Divider (default).                                                                               |

### Register: 8h Name

Name: Reset Register

Access: Write Only

| BIT NAME  | BIT # | RESET VALUE | DESCRIPTION                                     |       |             |

|-----------|-------|-------------|-------------------------------------------------|-------|-------------|

| DPA Reset | 0-3   | х           | Writing XAh to this register resets DPA working | VALUE | RESETS      |

|           |       |             | Register 5.                                     | ХА    | DPA         |

| PLL Reset | 4-7   | Х           | Writing 5Xh to this register resets PLL working | 5X    | PLL         |

|           |       |             | Registers 1-3.                                  | 5A    | DPA and PLL |

## Register: 10h

Name: Chip Version Register

Access: Read Only

| BI | IT NAME | BIT # | RESET VALUE | DESCRIPTION            |

|----|---------|-------|-------------|------------------------|

| CI | HIP VER | 0-7   | 17          | Chip Version 23 (17h). |

## Register: 11h N

Name: Chip Revision Register

Access: Read Only

| BIT NAME | BIT # | RESET VALUE | DESCRIPTION                                                         |

|----------|-------|-------------|---------------------------------------------------------------------|

| CHIP REV | 0-7   | 01+         | Initial value 01h.<br>+Value increments with each all-layer change. |

### Register: 12h

Name: Status Register

## Access: Read Only

| BIT NAME | BIT # | RESET VALUE | DESCRIPTION                                                                     |  |

|----------|-------|-------------|---------------------------------------------------------------------------------|--|

| DPA_LOCK | 0     | N/A         | DPA Lock Status (Refer to Register 0h, bits 6 and 7). 0 = Unlocked, 1 = Locked. |  |

| PLL_LOCK | 1     | N/A         | PLL Lock Status (Refer to Register 0h, bits 6 and 7). 0 = Unlocked, 1 = Locked. |  |

| Reserved | 2-7   | 0           | Reserved                                                                        |  |

| I <sup>2</sup> C Data Format (Notes 11-14)                                                                                                                                                                                                                                           |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| RANDOM REGISTER WRITE PROCEDURE                                                                                                                                                                                                                                                      |      |

| S       0       1       1       X       W       A       A       A       A       A       P         7       Bit Address       Register Address       Data       A       P                                                                                                              |      |

| RANDOM REGISTER READ PROCEDURE                                                                                                                                                                                                                                                       |      |

| S       0       1       0       0       1       1       X       W       A       A       S       0       1       0       0       1       1       X       R       A       F       P         7       Bit Address       Register Address       7       Bit Address       Data       Data |      |

| SEQUENTIAL REGISTER WRITE PROCEDURE                                                                                                                                                                                                                                                  |      |

| S 0 1 0 0 1 1 X W A A A A A A                                                                                                                                                                                                                                                        | AP   |

| 7 Bit Address Register Address Data Data                                                                                                                                                                                                                                             |      |

| SEQUENTIAL REGISTER READ PROCEDURE                                                                                                                                                                                                                                                   |      |

| S     0     1     0     0     1     1     X     W     A     A     S     0     1     0     0     1     1     X     R     A                                                                                                                                                            | Ā P  |

| 7 Bit Address Register Address 7 Bit Address Data                                                                                                                                                                                                                                    | Data |

| Direction: = Bus Host to Device = Device to Bus Host                                                                                                                                                                                                                                 |      |

| NOTES:                                                                                                                                                                                                                                                                               |      |

11. All values are transmitted with the most significant bit first and the least significant bit last.

12. The value of the X-bit equals the logic state of pin 13 (I<sup>2</sup>CADR).

13. R = Read Command = 1, W = Write Command = 0.

14. S = Start Condition, A = Acknowledge,  $\overline{A}$  = No Acknowledge, P = Stop Condition. See "I<sup>2</sup>C Data Characteristics" for description.

NOTE: These waveforms are from "The I<sup>2</sup>C bus and how to use it," published by Philips Semiconductor. The document can be obtained from: http://www-us2.semiconductors.philips.com/acrobat/various/i2c\_bus\_specification\_1995.pdf.

13

intersil

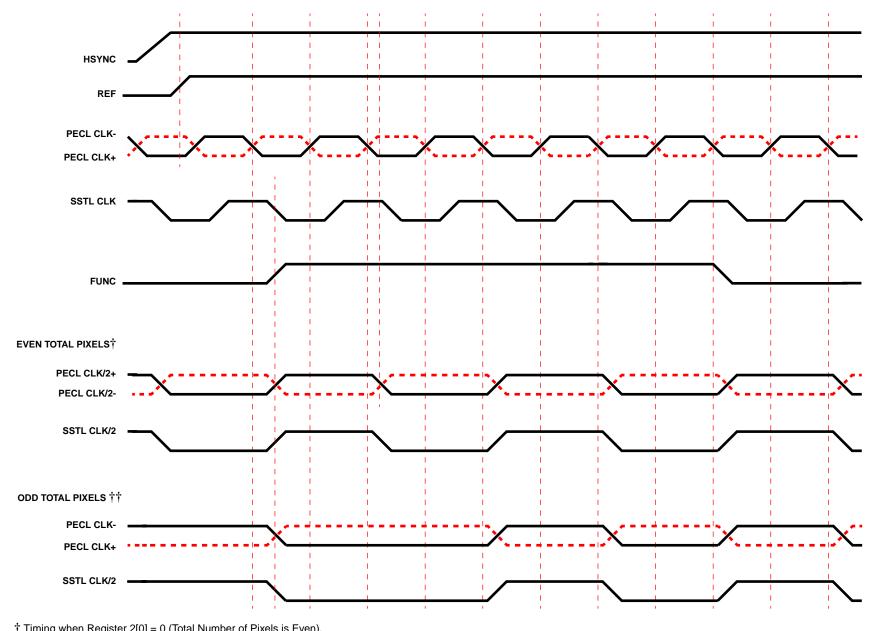

<sup>†</sup> Timing when Register 2[0] = 0 (Total Number of Pixels is Even). <sup>†</sup><sup>†</sup> Timing when Register 2[0] = 1 (Total Number of Pixels is Odd).

<sup>t</sup>7 →

$\dagger$ Timing when Register 2[0] = 0 (Total Number of Pixels is Even).

SSTL CLK/2

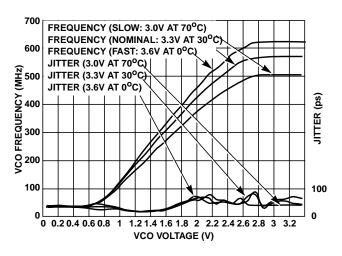

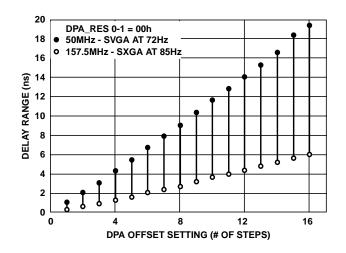

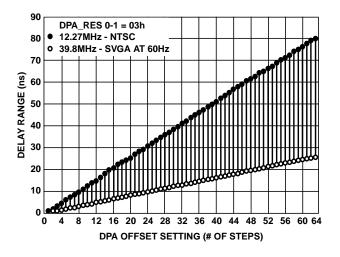

## Typical Performance Curves

FIGURE 1. VCO FREQUENCY AND JITTER vs VCO VOLTAGE

FIGURE 3. DPA DELAY vs OFFSET SETTING (32 ELEMENTS)

FIGURE 2. DPA DELAY vs OFFSET SETTING (16 ELEMENTS)

FIGURE 4. DPA DELAY vs OFFSET SETTING (64 ELEMENTS)

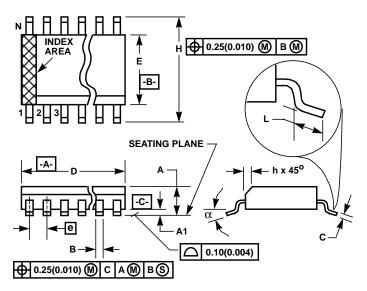

## Small Outline Plastic Packages (SOIC)

### NOTES:

- 1. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- 9. The lead width "B", as measured 0.36mm (0.014 inch) or greater

- above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch)

- 10. Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

### M24.3 (JEDEC MS-013-AD ISSUE C) 24 LEAD WIDE BODY SMALL OUTLINE PLASTIC PACKAGE

|        | INCHES MILLIMETER |                |                | <b>IETERS</b>  |       |

|--------|-------------------|----------------|----------------|----------------|-------|

| SYMBOL | MIN               | MAX            | MIN            | MAX            | NOTES |

| А      | 0.0926            | 0.1043         | 2.35           | 2.65           | -     |

| A1     | 0.0040            | 0.0118         | 0.10           | 0.30           | -     |

| В      | 0.013             | 0.020          | 0.33           | 0.51           | 9     |

| С      | 0.0091            | 0.0125         | 0.23           | 0.32           | -     |

| D      | 0.5985            | 0.6141         | 15.20          | 15.60          | 3     |

| Е      | 0.2914            | 0.2992         | 7.40           | 7.60           | 4     |

| е      | 0.05              | 0.05 BSC       |                | BSC            | -     |

| Н      | 0.394             | 0.419          | 10.00          | 10.65          | -     |

| h      | 0.010             | 0.029          | 0.25           | 0.75           | 5     |

| L      | 0.016             | 0.050          | 0.40           | 1.27           | 6     |

| Ν      | 24                |                | :              | 24             | 7     |

| α      | 0 <sup>0</sup>    | 8 <sup>0</sup> | 0 <sup>0</sup> | 8 <sup>0</sup> | -     |

Rev. 0 12/93

### All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com

## Sales Office Headquarters

### NORTH AMERICA

Intersil Corporation P. O. Box 883, Mail Stop 53-204 Melbourne, FL 32902 TEL: (407) 724-7000 FAX: (407) 724-7240

### EUROPE

Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05

### ASIA

Intersil (Taiwan) Ltd. 7F-6, No. 101 Fu Hsing North Road Taipei, Taiwan Republic of China TEL: (886) 2 2716 9310 FAX: (886) 2 2715 3029