## TOSHIBA Intelligent Power Device Silicon Monolithic Power MOS Integrated Circuit TPD7101F

#### 2 channel High-Side N-ch Power MOSFET Gate Driver

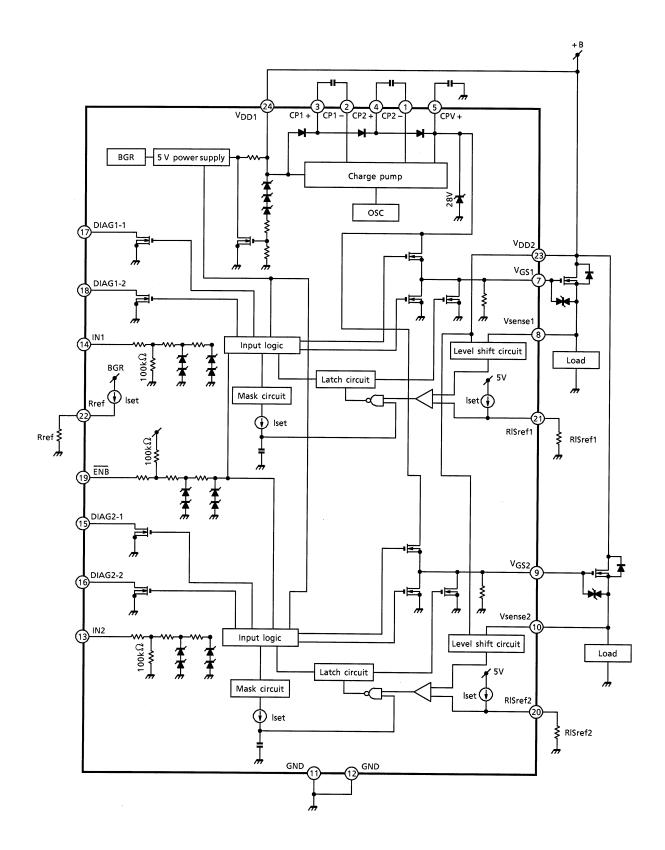

The TPD7101F is a 2 channel high-side N-ch power MOSFET gate driver. This IC contains a power MOSFET driver and power MOSFET protective and diagnostic functions, allowing easy configuration of a high-side switch for large-current applications.

#### Features

- The large-current charge pump allows for fast switching

- Power MOSFET protective and diagnostic functions are built-in. Protective functions: Overvoltage

(internal device protection), overcurrent protection, V<sub>DD</sub> voltage drop detection

\* Overvoltage is internally limited. No detection or shutdown functions are included.

Diagnostic functions: Overcurrent

- The level of overcurrent detection can set by external resistor.

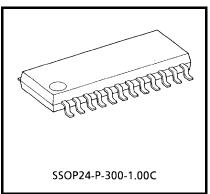

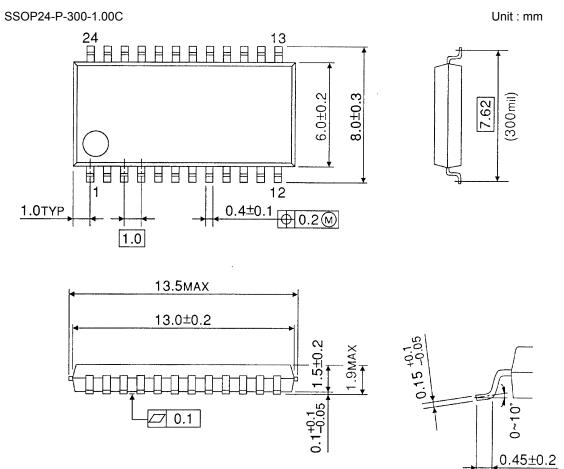

- Package: SSOP-24 (300 mil) with embossed-tape packing Due to its MOS structure, this product is sensitive to static electricity. Handle with care.

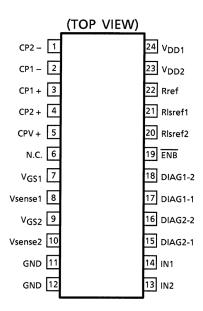

### **Pin Assignment**

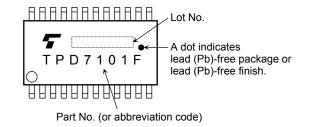

#### Marking

Weight: 0.29g(typ.)

**Block Diagram**

## **Pin Description**

| Pin No. | Symbol           | Pin Description                                                                                                                                                                                                                 |  |  |  |

|---------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1       | CP2 –            | Negative side connecting pin for the charge pump's second capacitor                                                                                                                                                             |  |  |  |

| 2       | CP 1-            | Negative side connecting pin for the charge pump's first capacitor                                                                                                                                                              |  |  |  |

| 3       | CP1 +            | Positive side connecting pin for the charge pump's first capacitor                                                                                                                                                              |  |  |  |

| 4       | CP2+             | Positive side connecting pin for the charge pump's second capacitor                                                                                                                                                             |  |  |  |

| 5       | CPV+             | Positive side connecting pin for the charge pump's third capacitor: Although about three times t V <sub>DD</sub> voltage is generated, it is limited to about 28 V by a voltage clamping circuit.                               |  |  |  |

| 6       | N.C.             | —                                                                                                                                                                                                                               |  |  |  |

| 7       | V <sub>GS1</sub> | External power MOSFET gate drive pin for ch1: This pin controls the external power MOSFET. Also, when overcurrent flows in the external power MOSFET, it shuts down the gate and is latched. It is unlatched by a low on-input. |  |  |  |

| 8       | Vsense1          | External power MOSFET monitor pin for ch1: Overcurrent is detected by comparing the difference between this and the $V_{DD2}$ pin with the reference voltage.                                                                   |  |  |  |

| 9       | V <sub>GS2</sub> | External power MOSFET gate drive pin for ch2: This pin controls the external power MOSFET. Also, when overcurrent flows in the external power MOSFET, it shuts down the gate and is latched. It is unlatched by a low on input. |  |  |  |

| 10      | Vsense2          | External power MOSFET monitor pin for ch2: Overcurrent is detected by comparing the difference between this and the $V_{DD2}$ pin with the reference voltage.                                                                   |  |  |  |

| 11      | GND              | Ground pin : shared internally with pin 12.                                                                                                                                                                                     |  |  |  |

| 12      | GND              | Shared internally with pin 11.                                                                                                                                                                                                  |  |  |  |

| 13      | IN2              | Input pin for ch2 (active high) : This pin has a pull-down resistor (100 k $\Omega$ typ.), so that even when it is open-circuited, output will not turn on inadvertently.                                                       |  |  |  |

| 14      | IN1              | Input pin for ch1 (active high) : This pin has a pull-down resistor (100 k $\Omega$ typ.), so that even when it is open-circuited, output will not turn on inadvertently.                                                       |  |  |  |

| 15      | DIAG2-1          | Diagnostic output pin for ch2 (N-ch open-drain): When the overcurrent condition is detected, its output goes low. Also, when overcurrent is detected, it remains latched until the next rising edge of input.                   |  |  |  |

| 16      | DIAG2-2          | Diagnostic output pin for ch2 (N-ch open-drain): By comparing the voltage between $V_{DD2}$ and Vsense2 pins with the set overcurrent level, it outputs external power MOSFET on / off state.                                   |  |  |  |

| 17      | DIAG1-1          | Diagnostic output pin for ch1 (N-ch open-drain): When overcurrent condition is detected, its out goes low; in this case, it also remains latched until the next rising edge of input.                                           |  |  |  |

| 18      | DIAG1-2          | Diagnostic output pin for ch1 (N-ch open-drain): By comparing the voltage between $V_{DD2}$ and Vsense1 pins with the set overcurrent level, it outputs external power MOSFET on / off state.                                   |  |  |  |

| 19      | ENB              | Chip inhibit pin (active low): By driving this pin high, all outputs can be turned off regardless of input signals. This pin has a pull-up resistor (100 k $\Omega$ typ.).                                                      |  |  |  |

| Pin No. | Symbol           | Pin Description                                                                                                                                                                                                                                          |  |  |  |

|---------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 20      | RISref2          | Overcurrent detection level setup pin for ch2: The voltage determined by the constant current set by the resistor connected to the Rref pin and the resistance of an external resistor connected to the RISref2 pin is referenced to detect overcurrent. |  |  |  |

| 21      | RISref1          | Overcurrent detection level setup pin for ch1: The voltage determined by the constant current set by the resistor connected to the Rref pin and the resistance of an external resistor connected to the RISref1 pin is referenced to detect overcurrent. |  |  |  |

| 22      | Rref             | Resistor connection pin:<br>This resistor determines the constant current used for the overcurrent detection circuit. Connect $62k\Omega$<br>(recommended) between this pin and GND.                                                                     |  |  |  |

| 23      | V <sub>DD2</sub> | External power MOSFET drain voltage detection pin.                                                                                                                                                                                                       |  |  |  |

| 24      | V <sub>DD1</sub> | Power supply pin: the internal device is protected when overvoltage is applied.                                                                                                                                                                          |  |  |  |

#### Absolute Maximum Ratings (Ta = 25°C)

| Characteristics          | Symbol           | Rating     | Unit |

|--------------------------|------------------|------------|------|

| Power supply voltage     | V <sub>DD</sub>  | 30         | V    |

| Input voltage            | V <sub>IN</sub>  | - 0.5 ~ 6  | V    |

| Diagnosis output current | IDIAG            | 2          | mA   |

| Power dissipation        | PD               | 0.8        | W    |

| Operating temperature    | T <sub>opr</sub> | - 40 ~ 110 | °C   |

| Storage temperature      | T <sub>stg</sub> | – 55 ~ 150 | °C   |

Note: Using continuously under heavy loads (e.g. the application of high temperature/current/voltage and the significant change in temperature, etc.) may cause this product to decrease in the reliability significantly even if the operating conditions (i.e. operating temperature/current/voltage, etc.) are within the absolute maximum ratings and the operating ranges.

Please design the appropriate reliability upon reviewing the Toshiba Semiconductor Reliability Handbook ("Handling Precautions"/Derating Concept and Methods) and individual reliability data (i.e. reliability test report and estimated failure rate, etc).

#### Electrical Characteristics (Unless otherwise specified, $V_{DD} = 8 \sim 18V$ , $T_j = -40$ to $110^{\circ}C$ )

| Characteristics                              | Rating                 | Pin No.                                | Test Condition                                        | Min   | Тур.            | Max             | Unit |  |

|----------------------------------------------|------------------------|----------------------------------------|-------------------------------------------------------|-------|-----------------|-----------------|------|--|

| Operating supply voltage                     | V <sub>DD</sub>        | V <sub>DD</sub>                        | _                                                     | 8     |                 | 18              | V    |  |

| Supply current                               | I <sub>DD</sub>        | V <sub>DD</sub>                        | $V_{DD}$ = 12 V, $V_{IN}$ = 0 V,<br>CP = 0.01 µF      | _     | _               | 10              | mA   |  |

| Input voltage                                | V <sub>IN (1)</sub>    | IN1, IN2                               | V <sub>DD</sub> = 12 V, V <sub>GS</sub> = "H"         | 3.5   |                 |                 | V    |  |

| input voltage                                | V <sub>IN (2)</sub>    | 1111, 1112                             | $V_{DD}$ = 12 V, $V_{GS}$ = "L"                       | —     |                 | 1.5             |      |  |

|                                              | I <sub>IN (1)</sub>    | IN1, IN2                               | V <sub>DD</sub> = 12 V, V <sub>IN</sub> = 5 V         | —     | —               | 200             |      |  |

| Input current                                | I <sub>IN (2)</sub>    |                                        | V <sub>DD</sub> = 12 V, V <sub>IN</sub> = 0 V         | - 1   |                 | 1               | μΑ   |  |

| Input current                                | I <sub>ENB</sub> (1)   | ENB                                    | $V_{DD}$ = 12 V, $V_{\overline{ENB}}$ = 5 V           | - 45  |                 | —               |      |  |

|                                              | I <sub>ENB</sub> (2)   |                                        | V <sub>DD</sub> = 12 V, V <sub>ENB</sub> = 0 V        | - 250 | _               | —               |      |  |

| Output voltage                               | V <sub>OH</sub>        |                                        | V <sub>DD</sub> = 12 V, V <sub>IN</sub> = 5 V         | _     | Vsense<br>+ 15* | Vsense<br>+ 19* | V    |  |

|                                              | V <sub>OL</sub>        | V <sub>GS1</sub>                       | V <sub>DD</sub> = 12 V, V <sub>IN</sub> = 0 V         | _     |                 | 0.4             | A    |  |

| Output current                               | ЮН                     | VGS1<br>VGS2                           | $V_{DD}$ = 12 V, $V_{IN}$ = 5 V,<br>CP = 0.01 $\mu$ F | _     | 0.1             | —               |      |  |

|                                              | I <sub>OL</sub>        |                                        | $V_{DD}$ = 12 V, $V_{IN}$ = 0 V,<br>CP = 0.01 µF      | _     | 0.1             | _               |      |  |

| Overcurrent detection resistance setup range | RISref                 | RISref                                 | _                                                     | 10    | 20              | 40              | KΩ   |  |

| Constant current source setup pin voltage    | VRref                  | Rref                                   | Rref = 62 kΩ                                          | 1.17  | 1.30            | 1.43            | V    |  |

|                                              | V <sub>DS(ON)(1)</sub> |                                        | Rref = 62 kΩ<br>RISref = 10 kΩ                        | 0.16  | 0.20            | 0.24            | V    |  |

| Overcurrent detection voltage                | V <sub>DS(ON)(2)</sub> | V <sub>DD2</sub><br>Vsense1<br>Vsense2 | Rref = 62 kΩ<br>RISref = 20 kΩ                        | 0.32  | 0.40            | 0.48            |      |  |

|                                              | V <sub>DS(ON)(3)</sub> |                                        | Rref = 62 kΩ<br>RISref = 40 kΩ                        | 0.64  | 0.80            | 0.96            |      |  |

| Diagnostic output current                    | IDH                    | DIAG1                                  | V <sub>DD</sub> = 12 V,<br>VDIAG = 5 V                | _     | _               | 10              | μA   |  |

| Diagnostic output voltage                    | V <sub>DL</sub>        | DIAG2                                  | V <sub>DD</sub> = 12 V, I <sub>DL</sub> = 1 mA        | _     |                 | 0.6             | V    |  |

| Power supply drop<br>detection voltage       | VDDUV1-                | \/                                     | _                                                     | 6.3   | 6.7             | 7.3             |      |  |

| Power supply drop<br>detection reset voltage | VDDUV1+                |                                        | _                                                     | 6.6   | 7.2             | 7.8             | V    |  |

| Undervoltage protection                      | VDDUV2                 |                                        |                                                       | —     |                 | 4.5             |      |  |

| Switching time                               | ton                    | V <sub>GS1</sub>                       | V <sub>DD</sub> = 12V, C = 3000 pF                    |       | 2               | 5               | 116  |  |

|                                              | tOFF                   | V <sub>GS2</sub>                       | ν <u>Π</u> – 12ν, C – 3000 μr                         |       | 2               | 5               | μS   |  |

\*: Vsense denotes the Vsense pin voltage. The following equation is used to calculate overcurrent detection resistance (RISref):

$RISref = Rref \times R_{DS} (ON) \times I_D / Vrref = Rref \times V_{DS} (ON) / VRref$

| R <sub>DS</sub> (ON) | : ON-resistance of external power MOSFET                                 |  |  |  |

|----------------------|--------------------------------------------------------------------------|--|--|--|

| ID                   | : drain current of external power MOSFET                                 |  |  |  |

| V <sub>DS (ON)</sub> | : ON-voltage of external power MOSFET                                    |  |  |  |

| Rref                 | : external resistor connected to Rref pin (used to set constant current) |  |  |  |

| VRref                | : Rref pin voltage                                                       |  |  |  |

|                      | V <sub>DS</sub> (ON)<br>Rref                                             |  |  |  |

### Truth Table

| In | ENB | V <sub>GS</sub> | DIAG*-1             | DIAG∗-2 | State                     |  |

|----|-----|-----------------|---------------------|---------|---------------------------|--|

| L  | Н   | L               | н                   | Н       |                           |  |

| Н  | Н   | L               | н                   | н       | Normal                    |  |

| L  | L   | L               | н                   | н       | normai                    |  |

| н  | L   | Н               | H (Note 1)          | L       |                           |  |

| L  | L   | L               | н                   | н       | Quanualtaga               |  |

| н  | L   | Н               | H (Note 1)          | L       | Overvoltage               |  |

| L  | L   | L               | L (Note 1 / Note 2) | н       | Overcurrent               |  |

| н  | L   | L               | L (Note 1)          | н       |                           |  |

| L  | L   | L               | н                   | н       | Supply voltage drop       |  |

| н  | L   | Н               | н                   | н       |                           |  |

| L  | L   | L               | н                   | н       | Lindon voltage protection |  |

| н  | L   | L               | н                   | н       | Undervoltage protection   |  |

| L  | L   | L               | н                   | L       | Power MOSFET shorted      |  |

| Н  | L   | Н               | Н                   | L       |                           |  |

Note 1: Since overcurrent is detected by checking the drain-to-source voltage of the power MOSFET, there is a possibility of erroneous detection of overcurrent for a while after the input is driven high but before the power MOSFET is turned on, during which interval the drain-to-source voltage is high. To prevent this erroneous detection, DIAG detection is disabled for 15  $\mu$ s (typ.) by a mask circuit. This masking time depends on the constant current determined by the internal capacitor and Rref. (The masking time is 15  $\mu$  when Rref = 62 k $\Omega$ .)

Note 2: After overcurrent is detected, DIAG remains latched until the next rising edge of input.

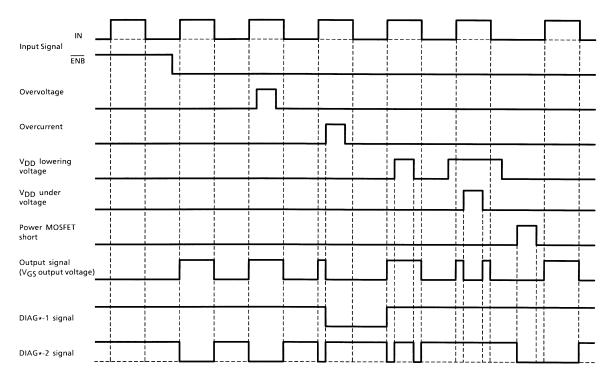

## **Timing Chart**

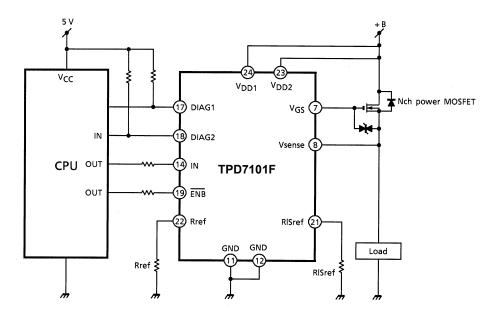

## **Application Circuit 1**

Monitoring Power MOSFET drain-source voltage

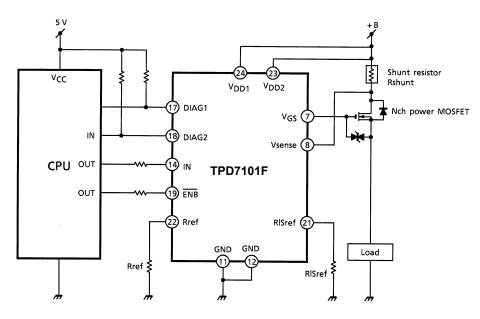

### **Application Circuit 2**

Monitoring voltage between shunt resistors (for detecting overcurrent with high accuracy)

### **Moisture-proof Packing**

After the pack is opened, use the devices in a 30°C, 60% RH environment, and within 48 hours.

Embossed-tape packing cannot be baked. Devices so packed must be used within their allowable time limits after unpacking, as specified on the packing.

Standard tape packing quantity: 2000 devices / reel (EL1)

## Package Dimensions

Weight: 0.29g (typ.)

#### **RESTRICTIONS ON PRODUCT USE**

20070701-EN

- The information contained herein is subject to change without notice.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc.

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.).These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in his document shall be made at the customer's own risk.

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations.

- The information contained herein is presented only as a guide for the applications of our products. No

responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which

may result from its use. No license is granted by implication or otherwise under any patents or other rights of

TOSHIBA or the third parties.

- Please contact your sales representative for product-by-product details in this document regarding RoHS compatibility. Please use these products in this document in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances. Toshiba assumes no liability for damage or losses occurring as a result of noncompliance with applicable laws and regulations.