# TOSHIBA

# 32bit TX System RISC TX19 family

# TMP1942FDU/XBG

Rev1.0 March 29, 2007

# 32-Bit RISC Microprocessor TX19 Family TMP1942FDU/FDXBG

## 1. Features

The TX19 is a family of high-performance 32-bit microprocessors that offers the speed of a 32-bit RISC solution with the added advantage of a significantly reduced code size of a 16-bit architecture. The instruction set of the TX19 includes as a subset the 32-bit instructions of the TX39, which is based on the MIPS R3000A<sup>TM</sup> architecture. Additionally, the TX19 supports the MIPS16 Application-Specific Extensions (ASE) for improved code density.

The TMP1942 is built on a TX19 core processor and a selection of intelligent peripherals. The TMP1942 is suitable for low-voltage and low-power applications.

Features of the TMP1942 include the following:

#### **RESTRICTIONS ON PRODUCT USE**

The information contained herein is subject to change without notice. 021023\_D

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can

malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when

utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations

in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most

recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for

Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc. 021023\_A

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk. 021023\_B

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations. 060106\_Q

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third parties. 070122\_C

- The products described in this document are subject to foreign exchange and foreign trade control laws. 060925\_E

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions. 030619\_S

- (1) TX19 core processor

- 1) Two instruction set architecture (ISA) modes: 16-bit ISA for code efficiency and 32-bit ISA for performance.

- The 16-bit ISA is object-code compatible with the code-efficient MIPS16<sup>™</sup> ASE.

- The 32-bit ISA is object-code compatible with the high-performance TX39 family.

- 2) High performance combined with low power consumption

- High performance

- Single clock cycle execution for most instructions

- 3-operand arithmetic instructions for high instruction throughput

- 5-stage pipeline

- On-chip high-speed memory

- DSP function: Executes 32-bit x 32-bit multiply operations in a single clock cycle.

- Low power consumption

- Optimized design using a low-power cell library

- Programmable standby modes in which processor clocks are stopped

- 3) Fast interrupt response suitable for real-time control

- Distinct starting locations for each interrupt service routine

- Automatically generated vectors for each interrupt source

- Automatic updates of the interrupt mask level

- (2) On-chip RAM:

TMP1942FDU/FDXB 20 KB

On-chip FROM

TMP1942FDU/FDXB 512 KB

ROM correction function (8 words x 4 blocks)

(In the flash-version product, only the registers exist and no correction is performed.)

- (3) External memory expansion

- 16-Mbyte off-chip address space for code and data

- External bus interface with dynamic bus sizing for 8-bit and 16-bit data ports

- (4) 4-channel DMA controller

- Interrupt- or software-triggered

- (5) 6-channel 8-bit PWM timer

- 12-channel 8-bit interval timer

- 6-channel 16-bit interval timer

- 6-channel 8-bit PPG output

- (6) 14-channel 16-bit timer

- Two channels support two-phase input pulse counter mode.

- (7) 1-channel RTC timer

- (8) 5-channel general-purpose serial interface

- Supports both UART and synchronous transfer modes.

- (9) 1-channel serial bus interface

- Either I<sup>2</sup>C bus mode or clock-synchronous mode can be selected.

- (10) 16-channel 10-bit A/D converter (with internal sample/hold)

- Conversion time: 2 µs (throughput), 4 µs to 5 µs (latency)

- (11) 3-channel 10-bit D/A converter

- (12) Watchdog timer

- (13) 4-channel chip select/wait controller

(14) Interrupt sources

- 4 CPU interrupts: software interrupt instruction

- 45 internal interrupts: 7 priority levels, with the exception of the watchdog timer interrupt

- 29 external interrupts: 7 priority levels, with the exception of the NMI interrupt Of the 29, 14 are used for key-on wakeup and share an interrupt vector. INTB, INTC, INTD, and INTE are extended interrupts which share an interrupt vector and are distinguished by flags. Therefore, a total of 13 interrupt sources are available.

- (15) 108-pin input/output ports

- (16) Three standby (HALT) modes

- IDLE, SLEEP, STOP

- (17) Dual clocks

- RTC clock: Low-speed clock (32.768 kHz)

- (18) Clock generator

- On-chip PLL (x4)

- Clock gear: Divides the high-speed clock to 1/2, 1/4, or 1/8.

(19) Operating voltage range: 2.7 V to 3.6 V

2.7 V to 3.6 V or 4.5 V to 5.25 V for Port C and Port F supporting 5-V operation

(20) Operating frequency

- 32 MHz (Vcc  $\geq$  3.0 V) (Interleave mode)

- 28 (Vcc ≥ 2.7 V)

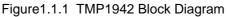

(21) Packages

- 144-pin QFP (16 mm ×16 mm × 1.4 mm thick, 0.4 mm pitch): TMP1942FDU

- 177-pin CSP (13 mm × 13 mm × 1.4 mm thick, 0.8 mm pitch): TMP1942FDXBG

Note: The TMP1942FDXBG packaged in a 177-pin CSP is under development.

#### 2. **Signal Descriptions**

This section contains pin assignments for the TMP1942FD as well as brief descriptions of the TMP1942FD input and output signals.

#### 2.1 **Pin Assignments**

Table 2.1.1 lists the pin assignments for the TMP1942FD in a 144-pin package.

144 143 142 141 140 139 138 137 136 135 134 133 132 131 130 129 128 127 126 125 124 123 122 121 120 119 118 117 116 115 114 113 112 111 110 109

| Pin # | Pin Function   | Pin #. | Pin Function | Pin # | Pin Function        | Pin # | Pin Function            |

|-------|----------------|--------|--------------|-------|---------------------|-------|-------------------------|

| 1     | VREFH          | 37     | P11/AD9/A9   | 73    | P90/KEY8/DCLK       | 109   | CVCC                    |

| 2     | VREFL          | 38     | P12/AD10/A10 | 74    | P91/KEY9/PCST2      | 110   | X2                      |

| 3     | P50/AN0        | 39     | P13/AD11/A11 | 75    | P92/TB4OUT/PCST1    | 111   | CVSS                    |

| 4     | P51/AN1        | 40     | P14/AD12/A12 | 76    | P93/TB5OUT/PCST0    | 112   | X1                      |

| 5     | P52/AN2        | 41     | P15/AD13/A13 | 77    | P94/TB6OUT/SDAO/TPC | 113   | TEST1                   |

| 6     | P53/AN3        | 42     | P16/AD14/A14 | 78    | P95/TB7IN0/DBGE     | 114   | RESET                   |

| 7     | DAVCC          | 43     | P17/AD15/A15 | 79    | P96/TB7IN1/ DINT    | 115   | PD6/XT1                 |

| 8     | DAVSS          | 44     | P20/A0/A16   | 80    | P97/TB7OUT/DRESET   | 116   | PD7/XT2                 |

| 9     | DAREH          | 45     | P21/A1/A17   | 81    | DVCC3               | 117   | NMI                     |

| 10    | DAOUT0         | 46     | P22/A2/A18   | 82    | PA0/TB0IN0/INT3     | 118   | BW0                     |

| 11    | DAOUT1         | 47     | P23/A3/A19   | 83    | PA1/TB0IN1/INT4     | 119   | PB0/TB2IN0/INTB         |

| 12    | DAOUT2         | 48     | P24/A4/A20   | 84    | PA2/TB0OUT          | 120   | PB1/TB2IN1/INTC         |

| 13    | P54/AN4        | 49     | P25/A5/A21   | 85    | PA3/TB1IN0/INT5     | 121   | PB2/TB2OUT/TB4IN0       |

| 14    | P55/AN5        | 50     | P26/A6/A22   | 86    | PA4/TB1IN1/INT6     | 122   | PB3/TB3IN0/INTD         |

| 15    | P56/AN6        | 51     | P27/A7/A23   | 87    | PA5/TB1OUT          | 123   | PB4/TB3IN1/INTE         |

| 16    | P57/AN7/ ADTRG | 52     | TEST0        | 88    | PA6/TA1OUT          | 124   | PB5/TB3OUT/TB4IN1       |

| 17    | P60/AN8/KEY0   | 53     | PLLOFF       | 89    | PA7/TA0IN/KEYA      | 125   | PB6/TA3OUT              |

| 18    | DVSS           | 54     | FVSS         | 90    | DVSS                | 126   | DVSS                    |

| 19    | P61/AN9/KEY1   | 55     | ALE          | 91    | RSTPUP              | 127   | DVCC3                   |

| 20    | P62/AN10/KEY2  | 56     | DVCC3        | 92    | PC0/TA4IN/INT8      | 128   | PB7/TA2IN/INT7/KEYB     |

| 21    | P63/AN11/KEY3  | 57     | BW1          | 93    | PC1/TA6IN/INT9      | 129   | PD0/TXD0/TB9IN0         |

| 22    | P64/AN12/KEY4  | 58     | P30/ RD      | 94    | PC2/TA8IN/INTA      | 130   | PD1/RXD0/TB9IN1         |

| 23    | P65/AN13/KEY5  | 59     | P31/ WR      | 95    | PC3/TA5OUT          | 131   | PD2/SCLK0/ CTS0         |

| 24    | P66/AN14/KEY6  | 60     | P32/HWR      | 96    | PC4/TAAIN           | 132   | PD3/TXD1/TBAIN0         |

| 25    | P67/AN15/KEY7  | 61     | P33/ WAIT    | 97    | PC5/TA7OUT          | 133   | PD4/RXD1/TBAIN1         |

| 26    | DVCC3          | 62     | P34/BUSRQ    | 98    | PC6/TB8IN0/KEYC     | 134   | PD5/SCLK1/ CTS1 /TABOUT |

| 27    | P00/AD0        | 63     | P35/BUSAK    | 99    | PC7/TB8IN1/TA9OUT   | 135   | PE0/TXD3                |

| 28    | P01/AD1        | 64     | P36/R/W      | 100   | DVCC52              | 136   | PE1/RXD3                |

| 29    | P02/AD2        | 65     | P37/DSU      | 101   | PF0/TXD5            | 137   | PE2/SCLK3/ CTS3         |

| 30    | P03/AD3        | 66     | DVSS         | 102   | PF1/RXD5/KEYD       | 138   | PE3/TXD4                |

| 31    | P04/AD4        | 67     | FVCC         | 103   | PF2/SCLK5/ CTS5     | 139   | PE4/RXD4                |

| 32    | P05/AD5        | 68     | P40/ CS0     | 104   | PF3/SCK             | 140   | PE5/SCLK4/CTS4          |

| 33    | P06/AD6        | 69     | P41/CS1      | 105   | PF4/SO/SDA          | 141   | PE6/INT1/BOOT           |

| 34    | P07/AD7        | 70     | P42/ CS2     | 106   | PF5/SI/SCL          | 142   | PE7/INT2/INTLV          |

| 35    | DVSS           | 71     | P43/ CS3     | 107   | PF6/INT0            | 143   | AVCC                    |

| 36    | P10/AD8/A8     | 72     | P44/SCOUT    | 108   | DVCC51              | 144   | AVSS                    |

| Table 2.1.1 144-Pin LQFP Pin Assignments |

|------------------------------------------|

|------------------------------------------|

|    | -  | -  | -  |    | -  |    | -        | -  |     | -   | -   | -   | -   |     |

|----|----|----|----|----|----|----|----------|----|-----|-----|-----|-----|-----|-----|

| A1 | A2 | A3 | A4 | A5 | A6 | A7 | A8       | A9 | A10 | A11 | A12 | A13 | A14 | A15 |

| B1 | B2 | B3 | B4 | B5 | B6 | B7 | B8       | B9 | B10 | B11 | B12 | B13 | B14 | B15 |

| C1 | C2 | C3 | C4 | C5 | C6 | C7 | C8       | C9 | C10 | C11 | C12 | C13 | C14 | C15 |

| D1 | D2 | D3 | D4 | D5 | D6 | D7 | D8       | D9 | D10 | D11 | D12 | D13 | D14 | D15 |

| E1 | E2 | E3 | E4 |    |    |    |          |    |     |     | E12 | E13 | E14 | E15 |

| F1 | F2 | F3 | F4 |    |    |    |          |    |     |     | F12 | F13 | F14 | F15 |

| G1 | G2 | G3 | G4 |    |    |    |          |    |     |     | G12 | G13 | G14 | G15 |

| H1 | H2 | H3 | H4 |    |    |    | $\times$ |    |     |     | H12 | H13 | H14 | H15 |

| J1 | J2 | J3 | J4 |    |    |    |          |    |     |     | J12 | J13 | J14 | J15 |

| K1 | K2 | K3 | K4 |    |    |    |          |    |     |     | K12 | K13 | K14 | K15 |

| L1 | L2 | L3 | L4 |    |    |    |          |    |     | /   | L12 | L13 | L14 | L15 |

| M1 | M2 | M3 | M4 | M5 | M6 | M7 | M8       | M9 | M10 | M11 | M12 | M13 | M14 | M15 |

| N1 | N2 | N3 | N4 | N5 | N6 | N7 | N8       | N9 | N10 | N11 | N12 | N13 | N14 | N15 |

| P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8       | P9 | P10 | P11 | P12 | P13 | P14 | P15 |

| R1 | R2 | R3 | R4 | R5 | R6 | R7 | R8       | R9 | R10 | R11 | R12 | R13 | R14 | R15 |

| Pin # | Pin Function                | Pin # | Pin Function            | Pin # |                 | Pin # | Pin Function |

|-------|-----------------------------|-------|-------------------------|-------|-----------------|-------|--------------|

| A1    | VREFL                       | D1    | P50/AN0                 | H13   | NC              | N4    | P16/AD14/A14 |

| A2    | AVSS                        | D2    | DAVSS                   | H14   | NC              | N5    | P21/A1/A17   |

| A3    | AVCC                        | D3    | P52/AN2                 | H15   | DVSS            | N6    | P25/A5/A21   |

| A4    | PE7/INT2/INTLV              | D4    | P51/AN1                 | J1    | P67/AN15/KEY7   | N7    | DVSS         |

| A5    | PE3/TXD4                    | D5    | PE0/TXD3                | J2    | P65/AN13/KEY5   | N8    | TEST0        |

| A6    | TCK (JTAG)                  | D6    | PD3/TXD1/TBAIN0         | J3    | P66/AN14/KEY6   | N9    | P30/ RD      |

| A7    | PD2/SCLK0/ CTS0             | D7    | PB7/TA2IN/INT7/<br>KEYB | J4    | P64/AN12/KEY4   | N10   | P32/HWR      |

|       | PB5/TB3OUT/<br>TB4IN1       | D8    | DVSS                    | J12   | PA6/TA1OUT      | N11   | P37/DSU      |

| A9    | PB1/TB2IN1/INTC             | D9    | PB2/TB2OUT/<br>TB4IN0   | J13   | PA7/TA0IN/KEYA  | N12   | DVSS         |

| A10   | PD7/TX2                     | D10   | NMI                     | J14   | NC              | N13   | P41/CS1      |

| A11   | PD6/TX1                     | D11   | NC                      | J15   | PA5/TB1OUT      | N14   | P91/KEY9     |

| A12   | X1                          | D12   | NC                      | K1    | P01/AD1         | N15   | NC           |

| A13   | X2                          | D13   | PF1/RXD5/KEYD           | K2    | DVCC3           | P1    | NC           |

| A14   | CVCC                        | D14   | PF3/SCK                 | K3    | NC              | P2    | P10/AD8/A8   |

| A15   | NC                          | D15   | PF6/INT0                | K4    | NC              | P3    | P12/AD10/A10 |

| B1    | NC                          | E1    | DAVCC                   | K12   | PA2/TB0OUT      | P4    | P20/A0/A16   |

| B2    | NC                          | E2    | DAOUT0                  | K13   | PA3/TB1IN0/INT5 | P5    | P22/A2/A18   |

| B3    | PE6/INT1                    | E3    | DAREFH                  | K14   | PA4/TB1IN1/INT6 | P6    | P26/A6/A22   |

| B4    | PE4/RXD4                    | E4    | P53/AN3                 | K15   | PA1/TB0IN1/INT4 | P7    | TDO (JTAG)   |

| B5    | TRST (JTAG)                 | E5    | NC(not bonded)          | L1    | P04/AD4         | P8    | ALE          |

|       | PD5/SCLK1/ CTS1 /<br>TABOUT | E12   | PC6/TB8IN0/KEYC         | L2    | P02/AD2         | P9    | BW1          |

| B7    | PD0/TXD0/TB9IN0             | E13   | DVCC52                  | L3    | TMS (JTAG)      | P10   | P33/ WAIT    |

| B8    | DVCC3                       | E14   | PF0/TXD5                | L4    | P00/AD0         | P11   | TDI (JTAG)   |

| B9    | PB4/TB3IN1/INTE             | E15   | PF2/SCLK5/ CTS5         | L12   | P97/TB7OUT      | P12   | P40/ CS0     |

| B10   | PB0/TB2IN0/INTB             | F1    | DAOUT1                  | L13   | DVCC3           | P13   | P42/ CS2     |

| B11   | NC                          | F2    | P55/AN5                 | L14   | PA0/TB0IN0/INT3 | P14   | P44/SCOUT    |

| B12   | RESET                       | F3    | P54/AN4                 | L15   | P96/TB7IN1      | P15   | NC           |

| B13   | CVSS                        | F4    | DAOUT2                  | M1    | P07/AD7         | R1    | P11/AD9/A9   |

| B14   | DVCC51                      | F12   | PC2/TA8IN/INTA          | M2    | P05/AD5         | R2    | NC           |

| B15   | NC                          | F13   | PC4/TAAIN               | М3    | P03/AD3         | R3    | NC           |

| C1    | VREFH                       | F14   | PC5/TA7OUT              | M4    | P14/AD12/A12    | R4    | P13/AD11/A11 |

| C2    | NC                          | F15   | PC7/TB8IN1/<br>TA9OUT   | M5    | P15/AD13/A13    | R5    | P17/AD15/A15 |

| C3    | PE5/SCLK4/ CTS4             | G1    | P56/AN6                 | M6    | P24/A4/A20      | R6    | P23/A3/A19   |

| C4    | PE2/SCLK3/ CTS3             | G2    | P61/AN9/KEY1            | M7    | PLLOFF          | R7    | P27/A7/A23   |

| C5    | PE1/RXD3                    | G3    | NC                      | M8    | NC              | R8    | NC           |

| C6    | PD4/RXD1/TBAIN1             | G4    | P60/AN8/KEY0            | M9    | DVCC3           | R9    | P31/ WR      |

| C7    | PD1/RXD0/TB9IN1             | G12   | PC0/TA4IN/INT8          | M10   | P34/BUSRQ       | R10   | P35/ BUSAK   |

| C8    | PB6/TA3OUT                  | G13   | PC1/TA6IN/INT9          | M11   | P36/ R / W      | R11   | DVCC3        |

| C9    | PB3/TB3IN0/INTD             | G14   | NC                      | M12   | P93/TB5OUT      | R12   | P43/ CS3     |

| C10   | BW0                         | G15   | PC3/TA5OUT              | M13   | P94/TB6OUT      | R13   | NC           |

| C11   | NC                          | H1    | DVSS                    | M14   | P95/TB7IN0      | R14   | NC           |

| C12   | TEST1                       | H2    | P63/AN11/KEY3           | M15   | P92/TB4OUT      | R15   | P90/KEY8     |

|       | PF4/SO/SDA                  | H3    | P57/AN7/ ADTRG          | N1    | NC              |       |              |

|       | PF5/SI/SCL                  | H4    | P62/AN10/KEY2           | N2    | DVSS            |       |              |

|       | NC                          |       | RSTPUP                  | N3    | P06/AD6         |       |              |

| 010   |                             | 1114  |                         | 110   |                 | ļ     | l            |

Table 2.1.2 177-Pin CSP Pin Assignments

# 2.2 Pin Usage Information

Table 2.2.1 lists the input and output pins of the TMP1942FD, including alternate pin names and functions for multi-function pins.

| Pin Name         | # of Pins | Туре         | Function                                                                                  |

|------------------|-----------|--------------|-------------------------------------------------------------------------------------------|

| P00-P07          | 8         | Input/Output | Port 0: Individually programmable as input or output                                      |

| AD0-AD7          |           | Input/Output | Address (Lower): Bits0-7 of the address/data bus                                          |

| P10-P17          | 8         | Input/Output | Port 1: Individually programmable as input or output                                      |

| AD8-AD15         |           | Input/Output | Address/Data (Upper): Bits 8-15 of the address/data bus                                   |

| A8-A15           |           | Output       | Address: Bits 8-15 of the address bus                                                     |

| P20-P27          | 8         | Input/Output | Port 2: Individually programmable as input or output                                      |

| A0-A7            |           | Output       | Address: Bits 0-7 of the address bus                                                      |

| A16-A23          |           | Output       | Address: Bits 16-23 of the address bus                                                    |

| P30              | 1         | Output       | Port 30: Output-only                                                                      |

| RD               |           | Output       | Read Strobe: Asserted during a read operation from an external memory device              |

| P31              | 1         | Output       | Port 31: Output-only                                                                      |

| WR               |           | Output       | Write Strobe: Asserted during a write operation on D0-D7                                  |

| P32              | 1         | Input/Output | Port 32: Programmable as input or output (with internal pull-up resistor)                 |

| HWR              |           | Output       | Higher Write Strobe: Asserted during a write operation on D8-D15                          |

| P33              | 1         | Input/Output | Port 33: Programmable as input or output (with internal pull-up resistor)                 |

| WAIT             |           | Input        | Wait: Causes the CPU to suspend external bus activity                                     |

| P34              | 1         | Input/Output | Port 34: Programmable as input or output (with internal pull-up resistor)                 |

| BUSRQ            |           | Input        | Bus Request: Asserted by an external bus master to request bus mastership                 |

| P35              | 1         | Input/Output | Port 35: Programmable as input or output (with internal pull-up resistor)                 |

| BUSAK            |           | Output       | Bus Acknowledge: Indicates that the CPU has relinquished the bus in response to           |

|                  |           |              | BUSRQ                                                                                     |

| P36              | 1         | Input/Output | Port 36: Programmable as input or output (with internal pull-up resistor)                 |

| $R/\overline{W}$ |           | Output       | Read/Write: Indicates the direction of data transfer on the bus: 1 = read or dummy cycle, |

|                  |           |              | 0 = write cycle                                                                           |

| P37              | 1         | Input/Output | Port 37: Programmable as input or output (with internal pull-up resistor)                 |

| DSU              |           | Input        | DSU enable signal: DSU is enabled when this pin is sampled low at the rising edge of      |

|                  |           |              | RESET . To enable DSU, this pin should be pulled down. (Flash version only)               |

| P40              | 1         | Input/Output | Port 40: Programmable as input or output (with internal pull-up resistor)                 |

| CSO              |           | Output       | Chip Select 0: Asserted low to enable external devices at programmed addresses            |

| P41              | 1         | Input/Output | Port 41: Programmable as input or output (with internal pull-up resistor)                 |

| CS1              |           | Output       | Chip Select 1: Asserted low to enable external devices at programmed addresses            |

| P42              | 1         | Input/Output | Port 42: Programmable as input or output (with internal pull-up resistor)                 |

| CS2              |           | Output       | Chip Select 2: Asserted low to enable external devices at programmed addresses            |

| P43              | 1         | Input/Output | Port 43: Programmable as input or output (with internal pull-up resistor)                 |

|                  |           | Output       | Chip Select 3: Asserted low to enable external devices at programmed addresses            |

| P44              | 1         | Input/Output | Port 44: Programmable as input or output                                                  |

| SCOUT            |           | Output       | System Clock Output: Drives out a clock signal at the same frequency as the CPU clock     |

|                  |           | o alp at     | (high-speed or low-speed)                                                                 |

| P50-P57          | 8         | Input        | Port 5: Input-only                                                                        |

| AN0-AN7          |           | Input        | Analog Input: Input to the on-chip A/D converter                                          |

| ADTRG            |           | Input        | External A/D trigger pin for starting an A/D conversion (multiplexed with P57)            |

| P60-P67          | 1         | Input/Output | Port 6: Input-only                                                                        |

| AN8-AN15         |           | Input        | Analog Input: Input to the on-chip A/D converter                                          |

| KEY0-KEY7        |           | Input        | Key-On Wakeup Input (dynamic pull-up selectable) (with internal pull-up resistor)         |

| P90              | 1         | Input/Output | Port 90: Programmable as input or output                                                  |

| DSU (DCLK)       | '         | Output       | DSU pin                                                                                   |

| KEY8             |           | Input        | Key-On Wakeup Input (dynamic pull-up selectable) (with internal pull-up resistor)         |

| P91              | 1         | Input/Output | Port 91: Programmable as input or output                                                  |

| DSU (PCST2)      |           | Output       | DSU pin                                                                                   |

| 200 (10012)      | 1         | Sulpui       | Key-On Wakeup Input (dynamic pull-up selectable) (with internal pull-up resistor)         |

| Table 2.2.1 | Pin | Names     | and | Functions |

|-------------|-----|-----------|-----|-----------|

|             |     | 1 Junio J | ana |           |

| Pin Name     | # of Pins | Туре           | Function                                                                                                             |

|--------------|-----------|----------------|----------------------------------------------------------------------------------------------------------------------|

| P92          | 1         | Input/Output   | Port 92: Programmable as input or output                                                                             |

| DSU (PCST1)  |           | Output         | DSU pin                                                                                                              |

| TB40UT       |           | Output         | 16-Bit Timer 4 Output: Output from 16-bit Timer 4                                                                    |

| P93          | 1         | Input/Output   | Port 93: Programmable as input or output                                                                             |

| DSU (PCST0)  |           | Output         | DSU pin                                                                                                              |

| TB5OUT       |           | Output         | 16-Bit Timer 5 Output: Output from 16-bit Timer 5                                                                    |

| P94          | 1         | Input/Output   | Port 94: Programmable as input or output                                                                             |

| DSU          |           | Output         | DSU pin                                                                                                              |

| (SDAO/TPC)   |           |                |                                                                                                                      |

| TB6OUT       |           | Output         | 16-Bit Timer 6 Output: Output from 16-bit Timer 6                                                                    |

| P95          | 1         | Input/Output   | Port 95: Programmable as input or output                                                                             |

| DSU (DBGE)   |           | Input          | DSU pin                                                                                                              |

| TB7IN0       |           |                | 16-Bit Timer 7 Input 0: Count/capture trigger input to 16-bit Timer 7                                                |

| P96          | 1         | Input/Output   | Port 96: Programmable as input or output                                                                             |

| DSU ( DINT ) |           | Input          | DSU pin                                                                                                              |

| TB7IN1       |           |                | 16-Bit Timer 7 Input 0: Capture trigger input to 16-bit Timer 7                                                      |

| P97          | 1         | Input/Output   | Port 97: Programmable as input or output                                                                             |

| DSU(DRESET)  |           | Input          | DSU pin                                                                                                              |

| TB7OUT       |           | Output         | 16-Bit Timer 7 Output: Output from 16-bit Timer 7                                                                    |

| PA0          | 1         | Input/Output   | Port A0: Programmable as input or output                                                                             |

| TB0IN0       |           | Input          | 16-Bit Timer 0 Input 0: Count/capture trigger input to 16-bit Timer 0                                                |

| INT3         |           | Input          | Interrupt Request 3: Programmable as high-level, low-level, rising-edge or falling-edge sensitive                    |

| PA1          | 1         | Input/Output   | Port A1: Programmable as input or output                                                                             |

| TB0IN1       |           | Input          | 16-Bit Timer 0 Input 1: Capture trigger input to 16-bit Timer 0                                                      |

| INT4         |           | Input          | Interrupt Request 4: Programmable to be high-level, low-level, rising-edge or falling edge sensitive                 |

| PA2          | 1         | Input/Output   | Port A2: Programmable as input or output                                                                             |

| TB0OUT       |           | Output         | 16-Bit Timer 0 Output: Output from 16-bit Timer 0                                                                    |

| PA3          | 1         | Input/Output   | Port A3: Programmable as input or output                                                                             |

| TB1IN0       |           | Input          | 16-Bit Timer 1 Input 0: Count/capture trigger input to 16-bit Timer 1                                                |

| INT5         |           | Input          | Interrupt Request 5: Programmable to be high-level, low-level, rising-edge or falling-edge sensitive                 |

| PA4          | 1         | Input/Output   | Port A4: Programmable as input or output                                                                             |

| TB1IN1       |           | Input          | 16-Bit Timer 1 Input 1: Capture trigger input to 16-bit Timer 1                                                      |

| INT6         |           | Input          | Interrupt Request 6: Programmable to be high-level, low-level, rising-edge or falling-edge sensitive                 |

| PA5          | 1         | Input/Output   | Port A5: Programmable as input or output                                                                             |

| TB1OUT       |           | Output         | 16-Bit Timer 1 Output: Output from 16-bit Timer 1                                                                    |

| PA6          | 1         | Input/Output   | Port A6: Programmable as input or output                                                                             |

| TA1OUT       |           | Output         | 8-Bit Timer 01 Output: Output from 8-bit Timer 0 or Timer 1                                                          |

| PA7          | 1         | Input/Output   | Port A7: Programmable as input or output                                                                             |

| TAOIN        |           | Input          | 8-Bit Timer 0 Input: Input to 8-bit Timer 0                                                                          |

| KEYA<br>PB0  | 1         | Input          | Key-On Wakeup Input (dynamic pull-up selectable) (with internal pull-up resistor)                                    |

| TB2IN0       | 1         | Input/Output   | Port B0: Programmable as input or output<br>16-Bit Timer 2 Input 0: Count/capture trigger input to 16-bit Timer 2 or |

| INTB         |           | Input<br>Input | two-phase input pulse counter input                                                                                  |

|              |           | input          | Interrupt Request 7: Programmable to be high-level, low-level, rising-edge or falling-edge sensitive                 |

| PB1          | 1         | Input/Output   | Port B1: Programmable as input or output                                                                             |

| TB2IN1       |           | Input          | 16-Bit Timer 2 Input 1: Capture trigger input to 16-bit Timer 2 or                                                   |

| INTC         |           | Input          | two-phase input pulse counter input                                                                                  |

|              |           |                | Interrupt Request 8: Programmable to be high-level, low-level, rising-edge or falling-edge sensitive                 |

| PB2          | 1         | Input/Output   | Port B2: Programmable as input or output                                                                             |

| TB2OUT       |           | Output         | 16-Bit Timer 2 Output: Output from 16-bit Timer 2                                                                    |

| TB4IN0       |           | Input          | 16-Bit Timer 4 Input 0: Count/capture trigger input to 16-bit Timer 4                                                |

| PB3          | 1         | Input/Output   | Port B3: Programmable as input or output                                                                             |

| TB3IN0       |           | Input          | 16-Bit Timer 3 Input 0: Count/capture trigger input to 16-bit Timer 3 or                                             |

| INTD         |           | Input          | two-phase input pulse counter input                                                                                  |

|              |           | -              | Interrupt Request B: Programmable to be high-level, low-level, rising-edge or falling-edge sensitive                 |

| PB4          | 1         | Input/Output   | Port B4: Programmable as input or output                                                                             |

| TB3IN1       |           | Input          | 16-Bit Timer 3 Input 1: Capture trigger input to 16-bit Timer 3 or                                                   |

| INTE         |           | Input          | two-phase input pulse counter input                                                                                  |

|              |           |                | Interrupt Request C: Programmable to be high-level, low-level, rising-edge or falling-edge sensitive                 |

| Pin Name | # of Pins | Туре                  | Function                                                                                                                |

|----------|-----------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|

| PB5      | 1         | Input/Output          | Port B5: Programmable as input or output                                                                                |

| TB3OUT   |           | Output                | 16-Bit Timer 3 Output: Output from 16-Bit Timer 3                                                                       |

| TB4IN1   |           | Input                 | 16-Bit Timer 4 Input 1: Capture trigger input to 16-bit Timer 4                                                         |

| PB6      | 1         | Input/Output          | Port B6: Programmable as input or output                                                                                |

| TA3OUT   |           | Output                | 8-Bit Timer 23 Output: Output from 8-bit Timer 2 or Timer 3                                                             |

| PB7      | 1         | Input/Output          | Port B7: Programmable as input or output                                                                                |

| TA2IN    |           | Input                 | 8-Bit Time 2 Input: Input to 8-bit Timer 2                                                                              |

| INT7     |           | Input                 | Interrupt Request 7: Programmable to be high-level, low-level, rising-edge or falling-edge sensitive                    |

| KEYB     |           | Input                 | Key-On Wakeup Input (dynamic pull-up selectable) (with internal pull-up resistor)                                       |

| PC0      | 1         | Input/Output          | Port C0: Programmable as input or output                                                                                |

| TA4IN    |           | Input                 | 8-Bit Timer 4 Input: Input to 8-bit Timer 4                                                                             |

| INT8     |           | Input                 | Interrupt Request 8: Programmable to be high-level, low-level, rising-edge or falling-edge sensitive                    |

| PC1      | 1         | Input/Output          | Port C1: Programmable as input or output                                                                                |

| TA6IN    |           | Input                 | 8-Bit Timer 6 Input: Input to 8-bit Timer 6                                                                             |

| INT9     |           | Input                 | Interrupt Request 9: Programmable to be high-level, low-level, rising-edge or falling-edge sensitive                    |

| PC2      | 1         | Input/Output          | Port C2: Programmable as input or output                                                                                |

| TA8IN    |           | Input                 | 8-Bit Timer 8 Input: Input to 8-bit Timer 8                                                                             |

| INTA     |           | Input                 | Interrupt Request A: Programmable to be high-level, low-level, rising-edge or falling-edge sensitive                    |

| PC3      | 1         | Input/Output          | Port C3: Programmable as input or output                                                                                |

| TA5OUT   |           | Output                | 8-Bit Timer 45 Output: Output from 8-bit Timer 4 or Timer 5                                                             |

| PC4      | 1         | Input/Output          | Port B7: Programmable as input or output                                                                                |

| TAAIN    |           | Input                 | 8-Bit Timer A Input: Input to 8-bit Timer A                                                                             |

| PC5      | 1         | Input/Output          | Port C5: Programmable as input or output                                                                                |

| TA7OUT   |           | Output                | 8-Bit Timer 67 Output: Output to 8-bit Timer 6 or Timer 7                                                               |

| PC6      | 1         | Input/Output          | Port C6: Programmable as input or output                                                                                |

| TB8IN0   |           | Input                 | 16-Bit Timer 8 Input 0: Count/capture trigger input to 16-bit Timer 8                                                   |

| KEYC     | - ·       | Input                 | Key-On Wakeup Input (dynamic pull up selectable) (with internal pull-up resistor)                                       |

| PC7      | 1         | Input/Output          | Port C7: Programmable as input or output                                                                                |

| TB8IN1   |           | Input                 | 16-Bit Timer 8 Input: Capture trigger input to 16-bit Timer 8                                                           |

| TA9OUT   |           | Output                | 8-Bit Timer 89 Output: Output from 8-bit Timer 8 or Timer 9                                                             |

| PD0      | 1         | Input/Output          | Port D0: Programmable as input or output                                                                                |

| TXD0     |           | Output                | Serial Transmit Data 0                                                                                                  |

| TB9IN0   |           | Input                 | Programmable as push-pull or open-drain output<br>16-Bit Timer 9 Input 0: Count/capture trigger input to 16-bit Timer 9 |

| PD1      | 1         | Input<br>Input/Output |                                                                                                                         |

| RXD0     | 1         | Input                 | Port D1: Programmable as input or output<br>Serial Receive Data 0                                                       |

| TB9IN1   |           | Input                 | 16-Bit Timer 9 Input 1: Capture trigger input to 16-bit Timer 9                                                         |

| PD2      | 1         | Input/Output          | Port D2: Programmable as input or output                                                                                |

| SCLK0    |           | Input/Output          | Serial Clock Input/Output 0                                                                                             |

|          |           | Input                 | Serial Clear-to-Send 0                                                                                                  |

| 0100     |           | input                 | Programmable as a push-pull or open-drain output                                                                        |

| PD3      | 1         | Input/Output          | Port d3: Programmable as input or output                                                                                |

| TXD1     |           | Output                | Serial Transmit Data 1                                                                                                  |

|          |           |                       | Programmable as a push-pull or open-drain output                                                                        |

| TBAIN0   |           | Input                 | 16-Bit Timer A Input 0: Count/capture trigger input to 16-bit Timer A                                                   |

| PD4      | 1         | Input/Output          | Port D4: Programmable as input or output                                                                                |

| RXD1     |           | Input                 | Serial Receive Data 1                                                                                                   |

| TBAIN1   |           | Input                 | 16-Bit Timer A Input 1: Capture trigger input to 16-bit Timer A                                                         |

| PD5      | 1         | Input/Output          | Port D5: Programmable as input or output                                                                                |

| SCLK1    |           | Input/Output          | Serial Clock Input/Output 1                                                                                             |

| CTS1     |           | Input                 | Serial Clear-to-Send 1                                                                                                  |

|          |           |                       | Programmable as a push-pull or open-drain output                                                                        |

| TABOUT   |           | Output                | 8-Bit Timer AB Output: Output from 8-bit Timer A or Timer B                                                             |

| PD6      | 1         | Input/Output          | Port D6: Programmable as input or open-drain output                                                                     |

| XT1      |           | Input                 | Connection pin for a low-speed crystal                                                                                  |

| PD7      | 1         | Input/Output          | Port D7: Programmable as input or open-drain output                                                                     |

| XT2      |           | Output                | Connection pin for a low-speed crystal                                                                                  |

| PE0      | 1         | Input/Output          | Port E0: Programmable as input or output                                                                                |

| TXD3     |           | Output                | Serial Transmit Data 3                                                                                                  |

|          |           |                       | Programmable as push-pull or open-drain output                                                                          |

| Pin Name | # of Pins | Туре         | Function                                                                                             |

|----------|-----------|--------------|------------------------------------------------------------------------------------------------------|

| PE1      | 1         | Input/Output | Port E1: Programmable as input or output                                                             |

| RXD3     |           | Input        | Serial Receive Data 3                                                                                |

| PE2      | 1         | Input/Output | Port E2: Programmable as input or output                                                             |

| SCLK3    |           | Input/Output | Serial Clock Input/Output 3                                                                          |

| CTS3     |           | Input        | Serial Clear-to-Send 3                                                                               |

|          |           |              | Programmable as push-pull or open-drain output                                                       |

| PE3      | 1         | Input/Output | Port E3: Programmable as input or output                                                             |

| TXD4     |           | Output       | Serial Transmit Data 4                                                                               |

|          |           |              | Programmable as push-pull or open-drain output                                                       |

| PE4      | 1         | Input/Output | Port E4: Programmable as input or output                                                             |

| RXD4     |           | Input        | Serial Receive Data 4                                                                                |

| PE5      | 1         | Input/Output | Port E5: Programmable as input or output                                                             |

| SCLK4    |           | Input/Output | Serial Clock Input/Output 4                                                                          |

| CTS4     |           | Input        | Serial Clear-to-Send 4                                                                               |

|          |           |              | Programmable as push-pull or open-drain output                                                       |

| PE6      | 1         | Input/Output | Port E6: Programmable as input or output                                                             |

| INT1     |           | Input        | Interrupt Request 1: Programmable to be high-level, low-level, rising-edge or falling-edge sensitive |

| BOOT     |           |              | Single Boot Mode: The on-chip flash memory enters Single Boot mode to allow                          |

|          |           |              | re-programming when this pin is sampled low. This pin should be pulled up to a logic 1 to            |

|          |           |              | put the flash memory in Normal mode or when the device contains a mask ROM.                          |

| PE7      | 1         | Input/Output | Port E7: Programmable as input or output                                                             |

| INT2     |           | Input        | Interrupt Request 2: Programmable to be high-level, low-level, rising-edge or falling-edge           |

| INTLV    |           |              | sensitive                                                                                            |

|          |           |              | Interleave Mode: This pin should be pulled up to a logic 1 when Interleave mode is used,             |

|          |           |              | and pulled down to a logic 0 when Interleave mode is not used.                                       |

| PF0      | 1         | Input/Output | Port F0: Programmable as input or output                                                             |

| TXD5     |           | Output       | Serial Transmit Data 5                                                                               |

|          |           |              | Programmable as push-pull or open-drain output                                                       |

| PF1      | 1         | Input/Output | Port F1: Programmable as input or output                                                             |

| RXD5     |           | Input        | Serial Receive Data 5                                                                                |

| KEYD     |           | Input        | Key-On wakeup Input (dynamic pull-up selectable) (with internal pull-up resistor)                    |

| PF2      | 1         | Input/Output | Port F2: Programmable as input or output                                                             |

| SCLK5    |           | Input/Output | Serial Clock Input/Output 5                                                                          |

| CTS5     |           | Input        | Serial Clear-to-Send 5                                                                               |

|          |           |              | Programmable as push-pull or open-drain output                                                       |

| PF3      | 1         | Input/Output | Port F3: Programmable as input or output                                                             |

| SCK      |           | Input/Output | Clock input/output pin when the Serial Bus Interface is in SIO mode                                  |

| PF4      | 1         | Input/Output | Port F4: Programmable as input or output                                                             |

| SO       |           | Output       | Data transmit pin when the Serial Bus Interface is in SIO mode                                       |

| SDA      |           | Input/Output | Data transmit/receive pin when the Serial Bus Interface is in I <sup>2</sup> C mode                  |

|          |           |              | Programmable as push-pull or open-drain output                                                       |

| PF5      | 1         | Input/Output | Port F5: Programmable as input or output                                                             |

| SI       |           | Input        | Data receive pin when the Serial Bus Interface is in SIO mode                                        |

| SCL      |           | Input/Output | Clock input/output pin when the Serial Bus Interface is in I <sup>2</sup> C mode                     |

|          |           |              | Programmable as push-pull or open-drain output                                                       |

| PF6      |           | Input/Output | Port F6: Programmable as input or output                                                             |

| INT0     |           | Input        | Interrupt Request 0: Programmable to be high-level, low-level, rising-edge or falling-edge sensitive |

| ALE      | 1         | Output       | Address Latch Enable (This signal is driven out only when external memory is accessed.)              |

| TEST0    | 1         | Input        | Test pin                                                                                             |

| TEST1    | 1         | Input        | Test pin                                                                                             |

| RSTPUP   | 1         | Input        | The pull-up resistors for Port 3 and Port 4 are enabled when this signal is high at reset, and       |

|          |           |              | they are disabled when this signal is low at reset.                                                  |

| DAOUT0-2 | 3         | Output       | DA Output                                                                                            |

| NMI      | 1         | Input        | Nonmaskable Interrupt Request: Causes an NMI interrupt on the falling edge                           |

| BW0-1    | 2         | Input        | Both BW0 and BW1 should be tied to logic 1.                                                          |

| PLLOFF   | 1         | Input        | This pin should be tied to logic 1 when the frequency multiplied clock from the PLL is used;         |

|          |           |              | otherwise, it should be tied to logic 0.                                                             |

| RESET    | 1         | Input        | Reset (with internal pull-up resistor): Initializes the whole TMP1942FD                              |

|          |           |              |                                                                                                      |

| VREFH    | 1         | Input        | Input pin for high reference voltage for the A/D Converter                                           |

| VREFL    | 1         | Input        | Input pin for low reference voltage for the A/D Converter                                            |

| Pin Name | # of Pins | Туре         | Function                                                                                                                         |

|----------|-----------|--------------|----------------------------------------------------------------------------------------------------------------------------------|

| AVCC     | 1         |              | Power supply pin for the A/D Converter<br>This pin should always be connected to power supply even when the A/D Converter is not |

|          |           |              | used.                                                                                                                            |

| AVSS     | 1         | _            | Ground pin for the A/D Converter (0V)                                                                                            |

|          |           |              | This pin should always be connected to ground even when the A/D Converter is not used.                                           |

| DAVCC    | 1         | —            | Power supply pin for the D/A Converter                                                                                           |

|          |           |              | This pin should always be connected to power supply even when the D/A Converter is not                                           |

|          |           |              | used.                                                                                                                            |

| DAVSS    | 1         | —            | Ground pin for the D/A Converter (0V)                                                                                            |

|          |           |              | This pin should always be connected to ground even when the D/A Converter is not used.                                           |

| DAREFH   | 1         | _            | Poser supply input pin for the D/A converter                                                                                     |

| X1/X2    | 2         | Input/Output | Connection pins for high-speed crystal                                                                                           |

| FVCC     | 1         | _            | Power supply pin for the on-chip flash memory (DVCC in the mask-version product)                                                 |

| FVSS     | 1         |              | Ground pin for the on-chip flash memory (DVSS in the mask-version product)                                                       |

| CVCC     | 1         |              | Power supply pin for an oscillator                                                                                               |

| CVSS     | 1         |              | Ground pin for an oscillator (0V)                                                                                                |

| DVCC3    | 4         |              | Power supply pins                                                                                                                |

| DVCC51   | 1         |              | Power supply pin (Port F)                                                                                                        |

| DVCC52   | 1         |              | Power supply pin (Port C)                                                                                                        |

| DVSS     | 5         |              | Ground pins (0V)                                                                                                                 |

Port C functions as a 5-V port when DVCC52 is connected to a 5-V power supply. Port F functions as a 5-V port when DVCC51 is connected to a 5-V power supply.

Note: When the DSU is enabled, Port 9 functions as an interface to a processor probe regardless of the setting of the Port 9 Control Register (P9CR).

The following JTAG pins are available in the TMP1942 FD in a CSP package.

| Pin Name | # of Pins | Туре   | Function                                                    |

|----------|-----------|--------|-------------------------------------------------------------|

| TRST     | 1         | Input  | JTAG reset pin (with internal pull-up resistor)             |

| ТСК      | 1         | Input  | JTAG clock pin                                              |

| TDI      | 1         | Input  | JTAG data input pin (with internal pull-up resistor)        |

| TDO      | 1         | Output | JTAG data output pin                                        |

| TMS      | 1         | Input  | JTAG mode switch input pin (with internal pull-up resistor) |

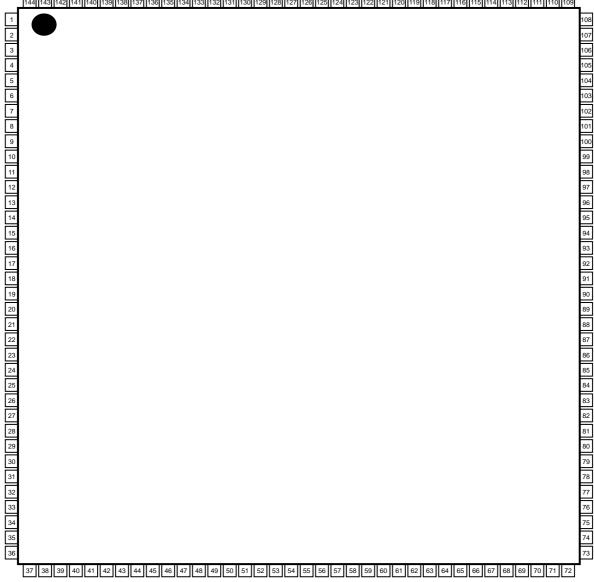

# 3. Flash Memory

This chapter describes the hardware configuration and functionality of the flash memory contained in the TMP1942FD.

#### 3.1 Features

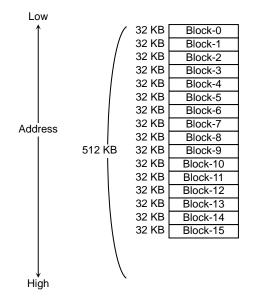

(1) Organization

The TMP1942FD contains 4 Mbits (512 Kbytes) of flash memory, which is divided into a total of 16 blocks (32 Kbytes x 16) to allow independent protection from program and erase for each block. While the CPU can access information in the flash memory through a full 32-bit data bus, an external flash programmer can only perform 16-bit data bus writes to the flash memory.

(2) Access Types

The flash memory of the TMP1942FD provides two selectable access types: one-clock access and interleaved access.

(3) Program/Erase Times

| Chip program time: | 6 seconds (typ.), including program verify operations |

|--------------------|-------------------------------------------------------|

|                    | (20 µs per long word)                                 |

| Chip erase time:   | 30 seconds (typ.), including erase verify operations  |

Note: These program and erase times are typical values and do not include data transfer overhead. The actual chip program and erase times depend on the programming method used.

(4) Programming Modes

On-Board Programming modes allow re-programming of the flash memory while the chip is soldered on a printed circuit board. Programmer mode utilizes an EPROM programmer to re-program the flash memory.

- On-Board Programming modes

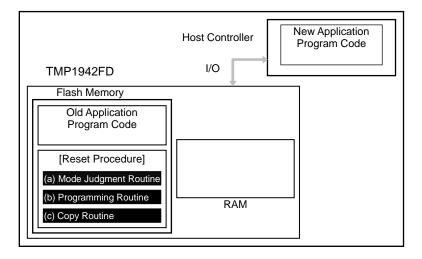

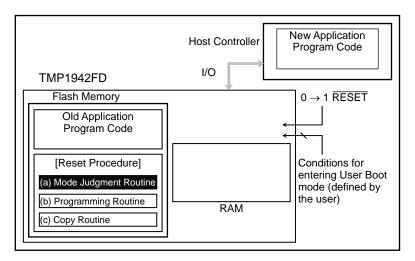

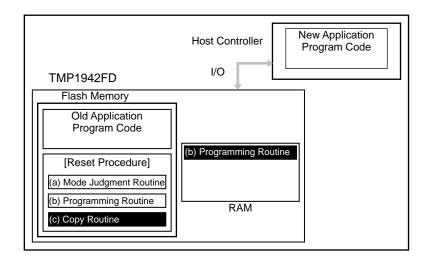

- 1) User Boot mode

Supports use of a user-written programming algorithm.

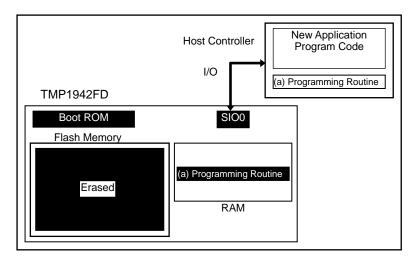

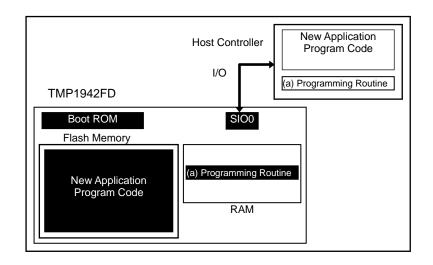

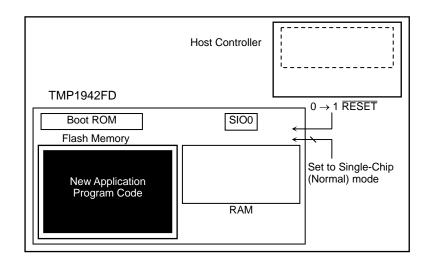

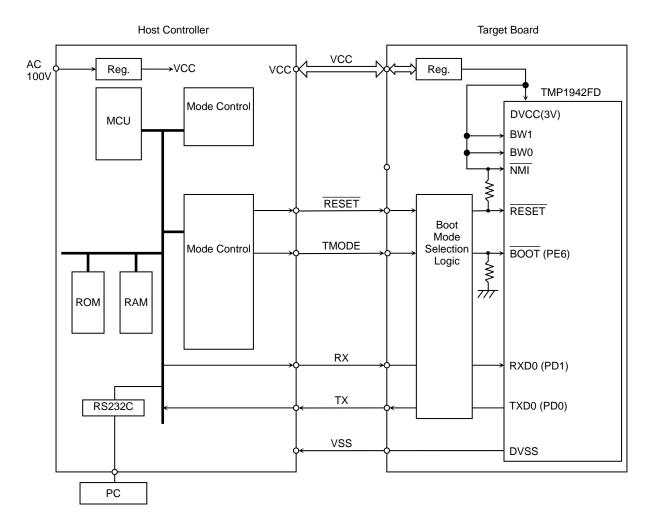

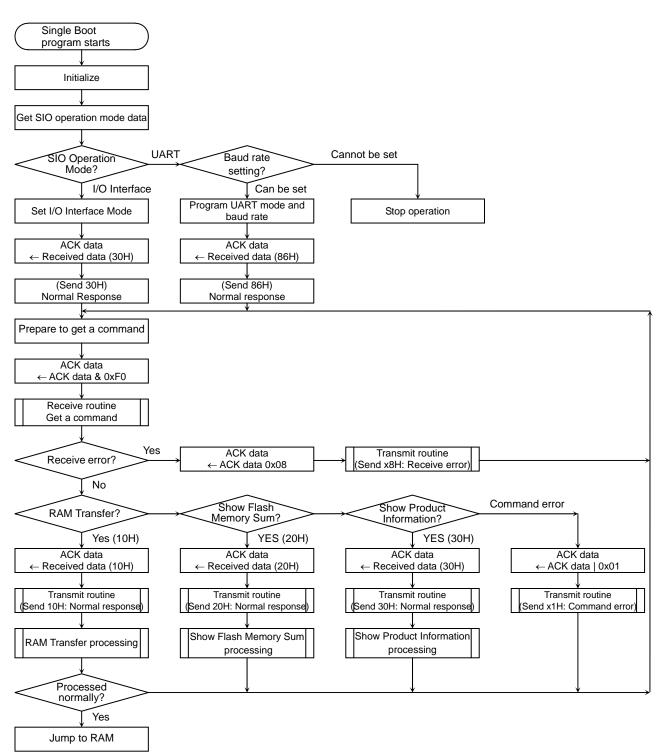

2) Single Boot mode

Downloads new program code using a Toshiba-defined serial interface protocol.

• Programmer mode

Supports use of a general-purpose EPROM programmer. (Planned)

(5) Re-programming

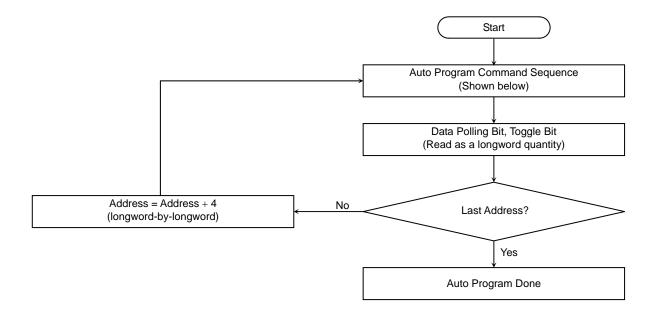

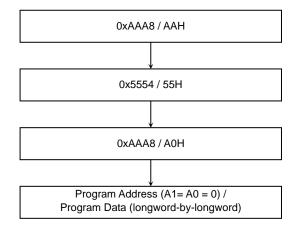

The flash memory contained in the TMP1942FD is compatible with the JEDEC standards, except a few unique functions. Thus, it is easy to migrate from a discrete flash memory device to the TMP1942FD on-chip flash memory. The TMP1942FD contains hardware to perform programming and erase operations automatically. This eliminates the need for the user to code complex program and erase sequences.

The security feature of the TMP1942FD flash memory prevents the stored data from being read while it is being re-programmed with programming equipment. The TMP1942FD also allows the user to protect individual blocks of the flash memory against program or erase through software commands; however, 12-V VPP programming does not support data protection on a block-by-block basis.

| JEDEC Standards                             | Changes and Enhancements                                                    |

|---------------------------------------------|-----------------------------------------------------------------------------|

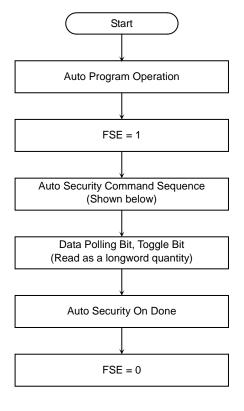

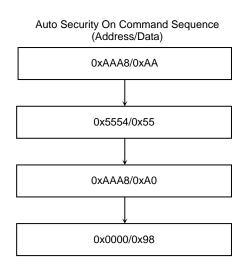

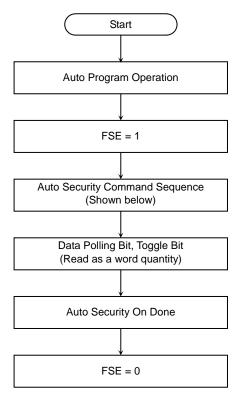

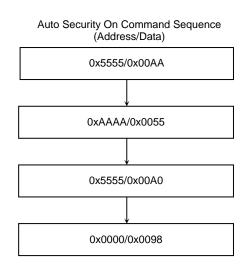

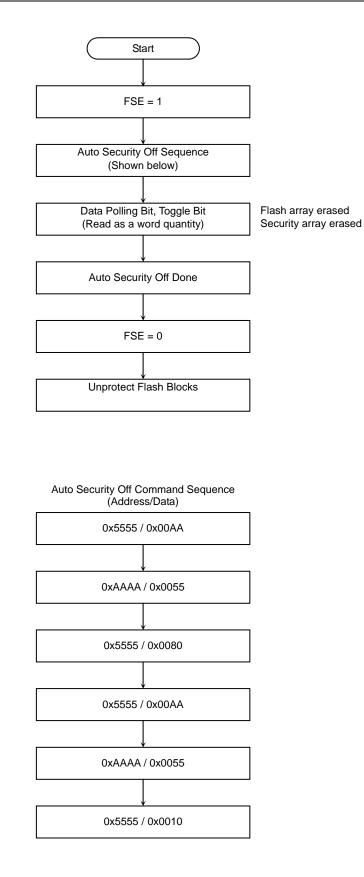

| Auto Program                                | Added feature: Security Auto Program                                        |

| Auto Chip Erase                             | Changed feature: Block protection is available only under software control. |

| Auto Block Erase                            | Removed feature: Erase Resume/Suspend mode                                  |

| <ul> <li>Auto Multi-Block Erase</li> </ul>  |                                                                             |

| <ul> <li>Data Polling/Toggle Bit</li> </ul> |                                                                             |

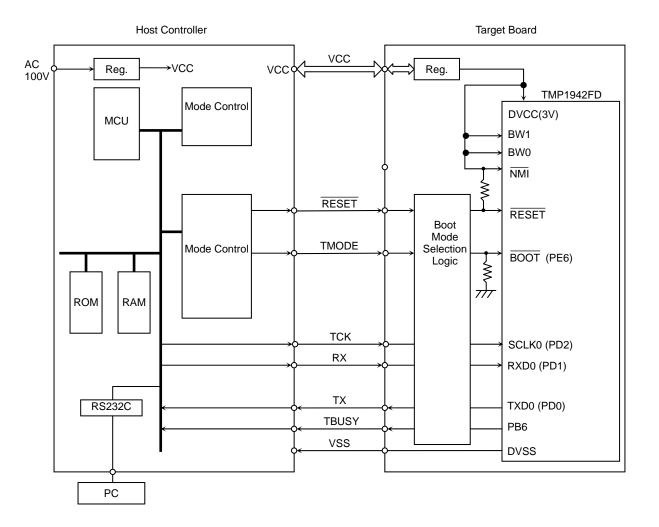

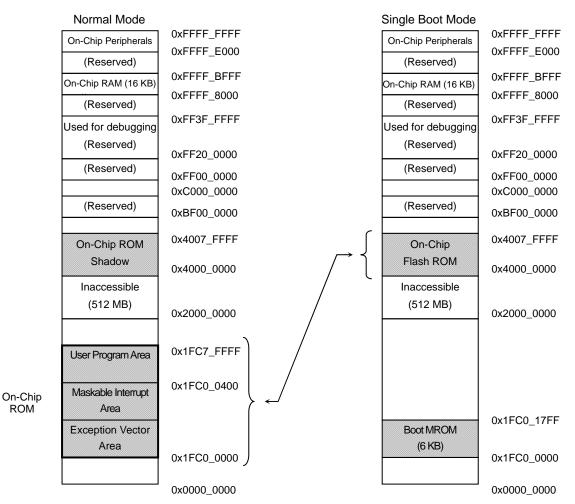

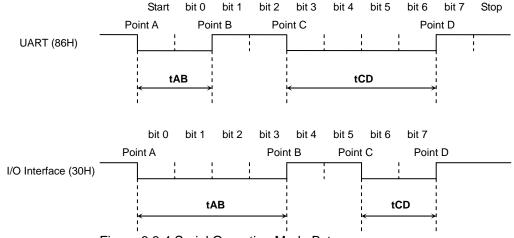

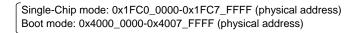

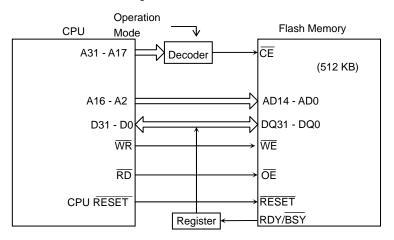

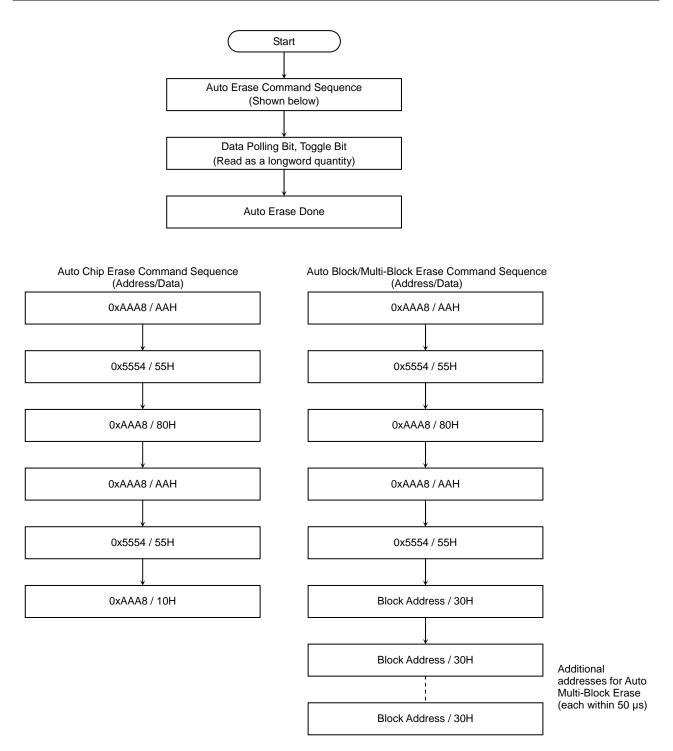

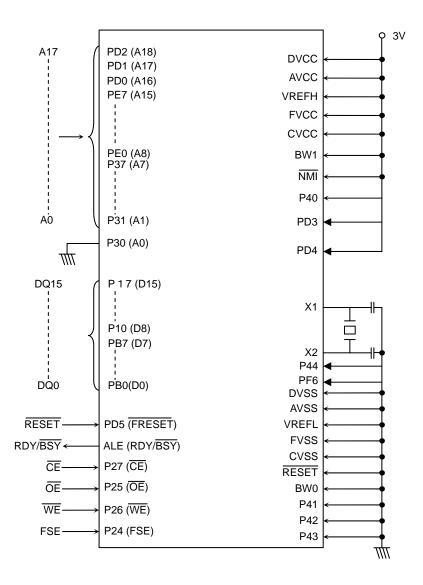

## 3.1.1 Block Diagram

Figure 3.1.1 Flash Memory Block Diagram

# 3.2 Operating Modes

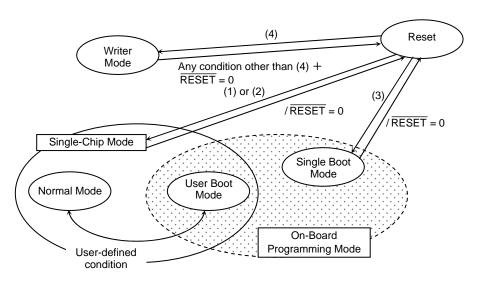

The TMP1942FD offers a total of five operating modes, including the one in which the flash memory is unused.

|                  | Operating Mode | Description                                                                                                                                                                                                                                                                                                                                             |

|------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Single-Chip Mode |                | After a reset, the TX19 core processor executes out of the on-chip flash memory. Either fast (one-clock) or interleave mode operation is selected through the INTLV pin when the reset state is released.                                                                                                                                               |

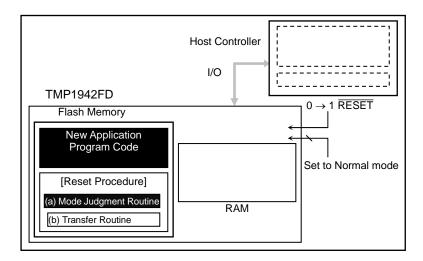

|                  | Normal Mode    | Single-Chip mode is further divided into Normal mode in which the user application executes and User<br>Boot mode which allows re-programming of the flash memory while the TMP1942FD is installed on a<br>printed circuit board.                                                                                                                       |

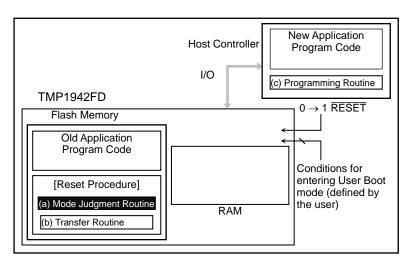

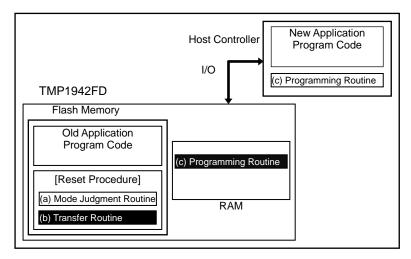

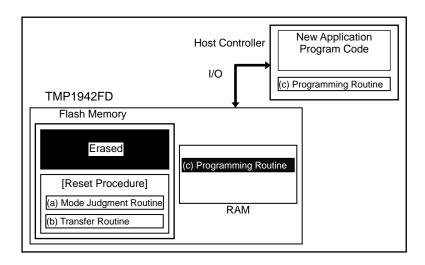

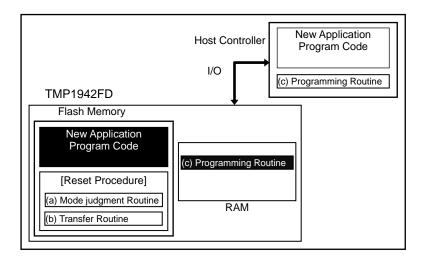

|                  | User Boot Mode | The user can freely define how to switch between Normal mode and User Boot mode. For example, the logic state on, for example, Port 00 can be used to determine whether to put the flash memory in Normal mode or User Boot mode. The user must include a routine in the application program to test the state of that port.                            |

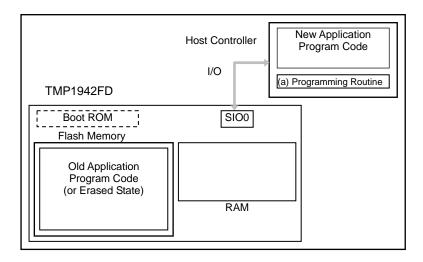

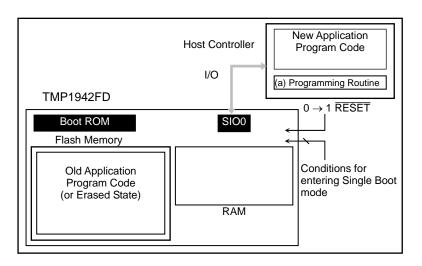

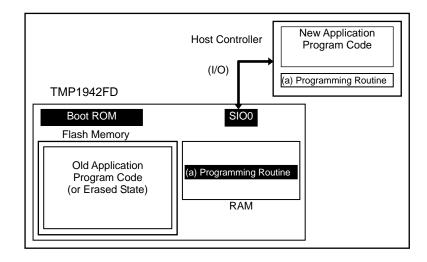

| Sin              | gle Boot Mode  | After a reset, the TX19 core processor executes out of the on-chip boot ROM (which is a mask ROM).The boot ROM contains a routine to aid users in performing on-board programming of the flash memory via a serial port of the TMP1942FD. The serial port is connected to an external host which transfers new data according to a prescribed protocol. |

| Writ             | ter Mode       | This mode allows re-programming of the flash memory with a general-purpose EPROM programmer.<br>Use the programmer and programming adaptor recommended by Toshiba.                                                                                                                                                                                      |

The on-chip flash memory can be re-programmed in one of the following three modes: User Boot mode, Single Boot mode and Writer mode. Of these modes, User Boot mode and Single Boot mode are collectively referred to as on-board programming modes.

The logic states on the BW0, BW1,  $\overline{\text{BOOT}}$  and INTLV pins during a reset sequence determine the mode of operation for the flash memory, as shown in Table 3.2.2. After  $\overline{\text{RESET}}$  is released, PE6 ( $\overline{\text{BOOT}}$ ) and PE7 (INTLV) can be configured as general-purpose I/O or timer output pins.

After  $\overline{\text{RESET}}$  is released, the CPU starts operating in the selected mode, except for Writer mode. When Writer mode is selected,  $\overline{\text{RESET}}$  must be held at logic 0. The input pins listed in Table 3.2.2 must remain stable once the flash memory is put in a given mode of operation.

|     | Operating Mode                  | Input Pins        |     |     |          |          |  |

|-----|---------------------------------|-------------------|-----|-----|----------|----------|--|

|     |                                 | RESET             | BW0 | BW1 | BOOT     | INTLV    |  |

| (1) | Single-Chip Mode (Interleave)   | $0 \rightarrow 1$ | 1   | 1   | 1        | 1        |  |

| (2) | Single-Chip Mode (Single-Clock) | $0 \rightarrow 1$ | 1   | 1   | 1        | 0        |  |

| (3) | Single Boot Mode                | $0 \rightarrow 1$ | 1   | 1   | 0        | (Note 1) |  |

| (4) | Writer Mode (Note 2)            | 0                 | 0   | 1   | (Note 1) | (Note 1) |  |

Table 3.2.2 Modes of Operation

Note 1: Don't care; however, the pins must be held at 0 or 1.

Note 2: In Writer mode, P40 must be held at 1, and P41 and P42 must be held at 0. For how to set other pins, refer to Section 3.4.2.3, *Pin Functions and Settings*.

Parenthesized numbers indicate that the relevant pins are at the logic states shown in Table 3.2.2.

#### Figure 3.2.1 Mode Transitions

#### 3.2.1 Reset Operation

To reset the TMP1942FD,  $\overline{\text{RESET}}$  must be asserted for at least 12 system clock periods after the power supply voltage and the internal high-frequency oscillator have stabilized. This time is typically 3 µs at 32 MHz when the on-chip PLL is utilized.

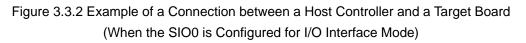

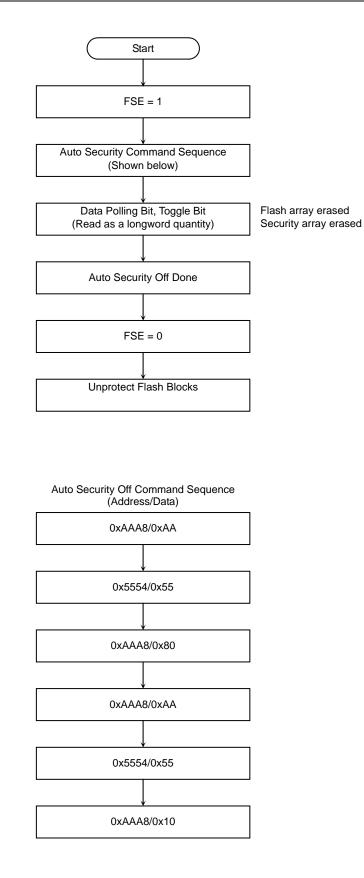

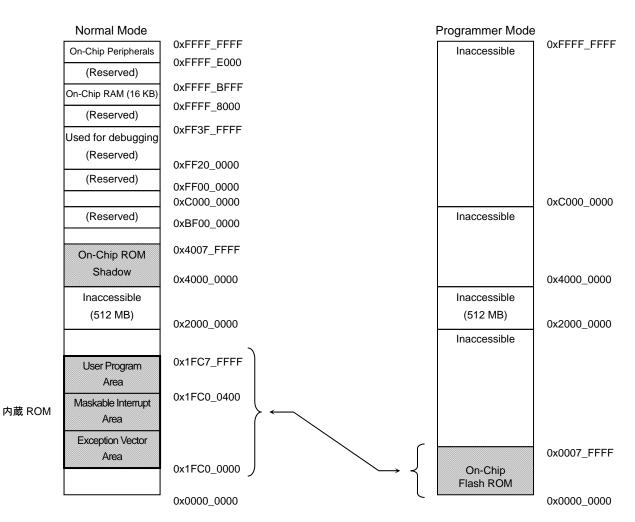

#### 3.2.2 Memory Maps

The memory map for the TMP1942FD varies according to the operation mode selected for the on-chip flash memory. Following are the memory maps in each operation mode.

| Normal Mode         |             | Single Boot Mode    |             | Writer Mode  |             |

|---------------------|-------------|---------------------|-------------|--------------|-------------|

| On-Chip Peripherals | 0xFFFF_FFFF | On-Chip Peripherals | 0xFFFF_FFF  | Inaccessible | 0xFFFF_FFF  |

| (Reserved)          | 0xFFFF_E000 | (Reserved)          | 0xFFFF_E000 |              |             |

| On-Chip RAM (20 KB) | 0xFFFF_CFFF | On-Chip RAM (20 KB) | 0xFFFF_CFFF |              |             |

| (Reserved)          | 0xFFFF_8000 | (Reserved)          | 0xFFFF_8000 |              |             |

| Used for debugging  | 0xFF3F_FFFF | Used for debugging  | 0xFF3F_FFFF |              |             |

| (Reserved)          | 0xFF20 0000 | (Reserved)          | 0xFF20 0000 |              |             |

| (Reserved)          | 0xFF00 0000 | (Reserved)          | 0xFF00 0000 |              |             |

|                     | 0xC000_0000 |                     | 0xC000_0000 |              | 0xC000_0000 |

| (Reserved)          | 0xBF00_0000 | (Reserved)          | 0xBF00_0000 | Inaccessible |             |

| On-Chip ROM         | 0x4007_FFFF | On-Chip             | 0x4007_FFFF |              |             |

| Shadow              | 0x4000_0000 | Flash ROM           | 0x4000_0000 |              | 0x4000_0000 |

| Inaccessible        |             | Inaccessible        |             | Inaccessible |             |

| (512 MB)            | 0x2000_0000 | (512 MB)            | 0x2000_0000 | (512 MB)     | 0x2000_0000 |

|                     | 0.2000_0000 |                     | 0.2000_0000 | Inaccessible | 0.2000_0000 |

|                     | 0x1FC7_FFFF |                     |             |              |             |

| User Program Area   |             |                     |             |              |             |

| Maskable Interrupt  | 0x1FC0_0400 |                     |             |              |             |

| Area                |             |                     | 0x1FC0 17FF |              |             |

| Exception Vector    |             | Boot MROM           | 001100_1111 |              | 0x0007_FFFF |

| Area                | 0x1FC0 0000 | (6 KB)              | 0x1FC0 0000 | On-Chip      | 0x0007_FFFF |

|                     |             |                     |             | Flash ROM    |             |

|                     | 0x0000_0000 |                     | 0x0000_0000 |              | 0x0000_0000 |

|                     |             |                     |             |              |             |

Note: The addresses shown above are physical addresses.

Figure 3.2.2 TMP1942FD Memory Maps

|          | User Boot Mode                                              | Boot Mode                 | Writer Mode               |

|----------|-------------------------------------------------------------|---------------------------|---------------------------|

| Block-0  | 0x1FC0_0000 - 0x1FC0_7FFF<br>(or 0x4000_0000 - 0x4000_7FFF) | 0x1FC0_0000 - 0x1FC0_7FFF | 0x0000_0000 - 0x0000_7FFF |

| Block-1  | 0x1FC0_8000 - 0x1FC0_FFFF<br>(or 0x4000_8000 - 0x4000_FFFF) | 0x1FC0_8000 - 0x1FC0_FFFF | 0x0000_8000 - 0x0000_FFFF |

| Block-2  | 0x1FC1_0000 - 0x1FC1_7FFF<br>(or 0x40010000 - 0x4001_7FFF)  | 0x1FC1_0000 - 0x1FC1_7FFF | 0x0001_0000 - 0x0001_7FFF |

| Block-3  | 0x1FC1_8000 - 0x1FC1_FFFF<br>(or 0x4001_8000 - 0x4001_FFFF) | 0x1FC1_8000 - 0x1FC1_FFFF | 0x0001_8000 - 0x0001_FFFF |

| Block-4  | 0x1FC2_0000 - 0x1FC2_7FFF<br>(or 0x4002_0000 - 0x4002_7FFF) | 0x1FC2_0000 - 0x1FC2_7FFF | 0x0002_0000 - 0x0002_7FFF |

| Block-5  | 0x1FC2_8000 - 0x1FC2_FFFF<br>(or 0x4002_8000 - 0x4002_FFFF) | 0x1FC2_8000 - 0x1FC2_FFFF | 0x0002_8000 - 0x0002_FFFF |

| Block-6  | 0x1FC3_0000 - 0x1FC3_7FFF<br>(or 0x4003_0000 - 0x4003_7FFF) | 0x1FC3_0000 - 0x1FC3_7FFF | 0x0003_0000 - 0x0003_7FFF |

| Block-7  | 0x1FC3_8000 - 0x1FC3_FFFF<br>(or 0x4003_8000 - 0x4003_FFFF) | 0x1FC3_8000 - 0x1FC3_FFFF | 0x0003_8000 - 0x0003_FFFF |

| Block-8  | 0x1FC4_0000 - 0x1FC4_7FFF<br>(or 0x4004_0000 - 0x4004_7FFF) | 0x1FC4_0000 - 0x1FC4_7FFF | 0x0004_0000 - 0x0004_7FFF |

| Block-9  | 0x1FC4_8000 - 0x1FC4_FFFF<br>(or 0x4004_8000 - 0x4004_FFFF) | 0x1FC4_8000 - 0x1FC4_FFFF | 0x0004_8000 - 0x000_4FFFF |

| Block-10 | 0x1FC5_0000 - 0x1FC5_7FFF<br>(or 0x4005_0000 - 0x4005_7FFF) | 0x1FC5_0000 - 0x1FC5_7FFF | 0x0005_0000 - 0x0005_7FFF |

| Block-11 | 0x1FC5_8000 - 0x1FC5_FFFF<br>(or 0x4005_8000 - 0x4005_FFFF) | 0x1FC5_8000 - 0x1FC5_FFFF | 0x0005_8000 - 0x0005_FFFF |

| Block-12 | 0x1FC6_0000 - 0x1FC6_7FFF<br>(or 0x4006_0000 - 0x4006_7FFF) | 0x1FC6_0000 - 0x1FC6_7FFF | 0x0006_0000 - 0x0006_7FFF |

| Block-13 | 0x1FC6_8000 - 0x1FC6_FFFF<br>(or 0x4006_8000 - 0x4006_FFFF) | 0x1FC6_8000 - 0x1FC6_FFFF | 0x0006_8000 - 0x0006_FFFF |

| Block-14 | 0x1FC7_0000 - 0x1FC7_7FFF<br>(or 0x4007_0000 - 0x4007_7FFF) | 0x1FC7_0000 - 0x1FC7_7FFF | 0x0007_0000 - 0x0007_7FFF |

| Block-15 | 0x1FC7_8000 - 0x1FC7_FFFF<br>(or 0x4007_8000 - 0x4007_FFFF) | 0x1FC7_8000 - 0x1FC7_FFFF | 0x0007_8000 - 0x0007_FFFF |

Table 3.2.3 Block Addresses

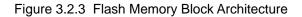

### 3.2.3 Interleave Mode

If Port E7 (PE7) is sampled high at the rising edge of  $\overline{\text{RESET}}$ , the flash memory enters Interleave mode. When the system clock (fsys) operates at 16 MHz or faster, the flash memory must be configured into Interleave mode.

The TMP1942FD flash memory is comprised of two banks which are distinguished by the second lowest bit of an address. The memory controller of the TMP1942FD core processor provides addresses for each bank. Each bank can be accessed in two system clock cycles. Switching between the two banks enables each address to be accessed in a single system clock cycle, unless a branch occurs (see Figure 3.2.4).

Figure 3.2.4 Interleave Configuration

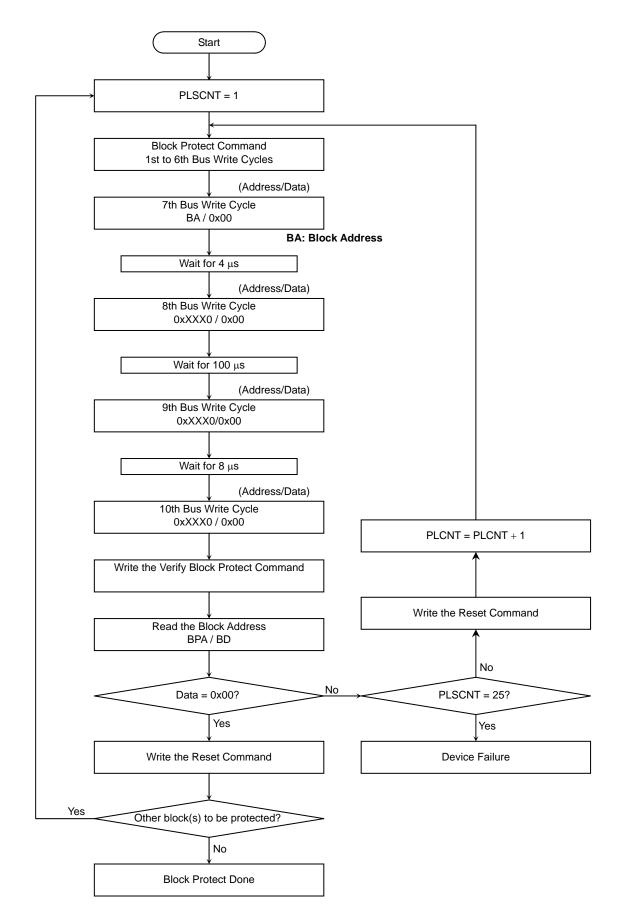

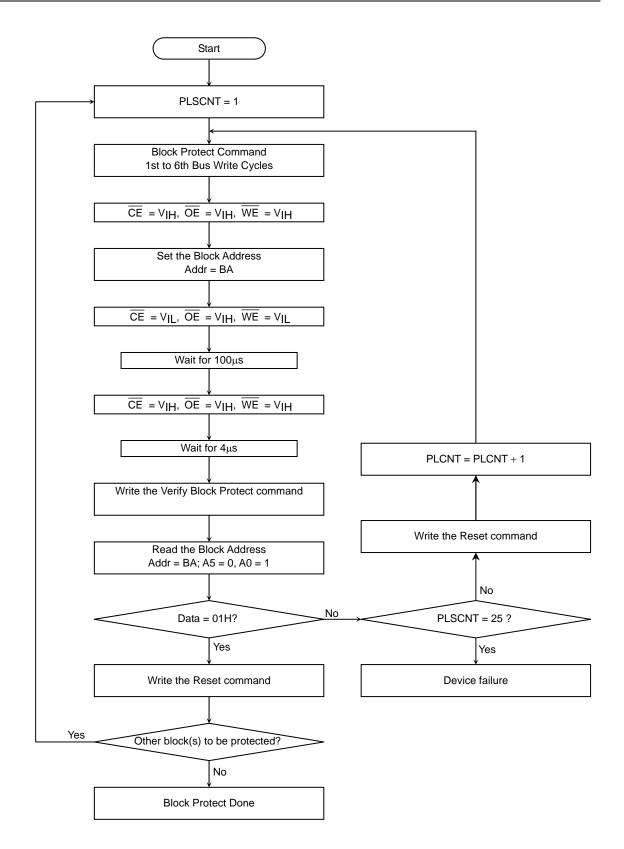

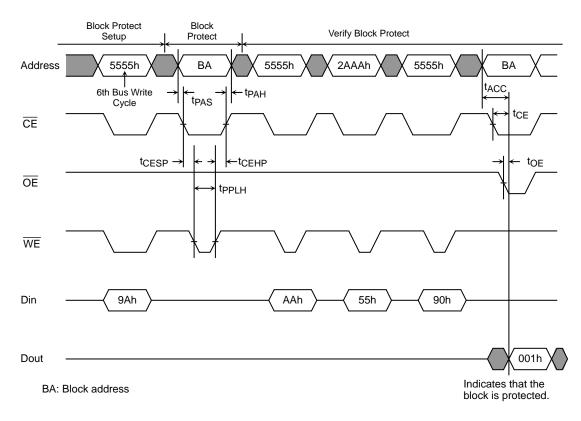

### 3.2.4 Block Protection

The TMP1942FD flash memory is organized into a total of 16 blocks (32 Kbytes x 16). To protect stored data from any program and erase operations, **each** block has a protect bit, which can be set by executing the Block Protect command sequence. Blocks in protection mode are protected from even the Chip Erase and Multi-Block Erase commands; these commands erase only unprotected blocks. Since protection status is stored in flash memory cells, it is retained even if the chip is powered off.

### 3.2.5 DSU-ICE Interface

If Port 37 (P37) is sampled high at the rising edge of  $\overline{\text{RESET}}$ , the TMP1942FD enters DSU mode, which is used for software debugging using an external DSU-ICE unit. In DSU mode, Port A serves as an interface to the DSU-ICE, and cannot be used for other functions. Consult the DSU-ICE operation manual for a description of debugging using the DSU-ICE. When the TMP1942FD is in DSU mode, the on-chip flash memory provides a security feature.

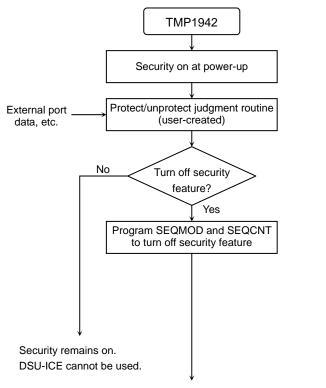

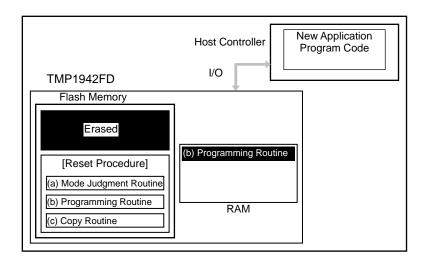

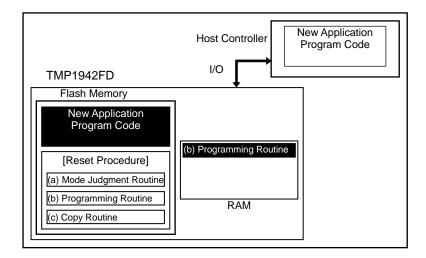

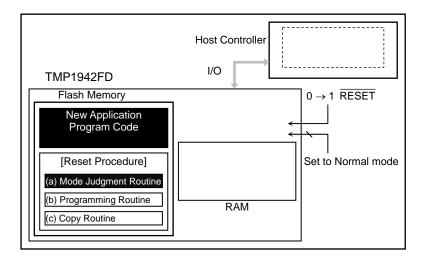

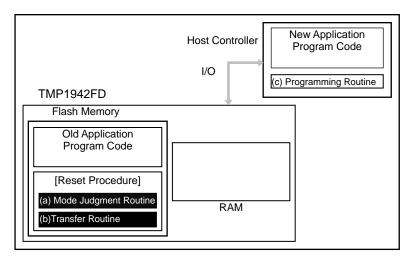

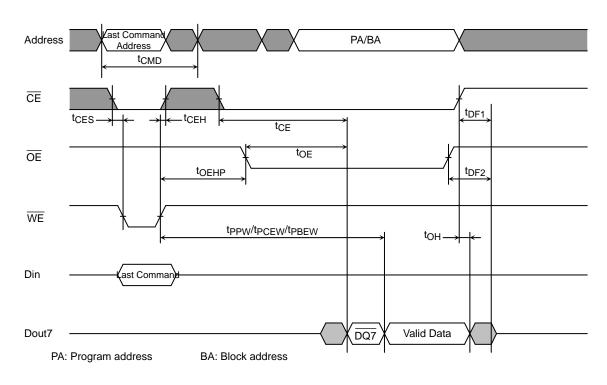

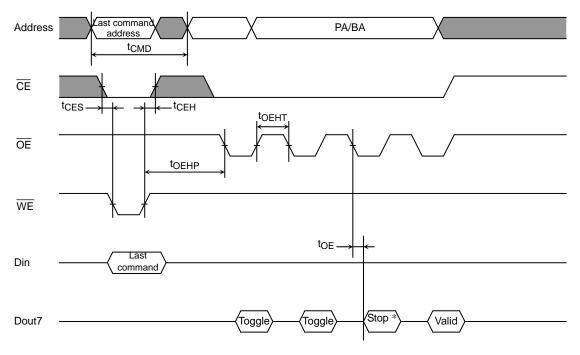

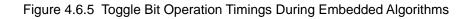

(1) Flash security feature