# **TOSHIBA**

# 32bit TX System RISC TX19A Family

TMP19A43FD/FZXBG

Rev2.0 2007.Apr.9

# 32-bit RISC Microprocessor - TX19 Family TMP19A43FZXBG, FDXBG

#### 1. Overview and Features

The TX19 family is a high-performance 32-bit RISC processor series that TOSHIBA originally developed by integrating the MIPS16<sup>TM</sup>ASE (Application Specific Extension), which is an extended instruction set of high code efficiency.

TMP19A43 is a 32-bit RISC microprocessor with a TX19A processor core and various peripheral functions integrated into one package. It can operate at low voltage with low power consumption.

Features of TMP19A43 are as follows:

#### RESTRICTIONS ON PRODUCT USE

070122EBP

- The information contained herein is subject to change without notice. 021023\_D

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor

devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress.

It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making

a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA

products could cause loss of human life, bodily injury or damage to property.

- In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc. 021023\_A

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk. 021023\_B

- The products described in this document shall not be used or embedded to any downstream products of which

manufacture, use and/or sale are prohibited under any applicable laws and regulations. 060106\_Q

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is

assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use.

No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third parties.

- The products described in this document are subject to foreign exchange and foreign trade control laws. 060925\_E

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions. 030619\_S

- (1) TX19A processor core

- 1) Improved code efficiency and operating performance have been realized through the use of two ISA (Instruction Set Architecture) modes 16- and 32-bit ISA modes.

- The 16-bit ISA mode instructions are compatible with the MIPS16<sup>™</sup>ASE instructions of superior code efficiency at the object level.

- The 32-bit ISA mode instructions are compatible with the TX39 instructions of superior operating performance at the object level.

- 2) Both high performance and low power dissipation have been achieved.

- High performance

- Almost all instructions can be executed with one clock.

- High performance is possible via a three-operand operation instruction.

- 5-stage pipeline

- Built-in high-speed memory

- DSP function: A 32-bit multiplication and accumulation operation can be executed with one clock.

- Low power dissipation

- Optimized design using a low power dissipation library

- Standby function that stops the operation of the processor core

- 3) High-speed interrupt response suitable for real-time control

- Independency of the entry address

- Automatic generation of factor-specific vector addresses

- Automatic update of interrupt mask levels

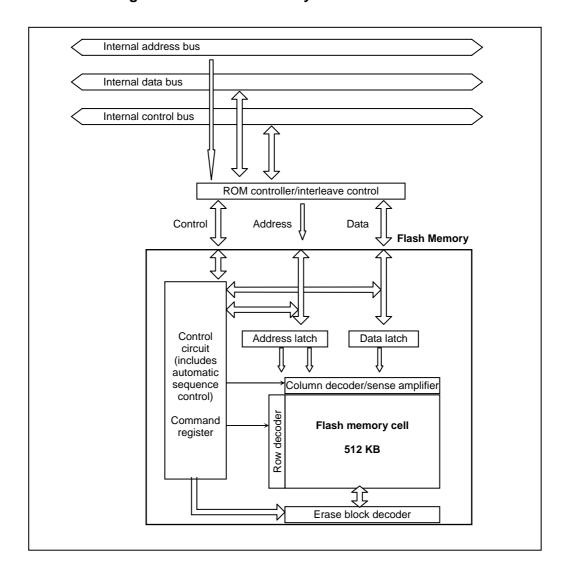

- (2) Internal program memory and data memory

| Product name    | Built-in ROM     | Built-in RAM |

|-----------------|------------------|--------------|

| TMP19A43CZXBG   | 384Kbyte         | 20Kbyte      |

| TMP19A43CDXBG * | 512Kbyte         | 24Kbyte      |

| TMP19A43FZXBG * | 384Kbyte (Flash) | 20Kbyte      |

| TMP19A43FDXBG   | 512Kbyte (Flash) | 24Kbyte      |

The product indicated by an asterisk \* is under development.

- ROM correction function: 1 word × 8 blocks, 8 words × 4 blocks

- (3) External memory expansion

- Expandable to 16 megabytes (for both programs and data)

- External data bus:

Separate bus/multiplexed bus : Coexistence of 8- and 16-bit widths is possible.

Chip select/wait controller : 4 channels

(4) DMA controller : 8 channels (2 interrupt factors)

Activated by an interrupt or software

Data to be transferred to internal memory, internal I/O, external memory, and external I/O

(5) 16-bit timer : 16 channels

- 16-bit interval timer mode

- 16-bit event counter mode

- 16-bit PPG output (every 4 channels, synchronous outputs are possible)

- Input capture function

- 2-phase pulse input counter function (4 channels assigned to perform this function): Multiplicationby-4 mode

(6) 32-bit timer

32-bit input capture register : 4 channels

32-bit compare register : 8 channels

32-bit time base timer : 1 channel

(7) Clock timer : 1 channel

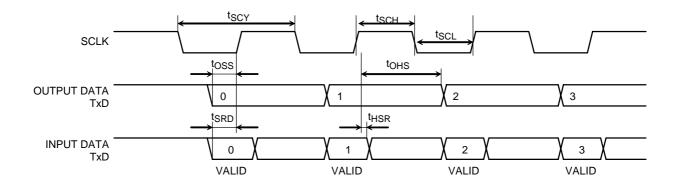

(8) General-purpose serial interface : 3 channels

• Selectable between the UART mode and the synchronization mode

(9) High-speed serial interface : 3 channels

• Selectable between the UART mode and the high-speed synchronization mode (maximum speed: 10 Mbps in the high-speed synchronization mode @40MHz)

(10) Serial bus interface : 1 channel

• Selectable between the I<sup>2</sup>C bus mode and the clock synchronization mode

(11) 10-bit A/D converter (with S/H) : 16 channels

- Start by an external trigger, and the internal timer activated by a trigger

- Fixed channel/scan mode

- Single/repeat mode

- High-priority conversion mode

- Timer monitor function

- Conversion time 1.15 μsec(@ 40MHz)

(12) 8-bit D/A converter : 2 channels(13) Watchdog timer : 1 channel

- (14) Interrupt function

- CPU: 2 factors .....software interrupt instruction

- Internal: 46 factors...... The order of precedence can be set over 7 levels (except the watchdog timer interrupt).

- External: 48 factors ....... The order of precedence can be set over 7 levels.

Because 32 factors are associated with KWUP, the number of interrupt factors is one.

- ractors is one

- (15) Input and output ports .....143 terminals

- (16) Standby function

- Three standby modes (IDLE, SLEEP, STOP)

- (17) Clock generator

- Built-in PLL (multiplication by 4)

- Clock gear function: The high-speed clock can be divided into 3/4, 1/2, 1/4 or 1/8.

- Sub-clock: SLOW and SLEEP modes (32.768 kHz)

- (18) Endian: Bi-endian (big-endian/little-endian)

- (19) Maximum operating frequency

- 40 MHz (PLL multiplication)

- (20) Operating voltage range

Core: 1.35 V to 1.65 V

I/O and ADC: 2.7 V to 3.6 V

DAC: 2.3 V to 2.7 V

(21) Package

P-FBGA193 (12 mm × 12 mm, 0.65 mm pitch)

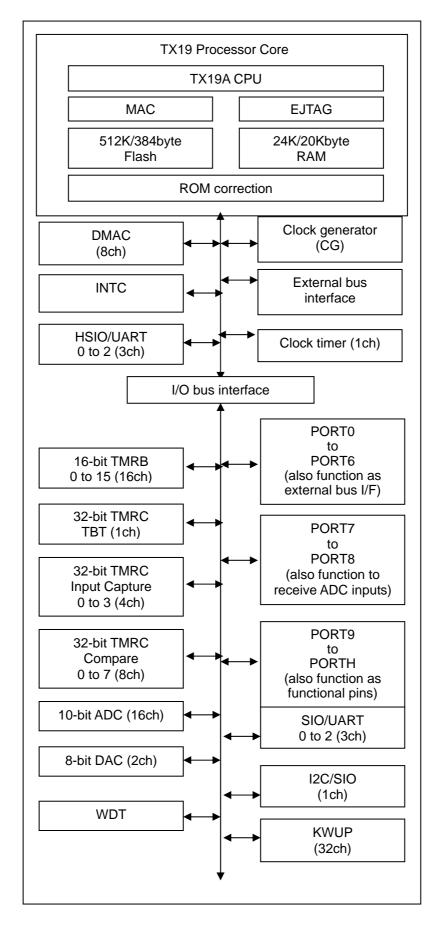

Fig. 1-1 TMP19A43 Block Diagram

# 2. Pin Layout and Pin Functions

This section shows the pin layout of TMP19A43 and describes the names and functions of input and output pins.

#### 2.1 Pin Layout (Top view)

Fig. 2-1 Pin Layout Diagram (P-FBGA193) shows the pin layout of TMP19A43.

| A1 | A2 | А3 | A4 | A5 | A6 | A7 | A8 | A9 | A10 | A11 | A12 | A13 | A14 | A15 | A16 | A17 |

|----|----|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|

| B1 | B2 | В3 | B4 | B5 | B6 | B7 | B8 | B9 | B10 | B11 | B12 | B13 | B14 | B15 | B16 | B17 |

| C1 | C2 |    |    |    |    |    |    |    |     |     |     |     |     |     | C16 | C17 |

| D1 | D2 |    | D4 | D5 | D6 | D7 | D8 | D9 | D10 | D11 | D12 | D13 | D14 |     | D16 | D17 |

| E1 | E2 |    | E4 | E5 | E6 | E7 | E8 | E9 | E10 | E11 | E12 | E13 | E14 |     | E16 | E17 |

| F1 | F2 |    | F4 | F5 | F6 |    |    |    |     |     |     | F13 | F14 |     | F16 | F17 |

| G1 | G2 |    | G4 | G5 |    |    |    |    |     |     |     | G13 | G14 |     | G16 | G17 |

| H1 | H2 |    | H4 | H5 |    |    |    |    |     |     |     | H13 | H14 |     | H16 | H17 |

| J1 | J2 |    | J4 | J5 |    |    |    |    |     |     |     | J13 | J14 |     | J16 | J17 |

| K1 | K2 |    | K4 | K5 |    |    |    |    |     |     |     | K13 | K14 |     | K16 | K17 |

| L1 | L2 |    | L4 | L5 |    |    |    |    |     |     |     | L13 | L14 |     | L16 | L17 |

| M1 | M2 |    | M4 | M5 |    |    |    |    |     |     |     | M13 | M14 |     | M16 | M17 |

| N1 | N2 |    | N4 | N5 | N6 | N7 | N8 | N9 | N10 | N11 | N12 | N13 | N14 |     | N16 | N17 |

| P1 | P2 |    | P4 | P5 | P6 | P7 | P8 | P9 | P10 | P11 | P12 | P13 | P14 |     | P16 | P17 |

| R1 | R2 |    |    |    |    |    |    |    |     |     |     |     |     |     | R16 | R17 |

| T1 | T2 | Т3 | T4 | T5 | T6 | T7 | T8 | Т9 | T10 | T11 | T12 | T13 | T14 | T15 | T16 | T17 |

| U1 | U2 | U3 | U4 | U5 | U6 | U7 | U8 | U9 | U10 | U11 | U12 | U13 | U14 | U15 | U16 | U17 |

Fig. 2-1 Pin Layout Diagram (P-FBGA193)

#### 2.2 Pin Numbers and Names

Table 2-1 shows the pin numbers and names of TMP19A43.

Table 2-1 Pin numbers and names

| Pin<br>No. | Pin Name         | Pin<br>No. | Pin Name         | Pin<br>No. | Pin Name        | Pin<br>No. | Pin Name           | Pin<br>No. | Pin Name            |

|------------|------------------|------------|------------------|------------|-----------------|------------|--------------------|------------|---------------------|

| A1         | DVSS             | D2         | PF3/KEY19/DACK4  | G2         | P95/SCLK2/CTS2  | M1         | PB5/HTXD1          | R2         | P33/WAIT/RDY        |

| A2         | P81/AN9/KEY05    | D4         | P71/AN1          | G4         | P94/RXD2        | M2         | PB4/HSCLK0/HCTS0   | R16        | P45/BUSMD           |

| А3         | P83/AN11/KEY07   | D5         | P73/AN3          | G5         | P93/TXD2        | M4         | PB3/HRXD0          | R17        | P46/ENDIAN          |

| A4         | P85/AN13/INT7    | D6         | P74/AN4/KEY00    | G13        | PH1/TPC1/TPD1   | M5         | TEST4              | T1         | P37/ALE/TC3IN       |

| A5         | P87/AN15/INT9    | D7         | P76/AN6/KEY02    | G14        | PH7/TPC7/TPD7   | M13        | FVCC3              | T2         | P34/BUSRQ/TBEOUT    |

| A6         | DA0              | D8         | PD5/TBDOUT       | G16        | PCST4           | M14        | PG3/TPD3           | T3         | P30/RD              |

| A7         | CVREF0           | D9         | PD3/TBBOUT       | G17        | DCLK            | M16        | PG4/TPD4           | T4         | P02/D2/AD2          |

| A8         | DA1              | D10        | PD0/HTXD2        | H1         | PC1/TCOUT0      | M17        | PG5/TPD2           | T5         | P06/D6/AD6          |

| A9         | CVREF1           | D11        | PE0/KEY8         | H2         | PC0/TBTIN/KEY30 | N1         | PB7/HSCLK1/HCTS1   | T6         | P12/D10/AD10/A10    |

| A10        | PD2/HSCLK2/HCTS2 | D12        | PE3/KEY11        | H4         | P97/TBAOUT      | N2         | PB6/HRXD1          | T7         | P16/D14/AD14/A14    |

| A11        | PE2/KEY10        | D13        | PA2/INT2/TB7IN0  | H5         | DVCC3           | N4         | P00/D0/AD0         | T8         | P21/A17/A1/TB0IN1   |

| A12        | PE5/KEY13        | D14        | PH4/TPC4/TPD4    | H13        | PH2/TPC2/TPD2   | N5         | P04/D4/AD4         | T9         | P24/A20/A4/TB4IN0   |

| A13        | PE7/KEY15        | D16        | PA3/INT3/TB7IN1  | H14        | TRST            | N6         | P10/D8/AD8/A8      | T10        | P26/A22/A6/TB5IN0   |

| A14        | X1               | D17        | XT1              | H16        | TMS             | N7         | P14/D12/AD12/A12   | T11        | P52/A2/INTE         |

| A15        | X2               | E1         | PF6/KEY22/TCOUT6 | H17        | EJE             | N8         | FVCC3              | T12        | P56/A6/TB2OUT/KEY28 |

| A16        | CVCCH            | E2         | PF5/KEY21/TCOUT5 | J1         | PC4/TCOUT3      | N9         | DVSS               | T13        | P62/A10/SCLK0/CTS0  |

| A17        | CVSS             | E4         | P70/AN0          | J2         | PC3/TCOUT2      | N10        | DVCC15             | T14        | P66/A14/TB4OUT      |

| B1         | PF0/KEY16/DREQ0  | E5         | P72/AN2          | J4         | PC2/TCOUT1      | N11        | P50/A0/INTC        | T15        | P40/CS0/KEY24       |

| B2         | P80/AN8/KEY04    | E6         | VREFH            | J5         | DVCC15          | N12        | P54/A4/TB0OUT      | T16        | P42/CS2/KEY26       |

| В3         | P82/AN10/KEY06   | E7         | AVSS             | J13        | PH3/TPC3/TPD3   | N13        | P60/A8/TXD0        | T17        | P44/SCOUT           |

| B4         | P84/AN12/INT6    | E8         | DAVCC            | J14        | DINT            | N14        | P64/A12/RXD1/INTB  | U1         | TEST2               |

| B5         | P86/AN14/INT8    | E9         | DAVREF           | J16        | TDO             | N16        | PG6/TPD6           | U2         | P35/BUSAK/TC1IN     |

| В6         | P75/AN5/KEY01    | E10        | DAGND            | J17        | DVSS            | N17        | PG7/TPD7           | U3         | P31/WR              |

| В7         | P77/AN7/KEY03    | E11        | DVCC3            | K1         | PC7/SCK         | P1         | BOOT               | U4         | P03/D3/AD3          |

| B8         | PD6/KEY31/AFTRG  | E12        | PA0/INT0/TB6IN0  | K2         | PC6/SI/SCL      | P2         | P32/HWR/TC0IN      | U5         | P07/D7/AD7          |

| В9         | PD4/TBCOUT       | E13        | PA1/INT1/TB6IN1  | K4         | PC5/SO/SDA      | P4         | P01/D1/AD1         | U6         | P13/D11/AD11/A11    |

| B10        | PD1/HRXD2        | E14        | PH5/TPC5/TPD5    | K5         | DVSS            | P5         | P05/D5/AD5         | U7         | P17/D15/AD15/A15    |

| B11        | PE1/KEY09        | E16        | PCST0            | K13        | DVCC15          | P6         | P11/D9/AD9/A9      | U8         | P22/A18/A2/TB1IN0   |

| B12        | PE4/KEY12        | E17        | PCST1            | K14        | TOVR/TSTA       | P7         | P15/D13/AD13/A13   | U9         | P25/A21/A5/TB4IN1   |

| B13        | PE6/KEY14        | F1         | PF7/KEY23/TCOUT7 | K16        | TDI             | P8         | P20/A16/A0/TB0IN0  | U10        | P27/A23/A7/TB5IN1   |

| B14        | PA5/INT5/TB8IN1  | F2         | P92/TB8OUT       | K17        | TCK             | P9         | P23/A19/A3/TB1IN1  | U11        | P53/A3/INTF         |

| B15        | PA6/ TB2IN0      | F4         | P91/TB7OUT       | L1         | PB2/HTXD0       | P10        | TEST0              | U12        | P57/A7/TB3OUT/KEY29 |

| B16        | PA7/TB2IN1       | F5         | P90/TB6OUT       | L2         | PB1/TB3IN1      | P11        | P51/A1/INTD        | U13        | P63/A11/TXD1        |

| B17        | CVCCL            | F6         | AVCC3            | L4         | PB0/TB3IN0      | P12        | P55/A5/TB1OUT      | U14        | P67/A15/TB5OUT      |

| C1         | PF2/KEY18/DREQ4  | F13        | PH0/TPC0/TPD0    | L5         | TEST1           | P13        | P61/A9/RXD0/INTA   | U15        | P41/CS1/KEY25       |

| C2         | PF1/KEY17/DACK0  | F14        | PH6/TPC6/TPD6    | L13        | DVSS            | P14        | P65/A13/SCLK1/CTS1 | U16        | P43/CS3/KEY27       |

| C16        | PA4/INT4/TB8IN0  | F16        | PCST2            | L14        | PG0/TPD0        | P16        | P47/TBFOUT         | U17        | TEST3               |

| C17        | XT2              | F17        | PCST3            | L16        | PG1/TPD1        | P17        | RESET              |            |                     |

| D1         | PF4/KEY20/TCOUT4 | G1         | P96/TB9OUT       | L17        | PG2/TPD2        | R1         | P36/RW/TC2IN       |            |                     |

#### 2.3 Pin Names and Functions

Table 2-2 through Table 2-7 show the names and functions of input and output pins.

Table 2-2 Pin Names and Functions (1 of 6)

| Pin name      | Number of pins | Input or output | Function                                                                                               |

|---------------|----------------|-----------------|--------------------------------------------------------------------------------------------------------|

| P00-P07       | 8              | Input/output    | Port 0: Input/output port (with pull-up) that allows input/output to be set in units of bits           |

| D0-D7         |                | Input/output    | Data (lower): Data bus 0 to 7 (separate bus mode)                                                      |

| AD0-D7        |                | Input/output    | Address data (lower): Address data bus 0 to 7 (multiplexed bus mode)                                   |

| P10-P17       | 8              | Input/output    | Port 1: Input/output port (with pull-up) that allows input/output to be set in units of bits           |

| D8-D15        |                | Input/output    | Data (upper): Data bus 8 to 15 (separate bus mode)                                                     |

| AD8-AD15      |                | Input/output    | Address data (upper): Address data bus 8 to 15 (multiplexed bus mode)                                  |

| A8-A15        |                | Output          | Address: Address bus 8 to 15 (multiplexed bus mode)                                                    |

| P20-P27       | 8              | Input/output    | Port 2: Input/output port (with pull-up) that allows input/output to be set in units of bits           |

| A16-A23       |                | Output          | Address: Address bus 15 to 23 (separate bus mode)                                                      |

| A0-A7         |                | Output          | Address: Address bus 0 to 7 (multiplexed bus mode)                                                     |

| TB0IN0,TB0IN1 |                | Input           | 16-bit timer 0 input 0,1: For inputting the count/capture trigger of a 16-bit timer 0                  |

| TB1IN0,TB1IN1 |                | Input           | 16-bit timer 1 input 0,1: For inputting the count/capture trigger of a 16-bit timer 1                  |

| TB4IN0,TB4IN1 |                | Input           | 16-bit timer 4 input 0,1: For inputting the count/capture trigger of a 16-bit timer 4                  |

| TB5IN0,TB5IN1 |                | Input           | 16-bit timer 5 input 0,1: For inputting the count/capture trigger of a 16-bit timer 5                  |

| P30           | 1              | Output          | Port 30: Port used exclusively for output                                                              |

| RD            |                | Output          | Read: Strobe signal for reading external memory                                                        |

| P31           | 1              | Output          | Port 31: Port used exclusively for output                                                              |

| WR            |                | Output          | Write: Strobe signal for writing data of D0 to D7 pins                                                 |

| P32           | 1              | Input/output    | Port 32: Input/output port (with pull-up)                                                              |

| HWR           |                | Output          | Write upper-pin data: Strobe signal for writing data of D8 to D15 pins                                 |

| TC0IN         |                | Input           | For inputting the capture trigger for 32-bit timer                                                     |

| P33           | 1              | Input/output    | Port 33: Input/output port (with pull-up)                                                              |

| WAIT          |                | Input           | Wait: Pin for requesting CPU to put a bus in a wait state                                              |

| RDY           |                | Input           | Ready: Pin for notifying CPU that a bus is ready                                                       |

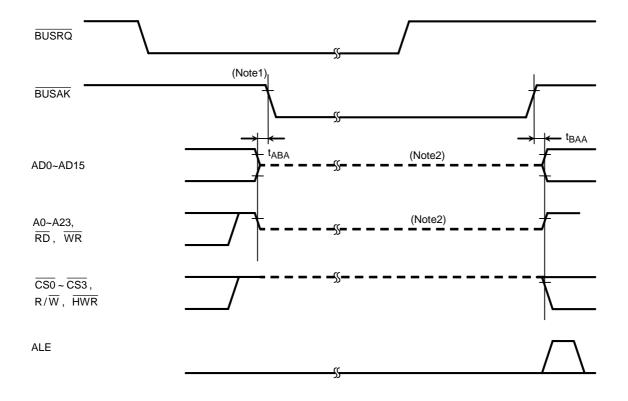

| P34           | 1              | Input/output    | Port 34: Input/output port (with pull-up)                                                              |

| BUSRQ         |                | Input           | Bus request: Signal requesting CPU to allow an external master to take the bus control authority       |

| TBEOUT        |                | Output          | 16-bit timer E output: Pin for outputting 16-bit timer E                                               |

| P35           | 1              | Input/output    | Port 35: Input/output port (with pull-up)                                                              |

| BUSAK         |                | Output          | Bus acknowledge: Signal notifying that CPU has released the bus control authority in response to BUSRQ |

| TC1IN         |                | Input           | For inputting the capture trigger for 32-bit timer                                                     |

| P36           | 1              | Input/output    | Port 36: Input/output port (with pull-up)                                                              |

| R/W           |                | Output          | Read/write: "1" shows a read cycle or a dummy cycle. "0" shows a write cycle.                          |

| TC2IN         |                | Input           | For inputting the capture trigger for 32-bit timer                                                     |

| P37           | 1              | Input/output    | Port 37: Input/output port (with pull-up)                                                              |

| ALE           |                | Output          | Address latch enable (address latch is enabled only if access to external memory is taking place)      |

| TC3IN         |                | Input           | For inputting the capture trigger for 32-bit timer                                                     |

| P40           | 1              | Input/output    | Port 40: Input/output port (with pull-up)                                                              |

| CS0           |                | Output          | Chip select 0: "0" is output if the address is in a designated address area.                           |

| KEY24         |                | Input           | KEY on wake up input 24: (Dynamic pull up is selectable) Input with Schmitt trigger with Noise filter  |

| P41           | 1              | Input/output    | Port 41: Input/output port (with pull-up)                                                              |

| CS1           |                | Output          | Chip select 1: "0" is output if the address is in a designated address area.                           |

| KEY25         |                | Input           | KEY on wake up input 25: (Dynamic pull up is selectable) Input with Schmitt trigger with Noise filter  |

| P42           | 1              | Input/output    | Port 42: Input/output port (with pull-up)                                                              |

| CS2           |                | Output          | Chip select 2: "0" is output if the address is in a designated address area.                           |

| KEY26         |                | Input           | KEY on wake up input 26: (Dynamic pull up is selectable)                                               |

| INL 120       |                | при             | Input with Schmitt trigger with Noise filter                                                           |

Table 2-3 Pin Names and Functions (2 of 6)

| Pin name                      | Number of pins | Input or output                 | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|-------------------------------|----------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| P43                           | 1              | Input/output                    | Port 43: Input/output port (with pull-up)                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| CS3                           |                | Output                          | Chip select 3: "0" is output if the address is in a designated address area.                                                                                                                                                                                                                                                                                                                                                                                         |  |

| KEY27                         |                | Input                           | KEY on wake up input 27: (Dynamic pull up is selectable) Input with Schmitt trigger with Noise filter                                                                                                                                                                                                                                                                                                                                                                |  |

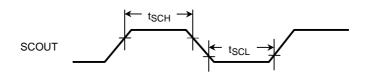

| P44                           | 1              | Input/output                    | Port 44: Input/output port (with pull-up)                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| SCOUT                         |                | Output                          | System clock output: Selectable between high- and low-speed clock outputs, as in the case of CPU                                                                                                                                                                                                                                                                                                                                                                     |  |

| P45<br>BUSMD                  | 1              | Input/output<br>Input           | Port 45: Input/output port (with pull-up) Pin for setting an external bus mode: This pin functions as a multiplexed bus by sampling the "H (DVCC3) level" at the rise of a reset signal. It also functions as a separate bus by sampling "L" at the rise of a reset signal. When performing a reset operation, pull it up or down according to a bus mode to be used. Input with Schmitt trigger.  (After a reset operation is performed, it can be used as a port.) |  |

| P46<br>ENDIAN                 | 1              | Input/output<br>Input           | Port 46: Input/output port (with pull-up)  This pin is used to set a mode. It performs a big-endian operation by sampling the "H (DVCC3) level" at the rise of a reset signal, and performs a little-endian operation by sampling "L" at the rise of a reset signal. When performing a reset operation, pull it up or down according to the type of endian to be used.  (After a reset operation is performed, it can be used as a port.) Input with Schmitt trigger |  |

| P47                           | 1              | Input/output                    | Port 47: Input/output port (with pull-up)                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| TBFOUT                        |                | Output                          | 16-bit timer F output: Pin for outputting a 16-bit timer F                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| P50-P53<br>A0-A3<br>INTC-INTF | 4              | Input/output<br>Output<br>Input | Port 5: Input/output port (with pull-up) that allows input/output to be set in units of bits Address: Address buses 0 to 3 (separate bus mode) Interrupt request pins C to F: Selectable between "H" level, "L" level, rising edge, and falling edge Input pin with Schmitt trigger with Noise filter                                                                                                                                                                |  |

| P54,P55<br>A4,A5              | 2              | Input/output Output             | Port 5: Input/output port (with pull-up) that allows input/output to be set in units of bits Address: Address buses 4 and 5 (separate bus mode)                                                                                                                                                                                                                                                                                                                      |  |

| TB0OUT                        |                | Output                          | 16-bit timer 0 output: Pin for outputting a 16-bit timer 0                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| TB1OUT                        |                | Output                          | 16-bit timer 1 output: Pin for outputting a 16-bit timer 1                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| P56,P57                       | 2              | Input/output                    | Port 5: Input/output port (with pull-up) that allows input/output to be set in units of bits                                                                                                                                                                                                                                                                                                                                                                         |  |

| A6,A7                         |                | Output                          | Address: Address buses 6 and 7 (separate bus mode)                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| TB2OUT                        |                | Output                          | 16-bit timer 2 output: Pin for outputting a 16-bit timer 2                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| TB3OUT<br>KEY28,KEY29         |                | Output<br>Input                 | 16-bit timer 3 output: Pin for outputting a 16-bit timer 3 KEY on wake up input 28 and 29: (Dynamic pull up is selectable) Input pin with Schmitt trigger with Noise filter                                                                                                                                                                                                                                                                                          |  |

| P60                           | 1              | Input/output                    | Port 60: Input/output port (with pull-up)                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| A8                            | 1              | Output                          | Address: Address bus 8 (separate bus mode)                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| TXD0                          |                | Output                          | Sending serial data 0: Open drain output pin depending on the program used                                                                                                                                                                                                                                                                                                                                                                                           |  |

| P61                           | 1              | Input/output                    | Port 61: Input/output port (with pull-up)                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| A9                            |                | Output                          | Address: Address bus 9 (separate bus mode)                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| RXD0<br>INTA                  |                | Input<br>Input                  | Receiving serial data 0 Interrupt request pin A: Selectable between "H" level, "L" level, rising edge, falling edge, and both rising and falling edges.                                                                                                                                                                                                                                                                                                              |  |

|                               |                |                                 | Input pin with Schmitt trigger with Noise filter                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| P62                           | 1              | Input/output                    | Port 62: Input/output port (with pull-up)                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| A10                           |                | Output                          | Address: Address bus 10 (separate bus mode)                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| SCLK0                         |                | Input/output                    | Serial clock input/output 0                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| CTS0                          |                | Input                           | Handshake input pin Open drain output pin depending on the program used                                                                                                                                                                                                                                                                                                                                                                                              |  |

| P63                           | 1              | Input/output                    | Port 63: Input/output port (with pull-up)                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| A11                           |                | Output                          | Address: Address bus 11 (separate bus mode)                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| TXD1                          |                | Output                          | Sending serial data 1: Open drain output pin depending on the program used                                                                                                                                                                                                                                                                                                                                                                                           |  |

| P64                           | 1              | Input/output                    | Port 64: Input/output port (with pull-up)                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| A12                           |                | Output                          | Address: Address bus 12 (separate bus mode)                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| RXD1<br>INTB                  |                | Input<br>Input                  | Receiving serial data 1  Interrupt request pin B: Selectable between "H" level, "L" level, rising edge, falling edge, and both rising and falling edges.                                                                                                                                                                                                                                                                                                             |  |

|                               |                |                                 | Input pin with Schmitt trigger with Noise filter                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

Table 2-4 Pin Names and Functions (3 of 6)

| Pin name       | Number of pins | Input or output | Function                                                                                                                                                                                |

|----------------|----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P65            | 1              | Input/output    | Port 65: Input/output port (with pull-up)                                                                                                                                               |

| A13            |                | Output          | Address: Address bus 13 (separate bus mode)                                                                                                                                             |

| SCLK1          |                | Input/output    | Serial clock input/output 1                                                                                                                                                             |

| CTS1           |                | Input           | Handshake input pin.                                                                                                                                                                    |

|                |                |                 | Open drain output pin depending on the program used                                                                                                                                     |

| P66,P67        | 2              | Input/output    | Port 6: Input/output port (with pull-up) that allows input/output to be set in units of bits                                                                                            |

| A14,A15        |                | Output          | Address: Address buses 14 and 15 (separate bus mode)                                                                                                                                    |

| TB4OUT         |                | Output          | 16-bit timer 4 output: Pin for outputting a 16-bit timer 4                                                                                                                              |

| TB5OUT         |                | Output          | 16-bit timer 5 output: Pin for outputting a 16-bit timer 5                                                                                                                              |

| P70-P73        | 4              | Input           | Port 7: Port used exclusively for input (with pull-up)                                                                                                                                  |

| AIN0-AIN3      |                | Input           | Analog input: Input from A/D converter                                                                                                                                                  |

| P74-P77        | 4              | Input           | Port 7: Port used exclusively for input (with pull-up)                                                                                                                                  |

| AIN4-AIN7      |                | Input           | Analog input: Input from A/D converter                                                                                                                                                  |

| KEY00-KEY03    |                | Input           | KEY on wake up input 00 to 03: (Dynamic pull up is selectable) Input pin with Schmitt trigger with Noise filter                                                                         |

| P80-P83        | 4              | Input           | Port 8: Port used exclusively for input (with pull-up)                                                                                                                                  |

| AIN8-AIN11     |                | Input           | Analog input: Input from A/D converter                                                                                                                                                  |

| KEY04-KEY07    |                | Input           | KEY on wake up input 04 to 07: (Dynamic pull up is selectable)                                                                                                                          |

|                |                | _               | Input pin with Schmitt trigger with Noise filter                                                                                                                                        |

| P84-P87        | 4              | Input           | Port 8: Port used exclusively for input (with pull-up)                                                                                                                                  |

| AIN12-AIN15    |                | Input           | Analog input: Input from A/D converter                                                                                                                                                  |

| INT6-9         |                |                 | Interrupt request pins 6 to 9: Selectable between "H" level, "L" level, rising edge, falling edge, and both rising and falling edges.  Input pin with Schmitt trigger with Noise filter |

| P90-P92        | 3              | Input/output    | Port 9: Input/output port (with pull-up) that allows input/output to be set in units of bits                                                                                            |

| TB6OUT         |                | Output          | 16-bit timer 6 output: Pin for outputting a 16-bit timer 6                                                                                                                              |

| TB7OUT         |                | Output          | 16-bit timer 7 output: Pin for outputting a 16-bit timer 7                                                                                                                              |

| TB8OUT         |                | Output          | 16-bit timer 8 output: Pin for outputting a 16-bit timer 8                                                                                                                              |

| P93            | 1              | Input/output    | Port 93: Input/output port (with pull-up)                                                                                                                                               |

| TXD2           | 1              | Output          | Sending serial data 2: Open drain output pin depending on the program used                                                                                                              |

| P94            | 1              | Input/output    | Port 94: Input/output port (with pull-up)                                                                                                                                               |

| RXD2           |                | Input           | Receiving serial data 2                                                                                                                                                                 |

| P95            | 1              | Input/output    | Port 95: Input/output port (with pull-up)                                                                                                                                               |

| SCLK2          | •              | Input/output    | Serial clock input/output 2                                                                                                                                                             |

| CTS2           |                | Input           | Handshake input pin Open drain output pin depending on the program used                                                                                                                 |

| P96,P97        | 2              | Input/output    | Ports 96 and 97: Input/output port (with pull-up) that allows input/output to be set in units of                                                                                        |

| TB9OUT         | _              | Output          | bits  16-bit timer 9 output: Pin for outputting a 16-bit timer 9                                                                                                                        |

| TBAOUT         |                | Output          | 16-bit timer A output: Pin for outputting a 16-bit timer A                                                                                                                              |

| PA0            | 1              | Input/output    | Port A0: Input/output port (with pull-up)                                                                                                                                               |

| TB6IN0         |                | Input           | 16-bit timer 6 input 0: For inputting the capture trigger of a 16-bit timer 6                                                                                                           |

| INT0           |                | Input           | Interrupt request pin 0: Selectable between "H" level, "L" level, rising edge, falling edge, and both rising and falling edges.  Input pin with Schmitt trigger with Noise filter       |

| PA1            | 1              | Input/output    | Port A1: Input/output port (with pull-up)                                                                                                                                               |

| TB6IN1         |                | Input           | 16-bit timer 6 input 1: For inputting the capture trigger of a 16-bit timer 6                                                                                                           |

| INT1           |                | Input           | Interrupt request pin 1: Selectable between "H" level, "L" level, rising edge, falling edge, and both rising and falling edges                                                          |

| PA2            | 1              | Innut/out       | Input pin with Schmitt trigger with Noise filter                                                                                                                                        |

| TB7IN0         | 1              | Input/output    | Port A2: Input/output port (with pull-up)  16 hit timer 7 input 0: For inputting the centure trigger of a 16 hit timer 7                                                                |

| IB/INU<br>INT2 |                | Input           | 16-bit timer 7 input 0: For inputting the capture trigger of a 16-bit timer 7  Interrupt request pin 0: Selectable "H" level, "L" level, rising edge, falling edge, and both            |

| 111117         |                | Input           | rising and falling edges.  Input pin with Schmitt trigger with Noise filter                                                                                                             |

| PA3            | 1              | Input/output    | Port A3: Input/output port (with pull-up)                                                                                                                                               |

| TB7IN1         |                | Input           | 16-bit timer 7 input 1: For inputting the capture trigger of a 16-bit timer 7                                                                                                           |

| INT3           |                | Input           | Interrupt request pin 1: Selectable between "H" level, "L" level, rising edge, falling edge, and both rising and falling edges.                                                         |

|                |                |                 | Input pin with Schmitt trigger with Noise filter                                                                                                                                        |

Table 2-5 Pin Names and Functions (4 of 6)

| Pin name          | Number of pins | Input or output | Function                                                                                                                                                                        |

|-------------------|----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PA4               | 1              | Input/output    | Port A4: Input/output port (with pull-up)                                                                                                                                       |

| TB8IN0            |                | Input           | 16-bit timer 8 input 0: For inputting the capture trigger of a 16-bit timer 8                                                                                                   |

| INT4              |                | Input           | Interrupt request pin 0: Selectable between "H" level, "L" level, rising edge, falling edge, and                                                                                |

|                   |                |                 | both rising and falling edges Input pin with Schmitt trigger with Noise filter                                                                                                  |

| PA5               | 1              | Input/output    | Port A5: Input/output port (with pull-up)                                                                                                                                       |

| TB8IN1            |                | Input           | 16-bit timer 8 input 1: For inputting the capture trigger of a 16-bit timer 8                                                                                                   |

| INT5              |                | Input           | Interrupt request pin 1: Selectable between "H" level, "L" level, rising edge, falling edge, and both rising and falling edges Input pin with Schmitt trigger with Noise filter |

| PA6               | 1              | Input/output    | Port A6: Input/output port (with pull-up)                                                                                                                                       |

| TB2IN0            |                | Input           | 16-bit timer 2 input 0: For inputting the capture trigger of a 16-bit timer 2                                                                                                   |

| PA7               |                | Input/output    | Port A7: Input/output port (with pull-up)                                                                                                                                       |

| TB2IN1            |                | Input           | 16-bit timer 2 input 1: For inputting the capture trigger of a 16-bit timer 2                                                                                                   |

| PB0               | 1              | Input/output    | Port B0: Input/output port (with pull-up)                                                                                                                                       |

| TB3IN0            |                | Input           | 16-bit timer 3 input 0: For inputting the capture trigger of a 16-bit timer 3                                                                                                   |

| PB1               | 1              | Input/output    | Port B1: Input/output port (with pull-up)                                                                                                                                       |

| TB3IN1            |                | Input           | 16-bit timer 3 input 1: For inputting the capture trigger of a 16-bit timer 3                                                                                                   |

| PB2               | 1              | Input/output    | Port B2: Input/output port (with pull-up)                                                                                                                                       |

| HTXD0             |                | Output          | Sending serial data 0 at high speeds: Open drain output pin depending on the program used                                                                                       |

| PB3               | 1              | Input/output    | Port B3: Input/output port (with pull-up)                                                                                                                                       |

| HRXD0             |                | Input           | Receiving serial data 0 at high speeds                                                                                                                                          |

| PB4               | 1              | Input/output    | Port B4: Input/output port (with pull-up)                                                                                                                                       |

| HSCLK0            |                | Input/output    | High-speed serial clock input/output 0                                                                                                                                          |

| HCTS0             |                | Input           | Handshake input pin: Open drain output pin depending on the program used                                                                                                        |

| PB5               | 1              | Input/output    | Port B5: Input/output port (with pull-up)                                                                                                                                       |

| HTXD1             |                | Output          | Sending serial data 1 at high speeds: Open drain output pin depending on the program used                                                                                       |

| PB6               | 1              | Input/output    | Port B6: Input/output port (with pull-up)                                                                                                                                       |

| HRXD1             |                | Input           | Receiving serial data 1 at high speeds                                                                                                                                          |

| PB7               | 1              | Input/output    | Port B7: Input/output port (with pull-up)                                                                                                                                       |

| HSCLK1            |                | Input/output    | High-speed serial clock input/output 1                                                                                                                                          |

| HCTS1             |                | Input           | Handshake input pin:  Open drain output pin depending on the program used                                                                                                       |

| PC0               | 1              | Input/output    | Port C0: Input/output port (with pull-up)                                                                                                                                       |

| TBTIN             |                | Input           | 32-bit time base timer input: For inputting a 32-bit time base timer                                                                                                            |

| KEY30             |                |                 | KEY on wake up input 30: (Dynamic pull up is selectable)                                                                                                                        |

|                   |                |                 | Input with Schmitt trigger with Noise filter                                                                                                                                    |

| PC1-PC4           | 4              | Input/output    | Ports C1 to C4: Input/output ports (with pull-up) that allow input/output to be set in units of bits                                                                            |

| TCOUT0-<br>TCOUT3 |                | Output          | Outputting 32-bit timer if the result of a comparison is a match                                                                                                                |

| PC5               | 1              | Input/output    | Port C5: Input/output port (with pull-up)                                                                                                                                       |

| SO                | 1              | Output          | Pin for sending data if the serial bus interface operates in the SIO mode                                                                                                       |

| SDA               |                | Input/output    | Pin for sending and receiving data if the serial bus interface operates in the I2C mode                                                                                         |

|                   |                | pas output      | Open drain output pin depending on the program used Input with Schmitt trigger                                                                                                  |

| PC6               | 1              | Input/output    | Port C6: Input/output port (with pull-up)                                                                                                                                       |

| SI                |                | Input           | Pin for receiving data if the serial bus interface operates in the SIO mode                                                                                                     |

| SCL               |                | Input/output    | Pin for inputting and outputting a clock if the serial bus interface operates in the I2C mode Open drain output pin depending on the program used Input with Schmitt trigger    |

| PC7               | 1              | Input/output    | Port C7: Input/output port (with pull-up)                                                                                                                                       |

| SCK               |                | Input/output    | Pin for inputting and outputting a clock if the serial bus interface operates in the SIO mode<br>Open drain output pin depending on the program used                            |

Table 2-6 Pin Names and Functions (5 of 6)

| Pin name    | Number of pins | Input or output | Function                                                                                                                     |  |

|-------------|----------------|-----------------|------------------------------------------------------------------------------------------------------------------------------|--|

| PD0         | 1              | Input/output    | Port D0: Input/output port (with pull-up)                                                                                    |  |

| HTXD2       |                | Output          | Sending serial data 2 at high speeds: Open drain output pin depending on the program used                                    |  |

| PD1         | 1              | Input/output    | Port D1: Input/output port (with pull-up)                                                                                    |  |

| HRXD2       |                | Input           | Receiving serial data 2 at high speeds                                                                                       |  |

| PD2         | 1              | Input/output    | Port D2: Input/output port (with pull-up)                                                                                    |  |

| HSCLK2      |                | Input/output    | High-speed serial clock input/output 2                                                                                       |  |

| HCTS2       |                | Input           | Handshake input pin: Open drain output pin depending on the program used                                                     |  |

| PD3-PD5     | 3              | Input/output    | Ports D3 to D5: Input/output ports (with pull-up) that allow input/output to be set in units of bits                         |  |

| TBBOUT-     |                | Output          | 16-bit timers B, C and D outputs: Pin for outputting 16-bit timers B, C and D                                                |  |

| TBDOUT      |                | <b>.</b>        |                                                                                                                              |  |

| PD6         | 1              | Input/output    | Port D6: Input/output port (with pull-up) that allows input/output to be set in units of bits                                |  |

| ADTRG       | _              | Input           | Pin (with Schmitt trigger) for starting A/D trigger or A/D converter from an external source                                 |  |

| KEY31       |                | Input           | KEY on wake up input 31: (Dynamic pull up is selectable) Input with Schmitt trigger with Noise filter                        |  |

| PE0-PE7     | 8              | Input/output    | Port E: Input/output port (with pull-up) that allows input/output to be set in units of bits                                 |  |

| KEY08-KEY15 |                | Input           | KEY on wake up input 08 to 15: (Dynamic pull up is selectable)                                                               |  |

|             |                |                 | Input with Schmitt trigger with Noise filter                                                                                 |  |

| PF0,PF2     | 2              | Input/output    | Port F: Input/output port (with pull-up) that allows input/output to be set in units of bits                                 |  |

| DREQ0,4     |                | Input           | DMA request signals 0 and 4: For inputting the request to transfer data by DMA from an external I/O device to DMAC0 or DMAC4 |  |

| KEY16,KEY18 |                | Input           | KEY on wake up input 16 to 19: (Dynamic pull up is selectable)  Input with Schmitt trigger with Noise filter                 |  |

| PF1,PF3     | 2              | Input/output    | Port F: Input/output port (with pull-up) that allows input/output to be set in units of bits                                 |  |

| DACK0,4     |                | Output          | DMA acknowledge signals 0 and 4: Signal showing that DREQ0 and DREQ4 have acknowledged a DMA transfer request                |  |

| KEY17,KEY19 |                | Input           | KEY on wake up input 16 to 19: (Dynamic pull up is selectable) Input with Schmitt trigger with Noise filter                  |  |

| PF4-PF7     | 4              | Input/output    | Port F: Input/output port (with pull-up) that allows input/output to be set in units of bits                                 |  |

| KEY20-KEY23 |                | Input           | KEY on wake up input 20 to 23: (Dynamic pull up is selectable)                                                               |  |

| TCOUT4-     |                |                 | Input with Schmitt trigger                                                                                                   |  |

| TCOUT7      |                | Output          | Outputting 32-bit timer if the result of a comparison is a match with Noise filter                                           |  |

| PG0-PG7     | 8              | Input/output    | Port G: Input/output port (with pull-up) that allows input/output to be set in units of bits                                 |  |

| TPD0-TPD7   |                | Output          | Outputting trace data from the data access address: Signal for DSU-ICE                                                       |  |

| PH0-PH7     | 8              | Input/output    | Port H: Input/output port (with pull-up) that allows input/output to be set in units of bits                                 |  |

| TPC0-TPC7   |                | Output          | Outputting trace data from the program counter: Signal for DSU-ICE                                                           |  |

| TPD0-TPD7   |                | Output          | Outputting trace data from the data access address: Signal for DSU-ICE                                                       |  |

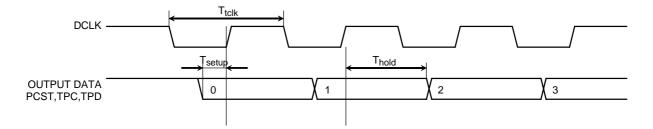

| DCLK        | 1              | Output          | Debug clock: Signal for DSU-ICE                                                                                              |  |

| EJE         | 1              | Input           | DSU-ICE enable: Signal for DSU-ICE (with Schmitt trigger) (with pull-up) with Noise filter                                   |  |

| PCST4-0     | 4              | Output          | PC trace status: Signal for DSU-ICE                                                                                          |  |

| DINT        | 1              | Input           | Debug interrupt: Signal for DSU-ICE (input with Schmitt trigger and pull-up) with Noise filter                               |  |

| TOVR/TSR    | 1              | Output          | Outputting the status of PD data overflow status: Signal for DSU-ICE                                                         |  |

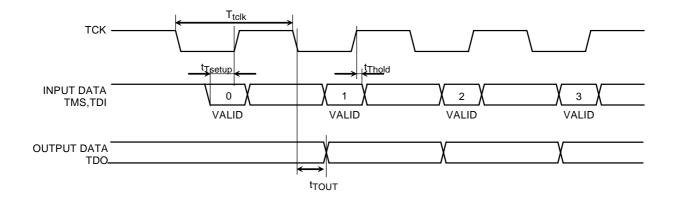

| TCK         | 1              | Input           | Test clock input: Signal for testing DSU-ICE (with Schmitt trigger and pull-up) with Noise filter                            |  |

| TMS         | 1              | Input           | Test mode select input: Signal for testing DSU-ICE (with Schmitt trigger and pull-up)                                        |  |

| TDI         | 1              | Input           | Test data input E: Signal for testing JTAG (with Schmitt trigger and pull-up)                                                |  |

| TDO         | 1              | Output          | Test data output: Signal for testing DSU-ICE                                                                                 |  |

| TRST        | 1              | Input           | Test reset input: Signal for testing DSU-ICE (with Schmitt trigger and pull-down) with Noise filter                          |  |

| RESET       | 1              | Input           | Reset: Initializing LSI (with pull-up) Input with Schmitt trigger with Noise filter                                          |  |

|             |                | i               |                                                                                                                              |  |

| X1/X2       | 2              | Input/output    | Pin for connecting a high-speed oscillator (X1: Input with Schmitt trigger)                                                  |  |

Table 2-7 Pin Names and Functions (6 of 6)

| Pin name | Number of pins | Input or output | Function                                                                                                                                                                                                                                                                                                                                                                      |

|----------|----------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

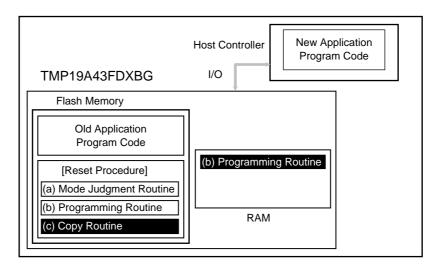

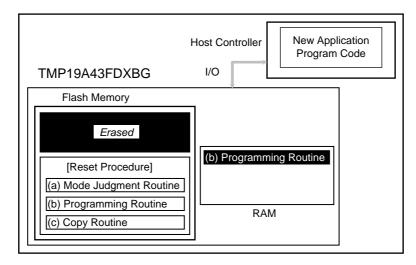

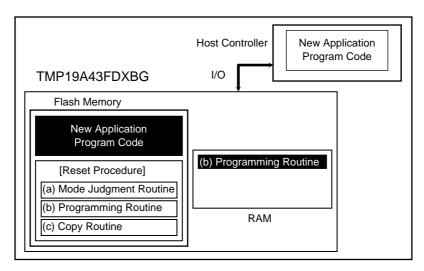

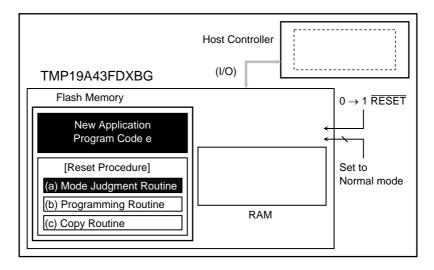

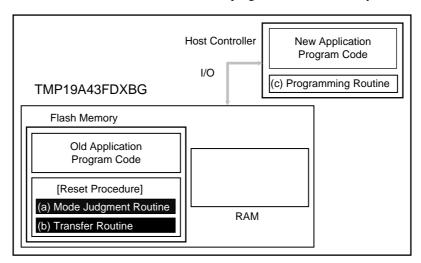

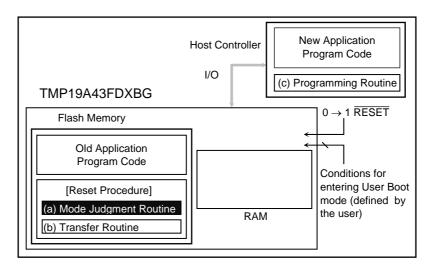

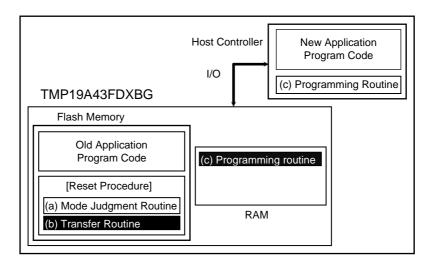

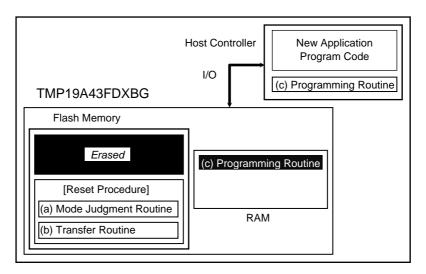

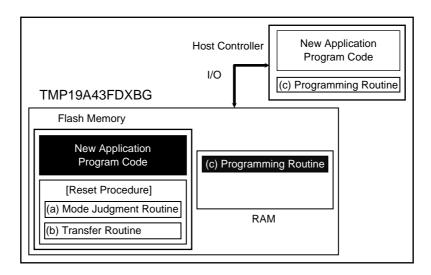

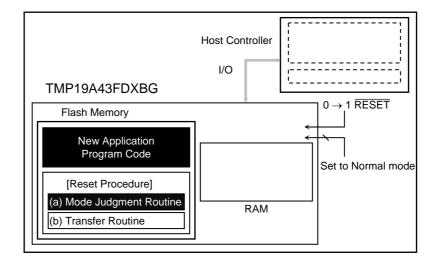

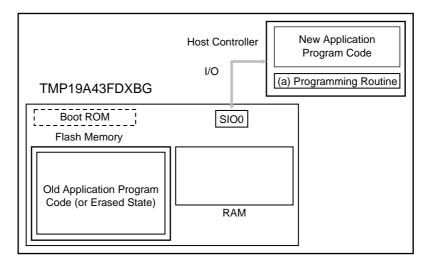

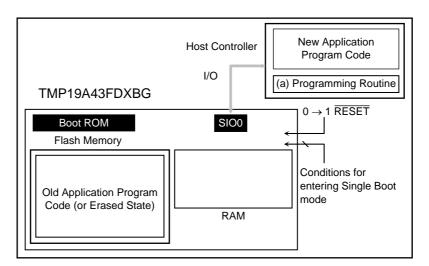

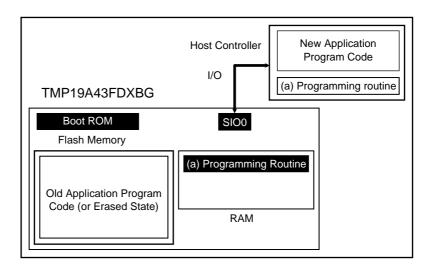

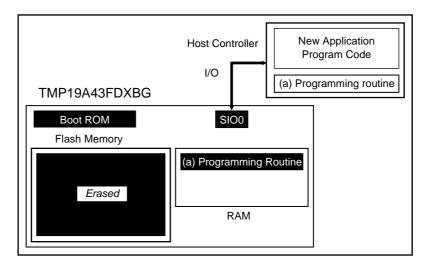

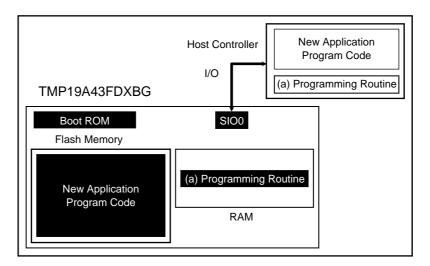

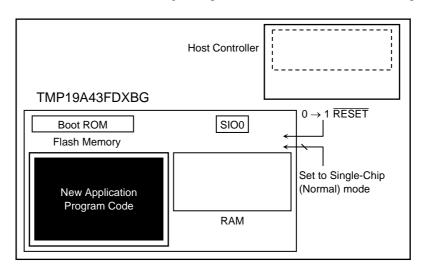

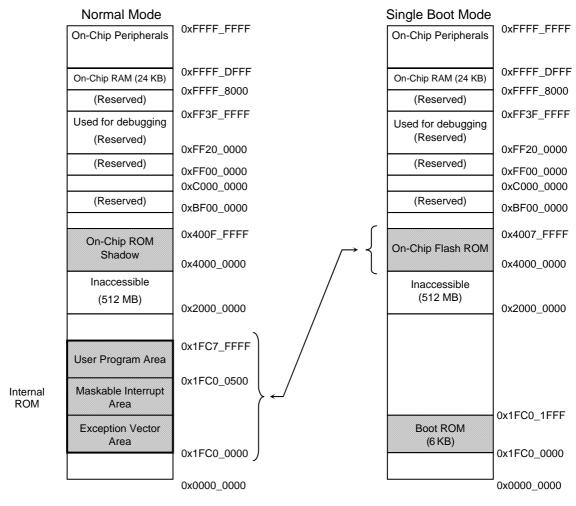

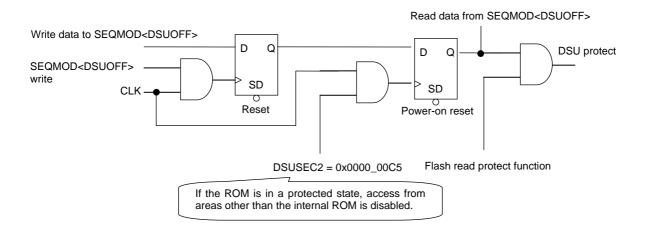

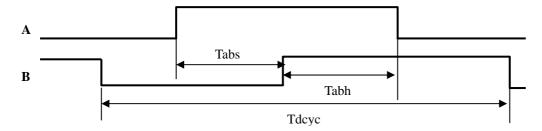

| BOOT     | 1              | Input           | Pin for setting a single boot mode: This pin goes into single boot mode by sampling "L" at the rise of a reset signal. It is used to overwrite internal flash memory. By sampling "H (DVCC3) level" at the rise of a reset signal, it performs a normal operation. This pin should be pulled up under normal operating conditions. Pull it up when resetting.  (With pull-up) |