# 1.5 MHz, 600 mA, High-Efficiency, Low Quiescent Current, Adjustable Output Voltage Step-Down Converter

The NCP9001 step-down PWM DC-DC converter is optimized for portable applications powered from one cell Li-ion or three cell Alkaline/NiCd/NiMH batteries. The device is available in an adjustable output voltage from 0.9 V to 3.3 V. It uses synchronous rectification to increase efficiency and reduce external part count. The device also has a built-in 1.5 MHz (nominal) oscillator which reduces component size by allowing a small inductor and capacitors. Automatic switching PWM/PFM mode offers improved system efficiency.

Finally, it includes an integrated soft-start, cycle-by-cycle current limiting, and thermal shutdown protection. The NCP9001 is available in the space saving, low profile TSOP5 package.

#### **Features**

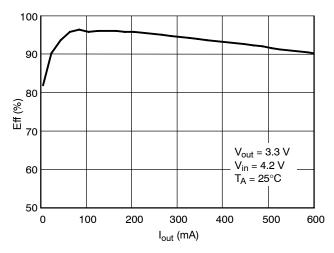

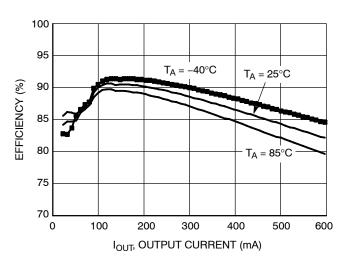

- 95.3% of Efficiency for 3.3 V Output and 4.2 V Input and 80 mA Load-Current

- Sources up to 600 mA

- 1.5 MHz Switching Frequency

- Adjustable Output Voltage from 0.9 V to 3.3 V

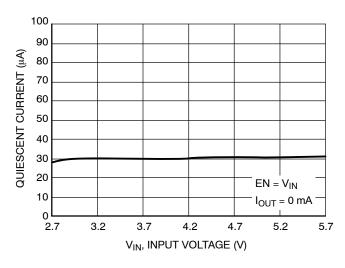

- 30 µA Quiescent Current

- Synchronous Rectification for Higher Efficiency

- 2.7 V to 5.5 V Input Voltage Range

- Thermal Limit Protection

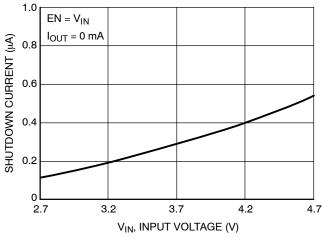

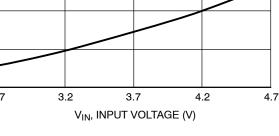

- Shutdown Current Consumption of 0.3 µA

- Short Circuit Protection

- This is a Pb-Free Device

#### **Typical Applications**

- Cellular Phones, Smart Phones and PDAs

- Digital Still/Video Cameras

- MP3 Players and Portable Audio Systems

- Wireless and DSL Modems

- Portable Equipment

- USB Powered Devices

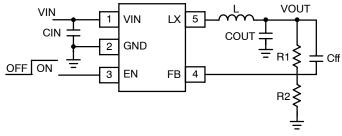

Figure 1. Typical Application

# ON Semiconductor®

http://onsemi.com

# MARKING DIAGRAM

TSOP-5 SN SUFFIX CASE 483

DBP = Specific Device Code A = Assembly Location

Y = Year W = Work Week ■ = Pb-Free Package

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

| Device       | Package             | Shipping         |

|--------------|---------------------|------------------|

| NCP9001SNT1G | TSOP-5<br>(Pb-Free) | 3000/Tape & Reel |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

Figure 2. Efficiency vs. Output Current

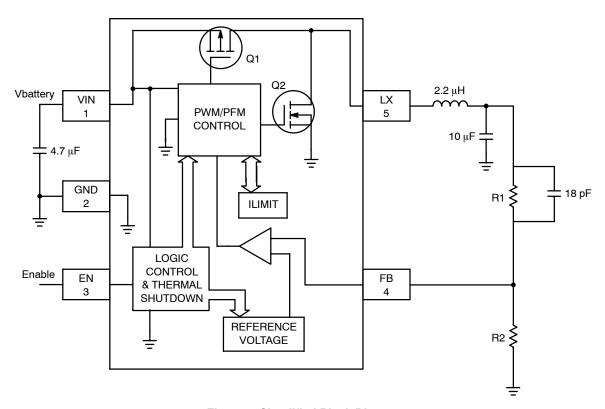

Figure 3. Simplified Block Diagram

## **PIN FUNCTION DESCRIPTION**

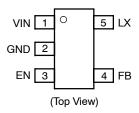

| Pin No.<br>TSOP5 | Pin No.<br>UDFN6 | Symbol | Function               | Description                                                                                                             |

|------------------|------------------|--------|------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 1                | 3                | VIN    | Analog Input           | Power Supply Input for Analog V <sub>CC</sub> .                                                                         |

| 2                | 2, 4             | GND    | Analog/Power<br>Ground | Ground connection for the NFET Power Stage and the Analog Sections of the IC.                                           |

| 3                | 1                | EN     | Digital Input          | Enable for Switching Regulator. This pin is active high. Do not float this pin.                                         |

| 4                | 6                | FB     | Analog Input           | Feedback voltage from the output of the power supply. This is the input to the error amplifier.                         |

| 5                | 5                | LX     | Analog Output          | Connection from Power MOSFETs to the Inductor. For one option, an output discharge circuit sinks current from this pin. |

# **PIN CONNECTIONS**

Figure 4. Pin Connections

## **MAXIMUM RATINGS**

| Rating                                                           | Symbol           | Value      | Unit    |

|------------------------------------------------------------------|------------------|------------|---------|

| Minimum Voltage All Pins                                         | V <sub>min</sub> | -0.3       | V       |

| Maximum Voltage All Pins (Note 2)                                | V <sub>max</sub> | 7.0        | V       |

| Maximum Voltage Enable, FB, LX                                   | V <sub>max</sub> | VIN + 0.3  | V       |

| Thermal Resistance, Junction -to-Air                             | $R_{\theta JA}$  | 200        | °C/W    |

| Operating Ambient Temperature Range                              | T <sub>A</sub>   | -40 to 85  | °C      |

| Storage Temperature Range                                        | T <sub>stg</sub> | -55 to 150 | °C      |

| Junction Operating Temperature                                   | Tj               | -40 to 125 | °C      |

| Latch-up Current Maximum Rating (T <sub>A</sub> = 85°C) (Note 4) | Lu               | +/-100     | mA      |

| ESD Withstand Voltage (Note 3) Human Body Model Machine Model    | Vesd             | 2.0<br>200 | kV<br>V |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

- 1. Maximum electrical ratings are defined as those values beyond which damage to the device may occur at  $T_A = 25$ °C.

- According to JEDEC standard JESD22–A108B.

This device series contains ESD protection and exceeds the following tests: Human Body Model (HBM) per JEDEC standard: JESD22-A114. Machine Model (MM) per JEDEC standard: JESD22-A115.

- 4. Latchup current maximum rating per JEDEC standard: JESD78.

**ELECTRICAL CHARACTERISTICS** (Typical values are referenced to  $T_A = +25^{\circ}C$ , Min and Max values are referenced  $-40^{\circ}C$  to  $+85^{\circ}C$  ambient temperature, unless otherwise noted, operating conditions  $V_{IN} = 3.6$  V,  $V_{OUT} = 1.8$  V, unless otherwise noted.)

| Characteristic                                                                | Symbol               | Min    | Тур             | Max    | Unit         |

|-------------------------------------------------------------------------------|----------------------|--------|-----------------|--------|--------------|

| Input Voltage Range                                                           | V <sub>IN</sub>      | 2.7    | -               | 5.5    | V            |

| Undervoltage Lockout (V <sub>IN</sub> Falling)                                | V <sub>UVLO</sub>    | 2.3    | 2.5             | 2.6    | V            |

| Quiescent Current<br>PFM No Load                                              | Iq                   | -      | 30              | 45     | μΑ           |

| Standby Current, EN Low                                                       | Istb                 | -      | 0.3             | 1.2    | μΑ           |

| Oscillator Frequency                                                          | F <sub>osc</sub>     | 1.3    | 1.5             | 1.8    | MHz          |

| Peak Inductor Current                                                         | I <sub>LIM</sub>     | _      | 1200            | -      | mA           |

| Feedback Reference Voltage                                                    | V <sub>ref</sub>     | _      | 0.6             | -      | V            |

| FB Pin Tolerance Overtemp @ I <sub>out</sub> = 100 mA                         | VFBtol               | -3.0   | -               | 3.0    | %            |

| Reference Voltage Line Regulation                                             | ΔVFB                 | _      | 0.1             | -      | %            |

| Output Voltage Accuracy @ I <sub>out</sub> = 100 mA (Note 5)                  | V <sub>OUT</sub>     | -3%    | Vnom            | +3%    | V            |

| Minimum Output Voltage                                                        | V <sub>OUT</sub>     | _      | 0.9             | -      | V            |

| Maximum Output Voltage                                                        | V <sub>OUT</sub>     | -      | 3.3             | -      | V            |

| Output Voltage Line Regulation (V <sub>in</sub> = 2.7–5.5)<br>Io = 100 mA     | $\Delta V_{OUT}$     | -      | 0.1             | -      | %            |

| Voltage Load Regulation<br>(IO = 100 mA to 300 mA)<br>(IO = 100 mA to 600 mA) | V <sub>LOADREG</sub> | -<br>- | 0.0005<br>0.001 | -<br>- | %/mA<br>%/mA |

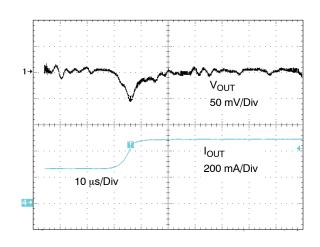

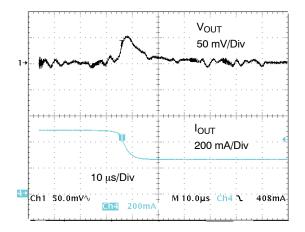

| Load Transient Response (300 mA to 600 mA Load Step, Trise 10 μs)             | V <sub>OUT</sub>     | _      | 50              | -      | mV           |

| Duty Cycle                                                                    | -                    | _      | -               | 100    | %            |

| P-Ch On-Resistance                                                            | RLxH                 | _      | 300             | -      | mΩ           |

| N-Ch On-Resistance                                                            | RLxL                 | _      | 300             | -      | mΩ           |

| P-Ch Leakage Current                                                          | ILeakH               | -      | 0.05            | -      | μΑ           |

| N-Ch Leakage Current                                                          | ILeakL               | -      | 0.01            | -      | μΑ           |

| Enable Pin High                                                               | VENH                 | 1.2    | -               | _      | V            |

| Enable Pin Low                                                                | VENL                 | _      | -               | 0.4    | V            |

| EN << H >> Input Current, EN = 3.6 V                                          | IENH                 | -      | 2.0             | -      | μА           |

| Soft-Start Time                                                               | T <sub>start</sub>   | -      | 350             | 500    | μs           |

| Thermal Shutdown Threshold                                                    | T <sub>SD</sub>      | -      | 160             | -      | °C           |

| Thermal Shutdown Hysteresis                                                   | T <sub>SDH</sub>     | _      | 25              | -      | °C           |

<sup>5.</sup> The overall output voltage tolerance depends upon the accuracy of the external resistor (R1, R2).

100 90 QUIESCENT CURRENT (µA) 80 70 60 50 40  $V_{IN} = 5.5 V$ 30  $V_{IN} = 2.7 V$ 20 10 -40 -20 20 40 100 60 80 TEMPERATURE (°C)

Figure 5. Quiescent Current vs. Supply Voltage

Figure 6. Quiescent Current vs. Temperature

Figure 7. Shutdown Current vs. Supply Voltage

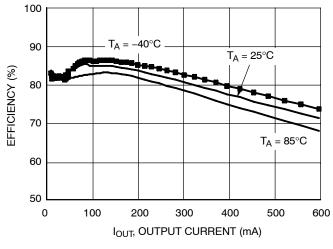

Figure 8. Efficiency vs. Output Current  $(V_{OUT} = 1.8 \text{ V}, V_{IN} = 3.6 \text{ V})$

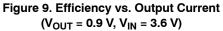

Figure 10. Efficiency vs. Output Current  $(V_{OUT} = 3.3 \text{ V}, V_{IN} = 4.5 \text{ V})$

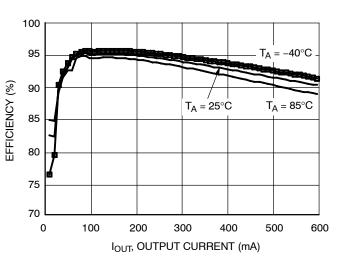

Figure 11. Soft Start Time (V<sub>IN</sub> = 3.6 V)

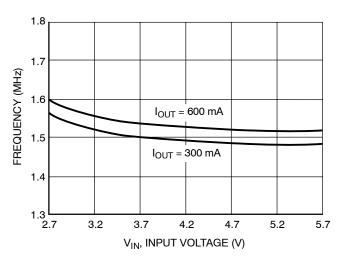

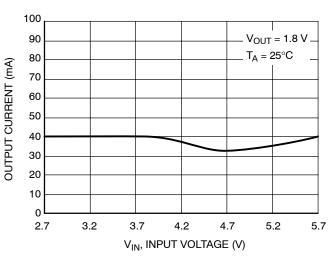

Figure 12. Frequency vs. Input Voltage

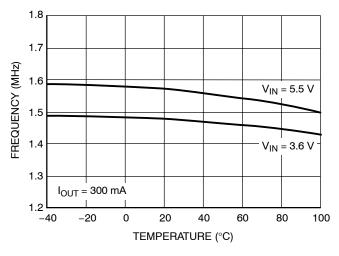

Figure 13. Frequency vs. Temperature

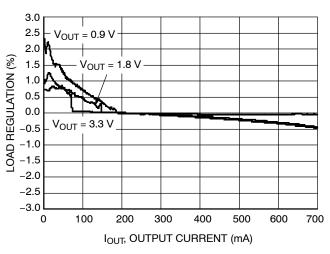

Figure 14. Load Regulation

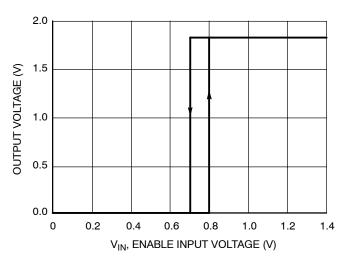

Figure 15. Output Voltage vs. Enable Input Pin Voltage

Figure 16. PFM/PWM Threshold vs. Input Voltage

2.0 1.5 OUTPUT VOLTAGE (%) 1.0  $I_{OUT} = 100 \text{ mA}$ 0.5  $I_{OUT} = 300 \text{ mA}$ 0.0 -0.5  $I_{OUT} = 600 \text{ mA}$ -1.5 $V_{IN} = 3.6 V$ -2.0 -50 100 150 TEMPERATURE (°C)

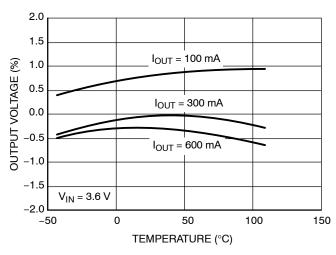

Figure 17. Output Voltage Accuracy (V<sub>OUT</sub> = 0.9 V)

Figure 18. Output Voltage Accuracy (V<sub>OUT</sub> = 1.8 V)

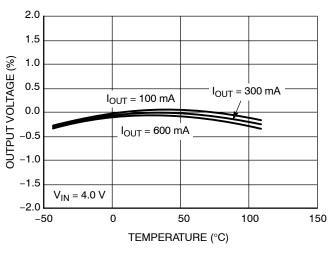

Figure 19. Output Voltage Accuracy (V<sub>OUT</sub> = 3.3 V)

Figure 20. Load Transient Response in PWM Operation (V<sub>IN</sub> = 3.6 V)

Figure 21. Load Transient Response in PWM Operation (V<sub>IN</sub> = 3.6 V)

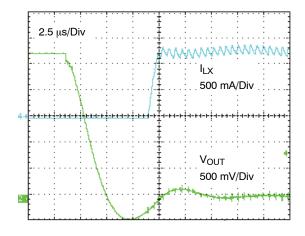

Figure 22. Short Circuit Protection (V<sub>IN</sub> = 3.6 V)

#### **OPERATION DESCRIPTION**

#### Overview

The NCP9001 uses a constant frequency, current mode step-down architecture. Both the main (P-Channel MOSFET) and synchronous (N-Channel MOSFET) switches are internal.

It delivers a constant voltage from either a single Li–Ion or three cell NiMH/NiCd battery to portable devices such as cell phones and PDA. The output voltage is set by the external resistor divider. The NCP9001 sources at least 600 mA, depending on external components chosen.

The NCP9001 works with two modes of operation; PWM/PFM depending on the current required. The device operates in PWM mode at load currents of approximately 40 mA or higher, having voltage tolerance of  $\pm\,3\%$  with 90% efficiency or better. Lighter load currents cause the device to automatically switch into PFM mode for reduced current consumption ( $I_Q$  = 30  $\mu A$  typ) and extended battery life.

Additional features include soft-start, undervoltage protection, current overload protection, and thermal shutdown protection. As shown in Figure 1, only six external components are required for implementation. The part uses an internal reference voltage of 0.6 V. It is recommended to keep the part in shutdown until the input voltage is 2.7 V or higher.

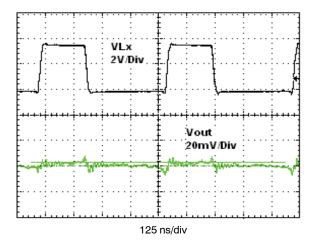

## **PWM Operating Mode**

In this mode, the output voltage of the NCP9001 is regulated by modulating the on-time pulse width of the main switch Q1 at a fixed frequency of 1.5 MHz. The switching of the PMOS Q1 is controlled by a flip-flop driven by the internal oscillator and a comparator that compares the error signal from an error amplifier with the sum of the sensed current signal and compensation ramp. At the beginning of each cycle, the main switch Q1 is turned ON by the rising edge of the internal oscillator clock. The inductor current ramps up until the sum of the current sense signal and compensation ramp becomes higher than the error voltage amplifier. Once this has occurred, the PWM comparator resets the flip-flop, Q1 is turned OFF and the synchronous switch Q2 is turned ON. Q2 replaces the external Schottky diode to reduce the conduction loss and improve the efficiency. To avoid overall power loss, a certain amount of dead time is introduced to ensure Q1 is completely turned OFF before Q2 is being turned ON.

Figure 23. PWM Switching Waveform (V<sub>in</sub> = 3.6 V, V<sub>out</sub> = 1.8 V, I<sub>out</sub> = 300 mA)

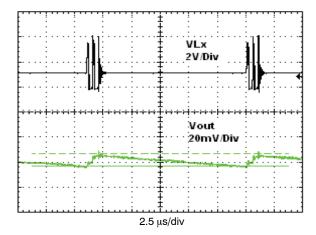

#### **PFM Operating Mode**

Under light load conditions (<40 mA), the NCP9001 enters in low current PFM mode operation to reduce power consumption. The output regulation is implemented by pulse frequency modulation. If the output voltage drops below the threshold of PFM comparator (typically Vnom-2%), a new cycle will be initiated by the PFM comparator to turn on the switch Q1. Q1 remains ON until the peak inductor current reaches 200 mA (nom). Then I<sub>I IM</sub> comparator goes high to switch off Q1. After a short dead time delay, switch rectifier Q2 is turned ON. The negative current detector (NCD) will detect when the inductor current drops below zero and sends the signal to turn off Q2. The output voltage continues to decrease through discharging the output capacitor. When the output voltage falls below the threshold of the PFM comparator, a new cycle starts immediately.

Figure 24. PFM Mode Switching Waveform (V<sub>in</sub> = 3.6 V, V<sub>out</sub> = 1.8 V, I<sub>out</sub> = 30 mA)

# Cycle-by-Cycle Current Limitation

From the block diagram (Figure 3), an  $I_{LIM}$  comparator is used to realize cycle-by-cycle current limit protection. The comparator compares the LX pin voltage with the reference voltage, which is biased by a constant current. If the inductor current reaches the limit, the  $I_{LIM}$  comparator detects the LX voltage falling below the reference voltage and releases the signal to turn off the switch Q1. The cycle-by-cycle current limit is set at 1200 mA (nom).

#### **Short Circuit Protection**

When the output is shorted to ground, the device limits the inductor current. The duty-cycle is minimum and the consumption on the input line is 300 mA (Typ). When the short circuit condition is removed, the device returns to the normal mode of operation.

#### Soft-Start

The NCP9001 uses soft-start (300  $\mu s$  Typ) to limit the inrush current when the device is initially enabled. Soft-start is implemented by gradually increasing the reference voltage until it reaches the full reference voltage. During startup, a pulsed current source charges the internal soft-start capacitor to provide gradually increasing reference voltage. When the voltage across the capacitor ramps up to the nominal reference voltage, the pulsed current source will be switched off and the reference voltage will switch to the regular reference voltage.

## **Shutdown Mode**

When the EN pin has a voltage applied of less than 0.4 V, the NCP9001 will be disabled. In shutdown mode, the internal reference, oscillator and most of the control circuitries are turned off. Therefore, the typical current

consumption will be 0.3  $\mu A$  (typical value). Applying a voltage above 1.2 V to EN pin will enable the device for normal operation. The typical threshold is around 0.7 V. The device will go through soft–start to normal operation, however, the EN pin should be tied low while the input voltage on  $V_{IN}$  pin is rising up.

#### **Thermal Shutdown**

Internal Thermal Shutdown circuitry is provided to protect the integrated circuit in the event that the maximum junction temperature is exceeded. If the junction temperature exceeds 160°C, the device shuts down. In this mode switch Q1 and Q2 and the control circuits are all turned off. The device restarts in soft–start after the temperature drops below 135°C. This feature is provided to prevent catastrophic failures from accidental device overheating, and it is not intended as a substitute for proper heatsinking.

#### **Low Dropout Operation**

The NCP9001 offers a low input to output voltage difference. The NCP9001 can operate at 100% duty cycle. In this mode the PMOS (Q1) switches completely on.

The minimum input voltage to maintain regulation can be calculated as:

- V<sub>OUT</sub>: Output Voltage (Volts)

- IOUT: Max Output Current

- R<sub>DS(on)</sub>: P-Channel Switch R<sub>DS(on)</sub>

- R<sub>INDUCTOR</sub>: Inductor Resistance (DCR)

# **APPLICATION INFORMATION**

## **Output Voltage Selection**

The output voltage is programmed through an external resistor divider connected from  $V_{OUT}$  to FB then to GND. For low power consumption and noise immunity, the resistor from FB to GND (R2) should be in the [100 k-600 k] range. If R2 is 200 k given the  $V_{FB}$  is 0.6 V, the current through the divider will be 3.0  $\mu$ A.

The formula below gives the value of  $V_{OUT}$ , given the desired R1 and the R1 value:

$$V_{OUT} = V_{FB} \times (1 + \frac{R1}{R2})$$

(eq. 2)

• V<sub>OUT</sub>: Output Voltage (Volts)

• V<sub>FB</sub>: Feedback Voltage = 0.6 V

• R1: Feedback Resistor from VOUT to FB

• R2: Feedback Resistor from FB to GND

# **Input Capacitor Selection**

In PWM operating mode, the input current is pulsating with large switching noise. Using an input bypass capacitor can reduce the peak current transients drawn from the input supply source, thereby reducing switching noise significantly. The capacitance needed for the input bypass capacitor depends on the source impedance of the input supply.

The maximum RMS current occurs at 50% duty cycle with maximum output current, which is IO, max/2.

For NCP9001, a low profile, low ESR ceramic capacitor of 4.7  $\mu F$  should be used for most of the cases. For effective bypass results, the input capacitor should be placed as close as possible to the  $V_{IN}$  pin.

**Table 1. List of Input Capacitor**

| •           | •               |

|-------------|-----------------|

| Murata      | GRM188R60J475KE |

|             | GRM21BR71C475KA |

| Taiyo Yuden | JMK212BY475MG   |

| TDK         | C2012X5ROJ475KB |

|             | C1632X5ROJ475KT |

# Output L-C Filter Design Considerations

The NCP9001 is built in 1.5 MHz frequency and uses current mode architecture. The correct selection of the output filter ensures good stability and fast transient response.

Due to the nature of the buck converter, the output L–C filter must be selected to work with internal compensation. For NCP9001, the internal compensation is internally fixed and it is optimized for an output filter of L = 2.2  $\mu H$  and  $C_{OUT}$  = 10  $\mu F$ .

The corner frequency is given by:

$$f_{C} = \frac{1}{2\pi\sqrt{L \times C_{OUT}}} = \frac{1}{2\pi\sqrt{2.2\,\mu\text{H}\,\times\,10\,\mu\text{F}}} = 34~\text{kHz} \label{eq:fc}$$

(eq. 3)

The device is intended to operate with inductance values between 1.0  $\mu H$  and maximum of 4.7  $\mu H$ .

If the corner frequency is moved, it is recommended to check the loop stability depending on the output ripple voltage accepted and output current required. For lower frequency, the stability will be increased; a larger output capacitor value could be chosen without critical effect on the system. On the other hand, a smaller capacitor value increases the corner frequency and it should be critical for the system stability. Take care to check the loop stability. The phase margin is usually higher than 45°.

Table 2. L-C Filter Example

| Inductance (L) | Output Capacitor (C <sub>out</sub> ) |

|----------------|--------------------------------------|

| 1.0 μΗ         | 22 μF                                |

| 2.2 μΗ         | 10 μF                                |

| 4.7 μΗ         | 4.7 μF                               |

#### **Inductor Selection**

The inductor parameters directly related to device performances are saturation current and DC resistance and inductance value. The inductor ripple current ( $\ddot{A}I_L$ ) decreases with higher inductance:

$$\Delta I_{L} = \frac{V_{OUT}}{L \times f_{SW}} \left( 1 - \frac{V_{OUT}}{V_{IN}} \right)$$

(eq. 4)

$\Delta I_L$  peak to peak inductor ripple current

L inductor value

f<sub>SW</sub> switching frequency

The saturation current of the inductor should be rated higher than the maximum load current plus half the ripple current:

$$I_{L(MAX)} = I_{O(MAX)} + \frac{\Delta I_{L}}{2}$$

(eq. 5)

ΔI<sub>L(MAX)</sub> Maximum inductor current

ΔI<sub>O(MAX)</sub> Maximum Output current

The inductor's resistance will factor into the overall efficiency of the converter. For best performances, the DC resistance should be less than  $0.3~\Omega$  for good efficiency.

Table 3. List of Inductor

| FDK         | MIPW3226 Series  |

|-------------|------------------|

| TDK         | VLF3010AT Series |

| Taiyo Yuden | LQ CBL2012       |

| Coil craft  | DO1605-T Series  |

|             | LPO3010          |

## **Output Capacitor Selection**

Selecting the proper output capacitor is based on the desired output ripple voltage. Ceramic capacitors with low ESR values will have the lowest output ripple voltage and are strongly recommended. The output capacitor requires either an X7R or X5R dielectric.

The output ripple voltage in PWM mode is given by:

$$\Delta V_{OUT} = \Delta I_{L} \times \left(\frac{1}{4 \times f_{SW}^{-3} \times C_{OUT}} + ESR\right)$$

(eq. 6)

In PFM mode (at light load), the output voltage is regulated by pulse frequency modulation. The output voltage ripple is independent of the output capacitor value. It is set by the threshold of PFM comparator.

**Table 4. List of Output Capacitor**

| Murata      | GRM188R60J475KE    | 4.7 μF |

|-------------|--------------------|--------|

|             | GRM21BR60J106ME19L | 10 μF  |

|             | GRM188R60OJ106ME   | 10 μF  |

| Taiyo Yuden | JMK212BY475MG      | 4.7 μF |

|             | JMK212BJ106MG      | 10 μF  |

| TDK         | C2012X5ROJ475KB    | 4.7 μF |

|             | C2012X5ROJ226M     | 22 μF  |

|             | C2012X5ROJ106K     | 10 μF  |

# **Feed-Forward Capacitor Selection**

The feed-forward capacitor sets the feedback loop response and is critical to obtain good loop stability.

Given that the compensation is internally fixed, a fixed 18 pF or higher ceramic capacitor is needed. Choose a small ceramic capacitor X7R or X5R or COG dielectric.

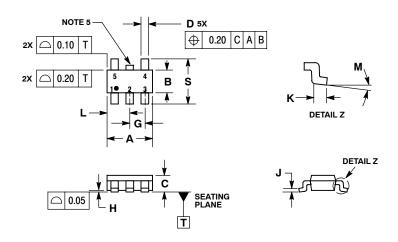

#### PACKAGE DIMENSIONS

## TSOP-5 CASE 483-02 **ISSUE F**

#### NOTES

- DIMENSIONING AND TOLERANCING PER

- ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

MAXIMUM LEAD THICKNESS INCLUDES

LEAD FINISH THICKNESS. MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL

- DIMENSIONS A AND B DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE

- OPTIONAL CONSTRUCTION: AN ADDITIONAL CONSTRUCTION: AN ADDITIONAL TRIMMED LEAD IS ALLOWED IN THIS LOCATION. TRIMMED LEAD NOT TO EXTEND MORE THAN 0.2 FROM BODY.

|     | MILLIMETERS |      |  |

|-----|-------------|------|--|

| DIM | MIN MAX     |      |  |

| Α   | 3.00        | BSC  |  |

| В   | 1.50        | BSC  |  |

| С   | 0.90        | 1.10 |  |

| D   | 0.25        | 0.50 |  |

| G   | 0.95 BSC    |      |  |

| Н   | 0.01        | 0.10 |  |

| J   | 0.10        | 0.26 |  |

| K   | 0.20        | 0.60 |  |

| L   | 1.25 1.55   |      |  |

| М   | 0° 10°      |      |  |

| S   | 2.50        | 3.00 |  |

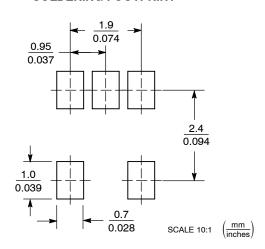

#### **SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and 👊 are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA **Phone**: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative