# **Single Wire CAN Transceiver**

The NCV7356 is a physical layer device for a single wire data link capable of operating with various Carrier Sense Multiple Access with Collision Resolution (CSMA/CR) protocols such as the Bosch Controller Area Network (CAN) version 2.0. This serial data link network is intended for use in applications where high data rate is not required and a lower data rate can achieve cost reductions in both the physical media components and in the microprocessor and/or dedicated logic devices which use the network.

The network shall be able to operate in either the normal data rate mode or a high-speed data download mode for assembly line and service data transfer operations. The high-speed mode is only intended to be operational when the bus is attached to an off-board service node. This node shall provide temporary bus electrical loads which facilitate higher speed operation. Such temporary loads should be removed when not performing download operations.

The bit rate for normal communications is typically 33 kbit/s, for high–speed transmissions like described above a typical bit rate of 83 kbit/s is recommended. The NCV7356 is designed in accordance to the Single Wire CAN Physical Layer Specification GMW3089 V2.4 and supports many additional features like undervoltage lockout, timeout for faulty blocked input signals, output blanking time in case of bus ringing and a very low sleep mode current.

#### **Features**

- Fully Compatible with J2411 Single Wire CAN Specification

- 60 μA (max) Sleep Mode Current

- Operating Voltage Range 5.0 to 27 V

- Up to 100 kbps High-Speed Transmission Mode

- Up to 40 kbps Bus Speed

- Selective BUS Wake-Up

- Logic Inputs Compatible with 3.3 V and 5 V Supply Systems

- Control Pin for External Voltage Regulators (14 Pin Package Only)

- Standby to Sleep Mode Timeout

- Low RFI Due to Output Wave Shaping

- Fully Integrated Receiver Filter

- Bus Terminals Short-Circuit and Transient Proof

- Loss of Ground Protection

- Protection Against Load Dump, Jump Start

- Thermal Overload and Short Circuit Protection

- ESD Protection of 4.0 kV on CAN Pin (2.0 kV on Any Other Pin)

- Undervoltage Lock Out

- Bus Dominant Timeout Feature

- NCV Prefix for Automotive and Other Applications Requiring Site and Change Control

- Pb-Free Packages are Available

# ON Semiconductor®

http://onsemi.com

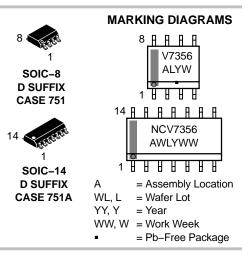

#### **PIN CONNECTIONS**

## **ORDERING INFORMATION**

| Device       | Package             | Shipping <sup>†</sup> |

|--------------|---------------------|-----------------------|

| NCV7356D1G   | SOIC-8<br>(Pb-Free) | 98 Units / Rail       |

| NCV7356D1R2G | SOIC-8<br>(Pb-Free) | 2500 Tape & Reel      |

| NCV7356D2    | SOIC-14             | 55 Units / Rail       |

| NCV7356D2R2  | SOIC-14             | 2500 Tape & Reel      |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

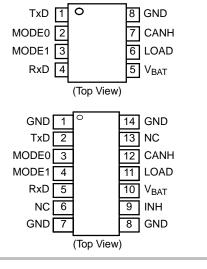

Figure 1. 8-Pin Package Block Diagram

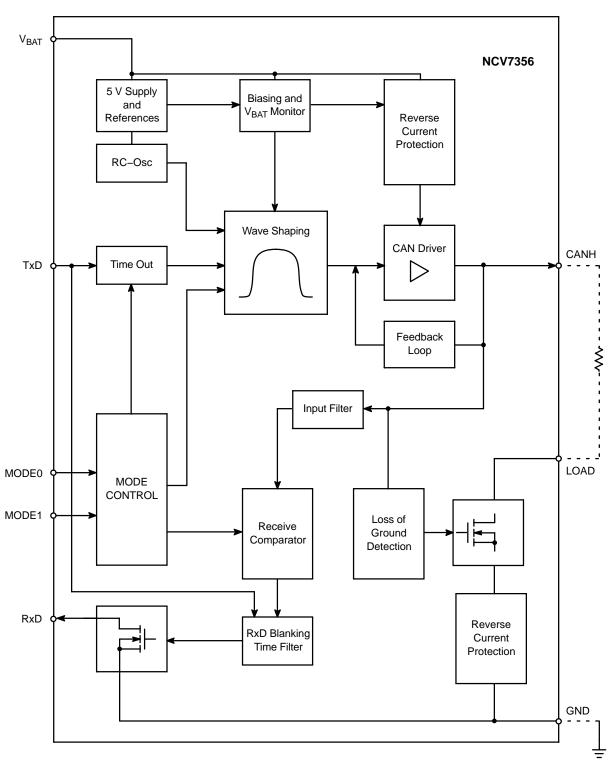

Figure 2. 14-Pin Package Block Diagram

# PACKAGE PIN DESCRIPTION

| SOIC-8 | SOIC-14     | Symbol    | Description                                                                                      |

|--------|-------------|-----------|--------------------------------------------------------------------------------------------------|

| 1      | 2           | TxD       | Transmit data from microprocessor to CAN.                                                        |

| 2      | 3           | MODE0     | Operating mode select input 0.                                                                   |

| 3      | 4           | MODE1     | Operating mode select input 1.                                                                   |

| 4      | 5           | RxD       | Receive data from CAN to microprocessor.                                                         |

| 5      | 10          | $V_{BAT}$ | Battery input voltage.                                                                           |

| 6      | 11          | LOAD      | Resistor load (loss of ground detection low side switch).                                        |

| 7      | 12          | CANH      | Single wire CAN bus pin.                                                                         |

| 8      | 1, 7, 8, 14 | GND       | Ground                                                                                           |

| _      | 6, 13       | NC        | No Connection (Note 1)                                                                           |

| -      | 9           | INH       | Control pin for external voltage regulator (high voltage high side switch) (14 pin package only) |

<sup>1.</sup> PWB terminal 13 can be connected to ground which will allow the board to be assembled with either the 8 pin package or the 14 pin package.

## **Electrical Specification**

All voltages are referenced to ground (GND). Positive currents flow into the IC. The maximum ratings given in the table below are limiting values that do not lead to a permanent damage of the device but exceeding any of these limits may do so. Long term exposure to limiting values may affect the reliability of the device.

## **MAXIMUM RATINGS**

| Rating                                  |                       | Symbol               | Condition                                                    | Min   | Max      | Unit        |

|-----------------------------------------|-----------------------|----------------------|--------------------------------------------------------------|-------|----------|-------------|

| Supply Voltage, Normal Operation        |                       | $V_{BAT}$            | -                                                            | -0.3  | 18       | V           |

| Short-Term Supply Voltage, Transient    |                       | V <sub>BAT.LD</sub>  | Load Dump; t < 500 ms                                        | _     | 40       | V<br>(peak) |

|                                         |                       |                      | Jump Start; t < 1.0 min                                      | -     | 27       | V           |

| Transient Supply Voltage                |                       | V <sub>BAT.TR1</sub> | ISO 7637/1 Pulse 1 (Note 2)                                  | -50   | -        | V           |

| Transient Supply Voltage                |                       | V <sub>BAT.TR2</sub> | ISO 7637/1 Pulses 2 (Note 2)                                 | -     | 100      | V           |

| Transient Supply Voltage                |                       | V <sub>BAT.TR3</sub> | ISO 7637/1 Pulses 3A, 3B                                     | -200  | 200      | V           |

| CANH Voltage                            |                       | V <sub>CANH</sub>    | V <sub>BAT</sub> < 27 V                                      | -20   | 40       | V           |

|                                         |                       |                      | V <sub>BAT</sub> = 0 V                                       | -40   | 40       |             |

| Transient Bus Voltage                   |                       | V <sub>CANHTR1</sub> | ISO 7637/1 Pulse 1 (Note 3)                                  | -50   | _        | V           |

| Transient Bus Voltage                   | Transient Bus Voltage |                      | ISO 7637/1 Pulses 2 (Note 3)                                 | -     | 100      | ٧           |

| Transient Bus Voltage                   |                       | V <sub>CANHTR3</sub> | ISO 7637/1 Pulses 3A, 3B (Note 3)                            | -200  | 200      | ٧           |

| DC Voltage on Pin LOAD                  |                       | $V_{LOAD}$           | Via RT > 2.0 kΩ                                              | -40   | 40       | ٧           |

| DC Voltage on Pins TxD, MODE1, Mo       | ODE0, RxD             | $V_{DC}$             | -                                                            | -0.3  | 7.0      | ٧           |

| ESD Capability of CANH                  |                       | V <sub>ESDBUS</sub>  | Human Body Model Eq. to Discharge 100 pF with 1.5 k $\Omega$ | -4000 | 4000     | V           |

| ESD Capability of Any Other Pins        |                       | V <sub>ESD</sub>     | Human Body Model<br>Eq. to Discharge 100 pF with 1.5 kΩ      | -2000 | 2000     | V           |

| Maximum Latchup Free Current at Any Pin |                       | I <sub>LATCH</sub>   | -                                                            | -500  | 500      | mA          |

| Storage Temperature                     |                       | T <sub>STG</sub>     | -                                                            | -55   | 150      | °C          |

| Junction Temperature                    |                       | TJ                   | -                                                            | -40   | 150      | °C          |

| Lead Temperature Soldering SOIC-14      |                       | T <sub>sld</sub>     | 60 s – 150 s above 183°C                                     | _     | 240 peak | °C          |

| Reflow: (SMD styles only)               | SOIC-8                |                      | 60 s – 150 s above 217°C                                     | -     | 260 peak |             |

Maximum ratings are those values beyond which device damage can occur. Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.

- 2. ISO 7637 test pulses are applied to  $V_{BAT}$  via a reverse polarity diode and >1.0  $\mu$ F blocking capacitor. 3. ISO 7637 test pulses are applied to CANH via a coupling capacitance of 1.0 nF.

- 4. ESD measured per Q100-002 (EIA/JESD22-A114-A).

# **TYPICAL THERMAL CHARACTERISTICS**

|                                                           | Test Condition, Typical Value |              |      |  |

|-----------------------------------------------------------|-------------------------------|--------------|------|--|

| Parameter                                                 | Min Pad Board                 | 1" Pad Board | Unit |  |

| SOIC-8                                                    |                               |              | 1    |  |

| Junction-to-Lead (psi-JL7, Ψ <sub>JL8</sub> ) or Pins 6-7 | 57 (Note 5)                   | 51 (Note 6)  | °C/W |  |

| Junction–to–Ambient ( $R_{\theta JA}, \theta_{JA}$ )      | 187 (Note 5)                  | 128 (Note 6) | °C/W |  |

| SOIC-14                                                   | <u> </u>                      |              | •    |  |

| Junction-to-Lead (psi-JL8, Ψ <sub>JL8</sub> )             | 30 (Note 7)                   | 30 (Note 8)  | °C/W |  |

| Junction–to–Ambient ( $R_{\theta JA}, \theta_{JA}$ )      | 122 (Note 7)                  | 84 (Note 8)  | °C/W |  |

- 5. 1 oz copper, 53 mm² coper area, 0.062" thick FR4.

- 5. 1 oz copper, 716 mm² coper area, 0.062" thick FR4.

7. 1 oz copper, 94 mm² coper area, 0.062" thick FR4.

8. 1 oz copper, 767 mm² coper area, 0.062" thick FR4.

# **ELECTRICAL CHARACTERISTICS** ( $V_{BAT} = 5.0$ to 27 V, $T_A = -40$ to +125°C, unless otherwise specified.)

| Characteristic                                 | Symbol                              | C                          | ondition                                                   | Min                       | Тур | Max                       | Unit |

|------------------------------------------------|-------------------------------------|----------------------------|------------------------------------------------------------|---------------------------|-----|---------------------------|------|

| GENERAL                                        |                                     |                            |                                                            |                           |     |                           |      |

| Undervoltage Lock Out                          | $V_{BATuv}$                         |                            | _                                                          | 3.5                       | -   | 4.8                       | V    |

| Supply Current, Recessive,                     | I <sub>BATN</sub>                   | V <sub>BAT</sub> = 18 V,   | Not High Speed Mode                                        | -                         | 5.0 | 6.0                       | mA   |

| All Active Modes                               |                                     | TxD Open                   | High Speed Mode                                            | _                         | -   | 8.0                       |      |

| Normal Mode Supply Current,<br>Dominant        | I <sub>BATN</sub> (Note 9)          |                            | IODE0 = MODE1 = H,<br>, $R_{load}$ = 200 $Ω$               | _                         | 30  | 35                        | mA   |

| High-Speed Mode Supply Current,<br>Dominant    | I <sub>BATN</sub> (Note 9)          |                            | DDE0 = H, MODE1 = L,<br>-, $R_{load}$ = 75 $\Omega$        | -                         | 70  | 75                        | mA   |

| Wake-Up Mode Supply Current,<br>Dominant       | I <sub>BATW</sub> (Note 9)          |                            | DDE0 = L, MODE1 = H,<br>, $R_{load}$ = 200 $\Omega$        | -                         | 60  | 75                        | mA   |

| Sleep Mode Supply Current                      | I <sub>BATS</sub>                   |                            | TxD, RxD, MODE0,<br>DE1 Open                               | -                         | 30  | 60                        | μΑ   |

| Thermal Shutdown (Note 9)                      | T <sub>SD</sub>                     |                            | _                                                          | 155                       | -   | 180                       | °C   |

| Thermal Recovery (Note 9)                      | T <sub>REC</sub>                    |                            | _                                                          | 126                       | -   | 150                       | °C   |

| CANH                                           |                                     |                            |                                                            |                           |     |                           |      |

| Bus Output Voltage                             | V <sub>oh</sub>                     |                            | Ω, Normal Mode<br>< V <sub>BAT</sub> < 27 V                | 4.4                       | -   | 5.1                       | V    |

| Bus Output Voltage<br>Low Battery              | V <sub>oh</sub>                     |                            | rmal High–Speed Mode<br>< V <sub>BAT</sub> < 6.0 V         | 3.4                       | -   | 5.1                       | V    |

| Bus Output Voltage<br>High-Speed Mode          | V <sub>oh</sub>                     |                            | High–Speed Mode<br>< V <sub>BAT</sub> < 16 V               | 4.2                       | -   | 5.1                       | V    |

| Fixed Wake-Up<br>Output High Voltage           | V <sub>ohWuFix</sub>                |                            | Mode, R <sub>L</sub> > 200 Ω,<br>< V <sub>BAT</sub> < 27 V | 9.9                       | -   | 12.5                      | V    |

| Offset Wake-Up<br>Output High Voltage          | V <sub>ohWuOffset</sub>             |                            | Mode, R <sub>L</sub> > 200 Ω,<br>V <sub>BAT</sub> < 11.4 V | V <sub>BAT</sub> –1.5     | -   | V <sub>BAT</sub>          | V    |

| Recessive State<br>Output Voltage              | V <sub>ol</sub>                     |                            | tate or Sleep Mode,<br>$_{ad}$ = 6.5 k $\Omega$            | -0.20                     | -   | 0.20                      | V    |

| Bus Short Circuit Current                      | -I <sub>CAN_SHORT</sub>             | V <sub>CANH</sub> = 0 V, V | <sub>BAT</sub> = 27 V, TxD = 0 V                           | 50                        | -   | 350                       | mA   |

| Bus Leakage Current<br>During Loss of Ground   | I <sub>LKN_CAN</sub><br>(Note 10)   | Loss of Gro                | ound, V <sub>CANH</sub> = 0 V                              | -50                       | -   | 10                        | μΑ   |

| Bus Leakage Current, Bus Positive              | I <sub>LKP_CAN</sub>                | Т                          | xD High                                                    | -10                       | -   | 10                        | μΑ   |

| Bus Input Threshold                            | V <sub>ih</sub>                     | ·                          | gh–Speed Mode, $V_{BAT} \leq 27 \text{ V}$                 | 2.0                       | 2.1 | 2.2                       | V    |

| Bus Input Threshold Low Battery                | V <sub>ihlb</sub>                   | Normal, V <sub>B</sub>     | AT = 5.0 V to 6.0 V                                        | 1.6                       | 1.7 | 2.2                       | V    |

| Fixed Wake-Up<br>Input High Voltage Threshold  | V <sub>ihWuFix</sub><br>(Note 9)    | Sleep Mod                  | de, V <sub>BAT</sub> > 10.9 V                              | 6.6                       | -   | 7.9                       | V    |

| Offset Wake-Up<br>Input High Voltage Threshold | V <sub>ihWuOffset</sub><br>(Note 9) | Sle                        | eep Mode                                                   | V <sub>BAT</sub> -4.3     | -   | V <sub>BAT</sub> -3.25    | V    |

| LOAD                                           |                                     |                            |                                                            |                           |     |                           | _    |

| Voltage on Switched Ground Pin                 | V <sub>LOAD_1mA</sub>               | I <sub>LOA</sub>           | <sub>AD</sub> = 1.0 mA                                     | -                         | -   | 0.1                       | V    |

| Voltage on Switched Ground Pin                 | $V_{LOAD}$                          | I <sub>LOAD</sub> = 5.0 mA |                                                            | -                         | -   | 0.5                       | V    |

| Voltage on Switched Ground Pin                 | V <sub>LOAD_LOB</sub>               | I <sub>LOAD</sub> = 7.     | 0 mA, V <sub>BAT</sub> = 0 V                               | -                         | -   | 1.0                       | V    |

| Load Resistance During Loss of Battery         | R <sub>LOAD_LOB</sub>               | \                          | / <sub>BAT</sub> = 0                                       | R <sub>LOAD</sub><br>-10% | _   | R <sub>LOAD</sub><br>+35% | Ω    |

Thresholds not tested in production, guaranteed by design.

Leakage current in case of loss of ground is the summary of both currents I<sub>LKN\_CAN</sub> and I<sub>LKN\_LOAD</sub>.

# $\textbf{ELECTRICAL CHARACTERISTICS (continued)} \ (V_{BAT} = 5.0 \ \text{to} \ 27 \ \text{V}, \ T_{A} = -40 \ \text{to} \ +125 ^{\circ}\text{C}, \ \text{unless otherwise specified.})$

| Characteristic                | ristic Symbol Condition |                                                           | Min                   | Тур                   | Max       | Unit |

|-------------------------------|-------------------------|-----------------------------------------------------------|-----------------------|-----------------------|-----------|------|

| TXD, MODE0, MODE1             |                         |                                                           |                       |                       |           |      |

| High Level Input Voltage      | V <sub>ih</sub>         | 6.0 < V <sub>BAT</sub> < 27 V                             | 2.0                   | -                     | -         | V    |

| Low Level Input Voltage       | V <sub>il</sub>         | 6.0 < V <sub>BAT</sub> < 27 V                             | -                     | -                     | 0.8       | V    |

| TxD Pullup Current            | -l <sub>IL_TXD</sub>    | TxD = L, MODE0 and 1 = H<br>5.0 < V <sub>BAT</sub> < 27 V | 10                    | -                     | 50        | μА   |

| MODE0 and 1 Pulldown Resistor | R <sub>MODE_pd</sub>    |                                                           | 10                    | -                     | 50        | kΩ   |

| RXD                           |                         |                                                           |                       |                       |           |      |

| Low Level Output Voltage      | V <sub>ol_rxd</sub>     | $I_{RxD} = 2.0 \text{ mA}$                                | _                     | -                     | 0.4       | V    |

| High Level Output Leakage     | I <sub>ih_rxd</sub>     | V <sub>RxD</sub> = 5.0 V                                  | -10                   | -                     | 10        | μΑ   |

| RxD Output Current            | Irxd                    | V <sub>RxD</sub> = 5.0 V                                  | -                     | -                     | 70        | mA   |

| INH (14 Pin Package Only)     |                         |                                                           |                       |                       |           |      |

| High Level Output Voltage     | V <sub>oh_INH</sub>     | I <sub>INH</sub> = -180 μA                                | V <sub>BAT</sub> -0.8 | V <sub>BAT</sub> -0.5 | $V_{BAT}$ | V    |

| Leakage Current               | I <sub>INH_Ik</sub>     | MODE0 = MODE1 = L, INH = 0 V                              | -5.0                  | -                     | 5.0       | μА   |

#### TIMING MEASUREMENT LOAD CONDITIONS

| Normal and High V  | High-Speed Mode   |                                    |

|--------------------|-------------------|------------------------------------|

| min load / min tau | 3.3 kohm / 540 pF | Additional 140 ohm tool resistance |

| min load / max tau | 3.3 kohm / 1.2 nF | to ground in parallel              |

| max load / min tau | 200 ohm / 5.0 nF  | Additional 120 ohm tool resistance |

| max load / max tau | 200 ohm / 20 nF   | to ground in parallel              |

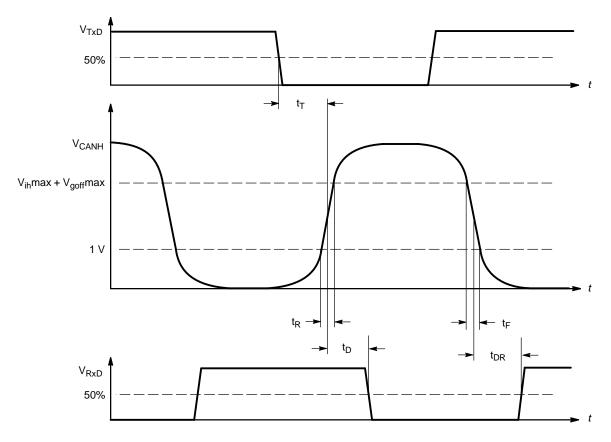

# **ELECTRICAL CHARACTERISTICS** (5.0 V $\leq$ V<sub>BAT</sub> $\leq$ 27 V, $-40^{\circ}$ C $\leq$ T<sub>A</sub> $\leq$ 125°C, unless otherwise specified.) **AC CHARACTERISTICS** (See Figures 3, 4, and 5)

| Characteristic Sym                                                                 |                                        | Condition                                                   | Min          | Тур    | Max        | Unit |

|------------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------|--------------|--------|------------|------|

| Transmit Delay in Normal and Wake-Up<br>Mode, Bus Rising Edge (Note 11)            | t <sub>Tr</sub>                        | Min and Max Loads per Timing<br>Measurement Load Conditions | 2.0          | _      | 6.3        | μs   |

| Transmit Delay in Wake-Up Mode to V <sub>ihWU</sub> ,<br>Bus Rising Edge (Note 12) | t <sub>TWUr</sub>                      | Min and Max Loads per Timing<br>Measurement Load Conditions | 2.0          | -      | 18         | μs   |

| Transmit Delay in Normal Mode,<br>Bus Falling Edge (Note 13)                       | t <sub>Tf</sub>                        | Min and Max Loads per Timing<br>Measurement Load Conditions | 1.8          | _      | 10         | μS   |

| Transmit Delay in Wake-Up Mode,<br>Bus Falling Edge (Note 13)                      | t <sub>TWU1f</sub>                     | Min and Max Loads per Timing<br>Measurement Load Conditions | 3.0          | -      | 13.7       | μS   |

| Transmit Delay in High-Speed Mode,<br>Bus Rising Edge (Note 14)                    | t <sub>THSr</sub>                      | Min and Max Loads per Timing<br>Measurement Load Conditions | 0.1          | _      | 1.5        | μS   |

| Transmit Delay in High-Speed Mode,<br>Bus Falling Edge (Note 15)                   | t <sub>THSf</sub>                      | Min and Max Loads per Timing<br>Measurement Load Conditions | 0.04         | _      | 3.0        | μS   |

| Receive Delay, All Active Modes (Note 16)                                          | t <sub>DR</sub>                        | CANH High to Low Transition                                 | 0.3          | -      | 1.0        | μS   |

| Receive Delay, All Active Modes (Note 16)                                          | t <sub>RD</sub>                        | CANH Low to High Transition                                 | 0.3          | -      | 1.0        | μS   |

| Input Minimum Pulse Length,<br>All Active Modes (Note 16)                          | t <sub>mpDR</sub><br>t <sub>mpRD</sub> | CANH High to Low Transition<br>CANH Low to High Transition  | 0.15<br>0.15 | -<br>- | 1.0<br>1.0 | μs   |

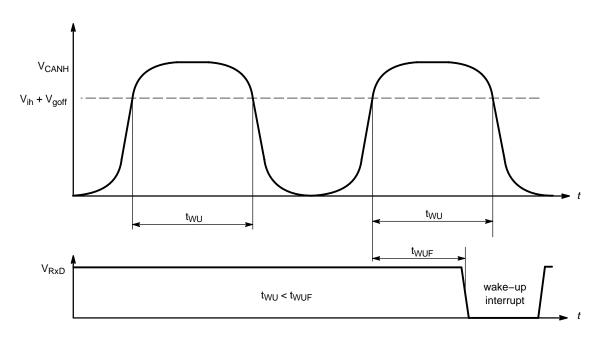

| Wake-Up Filter Time Delay                                                          | t <sub>WUF</sub>                       | See Figure 4                                                | 10           | _      | 70         | μS   |

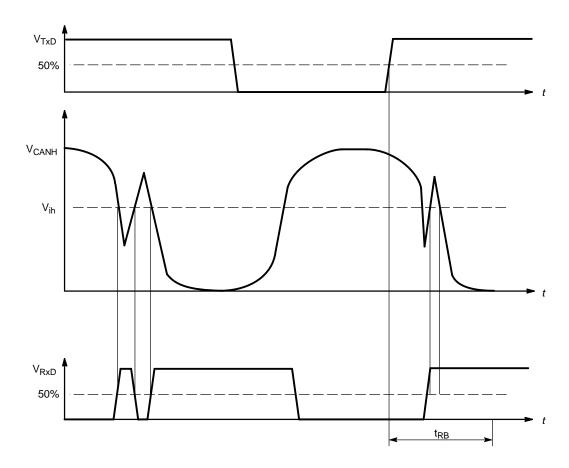

| Receive Blanking Time After TxD L-H Transition                                     | t <sub>rb</sub>                        | See Figure 5                                                | 0.5          | -      | 6.0        | μs   |

| TxD Timeout Reaction Time                                                          | t <sub>tout</sub>                      | Normal and High-Speed Mode                                  | 1            | 17     | _          | ms   |

| TxD Timeout Reaction Time                                                          | t <sub>toutwu</sub>                    | Wake-Up Mode                                                | -            | 17     | _          | ms   |

| Delay from Normal to High-Speed and<br>High Voltage Wake-Up Mode                   | t <sub>dnhs</sub>                      | -                                                           | -            | -      | 30         | ms   |

| Delay from High-Speed and High Voltage<br>Wake-Up to Normal Mode                   | t <sub>dhsn</sub>                      | -                                                           | -            | _      | 30         | ms   |

| Delay from Normal to Standby Mode                                                  | t <sub>dsby</sub>                      | V <sub>BAT</sub> = 6.0 V to 27 V                            | 1            | -      | 500        | μS   |

| Delay from Sleep to Normal Mode                                                    | t <sub>dsnwu</sub>                     | V <sub>BAT</sub> = 6.0 V to 27 V                            | _            | -      | 50         | ms   |

| Delay from Standby to Sleep Mode (Note 17)                                         | t <sub>dsleep</sub>                    | V <sub>BAT</sub> = 6.0 V to 27 V                            | 100          | 250    | 500        | ms   |

<sup>11.</sup> The maximum signal delay time for a bus rising edge is measured from Vcmos\_il on the TxD input pin to the VihMax + Vgoff max level on CANH at maximum network time constant, minimum signal delay time for a bus rising edge is measured from Vcmos\_ih on the TxD input pin to 1 V on CANH at minimum network time constant. These definitions are valid in both normal and High Voltage Wake–Up (HVWU) mode.

<sup>12.</sup> The maximum signal delay time for a bus rising edge in HVWU mode is measured from Vcmos\_ii on the TxD input pin to the VihWuMax + Vgoff max level on CANH at maximum network time constant, minimum signal delay time for a bus rising edge is measured from Vcmos\_ih on the TxD input pin to 1 V on CANH at minimum network time constant.

<sup>13.</sup> Maximum signal delay time for a bus falling edge is measured from V<sub>cmos\_ih</sub> on the TxD input pin to 1 V on CANH at maximum network time constant, minimum signal delay time for a bus falling edge is measured from V<sub>cmos\_ih</sub> on the TxD input pin to the V<sub>ihMax</sub> + V<sub>goff</sub> max level on CANH. These definitions are valid in both normal and HVWU mode.

<sup>14.</sup> The signal delay time in high–speed mode for a bus rising edge is measured from Vcmos\_il on the TxD input pin to the VihMax + Vgoff max level on CANH at maximum high–speed network time constant.

<sup>15.</sup> The signal delay time in high-speed mode for a bus falling edge is measured from Vcmos\_ih on the TxD input pin to 1 V on CANH at maximum high-speed network time constant.

<sup>16.</sup> Receive delay time is measured from the rising / falling edge crossing of the nominal Vih value on CANH to the falling (Vcmos\_il\_max) / rising (Vcmos\_ih\_min) edge of RxD. This parameter is tested by applying a square wave signal to CANH. The minimum slew rate for the bus rising and falling edges is 50 V/µs. The low level on bus is always 0 V. For normal mode and high–speed mode testing the high level on bus is 4 V. For HVWU mode testing the high level on bus is V<sub>RAT</sub> – 2 V.

<sup>17.</sup> Tested on 14 Pin package only.

## **BUS LOADING REQUIREMENTS**

| Characteristic                                | Symbol                  | Min  | Тур                    | Max   | Unit |

|-----------------------------------------------|-------------------------|------|------------------------|-------|------|

| Number of System Nodes                        | _                       | 2    | -                      | 32    | -    |

| Network Distance Between Any Two ECU Nodes    | Bus Length              | -    | _                      | 60    | m    |

| Node Series Inductor Resistance (If required) | R <sub>ind</sub>        | -    | _                      | 3.5   | Ω    |

| Ground Offset Voltage                         | $V_{goff}$              | -    | -                      | 1.5   | V    |

| Ground Offset Voltage, Low Battery            | V <sub>gofflowbat</sub> | -    | 0.1 x V <sub>BAT</sub> | 0.7   | V    |

| Device Capacitance (Unit Load)                | C <sub>ul</sub>         | 135  | 150                    | 300   | pF   |

| Network Total Capacitance                     | C <sub>tl</sub>         | 396  | -                      | 19000 | pF   |

| Device Resistance (Unit Load)                 | R <sub>ul</sub>         | 6435 | 6490                   | 6565  | Ω    |

| Device Resistance (Min Load)                  | R <sub>min</sub>        | 2000 | -                      | -     | Ω    |

| Network Total Resistance                      | R <sub>tl</sub>         | 200  | -                      | 4596  | Ω    |

| Network Time Constant (Note 18)               | τ                       | 1.0  | -                      | 4.0   | μs   |

| Network Time Constant in High-Speed Mode      | τ                       | -    | -                      | 1.5   | μs   |

| High-Speed Mode Network Resistance to GND     | R <sub>load</sub>       | 75   | -                      | 135   | Ω    |

<sup>18.</sup> The network time constant incorporates the bus wiring capacitance. The minimum value is selected to limit radiated emission. The maximum value is selected to ensure proper communication modes. Not all combinations of R and C are possible.

# **TIMING DIAGRAMS**

Figure 3. Input/Output Timing

# TIMING DIAGRAMS

Figure 4. Wake-Up Filter Time Delay

Figure 5. Receive Blanking Time

#### **FUNCTIONAL DESCRIPTION**

## **TxD Input Pin**

TxD Polarity

- TxD = logic 1 (or floating) on this pin produces an undriven or recessive bus state (low bus voltage)

- TxD = logic 0 on this pin produces either a bus normal or a bus high voltage dominant state depending on the transceiver mode state (high bus voltage)

If the TxD pin is driven to a logic low state while the sleep mode (Mode 0=0 and Mode 1=0) is activated, the transceiver can not drive the CANH pin to the dominant state.

The transceiver provides an internal pullup current on the TxD pin which will cause the transmitter to default to the bus recessive state when TxD is not driven.

TxD input signals are standard CMOS logic levels.

#### **Timeout Feature**

In case of a faulty blocked dominant TxD input signal, the CANH output is switched off automatically after the specified TxD timeout reaction time to prevent a dominant bus.

The transmission is continued by next TxD L to H transition without delay.

#### **MODE0 and MODE1 Pins**

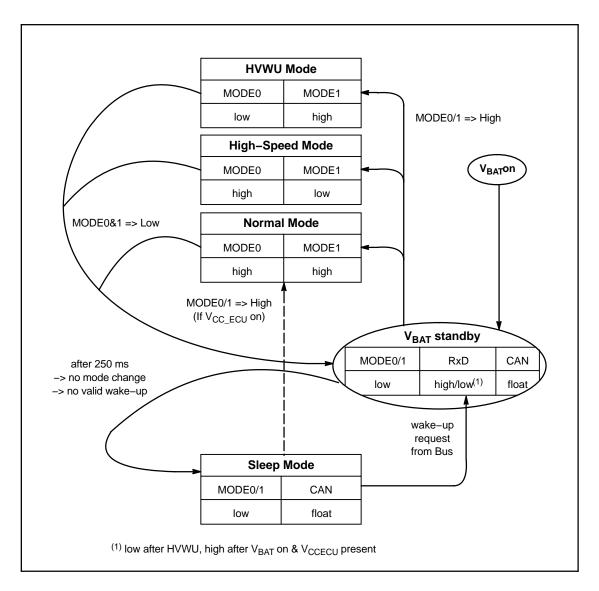

The transceiver provides a weak internal pulldown current on each of these pins which causes the transceiver to default to sleep mode when they are not driven. The mode input signals are standard CMOS logic level for 3.3 V and 5 V supply voltages.

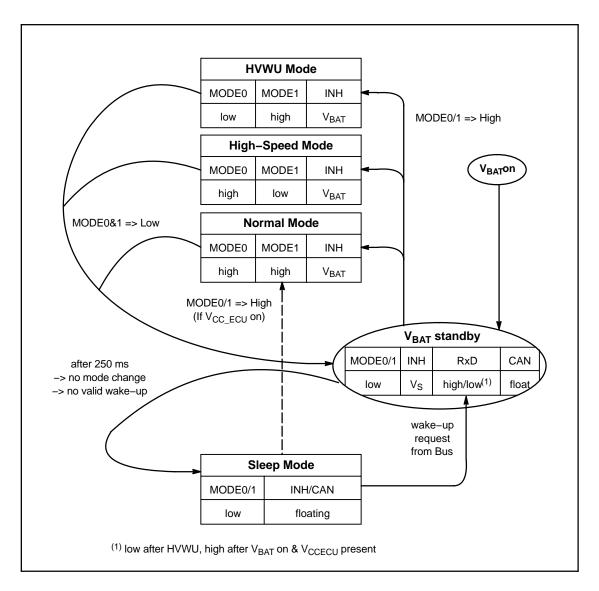

| MODE0 | MODE1 | Mode                 |

|-------|-------|----------------------|

| L     | L     | Sleep Mode           |

| Н     | L     | High-Speed Mode      |

| L     | Н     | High Voltage Wake-Up |

| Н     | Н     | Normal Mode          |

## Sleep Mode

Transceiver is in low power state, waiting for wake-up via high voltage signal or by mode pins change to any state other than 0,0. In this state, the CANH pin is not in the dominant state regardless of the state of the TxD pin.

### **High-Speed Mode**

This mode allows high–speed download with bit rates up to 100 Kbit/s. The output wave shapingaping circuit is disabled in this mode. Bus transmitter drive circuits for those nodes which are required to communicate in high–speed mode are able to drive reduced bus resistance in this mode.

# High Voltage Wake-Up Mode

This bus includes a selective node awake capability, which allows normal communication to take place among some nodes while leaving the other nodes in an undisturbed sleep state. This is accomplished by controlling the signal voltages such that all nodes must wake—up when they receive a higher voltage message signal waveform. The communication system communicates to the nodes information as to which nodes are to stay operational (awake) and which nodes are to put themselves into a non communicating low power "sleep" state. Communication at the lower, normal voltage levels shall not disturb the sleeping nodes.

#### **Normal Mode**

Transmission bit rate in normal communication is 33 Kbits/s. In normal transmission mode the NCV7356 supports controlled waveform rise and overshoot times. Waveform trailing edge control is required to assure that high frequency components are minimized at the beginning of the downward voltage slope. The remaining fall time occurs after the bus is inactive with drivers off and is determined by the RC time constant of the total bus load.

# **RxD Output Pin**

Logic data as sensed on the single wire CAN bus.

RxD Polarity

- RxD = logic 1 on this pin indicates a bus recessive state (low bus voltage)

- RxD = logic 0 on this pin indicates a bus normal or high voltage bus dominant state

## **RxD** in Sleep Mode

RxD does not pass signals to the microprocessor while in sleep mode until a valid wake-up bus voltage level is received or the MODE0 and MODE 1 pins are not 0, 0 respectively. When the valid wake-up bus voltage signal awakens the transceiver, the RxD pin signals an interrupt (logic 0). If there is no mode change within 250 ms (typ), the transceiver re-enters the sleep mode.

When not in sleep mode all valid bus signals will be sent out on the RxD pin.

RxD will be placed in the undriven or off state when in sleep mode.

RxD Typical Load

Resistance:  $2.7 \text{ k}\Omega$ Capacitance: < 25 pF

#### **Bus LOAD Pin**

Resistor ground connection with internal open-on-lossof-ground protection

When the ECU experiences a loss of ground condition, this pin is switched to a high impedance state.

The ground connection through this pin is not interrupted in any transceiver operating mode including the sleep mode. The ground connection only is interrupted when there is a valid loss of ground condition.

This pin provides the bus load resistor with a path to ground which contributes less than 0.1 V to the bus offset voltage when sinking the maximum current through one unit load resistor. This path exists in all operating modes, including the sleep mode.

The transceiver's maximum bus leakage current contribution to  $V_{ol}$  from the LOAD pin when in a loss of ground state is 50  $\mu A$  over all operating temperatures and  $3.5 < V_{BAT} < 27$  V.

## **VBAT Input Pin**

# Vehicle Battery Voltage

The transceiver is fully operational as described in the Electrical Characteristics Table over the range 6.0 V < V<sub>BAT</sub> < 18 V as measured between the GND pin and the V<sub>BAT</sub> pin.

For  $5.0~V < V_{Bat} < 6.0~V$ , the bus operates in normal mode with reduced dominant output voltage and reduced receiver input voltage. High voltage wake-up is not possible (dominant output voltage is the same as in normal or high-speed mode).

The transceiver operates in normal mode when  $18~V < V_{Bat} < 27~V$  at  $85^{\circ}C$  for one minute.

For  $0 < V_{BAT} < 4.0 \text{ V}$ , the bus is passive (not driven dominant) and RxD is undriven (high), regardless of the state of the TxD pin (undervoltage lockout).

#### **CAN BUS**

Input/Output Pin

Wave Shaping in Normal and High Voltage Wake-Up Mode

Wave shaping is incorporated into the transmitter to minimize EMI radiated emissions. An important contributor to emissions is the rise and fall times during output transitions at the "corners" of the voltage waveform. The resultant waveform is one half of a sin wave of frequency 50–65 kHz at the rising waveform edge and one quarter of this sin wave at falling or trailing edge.

## Wave Shaping in High-Speed Mode

Wave shaping control of the rising and falling waveform edges are disabled during high-speed mode. EMI emissions requirements are waived during this mode. The waveform rise time in this mode is less than 1.0 µs.

# Short Circuits

If the CAN BUS pin is shorted to ground for any duration of time, the current is limited as specified in the Electrical Characteristics Table until an overtemperature shutdown circuit disables the output high side drive source transistor preventing damage to the IC.

#### Loss of Ground

In case of a valid loss of ground condition, the LOAD pin is switched into high impedance state. The CANH transmission is continued until the undervoltage lock out voltage threshold is detected.

#### Loss of Battery

In case of loss of battery ( $V_{BAT}=0$  or open) the transceiver does not disturb bus communication. The maximum reverse current into the power supply system ( $V_{BAT}$ ) doesn't exceed 500  $\mu A$ .

# INH Pin (14 pin package only)

The INH pin is a high–voltage highside switch used to control the ECU's regulated microcontroller power supply. After power–on, the transceiver automatically enters an intermediate standby mode, the INH output will go high (up to  $V_{BAT}$ ) turning on the external voltage regulator. The external regulator provides power to the ECU. If there is no mode change within 250 ms (typ), the transceiver re–enters the sleep mode and the INH output goes to logic 0 (floating).

When the transceiver has detected a valid wake-up condition (bus HVWU traffic which exceeds the wake-up filter time delay) the INH output will become high (up to  $V_{BAT}$ ) again and the same procedure starts as described after power-on. In case of a mode change into any active mode, the sleep timer is stopped and INH stays high (up to  $V_{BAT}$ ). If the transceiver enters the sleep mode, INH goes to logic 0 (floating) after 250 ms (typ) when no wake-up signal is present.

Figure 6. State Diagram, 8 Pin Package

Figure 7. State Diagram, 14 Pin Package

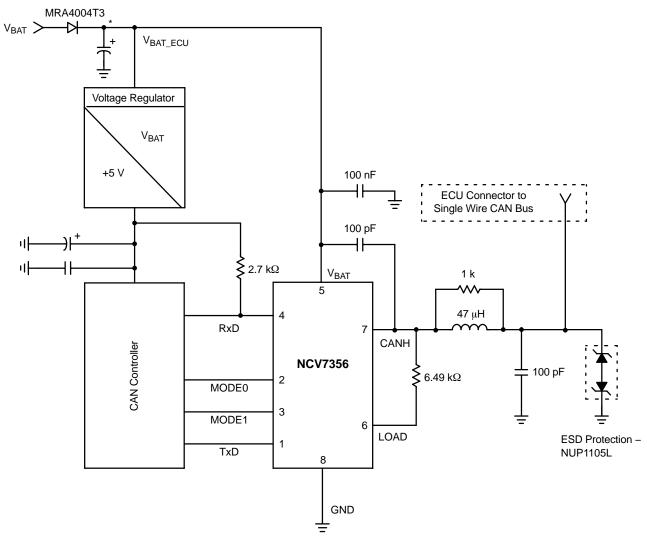

\*Recommended capacitance at  $V_{\mbox{\footnotesize{BAT\_ECU}}}\!>1.0~\mu\mbox{F}$  (immunity to ISO7637/1 test pulses)

Figure 8. Application Circuitry, 8 Pin Package

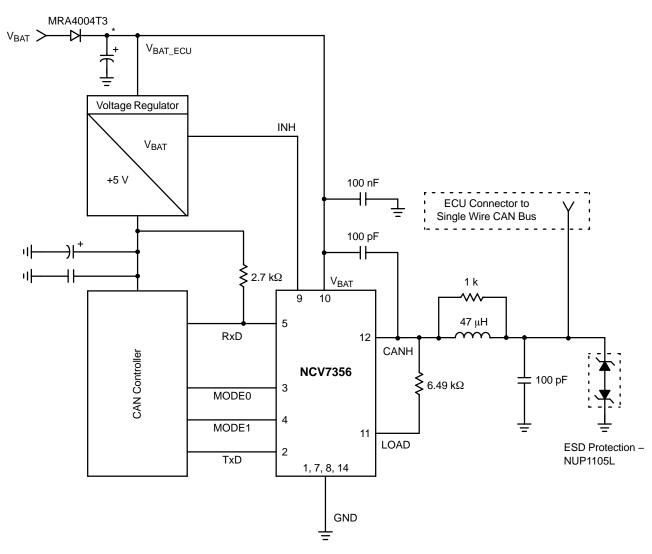

\*Recommended capacitance at  $V_{\mbox{\footnotesize{BAT\_ECU}}}\!>1.0~\mu\mbox{F}$  (immunity to ISO7637/1 test pulses)

Figure 9. Application Circuitry, 14 Pin Package

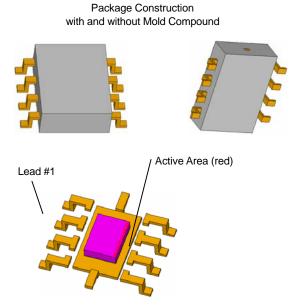

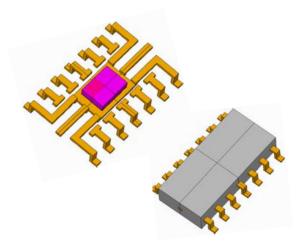

## **SOIC-8 Thermal Information**

|                                                           | Test Condition             | , Typical Value           |      |

|-----------------------------------------------------------|----------------------------|---------------------------|------|

| Parameter                                                 | Min Pad Board<br>(Note 19) | 1" Pad Board<br>(Note 20) | Unit |

| Junction-to-Lead (psi-JL7, Ψ <sub>JL8</sub> ) or Pins 6-7 | 57                         | 51                        | °C/W |

| Junction–to–Ambient ( $R_{\theta JA}, \theta_{JA}$ )      | 187                        | 128                       | °C/W |

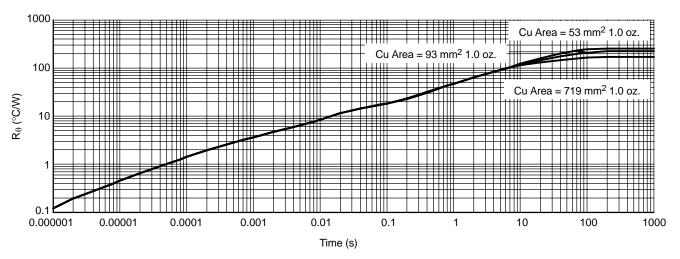

- 19.1 oz copper, 53 mm² coper area, 0.062" thick FR4.

- 20.1 oz copper, 716 mm² coper area, 0.062" thick FR4.

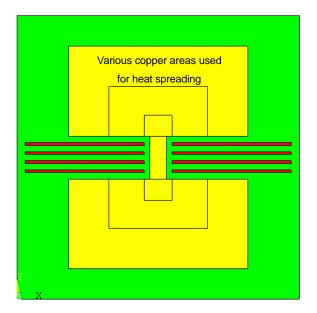

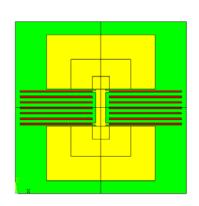

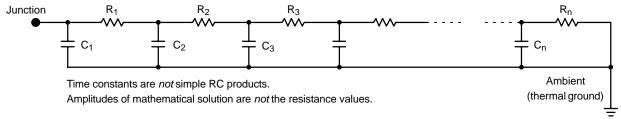

Figure 10. Internal constrution of the package simulation.

Figure 11. Min pad is shown as the red traces.

1" pad includes the yellow area. Internal construction is shown for later reference.

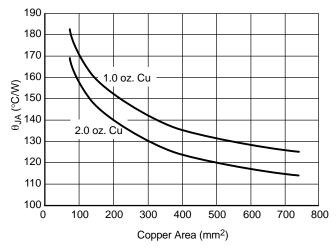

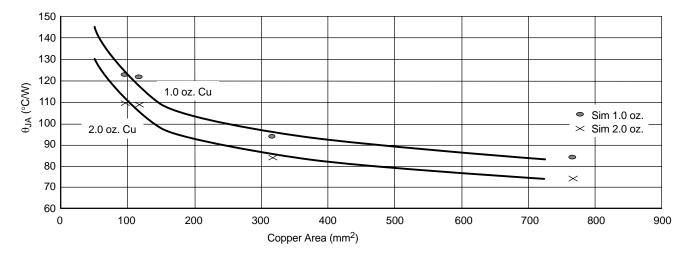

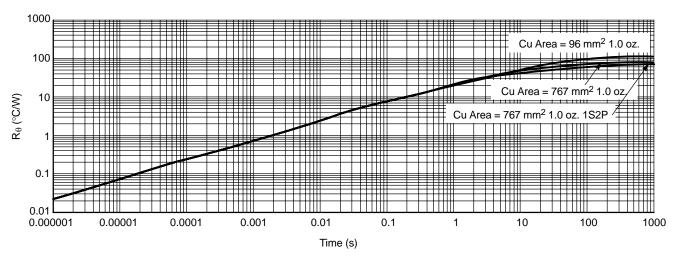

Figure 12. SOIC–8,  $\theta_{JA}$  as a Function of the Pad Copper Area Including Traces, Board Material

Table 1. SOIC-8 Thermal RC Network Models\*

| 53 mm <sup>2</sup> | 719 mm <sup>2</sup> | Copper Area | 53 mm2         | 719 mm <sup>2</sup> | Copper Area |  |

|--------------------|---------------------|-------------|----------------|---------------------|-------------|--|

| Cauer I            | Network             |             | Foster Network |                     |             |  |

| C's                | C's                 | Units       | Tau            | Tau                 | Units       |  |

| 5.86E-06           | 5.86E-06            | W-s/C       | 1.00E-06       | 1.00E-06            | sec         |  |

| 2.29E-05           | 2.29E-05            | W-s/C       | 1.00E-05       | 1.00E-05            | sec         |  |

| 6.98E-05           | 6.97E-05            | W-s/C       | 1.00E-04       | 1.00E-04            | sec         |  |

| 3.68E-04           | 3.68E-04            | W-s/C       | 1.99E-04       | 1.99E-04            | sec         |  |

| 3.75E-04           | 3.74E-04            | W-s/C       | 1.00E-03       | 1.00E-03            | sec         |  |

| 1.57E-03           | 1.56E-03            | W-s/C       | 1.64E-02       | 1.64E-02            | sec         |  |

| 2.05E-02           | 2.24E-02            | W-s/C       | 5.60E-01       | 5.60E-01            | sec         |  |

| 9.13E-02           | 7.35E-02            | W-s/C       | 4.50E+00       | 4.50E+00            | sec         |  |

| 2.64E-01           | 1.22E+00            | W-s/C       | 7.61E+01       | 7.61E+01            | sec         |  |

| 1.66E+01           | 9.74E+00            | W-s/C       | 3.00E+01       | 3.00E+01            | sec         |  |

| R's                | R's                 |             | R's            | R's                 |             |  |

| 0.22               | 0.22                | C/W         | 1.30E-01       | 1.30E-01            | C/W         |  |

| 0.50               | 0.50                | C/W         | 2.82E-01       | 2.82E-01            | C/W         |  |

| 1.30               | 1.30                | C/W         | 8.91E-01       | 8.91E-01            | C/W         |  |

| 1.80               | 1.79                | C/W         | 0.17           | 0.18                | C/W         |  |

| 0.95               | 0.96                | C/W         | 1.88           | 1.88                | C/W         |  |

| 7.43               | 7.37                | C/W         | 7.15           | 7.24                | C/W         |  |

| 31.19              | 31.59               | C/W         | 19.80          | 16.27               | C/W         |  |

| 59.97              | 47.70               | C/W         | 30.1           | 54.7                | C/W         |  |

| 75.79              | 28.63               | C/W         | 14.1           | 23.3                | C/W         |  |

| 4.41               | 6.15                | C/W         | 109.0          | 21.3                | C/W         |  |

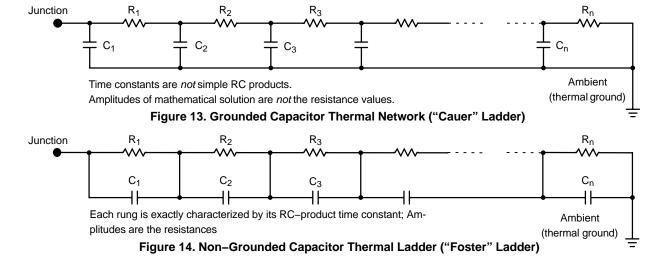

<sup>\*</sup>Bold face items in the Cauer network above, represent the package without the external thermal system. The Bold face items in the Foster network are computed by the square root of time constant R(t) = 130 \* sqrt(time(sec)). The constant is derived based on the active area of the device with silicon and epoxy at the interface of the heat generation.

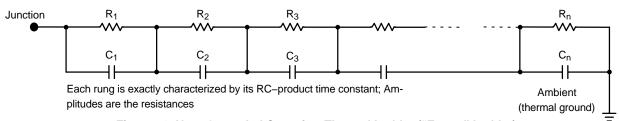

The Cauer networks generally have physical significance and may be divided between nodes to separate thermal behavior due to one portion of the network from another. The Foster networks, though when sorted by time constant (as above) bear a rough correlation with the Cauer networks, are really only convenient mathematical models. Both Foster and Cauer networks can be easily implemented

using circuit simulating tools, whereas Foster networks may be more easily implemented using mathematical tools (for instance, in a spreadsheet program), according to the following formula:

$$R(t) = \sum_{i=1}^{n} R_i (1-e^{-t/tau_i})$$

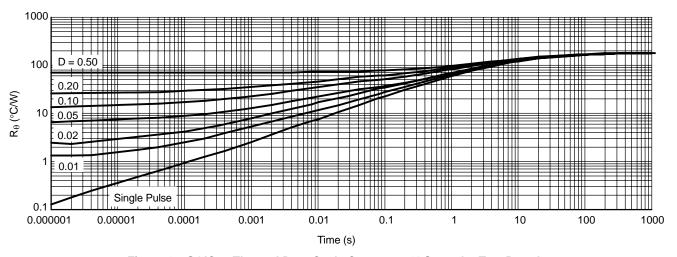

Figure 15. SOIC-8 Single Pulse Heating Curve

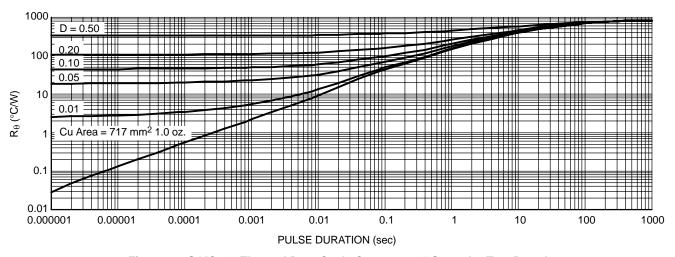

Figure 16. SOIC-8 Thermal Duty Cycle Curves on 1" Spreader Test Board

**SOIC-14 Thermal Information**

|                                                      | Test Condition             |                           |      |

|------------------------------------------------------|----------------------------|---------------------------|------|

| Parameter                                            | Min Pad Board<br>(Note 21) | 1" Pad Board<br>(Note 22) | Unit |

| Junction–to–Lead (psi–JL8, Ψ <sub>JL8</sub> )        | 30                         | 30                        | °C/W |

| Junction–to–Ambient ( $R_{\theta JA}, \theta_{JA}$ ) | 122                        | 84                        | °C/W |

<sup>21.1</sup> oz copper, 94 mm² coper area, 0.062" thick FR4.

<sup>22.1</sup> oz copper, 767 mm² coper area, 0.062" thick FR4.

Figure 18. Min pad is shown as the red traces.

1 inch pad includes the yellow area. Pin 1, 7, 8

and 14 are connected to flag internally to the

package and externally to the heat spreading area.

Figure 17. Internal construction of the package simulation.

Figure 19. SOIC–14,  $\theta_{JA}$  as a Function of the Pad Copper Area Including Traces, Board Material

Table 2. SOIC-14 Thermal RC Network Models\*

| 96 mm <sup>2</sup> | 767 mm <sup>2</sup> | Copper Area | 96 mm <sup>2</sup> | 767 mm <sup>2</sup> | Copper Area |

|--------------------|---------------------|-------------|--------------------|---------------------|-------------|

| Cauer I            | Network             |             | Foster I           | Network             |             |

| C's                | C's                 | Units       | Tau                | Tau                 | Units       |

| 3.12E-05           | 3.12E-05            | W-s/C       | 1.00E-06           | 1.00E-06            | sec         |

| 1.21E-04           | 1.21E-04            | W-s/C       | 1.00E-05           | 1.00E-05            | sec         |

| 3.53E-04           | 3.50E-04            | W-s/C       | 1.00E-04           | 1.00E-04            | sec         |

| 1.19E-03           | 1.19E-03            | W-s/C       | 0.028              | 0.001               | sec         |

| 4.86E-03           | 5.05E-03            | W-s/C       | 0.001              | 0.009               | sec         |

| 2.17E-02           | 7.16E-03            | W-s/C       | 0.280              | 0.047               | sec         |

| 8.94E-02           | 3.51E-02            | W-s/C       | 2.016              | 0.875               | sec         |

| 0.304              | 0.262               | W-s/C       | 16.64              | 7.53                | sec         |

| 1.71               | 2.43                | W-s/C       | 59.47              | 68.4                | sec         |

|                    | 411                 | W-s/C       |                    | 92.221              | sec         |

| R's                | R's                 |             | R's                | R's                 |             |

| 0.041              | 0.041               | °C/W        | 2.44E-02           | 2.44E-02            | °C/W        |

| 0.095              | 0.096               | °C/W        | 5.28E-02           | 5.28E-02            | °C/W        |

| 0.279              | 0.281               | °C/W        | 1.67E-01           | 1.67E-01            | °C/W        |

| 1.154              | 0.995               | °C/W        | 3.5                | 0.7                 | °C/W        |

| 5.621              | 6.351               | °C/W        | 0.7                | 0.1                 | °C/W        |

| 13.180             | 1.910               | °C/W        | 8.7                | 5.8                 | °C/W        |

| 23.823             | 21.397              | °C/W        | 15.9               | 16.4                | °C/W        |

| 53.332             | 27.150              | °C/W        | 31.9               | 27.1                | °C/W        |

| 24.794             | 25.276              | °C/W        | 61.3               | 29.0                | °C/W        |

|                    | 0.218               | °C/W        |                    | 4.3                 | °C/W        |

<sup>\*</sup>Bold face items in the Cauer network above, represent the package without the external thermal system. The Bold face items in the Foster network are computed by the square root of time constant R(t) = 24.4 \* sqrt(time(sec)). The constant is derived based on the active area of the device with silicon and epoxy at the interface of the heat generation.

The Cauer networks generally have physical significance and may be divided between nodes to separate thermal behavior due to one portion of the network from another. The Foster networks, though when sorted by time constant (as above) bear a rough correlation with the Cauer networks, are really only convenient mathematical models. Both Foster and Cauer networks can be easily implemented

using circuit simulating tools, whereas Foster networks may be more easily implemented using mathematical tools (for instance, in a spreadsheet program), according to the following formula:

$$R(t) = \sum_{i=1}^{n} R_i (1 - e^{-t/tau_i})$$

Figure 20. Grounded Capacitor Thermal Network ("Cauer" Ladder)

Figure 21. Non-Grounded Capacitor Thermal Ladder ("Foster" Ladder)

Figure 22. SOIC-14 Single Pulse Heating

Figure 23. SOIC-14 Thermal Duty Cycle Curves on 1" Spreader Test Board

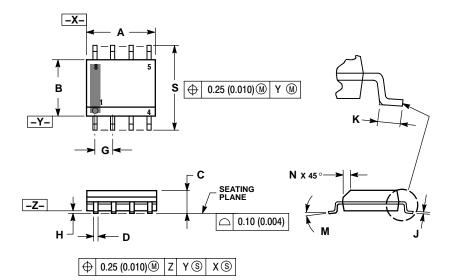

## **PACKAGE DIMENSIONS**

# SOIC-8 **D SUFFIX** CASE 751-07 **ISSUE AG**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER

- ANSI Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

- PER SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

6. 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

|     | MILLIMETERS |      | INCHES    |       |  |

|-----|-------------|------|-----------|-------|--|

| DIM | MIN         | MAX  | MIN       | MAX   |  |

| Α   | 4.80        | 5.00 | 0.189     | 0.197 |  |

| В   | 3.80        | 4.00 | 0.150     | 0.157 |  |

| С   | 1.35        | 1.75 | 0.053     | 0.069 |  |

| D   | 0.33        | 0.51 | 0.013     | 0.020 |  |

| G   | 1.27 BSC    |      | 0.050 BSC |       |  |

| Н   | 0.10        | 0.25 | 0.004     | 0.010 |  |

| J   | 0.19        | 0.25 | 0.007     | 0.010 |  |

| K   | 0.40        | 1.27 | 0.016     | 0.050 |  |

| M   | 0 °         | 8 °  | 0 °       | 8 °   |  |

| N   | 0.25        | 0.50 | 0.010     | 0.020 |  |

| S   | 5.80        | 6.20 | 0.228     | 0.244 |  |

# **SOLDERING FOOTPRINT\***

SCALE 6:1

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

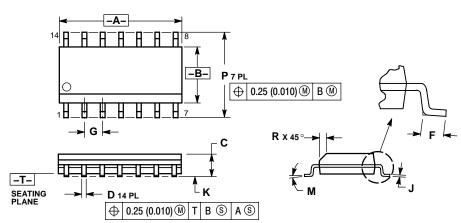

#### PACKAGE DIMENSIONS

SOIC-14 **D SUFFIX** CASE 751A-03 ISSUE G

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. 2. CONTROLLING DIMENSION: MILLIMETER.

- 3. DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

- 4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

- 5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |      | INCHES    |       |

|-----|-------------|------|-----------|-------|

| DIM | MIN         | MAX  | MIN       | MAX   |

| Α   | 8.55        | 8.75 | 0.337     | 0.344 |

| В   | 3.80        | 4.00 | 0.150     | 0.157 |

| С   | 1.35        | 1.75 | 0.054     | 0.068 |

| D   | 0.35        | 0.49 | 0.014     | 0.019 |

| F   | 0.40        | 1.25 | 0.016     | 0.049 |

| G   | 1.27 BSC    |      | 0.050 BSC |       |

| J   | 0.19        | 0.25 | 0.008     | 0.009 |

| K   | 0.10        | 0.25 | 0.004     | 0.009 |

| M   | 0 °         | 7 °  | 0 °       | 7°    |

| Р   | 5.80        | 6.20 | 0.228     | 0.244 |

| R   | 0.25        | 0.50 | 0.010     | 0.019 |

ON Semiconductor and una are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

## **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT

Literature Distribution Center for ON Semiconductor P.O. Box 61312, Phoenix, Arizona 85082-1312 USA Phone: 480-829-7710 or 800-344-3860 Toll Free USA/Canada Fax: 480–829–7709 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free

Japan: ON Semiconductor, Japan Customer Focus Center 2-9-1 Kamimeguro, Meguro-ku, Tokyo, Japan 153-0051 Phone: 81-3-5773-3850

ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your local Sales Representative.