# Low Dropout Linear Regulator with Watchdog, Wake Up, RESET, and ENABLE

The NCV8518 device is a precision micropower voltage regulator. It has a fixed output voltage of  $5.0\,\mathrm{V}$  and regulates within  $\pm 2\%$ . It is suitable for use in all automotive environments and contains all the required functions to control a microprocessor. This device has low dropout voltage and low quiescent current. It includes a watchdog timer, adjustable reset, wake up and enable function. Also encompassed in this device are safety features such as thermal shutdown and short circuit protection. It is capable of handling up to  $45\,\mathrm{V}$  transients.

#### **Features**

- Output Voltage of 5.0 V

- ±2% Output Voltage Tolerance

- Output Current up to 250 mA

- Micropower Compatible Control Functions:

- ENABLE

- Watchdog

- RESET

- Wake Up

- NCV Prefix for Automotive and Other Applications Requiring Site and Change Control

- Low Dropout Voltage

- Low Quiescent Current of 100 μA

- Protection Features:

- Thermal Shutdown

- Short Circuit

- Low Sleep Mode Current less than 1.0 μA

- These are Pb-Free Devices

## **Applications**

- Tire Pressure Monitor

- Battery Powered Consumer Electronics

## ON Semiconductor®

http://onsemi.com

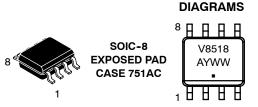

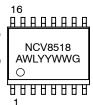

**MARKING**

A = Assembly Location

WL = Wafer Lot YY, Y = Year WW = Work Week •, or G = Pb-Free Package

#### **ORDERING INFORMATION**

| Device       | Package  | Shipping <sup>†</sup> |  |

|--------------|----------|-----------------------|--|

| NCV8518PDG   | SOIC-8*  | 98 Units / Rail       |  |

| NCV8518PDR2G | SOIC-8*  | 2500 / Tape & Reel    |  |

| NCV8518PWG   | SOIC-16* | 47 Units / Rail       |  |

| NCV8518PWR2G | SOIC-16* | 1000 / Tape & Reel    |  |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

1

<sup>\*</sup>These packages are inherently Pb-Free.

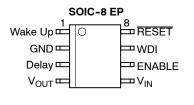

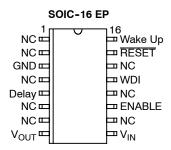

## **PIN CONNECTIONS**

## PIN FUNCTION DESCRIPTION

| Р         | in                           |                  |                                                                                                                                                           |  |

|-----------|------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SOIC-8 EP | SOIC-16<br>E PAD             | Symbol           | Description                                                                                                                                               |  |

| 4         | 8                            | V <sub>OUT</sub> | Regulated output voltage.                                                                                                                                 |  |

| 5         | 9                            | V <sub>IN</sub>  | Input supply voltage.                                                                                                                                     |  |

| 7         | 13                           | WDI              | CMOS compatible Watchdog input. The watchdog function monitors the falling edge of the incoming signal.                                                   |  |

| 2         | 3                            | GND              | Ground connection.                                                                                                                                        |  |

| 6         | 11                           | ENABLE           | ENABLE control for the IC. Positive logic.                                                                                                                |  |

| 8         | 15                           | RESET            | CMOS compatible output RESET goes low whenever V <sub>OUT</sub> drops by more than 7.0% from nominal, or during the absence of a correct watchdog signal. |  |

| 3         | 5                            | Delay            | Buffered reference voltage used to create timing current for $\overline{\text{RESET}}$ and Watchdog threshold frequency from $R_{Delay.}$                 |  |

| -         | 1, 2, 4, 6, 7,<br>10, 12, 14 | NC               | No Connection.                                                                                                                                            |  |

| 1         | 16                           | Wake Up          | Continuously generated signal that interrupts the microprocessor from sleep mode.                                                                         |  |

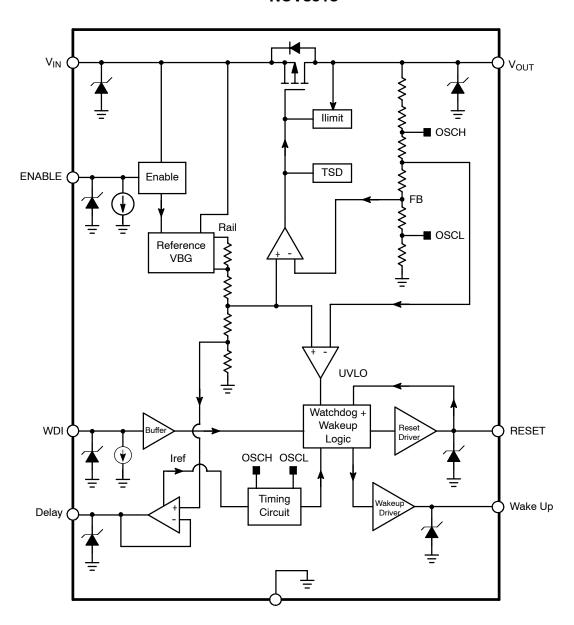

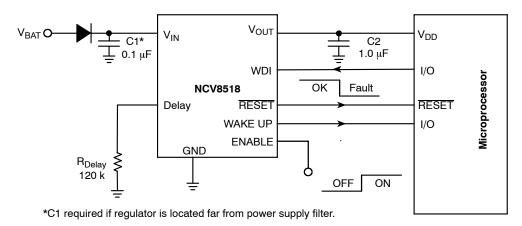

Figure 1. Block Diagram

#### **MAXIMUM RATINGS**

| Rating                                                                                                                                              | Symbol                               | Value                | Unit         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------|--------------|

| Input Voltage                                                                                                                                       | V <sub>IN</sub> , ENABLE             | -0.3 to 45           | V            |

| Output Voltage                                                                                                                                      | V <sub>OUT</sub>                     | -0.3 to +7.0         | V            |

| ESD Susceptibility (Human Body Model)                                                                                                               | -                                    | 2.0                  | kV           |

| Logic Inputs/Outputs (Reset, WDI, Wake Up, Delay)                                                                                                   | -                                    | -0.3 to +7.0         | V            |

| Operating Junction Temperature                                                                                                                      | $T_J$                                | -40 to150            | °C           |

| Storage Temperature Range                                                                                                                           | T <sub>S</sub>                       | -55 to +150          | °C           |

| Package Thermal Resistance, SOIC-8 EP (Please refer to Thermal Characteristics table)                                                               | -                                    | -                    | -            |

| Package Thermal Resistance, SOIC-16 EP (Note 1) Junction-to-Case Junction-to-Ambient                                                                | R <sub>θJC</sub><br>R <sub>θJA</sub> | 15<br>56             | °C/W<br>°C/W |

| Moisture Sensitivity Level SOIC-16 EP (Case 751R) SOIC-8 EP (Case 751AC)                                                                            | MSL                                  | 2<br>2               |              |

| Lead Temperature Soldering: Reflow Leaded Part 60-150 sec above 183°C, 30 sec max at peak Lead-Free Part 60-150 sec above 217°C, 40 sec max at peak |                                      | 240 peak<br>265 peak | °C           |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### THERMAL CHARACTERISTICS

| Parameter                                                         | Board/Mounting Conditions Typical Value |                                    | Unit |  |

|-------------------------------------------------------------------|-----------------------------------------|------------------------------------|------|--|

| SO-8 Exposed Pad Package                                          |                                         |                                    |      |  |

|                                                                   | minimum-pad board (Note 1)              | 1 sq. inch spreader board (Note 2) |      |  |

| Junction to case top ( $\Psi$ -JT, $\theta_{JT}$ )                | 19                                      | 8                                  | °C/W |  |

| Junction to pin1 (Ψ-JL1, θ <sub>JL1</sub> )                       | 68                                      | 63                                 | °C/W |  |

| Junction to board ( $\Psi$ -JB, $\theta_{JB}$ ) <sup>3</sup>      | 9                                       | 10                                 | °C/W |  |

| Junction to ambient ( $R_{\theta JA}$ , $\theta_{JA}$ )           | 235                                     | 57                                 | °C/W |  |

| SO-16 Exposed Pad Package                                         |                                         |                                    |      |  |

|                                                                   | minimum-pad board (Note 4)              | 1 sq. inch spreader board (Note 2) |      |  |

| Junction to case top ( $\Psi$ -JT, $\theta$ <sub>JT</sub> )       | 30                                      | 16                                 | °C/W |  |

| Junction to pin1 (Ψ-JL1, $\theta_{\text{JL1}}$ )                  | 70                                      | 65                                 | °C/W |  |

| Junction to board ( $\Psi$ -JB, $\theta$ <sub>JB</sub> ) (Note 3) | 15                                      | 17                                 | °C/W |  |

| Junction to ambient ( $R_{\theta,IA}, \theta_{IA}$ )              | 150                                     | 55                                 | °C/W |  |

## Specific notes on thermal characterization conditions:

All boards are 0.062" thick FR4, 3" square, with varying amounts of copper heat spreader, in still air (free convection) conditions. Numerical values are derived from an axisymmetric finite-element model where active die area, total die area, flag area, pad area, and board area are equated to the actual corresponding areas.

- 1. 1 oz copper, 3.5 mm<sup>2</sup> spreader area (minimum exposed pad, not including traces which are assumed).

- 2. 1 oz copper, 645 mm² (1in²) spreader area (includes exposed pad).

- 3. "board" is defined as center of exposed pad soldered to board; this is the recommended number to be used for thermal calculations, as it best represents the primary heat flow path and is least sensitive to board and ambient properties.

- 4. 1 oz copper, 17.2 mm² spreader area (minimum exposed pad, not including traces which are assumed).

$\textbf{ELECTRICAL CHARACTERISTICS} \; (-40^{\circ}C \leq T_{J} \leq 150^{\circ}C; \; 6.0 \; V \leq V_{IN} \leq 28 \; V, \; 100 \; \mu A \leq I_{OUT} \leq 150 \; mA, \; C_{2} = 1.0 \; \mu F, \; R_{Delay} = 60 \; k; \; C_{2} = 1.0 \; \mu F, \; R_{Delay} = 1.0 \; \mu F, \; R_$ unless otherwise specified.)

| Characteristic                                                                                                                                                                             | Symbol              | Min                    | Тур                    | Max         | Unit              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------|------------------------|-------------|-------------------|

| Output                                                                                                                                                                                     |                     |                        |                        |             |                   |

| Output Voltage                                                                                                                                                                             | V <sub>OUT</sub>    | 4.9<br>-2%             | 5.00                   | 5.10<br>+2% | V                 |

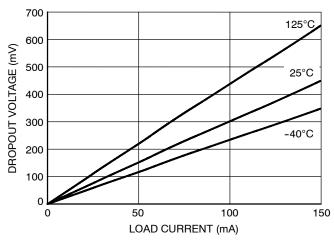

| Dropout Voltage (V <sub>IN</sub> - V <sub>OUT</sub> , I <sub>OUT</sub> = 150 mA) (Note 5)                                                                                                  | $V_{DO}$            | -                      | 425                    | 750         | mV                |

| Load Regulation $(V_{IN}=13.5 \text{ V}, 100 \mu\text{A} \leq I_{OUT} \leq 150 \text{ mA})$                                                                                                | Reg <sub>load</sub> | -                      | 5.0                    | 30          | mV                |

| Line Regulation (6.0 V $\leq$ V <sub>IN</sub> $\leq$ 28 V, I <sub>OUT</sub> = 5.0 mA)                                                                                                      | Reg <sub>line</sub> | -                      | 5.0                    | 20          | mV                |

| Current Limit                                                                                                                                                                              | I <sub>lim</sub>    | 255                    | 400                    | -           | mA                |

| Thermal Shutdown (Guaranteed by Design)                                                                                                                                                    | T <sub>Jmax</sub>   | 150                    | 180                    | 210         | °C                |

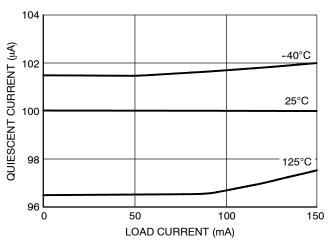

| Quiescent Current (V <sub>IN</sub> = 13.5 V, I <sub>OUT</sub> = 100 $\mu$ A, 150 mA, ENABLE = 2.0 V) (ENABLE = 0 V)                                                                        | IQ                  | -<br>-                 | 100<br>-               | 150<br>1.0  | μΑ                |

| RESET                                                                                                                                                                                      |                     |                        |                        |             |                   |

| Threshold Voltage                                                                                                                                                                          | -                   | 4.50                   | 4.65                   | 4.75        | V                 |

| Output Low<br>(R <sub>LOAD</sub> = 10 k to V <sub>OUT</sub> , V <sub>OUT</sub> = 1.0 V)                                                                                                    | -                   | -                      | 0.2                    | 0.4         | V                 |

| Output High (R <sub>LOAD</sub> = 10 k to GND)                                                                                                                                              | -                   | V <sub>OUT</sub> - 0.4 | V <sub>OUT</sub> - 0.2 | -           | V                 |

| Power On Reset Delay Time $(V_{IN} = 13.5 \text{ V}, R_{Delay} = 60 \text{ k}, I_{OUT} = 5.0 \text{ mA})$ $(V_{IN} = 13.5 \text{ V}, R_{Delay} = 120 \text{ k}, I_{OUT} = 5.0 \text{ mA})$ | t <sub>D</sub>      | 2.0                    | 3.0<br>6.0             | 4.0         | ms                |

| Watchdog Input                                                                                                                                                                             |                     |                        |                        |             |                   |

| Threshold                                                                                                                                                                                  | WDI <sub>high</sub> | 30                     | 50                     | 70          | %V <sub>OUT</sub> |

| Hysteresis T                                                                                                                                                                               | WDI <sub>hys</sub>  | 25                     | 100                    | -           | mV                |

| Input Current (WDI = 6.0 V)                                                                                                                                                                | -                   | -                      | 0.1                    | 2.0         | μΑ                |

| Wake Up Rising Edge to WDI Falling Edge Delay Wake Up WDI                                                                                                                                  | -                   | 5.0                    | -                      | -           | μs                |

| ENABLE (Note 6)                                                                                                                                                                            | •                   |                        |                        |             | •                 |

| Input Threshold<br>Logic Low<br>Logic High                                                                                                                                                 | V <sub>th(EN)</sub> | -<br>2.0               |                        | 0.8         | V                 |

| Input Current (ENABLE = 2.0 V)                                                                                                                                                             | -                   | -                      | 3.0                    | 10          | μА                |

<sup>5.</sup> Measured when the output voltage has dropped 2% from the nominal value. 6. If ENABLE is connected to  $V_{\text{IN}}$ , a 20 k $\Omega$  resistor must be placed in series.

**ELECTRICAL CHARACTERISTICS (continued)** (-40°C  $\leq$  T<sub>J</sub>  $\leq$  150°C; 6.0 V  $\leq$  V<sub>IN</sub>  $\leq$  28 V, 100  $\mu$ A  $\leq$  I<sub>OUT</sub>  $\leq$  150 mA, C<sub>2</sub> = 1.0  $\mu$ F, R<sub>Delay</sub> = 60 k; unless otherwise specified.)

| Characteristic                                                                                                                                   | Symbol | Min                    | Тур                     | Max     | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------|-------------------------|---------|------|

| Wake Up Output (V <sub>IN</sub> = 14 V, I <sub>OUT</sub> = 5.0 mA)                                                                               |        |                        |                         |         |      |

| Wake Up Period<br>(R <sub>DELAY</sub> = 60 k)<br>(R <sub>DELAY</sub> = 120 k)                                                                    | -      | 18<br>-                | 25<br>50                | 32<br>- | ms   |

| Wake Up Duty Cycle Nominal                                                                                                                       | -      | 45                     | 50                      | 55      | %    |

| RESET HIGH to Wake Up Rising Delay Time<br>(R <sub>DELAY</sub> = 60 k) 50% RESET Rising Edge to<br>50% Wake Up Edge (R <sub>DELAY</sub> = 120 k) | -      | 9.0                    | 12.5<br>25              | 16<br>- | ms   |

| Wake Up Response to Watchdog Input<br>50% WDI Falling Edge to<br>50% Wake Up Falling Edge                                                        | -      | -                      | 0.1                     | 5.0     | μs   |

| Wake Up Response to RESET 50% RESET Falling Edge to 50% Wake Up Falling Edge (V <sub>OUT</sub> = 5.0 V→ 4.5 V)                                   | -      | -                      | 0.1                     | 5.0     | μs   |

| Output Low (R <sub>LOAD</sub> = 10 k)                                                                                                            | -      | -                      | 0.2                     | 0.4     | V    |

| Output High (R <sub>LOAD</sub> = 10 k)                                                                                                           | -      | V <sub>OUT</sub> - 0.5 | V <sub>OUT</sub> - 0.25 | -       | V    |

| Delay                                                                                                                                            |        |                        |                         |         |      |

| Output Voltage (R <sub>DELAY</sub> = 60 k, 120 k)                                                                                                | -      | -                      | 0.48                    | -       | V    |

## **DEFINITION OF TERMS**

**Dropout Voltage:** The input-to-output voltage differential at which the circuit ceases to regulate against further reduction in input voltage. Measured when the output voltage has dropped 100 mV from the nominal value obtained at 14 V input, dropout voltage is dependent upon load current and junction temperature.

Input Voltage: The DC voltage applied to the input terminals with respect to ground.

**Line Regulation:** The change in output voltage for a change in the input voltage. The measurement is made under conditions of low dissipation or by using pulse techniques such that the average chip temperature is not significantly affected.

Load Regulation: The change in output voltage for a change in load current at constant chip temperature.

**Quiescent Current:** The part of the positive input current that does not contribute to the positive load current. The regulator ground lead current with no load.

Current Limit: Peak current that can be delivered to the output.

#### **TIMING DIAGRAMS**

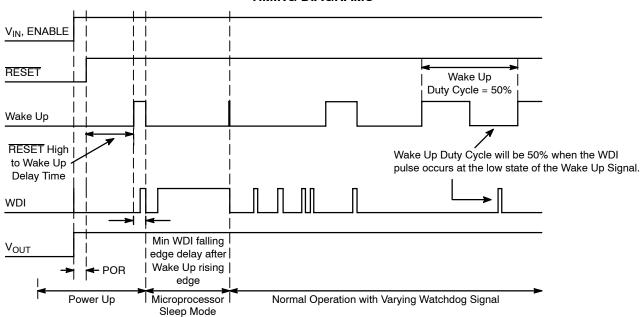

Figure 2. Power Up, Sleep Mode and Normal Operation

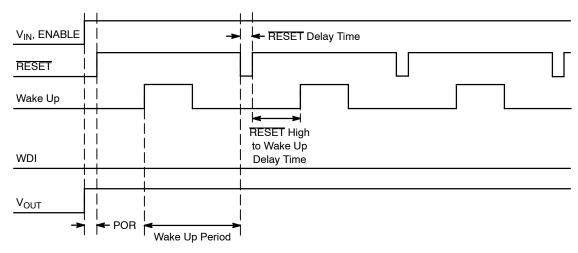

Figure 3. Error Condition: Watchdog Remains Low and a RESET is Issued

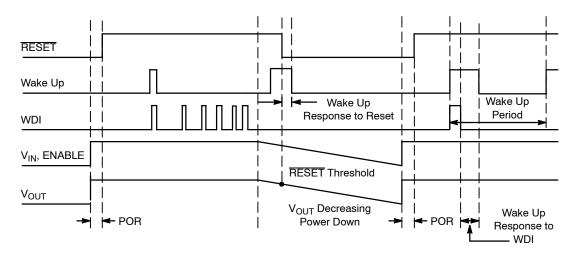

Figure 4. Power Down, Restart Sequence, and Wake Up Response to WDI

#### TYPICAL PERFORMANCE CHARACTERISTICS

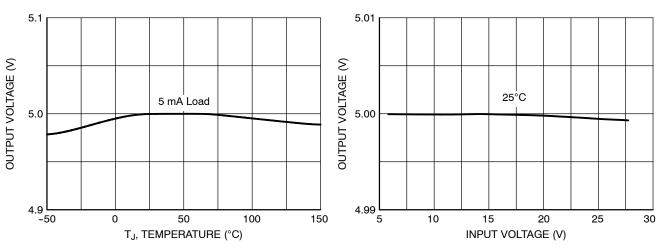

Figure 5. Output Voltage vs. Temperature

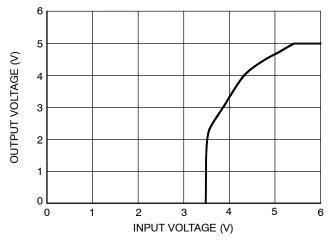

Figure 6. Output Voltage vs. Input Voltage

Figure 7. POR Delay vs. Temperature, 60 k $\Omega$  Rdelay

Figure 8. POR Delay vs. Temperature, 120 k $\Omega$  Rdelay

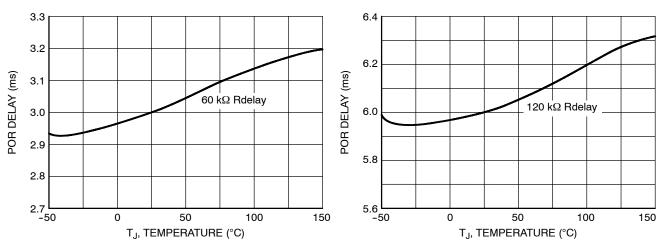

Figure 9. Stability Region of Capacitive ESR vs.

Output Current

Figure 10. Wakeup Period vs. Temperature

#### TYPICAL PERFORMANCE CHARACTERISTICS

6

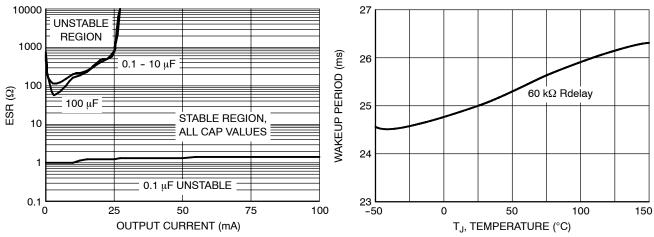

Figure 11. Wakeup Period vs. RDelay

Figure 12. POR Delay vs. RDelay

Figure 13. Output Voltage vs. Input Voltage, 5 mA Load

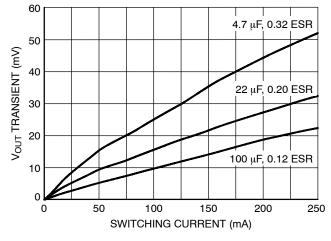

Figure 14. Load Transient Response

Figure 15. Dropout Voltage vs. Output Current

Figure 16. Quiescent Current vs. Output Current

#### **OPERATING DESCRIPTION**

#### General

The NCV8518 is a precision micropower voltage regulator featuring low quiescent current (100  $\mu A$  typical at 250 mA load) and low dropout voltage (450 mV typical at 150 mA). Integrated microprocessor control functions include Watchdog, Wakeup and  $\overline{RESET}.$  An Enable input is provided for logic level control of the regulator state. The combination of low quiescent current and comprehensive microprocessor interface functions make the NCV8518 ideal for use in both battery operated and automotive applications.

The NCV8518 is internally protected against short circuit and thermal runaway conditions. No external components are required to engage these protective mechanisms. The device continues to operate through 45 volt input transients, an important consideration in automotive environments.

#### Wakeup and Watchdog

To reduce battery drain, a microprocessor or microcontroller can transition to a low current consumption ("sleep") mode when code execution is suspended or complete. The NCV8518 Wakeup signal is generated and output periodically to interrupt sleep mode. The nominal Wakeup output is a 5 volt square wave (generated from VOUT) with a duty cycle of 50%, at a frequency determined by external timing resistor  $R_{\rm DELAY}$ . In response to the rising edge of the Wakeup signal, the microprocessor will subsequently output a Watchdog pulse and check its inputs to decide if it should resume normal operation or remain in sleep mode.

The NCV8518 responds to the falling edge of the Watchdog signal, which it expects at least once during each Wakeup period. When the correct Watchdog signal is received, the Wakeup output is forced low. Other Watchdog pulses received within the same cycle are ignored. The Watchdog circuitry continuously monitors the input Watchdog signal (WDI) from the microprocessor. The absence of a falling edge on the Watchdog input during one Wakeup cycle will cause a Reset pulse to be output at the end of the Wakeup cycle (see Figure 4).

#### RESET

RESET is independent of VIN and maintains its correct state to an output voltage as low as 1.0 V. A Reset signal (active low) is issued for any of three conditions:

- 1. During power up, the RESET is held low until the output voltage is in regulation.

- 2. During operation, if the output voltage shifts below the regulation limits, the RESET toggles low, and remains low until proper output voltage regulation is restored.

- 3. Finally, RESET goes low if the regulator does not receive a Watchdog signal within a Wakeup period.

The RESET pulse width, Wakeup signal frequency, and Wakeup delay time are all set by one external resistor, RDelay.

During power up,  $\overline{RESET}$  is held low until the output voltage is in regulation. During operation, if the output voltage shifts below the regulation limits, the  $\overline{RESET}$  will toggle low and remain low as long as the output remains out of regulation. Once proper output voltage regulation is restored,  $\overline{RESET}$  stays low during the  $\overline{RESET}$  delay time, and then goes high.

The Wakeup output is pulled low during a  $\overline{RESET}$  regardless of the cause of the  $\overline{RESET}$ . After the  $\overline{RESET}$  returns high, the Wakeup cycle begins again (see Figure 4).

The RESET Delay Time, Wakeup signal frequency and RESET high to Wakeup delay time are all set by one external resistor, RDelay, according to the following equations:

Wakeup Period (seconds) =  $(4.17 \times 10^{-7}) * R_{DELAY} (\Omega)$

RESET Delay Time (seconds) =  $(5.21 \times 10^{-8}) * R_{DELAY}(\Omega)$

RESET High to Wakeup Delay Time (seconds) =

$$(2.08 \times 10^{-7}) * R_{DELAY}(\Omega)$$

The voltage present at the Delay pin is a buffered bandgap voltage (~1.25 V) and can be used as a reference for an external tracking regulator.

#### **Enable**

This is a standard TTL and CMOS logic compatible input that can be used to turn the regulator on or off. Logic high enables the regulator; logic low disables it (also called *shutdown*). In the disabled/shutdown state, the pass transistor is off and total quiescent current is less than 1 µA.

Figure 17. Application Circuit

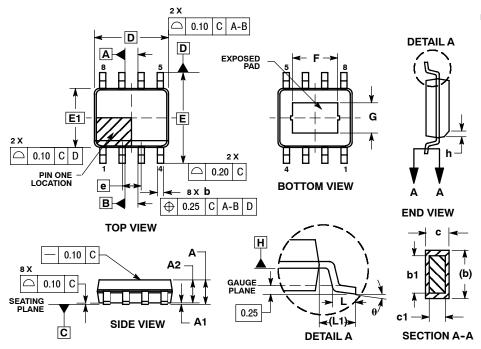

#### **PACKAGE DIMENSIONS**

#### SOIC-8 EP **D SUFFIX** CASE 751AC-01 **ISSUE B**

- NOTES:

1. DIMENSIONS AND TOLERANCING PER

- DIMENSIONS AND TOLERANCING PER ASME Y14.5M, 1994.

DIMENSIONS IN MILLIMETERS (ANGLES IN DEGREES).

DIMENSION & DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 MM TOTAL IN EXCESS OF THE "b" DIMENSION AT MAXIMUM MATERIAL. DIMENSION AT MAXIMUM MATERIAL CONDITION.

DATUMS A AND B TO BE DETERMINED AT DATUM PLANE H.

|     | MILLIMETERS |      |  |

|-----|-------------|------|--|

| DIM | MIN         | MAX  |  |

| Α   | 1.35        | 1.75 |  |

| A1  | 0.00        | 0.10 |  |

| A2  | 1.35        | 1.65 |  |

| b   | 0.31        | 0.51 |  |

| b1  | 0.28        | 0.48 |  |

| c   | 0.17        | 0.25 |  |

| с1  | 0.17        | 0.23 |  |

| D   | 4.90        | BSC  |  |

| Е   | 6.00        | BSC  |  |

| E1  | 3.90        | BSC  |  |

| е   | 1.27        | BSC  |  |

| L   | 0.40        | 1.27 |  |

| L1  | 1.04        | REF  |  |

| F   | 2.24        | 3.20 |  |

| G   | 1.55        | 2.51 |  |

| h   | 0.25        | 0.50 |  |

| θ   | 0 °         | 8°   |  |

|     |             |      |  |

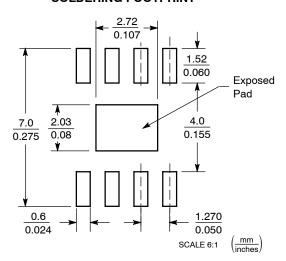

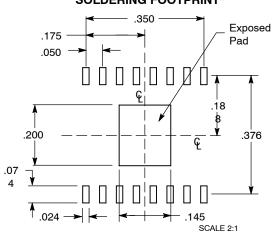

## **SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

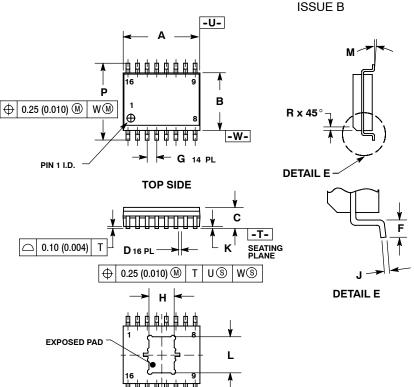

#### **PACKAGE DIMENSIONS**

## SOIC-16 LEAD WIDE BODY, EXPOSED PAD **PDW SUFFIX**

CASE 751R-02

**BACK SIDE**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

- Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER. DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER

- 5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.13 (0.005) TOTAL IN EXCESS OF THE D DIMENSION

- AT MAXIMUM MATERIAL CONDITION.

6. 751R-01 OBSOLETE, NEW STANDARD 751R-02.

|     | MILLIMETERS |       | INCHES    |       |  |

|-----|-------------|-------|-----------|-------|--|

| DIM | MIN         | MAX   | MIN       | MAX   |  |

| Α   | 10.15       | 10.45 | 0.400     | 0.411 |  |

| В   | 7.40        | 7.60  | 0.292     | 0.299 |  |

| С   | 2.35        | 2.65  | 0.093     | 0.104 |  |

| D   | 0.35        | 0.49  | 0.014     | 0.019 |  |

| F   | 0.50        | 0.90  | 0.020     | 0.035 |  |

| G   | 1.27        | BSC   | 0.050 BSC |       |  |

| Н   | 3.31        | 3.51  | 0.130     | 0.138 |  |

| 7   | 0.25        | 0.32  | 0.010     | 0.012 |  |

| K   | 0.10        | 0.25  | 0.004     | 0.009 |  |

| L   | 4.58        | 4.78  | 0.180     | 0.188 |  |

| M   | 0 °         | 7 °   | 0 °       | 7 °   |  |

| P   | 10.05       | 10.55 | 0.395     | 0.415 |  |

| R   | 0.25        | 0.75  | 0.010     | 0.029 |  |

## **SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and was are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 61312, Phoenix, Arizona 85082-1312 USA Phone: 480-829-7710 or 800-344-3860 Toll Free USA/Canada Fax: 480-829-7709 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Japan: ON Semiconductor, Japan Customer Focus Center 2-9-1 Kamimeguro, Meguro-ku, Tokyo, Japan 153-0051 Phone: 81-3-5773-3850

ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your local Sales Representative.