Preferred Device

# **Sensitive Gate Silicon Controlled Rectifiers**

# **Reverse Blocking Thyristors**

Designed for high volume, low cost, industrial and consumer applications such as motor control; process control; temperature, light and speed control.

- Small Size

- Passivated Die for Reliability and Uniformity

- Low Level Triggering and Holding Characteristics

- Device Marking: Device Type, e.g., for MCR12DSM: R12DSM, Date Code

#### **MAXIMUM RATINGS** (T<sub>J</sub> = 25°C unless otherwise noted)

| Rating                                                                                                              | Symbol                     | Value      | Unit               |

|---------------------------------------------------------------------------------------------------------------------|----------------------------|------------|--------------------|

| Peak Repetitive Off–State Voltage <sup>(1)</sup> (T <sub>J</sub> = -40 to 110°C, Sine Wave, 50 to 60 Hz, Gate Open) | V <sub>DRM</sub> ,<br>VRRM |            | Volts              |

| MCR12DSM<br>MCR12DSN                                                                                                |                            | 600<br>800 |                    |

| On–State RMS Current<br>(180° Conduction Angles; T <sub>C</sub> = 75°C)                                             | I <sub>T(RMS)</sub>        | 12         | Amps               |

| Average On–State Current (180° Conduction Angles; T <sub>C</sub> = 75°C)                                            | l <sub>T(AV)</sub>         | 7.6        | Amps               |

| Peak Non-Repetitive Surge Current<br>(1/2 Cycle, Sine Wave 60 Hz,<br>T <sub>J</sub> = 110°C)                        | ITSM                       | 100        | Amps               |

| Circuit Fusing Consideration (t = 8.3 msec)                                                                         | I <sup>2</sup> t           | 41         | A <sup>2</sup> sec |

| Forward Peak Gate Power (Pulse Width ≤ 1.0 μsec, T <sub>C</sub> = 75°C)                                             | РGМ                        | 5.0        | Watts              |

| Forward Average Gate Power (t = 8.3 msec, T <sub>C</sub> = 75°C)                                                    | PG(AV)                     | 0.5        | Watts              |

| Forward Peak Gate Current<br>(Pulse Width ≤ 1.0 μsec, T <sub>C</sub> = 75°C)                                        | I <sub>GM</sub>            | 2.0        | Amps               |

| Operating Junction Temperature Range                                                                                | TJ                         | -40 to 110 | °C                 |

| Storage Temperature Range                                                                                           | T <sub>stg</sub>           | -40 to 150 | °C                 |

(1) V<sub>DRM</sub> and V<sub>RRM</sub> for all types can be applied on a continuous basis. Ratings apply for zero or negative gate voltage; however, positive gate voltage shall not be applied concurrent with negative potential on the anode. Blocking voltages shall not be tested with a constant current source such that the voltage ratings of the device are exceeded.

# **ON Semiconductor**

http://onsemi.com

# SCRs 12 AMPERES RMS 600 thru 800 VOLTS

D-PAK CASE 369A STYLE 4

| PIN ASSIGNMENT |       |  |  |

|----------------|-------|--|--|

| 1 Cathode      |       |  |  |

| 2              | Anode |  |  |

| 3              | Gate  |  |  |

| 4              | Anode |  |  |

#### ORDERING INFORMATION

| Device     | Package   | Shipping                             |

|------------|-----------|--------------------------------------|

| MCR12DSMT4 | DPAK 369A | 16mm Tape<br>and Reel<br>(2.5K/Reel) |

| MCR12DSNT4 | DPAK 369A | 16mm Tape<br>and Reel<br>(2.5K/Reel) |

Preferred devices are recommended choices for future use and best overall value

#### THERMAL CHARACTERISTICS

| Characteristic                                                                                   | Symbol                                                      | Max             | Unit |

|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------|------|

| Thermal Resistance — Junction to Case — Junction to Ambient — Junction to Ambient <sup>(1)</sup> | R <sub>Ð</sub> JC<br>R <sub>Ð</sub> JA<br>R <sub>Ð</sub> JA | 2.2<br>88<br>80 | °C/W |

| Maximum Lead Temperature for Soldering Purposes <sup>(2)</sup>                                   | $T_L$                                                       | 260             | °C   |

# **ELECTRICAL CHARACTERISTICS** (T<sub>J</sub> = 25°C unless otherwise noted)

| Characteristics                                                                                                                                                                              |                                                                           | Symbol                     | Min              | Тур            | Max             | Unit  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------|------------------|----------------|-----------------|-------|--|

| OFF CHARACTERISTICS                                                                                                                                                                          |                                                                           |                            |                  |                |                 |       |  |

| Peak Repetitive Forward or Reverse Blocking Current(3) $(V_{AK} = Rated \ V_{DRM} \ or \ V_{RRM}; \ R_{GK} = 1.0 \ K\Omega) \qquad T_{J} = 25^{\circ}C \\ T_{J} = 110^{\circ}C$              |                                                                           | I <sub>DRM</sub> ,<br>IRRM | =                | _              | 10<br>500       | μΑ    |  |

| ON CHARACTERISTICS                                                                                                                                                                           |                                                                           | •                          | •                |                |                 |       |  |

| Peak Reverse Gate Blocking Voltage (I <sub>GR</sub> = 10 μA)                                                                                                                                 |                                                                           | VGRM                       | 10               | 12.5           | 18              | Volts |  |

| Peak Reverse Gate Blocking Current (VGR = 10 V)                                                                                                                                              |                                                                           | IGRM                       | _                | _              | 1.2             | μΑ    |  |

| Peak Forward On–State Voltage(4)<br>(I <sub>TM</sub> = 20 A)                                                                                                                                 |                                                                           | VTM                        | _                | 1.3            | 1.9             | Volts |  |

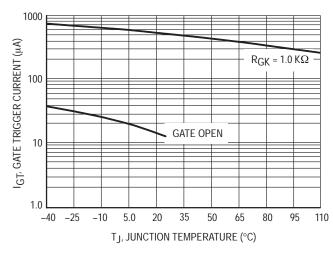

| Gate Trigger Current (Continuous dc) <sup>(5)</sup> $(V_D = 12 \text{ V}, \text{RL} = 100 \Omega)$                                                                                           | T <sub>J</sub> = 25°C<br>T <sub>J</sub> = -40°C                           | <sup>I</sup> GT            | 5.0<br>—         | 12<br>—        | 200<br>300      | μΑ    |  |

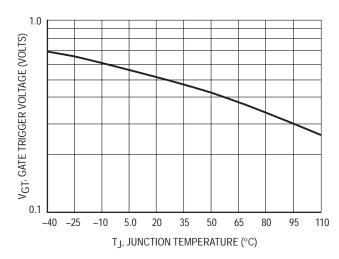

| Gate Trigger Voltage (Continuous dc) <sup>(5)</sup> $(V_D = 12 \text{ V}, \text{ R}_L = 100 \Omega)$                                                                                         | T <sub>J</sub> = 25°C<br>T <sub>J</sub> = -40°C<br>T <sub>J</sub> = 110°C | V <sub>GT</sub>            | 0.45<br>—<br>0.2 | 0.65<br>—<br>— | 1.0<br>1.5<br>— | Volts |  |

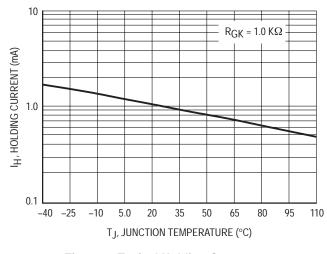

| Holding Current (V <sub>D</sub> = 12 V, Initiating Current = 200 mA, Gate Open)                                                                                                              | T <sub>J</sub> = 25°C<br>T <sub>J</sub> = -40°C                           | lн                         | 0.5<br>—         | 1.0            | 6.0<br>10       | mA    |  |

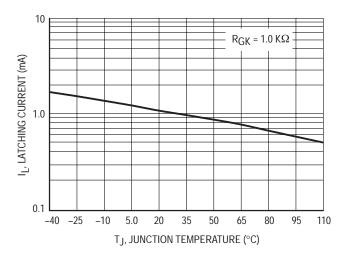

| Latching Current<br>(V <sub>D</sub> = 12 V, I <sub>G</sub> = 2.0 mA)                                                                                                                         | T <sub>J</sub> = 25°C<br>T <sub>J</sub> = -40°C                           | ΙL                         | 0.5<br>—         | 1.0            | 6.0<br>10       | mA    |  |

| Turn–On Time (Source Voltage = 12 V, R <sub>S</sub> = 6.0 K $\Omega$ , I <sub>T</sub> = 16 A(pk), R <sub>0</sub> (V <sub>D</sub> = Rated V <sub>DRM</sub> , Rise Time = 20 ns, Pulse Width = |                                                                           | tgt                        |                  | 2.0            | 5.0             | μs    |  |

#### **DYNAMIC CHARACTERISTICS**

| Characteristics                                                                                                                                                           | Symbol | Min | Тур | Max | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|------|

| Critical Rate of Rise of Off–State Voltage ( $V_D = 0.67 \text{ X Rated } V_{DRM}$ , Exponential Waveform, $R_{GK} = 1.0 \text{ K}\Omega$ , $T_J = 110^{\circ}\text{C}$ ) | dv/dt  | 2.0 | 10  | ı   | V/μs |

<sup>(1)</sup> Surface mounted on minimum recommended pad size.

<sup>(2) 1/8&</sup>quot; from case for 10 seconds.

<sup>(3)</sup> Ratings apply for negative gate voltage or  $R_{GK} = 1.0 \text{ K}\Omega$ . Devices shall not have a positive gate voltage concurrently with a negative voltage on the anode. Devices should not be tested with a constant current source for forward and reverse blocking capability such that the voltage applied exceeds the rated blocking voltage.

<sup>(4)</sup> Pulse Test: Pulse Width  $\leq$  2.0 msec, Duty Cycle  $\leq$  2%.

<sup>(5)</sup> RGK current not included in measurement.

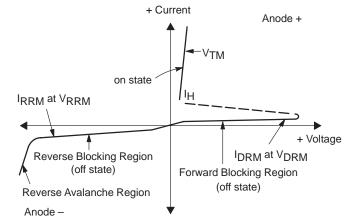

# **Voltage Current Characteristic of SCR**

| Symbol          | Parameter                                 |

|-----------------|-------------------------------------------|

| VDRM            | Peak Repetitive Off State Forward Voltage |

| IDRM            | Peak Forward Blocking Current             |

| VRRM            | Peak Repetitive Off State Reverse Voltage |

| IRRM            | Peak Reverse Blocking Current             |

| V <sub>TM</sub> | Peak On State Voltage                     |

| lΗ              | Holding Current                           |

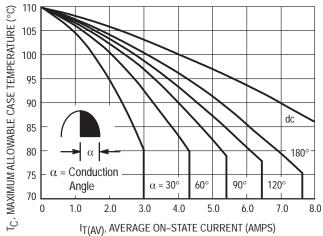

I<sub>T(AV)</sub>, AVERAGE ON-STATE CURRENT (AMPS)

Figure 1. Average Current Derating

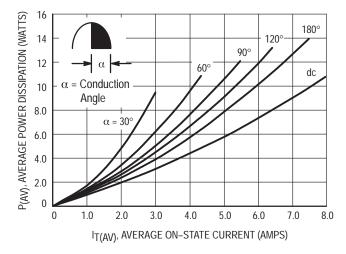

Figure 2. On-State Power Dissipation

1.0 (NORWALIZED)

2 (A) TRANSIENT THERMAL RESISTANCE

(NORWALIZED)

1.0 (NORWALIZED)

2 (NORWALIZED)

1.0 (NORWALIZED)

4 (NORWALIZED)

1.0 (NORWALIZED)

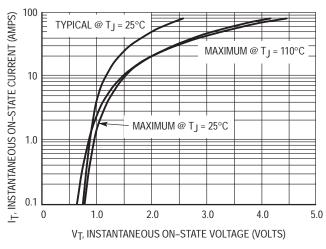

Figure 3. On-State Characteristics

**Figure 4. Transient Thermal Response**

Figure 5. Typical Gate Trigger Current versus Junction Temperature

Figure 6. Typical Gate Trigger Voltage versus Junction Temperature

Figure 7. Typical Holding Current versus Junction Temperature

Figure 8. Typical Latching Current versus Junction Temperature

1000

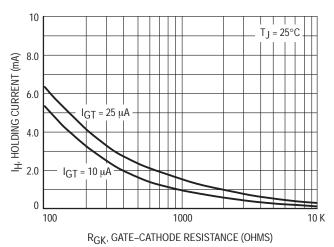

Figure 9. Holding Current versus Gate-Cathode Resistance

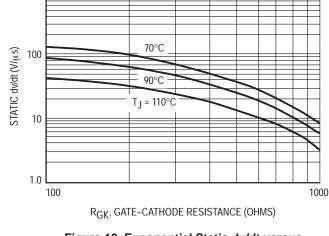

Figure 10. Exponential Static dv/dt versus Gate—Cathode Resistance and Junction Temperature

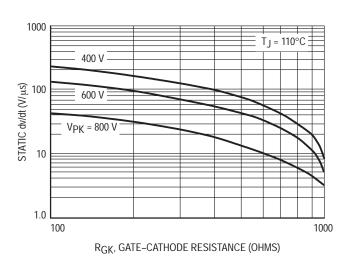

Figure 11. Exponential Static dv/dt versus Gate-Cathode Resistance and Peak Voltage

$\mathsf{R}_{GK}, \mathsf{GATE}\text{-}\mathsf{CATHODE}$  RESISTANCE (OHMS)

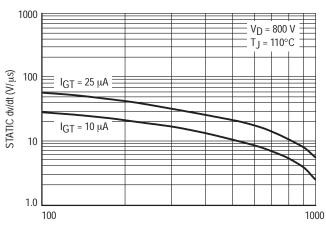

Figure 12. Exponential Static dv/dt versus Gate-Cathode Resistance and Gate Trigger Current Sensitivity

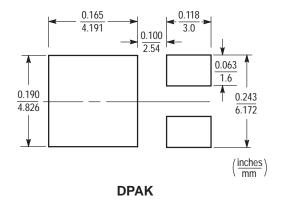

# MINIMUM RECOMMENDED FOOTPRINT FOR SURFACE MOUNTED APPLICATIONS

Surface mount board layout is a critical portion of the total design. The footprint for the semiconductor packages must be the correct size to insure proper solder connection

interface between the board and the package. With the correct pad geometry, the packages will self align when subjected to a solder reflow process.

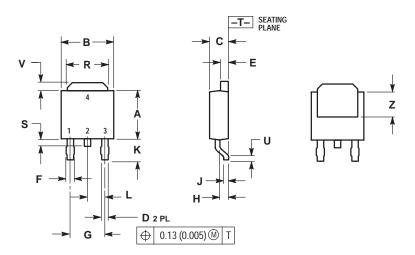

# **PACKAGE DIMENSIONS**

# D-PAK CASE 369A-13 ISSUE Z

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

|     | INC       | HES   | MILLIMETERS |      |

|-----|-----------|-------|-------------|------|

| DIM | MIN       | MAX   | MIN         | MAX  |

| Α   | 0.235     | 0.250 | 5.97        | 6.35 |

| В   | 0.250     | 0.265 | 6.35        | 6.73 |

| С   | 0.086     | 0.094 | 2.19        | 2.38 |

| D   | 0.027     | 0.035 | 0.69        | 0.88 |

| E   | 0.033     | 0.040 | 0.84        | 1.01 |

| F   | 0.037     | 0.047 | 0.94        | 1.19 |

| G   | 0.180     | BSC   | 4.58        | BSC  |

| Н   | 0.034     | 0.040 | 0.87        | 1.01 |

| J   | 0.018     | 0.023 | 0.46        | 0.58 |

| K   | 0.102     | 0.114 | 2.60        | 2.89 |

| L   | 0.090 BSC |       | 2.29        | BSC  |

| R   | 0.175     | 0.215 | 4.45        | 5.46 |

| S   | 0.020     | 0.050 | 0.51        | 1.27 |

| U   | 0.020     |       | 0.51        |      |

| ٧   | 0.030     | 0.050 | 0.77        | 1.27 |

| Z   | 0.138     |       | 3.51        |      |

STYLE 4: PIN 1. CATHODE 2. ANODE 3. GATE 4. ANODE

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### **PUBLICATION ORDERING INFORMATION**

#### NORTH AMERICA Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

**Phone**: 303–675–2175 or 800–344–3860 Toll Free USA/Canada **Fax**: 303–675–2176 or 800–344–3867 Toll Free USA/Canada

Email: ONlit@hibbertco.com

Fax Response Line: 303-675-2167 or 800-344-3810 Toll Free USA/Canada

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

EUROPE: LDC for ON Semiconductor - European Support

German Phone: (+1) 303-308-7140 (M-F 1:00pm to 5:00pm Munich Time)

Email: ONlit-german@hibbertco.com

French Phone: (+1) 303–308–7141 (M–F 1:00pm to 5:00pm Toulouse Time)

Email: ONlit-french@hibbertco.com

**English Phone**: (+1) 303–308–7142 (M–F 12:00pm to 5:00pm UK Time)

Email: ONlit@hibbertco.com

EUROPEAN TOLL-FREE ACCESS\*: 00-800-4422-3781

\*Available from Germany, France, Italy, England, Ireland

CENTRAL/SOUTH AMERICA:

Spanish Phone: 303-308-7143 (Mon-Fri 8:00am to 5:00pm MST)

Email: ONlit-spanish@hibbertco.com

ASIA/PACIFIC: LDC for ON Semiconductor – Asia Support

**Phone**: 303–675–2121 (Tue–Fri 9:00am to 1:00pm, Hong Kong Time)

Toll Free from Hong Kong & Singapore:

001-800-4422-3781 Email: ONlit-asia@hibbertco.com

JAPAN: ON Semiconductor, Japan Customer Focus Center 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–0031

**Phone**: 81–3–5740–2745 **Email**: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local Sales Representative.