- 8.0 - 6.0 - 4.0 - 2.0

# **Linear Four-Quadrant Multiplier**

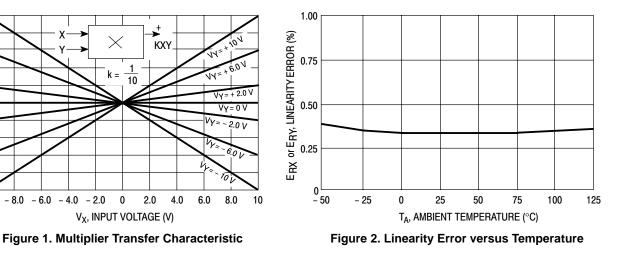

The MC1494 is designed for use where the output voltage is a linear product of two input voltages. Typical applications include: multiply, divide, square root, mean square, phase detector, frequency doubler, balanced modulator/ demodulator, electronic gain control.

The MC1494 is a variable transconductance multiplier with internal level-shift circuitry and voltage regulator. Scale factor, input offsets and output offset are completely adjustable with the use of four external potentiometers. Two complementary regulated voltages are provided to simplify offset adjustment and improve power supply rejection.

+

KXY

- Operates with ±15 V Supplies

- Excellent Linearity: Maximum Error (X or Y) ±1.0 %

- Wide Input Voltage Range: ±10 V

- Adjustable Scale Factor, K (0.1 nominal)

- Single-Ended Output Referenced to Ground

- Simplified Offset Adjust Circuitry

10

8.0

6.0

4.0

2.0

0

- 2.0

- 4.0

- 6.0 - 8.0

-10

-10

VO, OUTPUT VOLTAGE (V)

- Frequency Response (3.0 dB Small–Signal): 1.0 MHz

- Power Supply Sensitivity: 30 mV/V typical

# LINEAR FOUR–QUADRANT **MULTIPLIER INTEGRATED** CIRCUIT

# SEMICONDUCTOR **TECHNICAL DATA**

P SUFFIX PLASTIC PACKAGE CASE 648C

# **ORDERING INFORMATION**

| Device  | Tested Operating<br>Temperature Range | Package     |

|---------|---------------------------------------|-------------|

| MC1494P | $T_A = 0^\circ$ to + 70°C             | Plastic DIP |

k = 10

0

2.0

#### **MAXIMUM RATINGS** ( $T_A = + 25^{\circ}C$ , unless otherwise noted.)

| Rating                                                                                                | Symbol                               | Value                                                | Unit       |

|-------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------|------------|

| Power Supply Voltages                                                                                 | ± V                                  | ± 18                                                 | Vdc        |

| Differential Input Signal                                                                             |                                      | $\pm  6 + I_1 R_Y  < 30$<br>$\pm  6 + I_1 R_X  < 30$ | Vdc        |

| Common Mode Input Voltage<br>$V_{CMY} = V_9 = V_6$<br>$V_{CMX} = V_{10} = V_{13}$                     | V <sub>CMY</sub><br>V <sub>CMX</sub> | ±11.5<br>±11.5                                       | Vdc        |

| Power Dissipation (Package Limitation)<br>$T_A = + 25^{\circ}C$<br>Derate above $T_A = + 25^{\circ}C$ | Ρ <sub>D</sub><br>1/θ <sub>JA</sub>  | 1.25<br>20                                           | W<br>mW/°C |

| Operating Temperature Range                                                                           | T <sub>A</sub>                       | 0 to +70                                             | °C         |

| Storage Temperature Range                                                                             | T <sub>stg</sub>                     | - 65 to +150                                         | °C         |

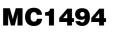

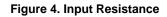

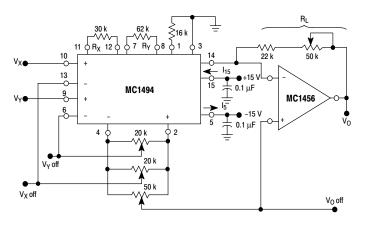

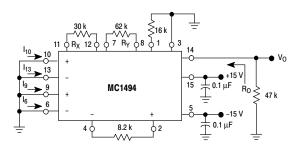

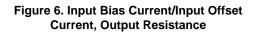

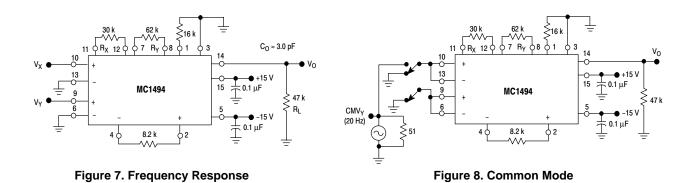

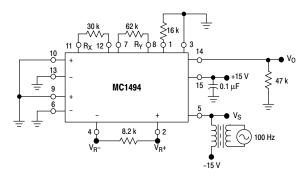

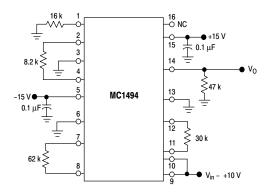

**ELECTRICAL CHARACTERISTICS** ( $\pm$ V =  $\pm$ 15 V, T<sub>A</sub> = + 25°C, R1 = 16 kΩ, R<sub>X</sub> = 30 kΩ, R<sub>Y</sub> = 62 kΩ, R<sub>L</sub> = 47 kΩ, unless otherwise noted.) Figure Symbol Characteristics Min Typ Max Unit 3 % Linearity E<sub>RX</sub> or E<sub>RY</sub> Output error in percent of full scale  $\begin{array}{l} -10 \ V <\!V_X < +10 \ V \ (V_Y = \pm 10 \ V) \\ -10 \ V <\!V_Y < +10 \ V \ (V_X = \pm 10 \ V) \end{array}$  $T_A = +25^{\circ}C$ \_ ±0.5  $\pm 1.0$  $T_A = T_{high}$  or  $T_{low}$  (Note 1) ±1.3 \_ 4, 5, 6 Input Voltage Range ( $V_X = V_Y = V_{in}$ ) Vin ±10 V<sub>pk</sub> \_ R<sub>in</sub> Resistance (X or Y Input) 300 \_ MΩ Offset Voltage (X Input) (Note 1) 2.5 V 0.2 |V<sub>iox</sub>| \_ (Y Input) (Note 1) 0.8 2.5 |V<sub>iov</sub>| \_ **Bias Current** (X or Y Input) \_ 1.0 2.5 μA Ιb (X or Y Input) Offset Current  $|I_{io}|$ \_ 50 400 nA Output 5, 6 Voltage Swing Capability ±10  $V_{O}$ \_ V<sub>pk</sub> \_ Impedance 850 \_ kΩ  $R_{O}$ \_ Offset Voltage (Note 1) \_ 2.5 V |Voo| 1.2 Offset Current (Note 1) \_ 25 52 μΑ  $||_{OO}|$ Temperature Stability (Drift) \_  $T_A = T_{high}$  to  $T_{low}$ mV/°C |TCV<sub>OO</sub>| 1.3 Output Offset (X = 0, Y = 0)\_ \_ Voltage TCloo nA/°C \_ 27 \_ Current |TCV<sub>iox</sub>| \_ 0.3 \_ mV/°C X Input Offset (Y = 0) TCV<sub>ioy</sub> \_ 1.5 \_ Y Input Offset (X = 0) TCK %/°C \_ 0.07 \_ Scale Factor TCE 0.09 \_ Total DC Accuracy Drift (X = 10, Y = 10) Dynamic Response 7 Small Signal (3.0 dB) BW<sub>3dB</sub>(X) 0.8 MHz \_ \_ BW<sub>3dB (Y)</sub> \_ 1.0 \_ Power Bandwidth (47 k)  $\mathsf{P}_{\mathsf{BW}}$ 440 kHz \_ \_ 3° Relative Phase Shift 240 \_ fφ \_ \_ 1% Absolute Error fθ \_ 30 Common Mode 8

**NOTE:** 1. Offsets can be adjusted to zero with external potentiomers.  $T_{High} = +70^{\circ}C$ ,  $T_{Low} = 0^{\circ}C$

Input Swing

Power Supply

Sensitivity

Positive/Negative

**Quiescent Power Dissipation**

Regulated Offset Adjust Voltages

Temperature Coefficient (V<sub>R</sub>+ or V<sub>R</sub>-)

Power Supply Sensitivity (V<sub>R</sub>+ or V<sub>R</sub>-)

Current

Gain

9

9

(X or Y)

(X or Y)

CMV

A<sub>CM</sub>

l<sub>d</sub>+

$I_d$ -

$P_{D}$

S+

S–

V<sub>R</sub>+, V<sub>R</sub>-TCV<sub>R</sub>

$S_R$ +,  $S_R$ -

±10.5

\_

\_

\_

\_

\_

\_

3.5

\_

- 65

6.0

6.5

185

13

30

4.3

0.03

0.6

V<sub>pk</sub> dB

mAdc

mW

mV/V

Vdc

mV/°C

mV/V

\_

\_

12

12

350

100

200

5.0

\_

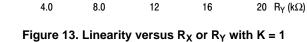

Figure 3. Linearity

Figure 5. Offset Voltages, Gain

Figure 9. Power Supply Sensitivity

Figure 10. Burn-In

Figure 14. Linearity versus  $R_X$  or  $R_Y$  with K = 1/10

80

100

$R_{Y}(k\Omega)$

60

40

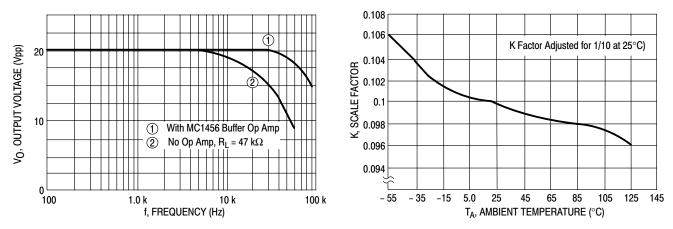

Figure 15. Large Signal Voltage versus Frequency

Figure 16. Scale Factor (K) versus Temperature

# **CIRCUIT DESCRIPTION**

#### Introduction

The MC1494 is a monolithic, four-quadrant multiplier that operates on the principle of variable transconductance. It features a single-ended current output referenced to ground and provides two complementary regulated voltages for use with the offset adjust circuits to virtually eliminate sensitivity of the offset voltage nulls to changes in supply voltages.

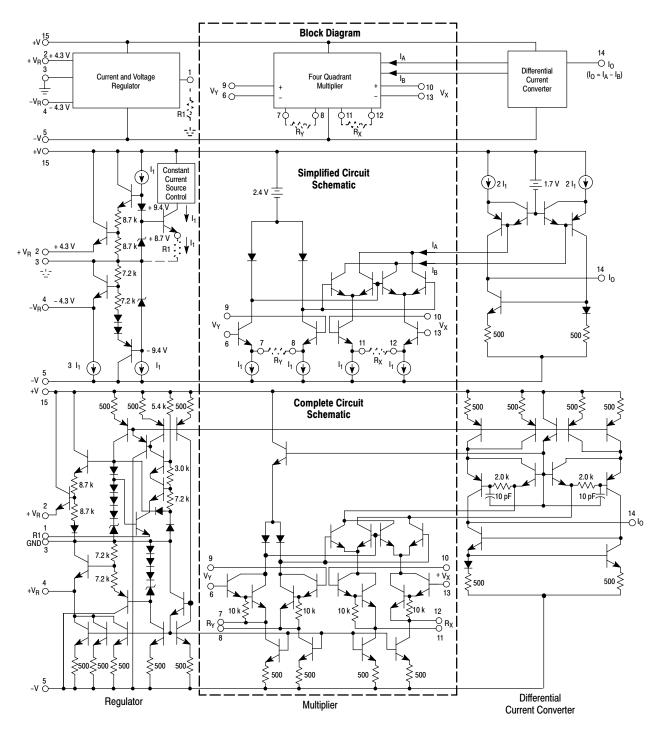

As shown in Figure 17, the MC1494 consists of a multiplier proper and associated peripheral circuitry to provide these features.

#### Regulator

The regulator biases the entire MC1494 circuit making it essentially independent of supply variation. It also provides two convenient regulated supply voltages which can be used in the offset adjust circuitry. The regulated output voltage at Pin 2 is approximately + 4.3 V, while the regulated voltage at Pin 4 is approximately – 4.3 V. For optimum temperature stability of these regulated voltages, it is recommended that  $|I_2| = |I_4| = 1.0$  mA (equivalent load of 8.6 k $\Omega$ ). As will be shown later, there will normally be two 20 k $\Omega$ potentiometers and one 50 k $\Omega$  potentiometer connected between Pins 2 and 4.

The regulator also establishes a constant current reference that controls all of the constant current sources in the MC1494. Note that all current sources are related to current I<sub>1</sub> which is determined by R1. For best temperatures performance, R1 should be 16 k $\Omega$  so that I<sub>1</sub>  $\approx$  0.5 mA for all applications.

#### Multiplier

The multiplier section of the MC1494 (center section of Figure 17) is nearly identical to the MC1495 and is discussed in detail in Application Note AN489, *Analysis and Basic Operation of the MC1495*. The result of this analysis is that the differential output current of the multiplier is given by:

$$I_{A} - I_{B} = \Delta I \approx -\frac{2V_{X}V_{Y}}{R_{X}R_{Y}I_{1}}$$

Therefore, the output is proportional to the product of the two input voltages.

# **Differential Current Converter**

This portion of the circuitry converts the differential output current  $(I_A - I_B)$  of the multiplier to a single–ended output current  $(I_O)$ ;  $I_O = I_A - I_B$

or

$$I_0 = \frac{2V_X V_Y}{R_X R_Y I_1}$$

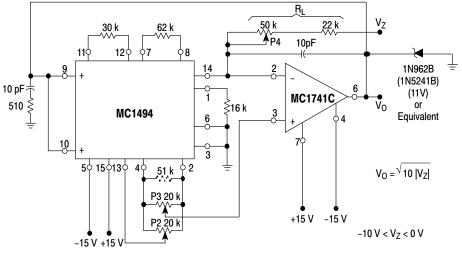

The output current can be easily converted to an output voltage by placing a load resistor  $R_L$  from the output (Pin 14) to ground (Figure 19) or by using an op amp as a current-to-voltage converter (Figure 18). The result in both circuits is that the output voltage is given by:

$$V_{O} = \frac{2R_{L}V_{X}V_{Y}}{R_{X}R_{Y}I_{1}} = KV_{X}V_{Y}$$

where, K (scale factor) =  $\frac{2R_L}{R_X R_Y I}$

# DC OPERATION

#### Selection of External Components

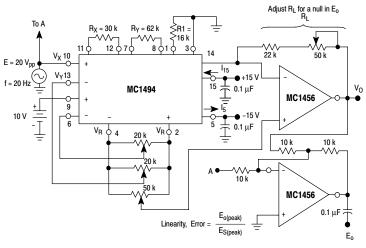

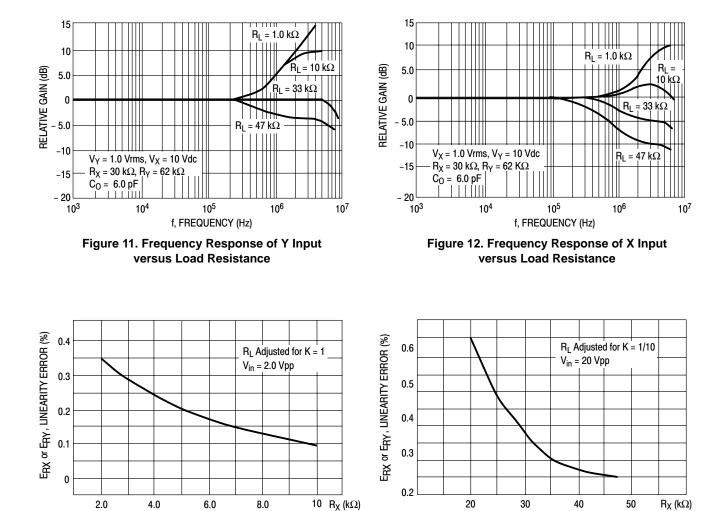

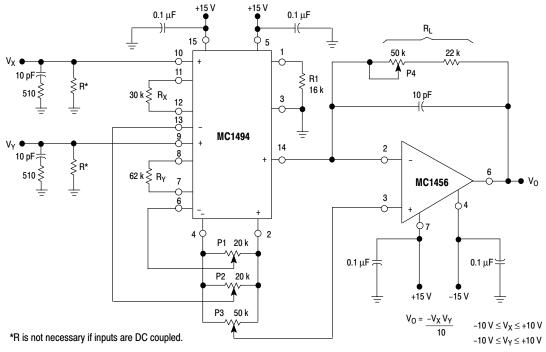

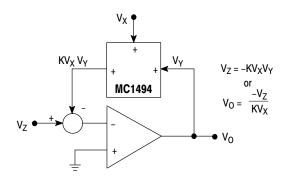

For low frequency operation the circuit of Figure 18 is recommended. For this circuit,  $R_X=30~k\Omega,~R_Y=62~k\Omega,~R1=16~k\Omega$  and, hence,  $I_1\approx 0.5~mA$ . Therefore, to set the scale factor (K) equal to 1/10, the value of  $R_L$  can be calculated to be:

$$K = \frac{1}{10} = \frac{2R_L}{R_X R_Y I_1}$$

or  $R_L = \frac{R_X R_Y I_1}{(2) (10)} = \frac{(30 \text{ k}) (62 \text{ k}) (0.5 \text{ mA})}{20}$

$R_L = 46.5 \text{ k}$

Thus, a reasonable accuracy in scale factor can be achieved by making  $R_L$  a fixed 47 k $\Omega$  resistor. However, if it is desired that the scale factor be exact,  $R_L$  can be comprised of a fixed resistor and a potentiometer as shown in Figure 18.

Figure 17. Internal Schematic

(Recommended External Circuitry is Depicted within Dotted Lines)

Figure 18. Typical Multiplier Connection

It should be pointed out that there is nothing magic about setting the scale factor to 1/10. This is merely a convenient factor to use if the  $V_X$  and  $V_Y$  input voltages are expected to be large, say ±10 V. Obviously with  $V_X = V_Y = 10$  V and a scale factor of unity, the device could not hope to provide a 100 V output, so the scale factor is set to 1/10 and provides an output scaled down by a factor of ten. For many applications it may be desirable to set K = 1/2 or K = 1 or even K = 100. This can be accomplished by adjusting  $R_{X_1}$ ,  $R_Y$  and  $R_L$  appropriately.

The selection of  $R_L$  is arbitrary and can be chosen after resistors  $R_X$  and  $R_Y$  are found. Note in Figure 18 that  $R_Y$  is 62 k $\Omega$  while  $R_X$  is 30 k $\Omega$ . The reason for this is that the "Y" side of the multiplier exhibits a second order nonlinearity whereas the "X" side exhibits a simple nonlinearity. By making the  $R_Y$  resistor approximately twice the value of the  $R_X$  resistor, the linearity on both the "X" and "Y" sides are made equal. The selection of the  $R_X$  and  $R_Y$  resistor values is dependent upon the expected amplitude of  $V_X$  and  $V_Y$ inputs. To maintain a specified linearity, resistors  $R_X$  and  $R_Y$ should be selected according to the following equations:

$R_X \ge 3 V_X$  (max) in k $\Omega$  when  $V_X$  is in Volts,

$R_{Y} \ge 6 V_{Y} (max)$  in  $k\Omega$  when  $V_{Y}$  is in Volts.

For example, if the maximum input on the "X" side is  $\pm 1.0$  V, resistor R<sub>X</sub> can be selected to be 3.0 k $\Omega$ . If the maximum input on the "Y" side is also  $\pm 1.0$  V, then resistor R<sub>Y</sub> can be selected to be 6.0 k $\Omega$  (6.2 k $\Omega$  nominal value). If a scale factor of K = 10 is desired, the load resistor is found to be 47 k $\Omega$ . In this example, the multiplier provides a gain of 20 dB.

#### **Operational Amplifier Selection**

The operational amplifier connection in Figure 18 is a simple but extremely accurate current-to-voltage

converter. The output current of the multiplier flows through the feedback resistor  $R_L$  to provide a low impedance output voltage from the op amp. Since the offset current and bias currents of the op amp will cause errors in the output voltage, particularly with temperature, one with very low bias and offset currents is recommended. The MC1456 or MC1741 are excellent choices for this application.

Since the MC1494 is capable of operation at much higher frequencies than the op amp, the frequency characteristics of the circuit in Figure 18 will be primarily dependent upon the operational amplifier.

### Stability

The current-to-voltage converter mode is a most demanding application for an operational amplifier. Loop gain is at its maximum and the feedback resistor in conjunction with stray or input capacitance at the multiplier output adds additional phase shift. It may therefore be necessary to add (particularly in the case of internally compensated op amps) a small feedback capacitor to reduce loop gain at the higher frequencies. A value of 10 pF in parallel with  $R_L$  should be adequate to insure stability over production and temperature variations, etc.

An externally compensated op amp might be employed using slightly heavier compensation than that recommended for unity–gain operation.

### Offset Adjustment

The noninverting input of the op amp provides a convenient point to adjust the output offset voltage. By connecting this point to the wiper arm of a potentiometer (P3), the output offset voltage can be adjusted to zero (see Offset and Scale Factor Adjustment Procedure).

The input offset adjustment potentiometers, P1 and P2 will be necessary for most applications where it is desirable to take advantage of the multiplier's excellent linearity characteristics. Depending upon the particular application, some of the potentiometers can be omitted (see Figures 19, 21, 24, 26 and 27).

# **Offset and Scale Factor Adjustment Procedure**

The adjustment procedure for the circuit of Figure 18 is:

- A. X Input Offset

- 1. Connect oscillator (1.0 kHz, 5.0 Vpp sinewave) to the "Y" input (Pin 9).

- 2. Connect "X" input (Pin 10) to ground.

- 3. Adjust X–offset potentiometer, P2 for an AC null at the output.

- B. Y Input Offset

- 1. Connect oscillator (1.0 kHz, 5.0 Vpp sinewave) to the "X" input (Pin 10).

- 2. Connect "Y" input (Pin 9) to ground.

- 3. Adjust Y–offset potentiometer, P1 for an AC null at the output.

- C. Output Offset

- 1. Connect both "X" and "Y" inputs to ground.

- 2. Adjust output offset potentiometer, P3 until the output voltage  $V_{O}$  is 0 Vdc.

- D. Scale Factor

- 1. Apply +10 Vdc to both the "X" and "Y" inputs.

- 2. Adjust P4 to achieve -10 V at the output.

- 3. Apply -10 Vdc to both "X" and "Y" inputs and check for V<sub>O</sub> = -10 V.

- E. Repeat steps A through D as necessary.

The ability to accurately adjust the MC1494 is dependent on the offset adjust potentiometers. Potentiometers should be of the "infinite" resolution type rather than wirewound. Fine adjustments in balanced–modulator applications may require two potentiometers to provide "coarse" and "fine" adjustment. Potentiometers should have low temperature coefficients and be free from backlash.

# **Temperature Stability**

While the MC1494 provides excellent performance in itself, overall performance depends to a large degree on the quality of the external components. Previous discussion shows the direct dependence on  $R_X$ ,  $R_Y$  and  $R_L$  and indirect dependence on R1 (through I<sub>1</sub>). Any circuit subjected to temperature variations should be evaluated with these effects in mind.

# **Bias Currents**

The MC1494 multiplier, like most linear ICs, requires a DC bias current into its input terminals. The device cannot be capacitively coupled at the input without regard for this bias current. If inputs  $V_X$  and  $V_Y$  are able to supply the small bias current ( $\approx 0.5 \,\mu$ A) resistors R can be omitted (see Figure 18). If the MC1494 is used in an AC mode of operation and capacitive coupling is used the value of resistor R can be any reasonable value up to 100 k $\Omega$ . For minimum noise and optimum temperature performance, the value of resistor R should be as low as practical.

## **Parasitic Oscillation**

When long leads are used on the inputs, oscillation may occur. In this event, an RC parasitic suppression network similar to the ones shown in Figure 18 should be connected directly to each input using short leads. The purpose of the network is to reduce the "Q" of the source–tuned circuits which cause the oscillation.

Inability to adjust the circuit to within the specified accuracy may be an indication of oscillation.

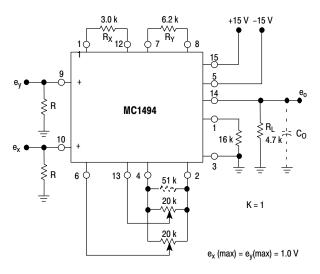

# AC OPERATION

# General

For AC operation, such as balanced modulation, frequency doubler, AGC, etc., the op amp will usually be omitted as well as the output offset adjust potentiometer. The output offset adjust potentiometer is omitted since the output will normally be AC coupled and the DC voltage at the output is of no concern providing it is close enough to zero volts that it will not cause clipping in the output waveform. Figure 19 shows a typical AC multiplier circuit with a scale factor  $K \approx 1$ . Again, resistor  $R_X$  and  $R_Y$  are chosen as outlined in the previous section, with  $R_L$  chosen to provide the required scale factor.

Figure 19. Wideband Multiplier

The offset voltage then existing at the output will be equal to the offset current times the load resistance. The output offset current of the MC1494 is typically 17  $\mu$ A and 35  $\mu$ A maximum. Thus, the maximum output offset would be about 160 mV.

#### Bandwidth

The bandwidth of the MC1494 is primarily determined by two factors. First, the dominant pole will be determined by the load resistor and the stray capacitance at the output terminal. For the circuit shown in Figure 19, assuming a total output capacitance ( $C_O$ ) of 10 pF, the 3.0 dB bandwidth would be approximately 3.4 MHz. If the load resistor were 47 k $\Omega$ , the bandwidth would be approximately 340 kHz.

Secondly, a "zero" is present in the frequency response characteristic for both the "X" and "Y" inputs which causes the output signal to rise in amplitude at a 6.0 dB/octave slope at frequencies beyond the breakpoint of the "zero". The "zero" is caused by the parasitic and substrate capacitance which is related to resistors R<sub>X</sub> and R<sub>Y</sub> and the transistors associated with them. The effect of these transmission "zeros" is seen in Figures 11 and 12. The reason for this increase in gain is due to the bypassing of R<sub>X</sub> and R<sub>Y</sub> at high frequencies. Since the Ry resistor is approximately twice the value of the R<sub>X</sub> resistor, the zero associated with the "Y" input will occur at approximately one octave below the zero associated with "X" input. For  $R_X$  = 30 k $\Omega$  and  $R_Y$  = 62 k $\Omega$ the zeros occur at 1.5 MHz for the "X" input and 700 kHz for the "Y" input. These two measured breakpoints correspond to a shunt capacitance of about 3.5 pF. Thus, for the circuit of Figure 19, the "X" input zero and "Y" input zero will be at approximately 15 MHz and 7.0 MHz respectively.

It should be noted that the MC1494 multiplies in the time domain, hence, its frequency response is found by means of complex convolution in the frequency (Laplace) domain. This means that if the "X" input does not involve a frequency, it is not necessary to consider the "X" side frequency response in the output product. Likewise, for the "Y" side. Thus, for applications such as a wideband linear AGC amplifier which has a DC voltage as one input, the multiplier frequency response has one zero and one pole. For applications which involve an AC voltage on both the "X" and "Y" side such as a balanced modulator, the product voltage response will have two zeros and one pole, hence, peaking may be present in the output.

From this brief discussion, it is evident that for AC applications; (1) the value of resistors  $R_X$ ,  $R_Y$  and  $R_L$  should be kept as small as possible to achieve maximum frequency response, and (2) it is possible to select a load resistor  $R_L$  such that the dominant pole ( $R_L$ ,  $C_O$ ) cancels the input zero ( $R_X$ , 3.5 pF or  $R_Y$ , 3.5 pF) to give a flat amplitude characteristic with frequency. This is shown in Figures 11 and 12. Examination of the frequency characteristics of the "X" and "Y" inputs will demonstrate that for wideband

amplifier applications, the best tradeoff with frequency response and gain is achieved by using the "Y" input for the AC signal.

For AC applications requiring bandwidths greater than those specified for the MC1494, two other devices are recommended. For modulator–demodulator applications, the MC1496 may be used up to 100 MHz. For wideband multiplier applications, the MC1495 (using small collector loads and AC coupling) can be used.

#### Slew-Rate

The MC1494 multiplier is not slew-rate limited in the ordinary sense that an op amp is. Since all the signals in the multiplier are currents and not voltages, there is no charging and discharging of stray capacitors and thus no limitations beyond the normal device limitations. However, it should be noted that the quiescent current in the output transistors is 0.5 mA and thus the maximum rate of change of the output voltage is limited by the output load capacitance by the simple equation:

Slew Rate

$$\frac{\Delta V_O}{\Delta T} = \frac{I_O}{C}$$

Thus, if C<sub>O</sub> is 10 pF, the maximum slew rate would be:

$$\frac{\Delta V_{O}}{\Delta T} = \frac{0.5 \times 10^{-3}}{10 \times 10^{-12}} = 50 \text{ V/}\mu\text{s}$$

This can be improved, if necessary, by the addition of an emitter–follower or other type of buffer.

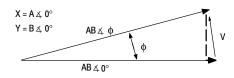

#### Phase Vector Error

All multipliers are subject to an error which is known as the phase vector error. This error is a phase error only and does not contribute an amplitude error per se. The phase vector error is best explained by an example. If the "X" input is described in vector notation as;

Х= А Ҳ 0°

and the "Y" input is described as;

Y= В ≰ 0°

then the output product would be expected to be;  $V_0 = AB \measuredangle 0^\circ$  (see Figure 20)

However, due to a relative phase shift between the "X" and "Y" channels, the output product will be given by:

$$V_{O} = AB \measuredangle \phi$$

Notice that the magnitude is correct but the phase angle of the product is in error. The vector (V) associated with this error is the "phase vector error". The startling fact about the phase vector error is that it occurs and accumulates much more rapidly than the amplitude error associated with frequency response. In fact, a relative phase shift of only 0.57° will result in a 1% phase vector error. For most applications, this error is meaningless. If phase of the output product is not important, then neither is the phase vector error. If phase is important, such as in the case of double sideband modulation or

demodulation, then a 1% phase vector error will represent a 1% amplitude error a the phase angle of interest.

Figure 20. Phase Vector Error

# **Circuit Layout**

If wideband operation is desired, careful circuit layout must be observed. Stray capacitance across  $R_X$  and  $R_Y$  should be avoided to minimize peaking (caused by a zero created by the parallel RC circuit).

# DC APPLICATIONS

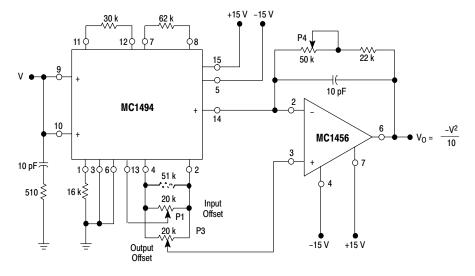

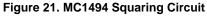

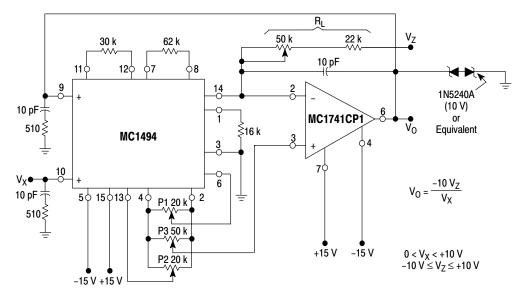

#### **Squaring Circuit**

If the two inputs are connected together, the resultant function is squaring:

$$V_{O} = KV^{2}$$

where K is the scale factor (see Figure 21).

However, a more careful look at the multiplier's defining equation will provide some useful information. The output voltage, without initial offset adjustments is given by:

$$V_{O} = K(V_{X} + V_{iox} - V_{X off}) (V_{Y} + V_{ioy} - V_{Y off}) + V_{OO}$$

(Refer to "Definitions" section for an explanation of terms.)

With

$$V_X = V_Y = V$$

(squaring) and defining;

$$\begin{aligned} & \in_{x} = V_{iox} - V_{x} \text{ (off)} \\ & \in_{y} = V_{ioy} - V_{y} \text{ (off)} \end{aligned}$$

The output voltage equation becomes:

$$V_{O} = KV_{x}^{2} + KV_{x} (\in_{x} + \in_{y}) + K \in_{x} \in_{y} + V_{OO} \end{aligned}$$

This shows that all error terms can be eliminated with only three adjustment potentiometers, eliminating one of the input offset adjustments. For instance, if the "X" input offset adjustment is eliminated,  $\in_x$  is determined by the internal offset (V<sub>iox</sub>) but  $\in_y$  is adjustable to the extent that the ( $\in_x + \in_y$ ) term can be zeroed. Then the output offset adjustment is used to adjust the V<sub>oo</sub> term and thus zero the remaining error terms. An AC procedure for nulling with three adjustments is:

- A. AC Procedure:

- 1. Connect oscillator (1.0 kHz, 15 Vpp) to input.

- 2. Monitor output at 2.0 kHz with tuned voltmeter and adjust P4 for desired gain ( Be sure to peak response of voltmeter).

- 3. Tune voltmeter to 1.0 kHz and adjust P1 for a minimum output voltage.

- 4. Ground input and adjust P3 (output offset) for 0 Vdc out.

- 5. Repeat steps 1 through 4 as necessary.

- B. DC Procedure:

- 1. Set  $V_X = V_Y = 0$  V and adjust P3 (output offset potentiometer) such that  $V_O = 0$  Vdc.

- 2. Set  $V_X = V_Y = 1.0$  V and adjust P1 (Y input offset potentiometer) such that the output voltage is -0.100 V.

- 3. Set  $V_X = V_Y = 10$  Vdc and adjust P4 (load resistor) such that the output voltage is -10 V.

- 4. Set  $V_X = V_Y = -10$  Vdc and check that  $V_O = -10$  V.

- 5. Repeat steps 1 through 4 as necessary.

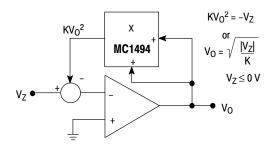

#### Divide

Divide circuits warrant a special discussion as a result of their special problems. Classic feedback theory teaches that if a multiplier is used as a feedback element in an operational amplifier circuit, the divide function results. Figure 22 illustrates the theoretical simplicity of such an approach and a practical realization is shown in Figure 23.

The characteristic "failure" mode of the divide circuit is latch–up. One way it can occur is if  $V_X$  is allowed to go negative, or in some cases, if  $V_X$  approaches zero.

Figure 22 illustrates why this is so. For  $V_X > 0$  the transfer function through the multiplier is noninverting. Its output is fed to the inverting input of the op amp Thus, operation is in the negative feedback mode and the circuit is DC stable.

Figure 22. Basic Divide Circuit Using Multiplier

Should  $V_X$  change polarity, the transfer function through the multiplier becomes inverting, the amplifier has positive feedback and latch–up results. The problem resulting from  $V_X$  being near zero is a result of the transfer through the multiplier being near zero. The op amp is then operating with a very high closed–loop gain and error voltages can thus become effective in causing latch–up.

The other mode of latch–up results from the output voltage of the op amp exceeding the rated common mode input voltage of the multiplier. The input stage of the multiplier becomes saturated, phase reversal results, and the circuit is latched up. The circuit of Figure 23 protects against this happening by clamping the output swing of the op amp to approximately  $\pm$  10.7 V. Five percent tolerance, 10 V zeners are used to assure adequate output swing but still limit the output voltage of the op amp from exceeding the common mode input range of the MC1494.

Setting up the divide circuit for reasonably accurate operation is somewhat different from the procedure for the multiplier itself. One approach, however, is to break the feedback loop, null out the multiplier circuit, and then close the loop.

A simpler approach, since it does not involve breaking the loop (thus making it more practical on a production basis), is:

- 1. Set  $V_Z = 0$  V and adjust the output offset potentiometer (P3) until the output voltage (V<sub>O</sub>) remains at some (not necessarily zero) constant value as  $V_X$  is varied between +1.0 V and +10 V.

- 2. Maintain  $V_Z$  at 0 V, set  $V_X$  at +10 V and adjust the Y input offset potentiometer (P1) until  $V_O = 0$  V.

- 3. With  $V_X = V_Z$ , adjust the X input offset potentiometer (P2) until the output voltage remains at some (not necessarily -10 V) constant value as  $V_Z = V_X$  is varied between +1.0 V and +10 V.

- 4. Maintain  $V_X = V_Z$  and adjust the scale factor potentiometer (R<sub>L</sub>) until the average value of V<sub>O</sub> is -10 V as  $V_Z = V_X$  is varied between +1.0 V and +10 V.

- 5. Repeat steps 1 through 4 as necessary to achieve optimum performance.

Users of the divide circuit should be aware that the accuracy to be expected decreases in direct proportion to the denominator voltage. As a result, if  $V_X$  is set to 10 V and 0.5% accuracy is available, then 5% accuracy can be expected when  $V_X$  is only 1.0 V.

In accordance with an earlier statement,  $V_X$  may have only one polarity (positive) while  $V_Z$  may be either polarity.

Figure 24. Basic Square Root Circuit

#### **Square Root**

A special case of the divide circuit in which the two inputs to the multiplier are connected together results in the square root function as indicated in Figure 24. This circuit too may suffer from latch–up problems similar to those of the divide circuit. Note that only one polarity of input is allowed and diode clamping (see Figure 25) protects against accidental latch–up.

This circuit too, may be adjusted in the closed-loop mode:

- 1. Set  $V_Z = -0.01$  Vdc and adjust P3 (output offset) for  $V_Q = 0.316$  Vdc.

- 2. Set V<sub>Z</sub> to -0.9 Vdc and adjust P2 ("X" adjust) for V<sub>Q</sub> = +3.0 Vdc.

- 3. Set  $V_Z$  to -10 Vdc and adjust P4 (gain adjust) for  $V_Q = +10$  Vdc.

- 4. Steps 1 through 3 may be repeated as necessary to achieve desired accuracy.

**NOTE**: Operation near 0 V input may prove very inaccurate, hence, it may not be possible to adjust  $V_0$  to zero but rather only to within 100 mV to 400 mV of zero.

# **AC APPLICATIONS**

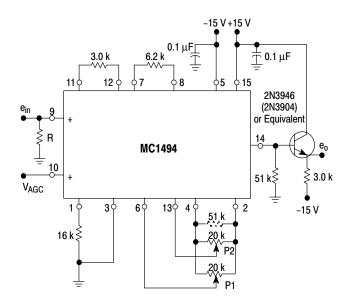

#### Wideband Amplifier with Linear AGC

If one input to the MC1494 is a DC voltage and a signal voltage is applied to the other input, the amplitude of the output signal can be controlled in a linear fashion by varying the DC voltage. Hence, the multiplier can function as a DC coupled, wideband amplifier with linear AGC control.

In addition to the advantage of linear AGC control, the multiplier has three other distinct advantages over most other types of AGC systems. First, the AGC dynamic range is theoretically infinite. This stems from the basic fact that with 0 Vdc applied to the AGC, the output will be zero regardless of the input. In practice, the dynamic range is limited by the ability to adjust the input offset adjust potentiometers. By using cermet multi-turn potentiometers, a dynamic range of 80 dB can be obtained. The second advantage of the multiplier is that variation of the AGC voltage has no effect on the signal handling capability of the signal port, nor does it alter the input impedance of the signal port. This feature is particularly important in AGC systems which are phase sensitive. A third advantage of the multiplier is that the output voltage swing capability and output impedance are unchanged with variations in AGC voltage.

Figure 25. Square Root Circuit

The circuit of Figure 26 demonstrates the linear AGC amplifier. The amplifier can handle 1.0 Vrms and exhibits a gain of approximately 20 dB. It is AGC'd through a 60 dB dynamic range with the application of an AGC voltage from

0 Vdc to 1.0 Vdc. The bandwidth of the amplifier is determined by the load resistor and output stray capacitance. For this reason, an emitter–follower buffer has been added to extend the bandwidth in excess of 1.0 MHz.

Figure 26. Wideband Amplifier with Linear AGC

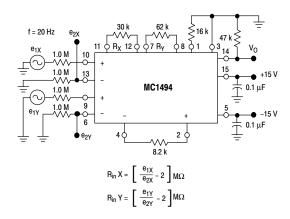

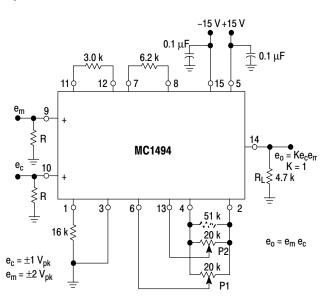

#### **Balanced Modulator**

When two-time variant signals are used as inputs, the resulting output is suppressed-carrier double-sideband modulation. In terms of sinusoidal inputs, this can be seen in the following equation:

$V_{O} = K_{(e_1 \cos \omega_m t)} (e_2 \cos \omega_c t)$

where  $\omega_m$  is the modulation frequency and  $\omega_c$  is the carrier frequency. This equation can be expanded to show the suppressed carrier or balanced modulation:

$$V_{O} = \frac{Ke_{1}e_{2}}{2} \left[ \cos(\omega_{c} + \omega_{m}) t + \cos(\omega_{c} - \omega_{m})t \right]$$

Unlike many modulation schemes, which are nonlinear in nature, the modulation which takes place when using the MC1494 is linear. This means that for two sinusoidal inputs, the output will contain only two frequencies, the sum and difference, as seen in the above equation. There will be no spectrum centered about the second harmonic of the carrier, or any multiple of the carrier. For this reason, the filter requirements of a modulation system are reduced to the minimum. Figure 27 shows the MC1494 configuration to perform this function.

Notice that the resistor values for  $R_X$ ,  $R_Y$  and  $R_L$  have been modified. This has been done primarily to increase the bandwidth by lowering the output impedance of the MC1494 and then lowering  $R_X$  and  $R_Y$  to achieve a gain of 1. The  $e_c$  can be as large as 1.0 V peak and  $e_m$  as high as 2.0 V peak. No output offset adjust is employed since we are interested only in the AC output components.

The input resistors (R) are used to supply bias current to the multiplier inputs as well as provide matching input impedance. The output frequency range of this configuration is determined by the 4.7 k $\Omega$  output impedance and capacitive loading. Assuming a 6.0 pF load, the small–signal bandwidth is 5.5 MHz.

The circuit of Figure 27 will provide at typical carrier rejection of  $\geq$  70 dB from 10 kHz to 1.5 MHz.

Figure 27. Balanced Modulator

The adjustment procedure for this circuit is quite simple.

- 1. Place the carrier signal at Pin 10. With no signal applied to Pin 9, adjust potentiometer P1 such that an AC null is obtained at the output.

- 2. Place a modulation signal at Pin 9. With no signal applied to Pin 10, adjust potentiometer P2 such that an AC null is obtained at the output.

Again, the ability to make careful adjustment of these offsets will be a function of the type of potentiometers used for P1 and P2. Multiple turn cermet type potentiometers are recommended.

#### **Frequency Doubler**

If for Figure 27 both inputs are identical:

$$e_m = e_c = E \cos \omega$$

then the output is given by,

$e_o = e_m e_c = E^2 \cos^2 \omega t$

$$e_0 = \frac{E^2}{2} (1 + \cos 2\omega t)$$

This equation states that the output will consist of a DC term equal to one half the peak voltage squared and the second harmonic of the input frequency. Thus, the circuit acts as a frequency doubler. Two facts about this circuit are worthy of note. First, the second harmonic of the input frequency is the only frequency appearing at the output. The fundamental does not appear. Second, if the input is sinusoidal, the output will be sinusoidal and requires *no* filtering.

The circuit of Figure 27 can be used as a frequency doubler with input frequencies in excess of 2.0 MHz.

# **Amplitude Modulator**

The circuit of Figure 27 is also easily used as an amplitude modulator. This is accomplished by simply varying the input offset adjust potentiometer (P1) associated with the modulation input. This procedure places a DC offset on the modulation input of the multiplier such that the carrier still passes through the multiplier when the modulating signal is zero. The result is amplitude modulation. This is easily seen by examining the basic mathematical expression for amplitude modulation given below. For the case under discussion, with K = 1,

$e_o = (E + E_m \cos \omega_m t) (E_c \cos \omega_c t)$

where E is the DC input offset adjust voltage. This expression can be written as:

$e_o = E_o [1 + M \cos \omega_c t] \cos \omega_c t$

where,  $E_0 = EE_c$

and,  $M = \frac{\tilde{E}_m}{E}$  = modulation index.

This is the standard equation for amplitude modulation. From this, it is easy to see that 100% modulation can be achieved by adjusting the input offset adjust voltage to be exactly equal to the peak value of the modulation  $(E_m)$ . This is done by observing the output waveform and adjusting the input offset potentiometer (P1) until the output exhibits the familiar amplitude modulation waveform.

# Phase Detector

If the circuit of Figure 27 has as its inputs two signals of identical frequency, but having a relative phase shift, the output will be a DC signal which is directly proportional to the cosine of phase difference as well as the double frequency term.

$$\begin{split} & e_c = E_c \ cos \omega_c t \\ & e_m = E_m \ cos(\omega_c t + \phi) \\ & e_o = e_c e_m = E_c E_m \ cos \omega_c t \ cos(\omega_c t + \phi) \\ & \text{or, } e_o = \frac{E_c E_m}{2} \quad [cos \phi + cos(2\omega_c t + \phi)] \end{split}$$

The addition of a simple low pass filter to the output (which eliminates the second cosine term) and return of  $R_L$  to an offset adjustment potentiometer will result in a DC output voltage which is proportional to the cosine of the phase difference. Hence, the circuit functions as a synchronous detector.

# DEFINITION OF SPECIFICATIONS

Because of the unique nature of a multiplier, i.e., two inputs and one output, operating specifications are difficult to define and interpret. Indeed the same specification may be defined in several completely different ways depending upon which manufacturer is doing the defining. In order to clear up some of the mystery, the following definitions and examples are presented.

**Multiplier Transfer Function** – The output of the multiplier may be expressed by the following equation:

$$V_{O} = K[V_{x} \pm V_{iox} - V_{x(off)}] [V_{y} \pm V_{ioy} - V_{y(off)}] \pm V_{OO} (1)$$

where, K = scale factor

$V_{x} = "x"$  input voltage

$V_{y} = "y"$  input voltage

$V_{iox} = "x"$  input offset voltage

$V_{ioy} = "y"$  input offset voltage

$V_{x(off)} = "x"$  input offset adjust voltage

$V_{y(off)} = "y"$  input offset adjust voltage

$V_{OO} =$  output offset voltage

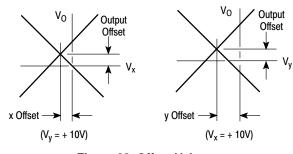

The voltage transfer characteristic below indicates x, y and output offset voltages.

Figure 28. Offset Voltages

**Linearity** – Linearity is defined to be the maximum deviation of output voltage from a straight line transfer function. It is expressed as a percentage of full–scale output and is measured for  $V_x$  and  $V_y$  separately, either using an X–Y plotter (and checking the deviation from a straight line) or by using the method shown in Figure 3. The latter method nulls the output signal with the input signal, resulting in distortion components proportional to the linearity.

Example: 0.35% linearity means

$$V_{O} = \frac{V_x V_y}{10} \pm (0.0035)(10 V)$$

**Input Offset Voltage** – The input offset voltage is defined from Equation (1). It is measured for  $V_x$  and  $V_y$  separately and is defined to be that DC input offset adjust voltage (x or y) that will result in minimum AC output when AC (5.0 Vpp, 1.0 kHz) is applied to the other input (y or x, respectively). From Equation (1) we have:

$$\begin{split} V_O(AC) &= K \; [0 \pm V_{iox} - V_{x(off)}] \; [\text{sin}\omega t] \\ \text{adjust} \; V_{x(off)} \; \text{so that} \; [\pm V_{iox} - V_{x(off)}] = 0. \end{split}$$

**Output Offset Current and Voltage** – Output offset current ( $I_{OO}$ ) is the DC current flowing in the output lead when  $V_x = V_y = 0$  and X and Y offset voltages are adjusted to zero.

Output offset voltage (V<sub>OO</sub>) is:

$$V_{OO} = I_{OO} R_L$$

where  $R_L$  is the load resistance.

**NOTE:** Output offset voltage is defined by many manufacturers with all inputs at zero but without adjusting X and Y offset voltages to zero. Thus, it includes input offset terms, an output offset term and a scale factor term.

**Scale Factor** – Scale factor is the K term in Equation (1). It determines the gain of the multiplier and is expressed approximately by the following equation.

$$K = \frac{2R_L}{R_xR_yl_1}$$

, where  $R_x$  and  $R_y >> \frac{kT}{ql_1}$

and  $l_1$  is the current out of Pin 1.

**Total DC Accuracy** – The total DC accuracy of a multiplier is defined as error in multiplier output with DC ( $\pm$  10 Vdc) applied to both inputs. It is expressed as a percent of full scale. Accuracy is not specified for the MC1494 because error terms can be nulled by the user.

**Temperature Stability (Drift)** – Each term defined above will have a finite drift with temperature. The temperature specifications are obtained by readjusting the multiplier offsets and scale factor at each new temperature (see previous definitions and the adjustment procedure) and noting the change.

Assume inputs are grounded and initial offset voltages have been adjusted to zero. Then output voltage drift is given by:

$$\Delta V_{O} = \pm [K \pm K (TCK) (\Delta T)] [(TCV_{iox}) (\Delta T)]$$

[(TCV\_{iov}) (\Delta T)] \pm (TCV\_{OO}) (\Delta T)

**Total DC Accuracy Drift** – This is the temperature drift in output voltage with 10 V applied to each input. The output is adjusted to 10 V at  $T_A = +25^{\circ}$ C. Assuming initial offset voltages have been adjusted to zero at  $T_A = +25^{\circ}$ C, then:

$V_{O} = [K \pm K (TCK) (\Delta T)] [10 \pm (TCV_{iox}) (\Delta T)]$  $[10 \pm (TCV_{ioy}) (\Delta T)] \pm (TCV_{OO}) (\Delta T)$

**Power Supply Rejection** – Variation in power supply voltages will cause undesired variation of the output voltage. It is measured by superimposing a 1.0 V, 100 Hz signal on each supply ( $\pm 15$  V) with each input grounded. The resulting change in the output is expressed in mV/V.

**Output Voltage Swing** – Output voltage swing capability is the maximum output voltage swing (without clipping) into a resistive load. (Note, output offset is adjusted to zero).

If an op amp is used, the multiplier output becomes a virtual ground – the swing is then determined by the scale factor and the op amp selected.

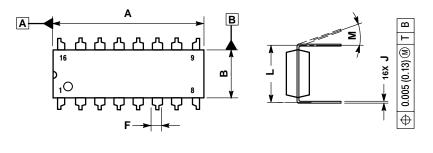

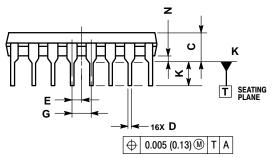

#### **OUTLINE DIMENSIONS**

**P SUFFIX** PLASTIC PACKAGE CASE 648C-04 ISSUE D

NOTES

DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: INCH.

3. DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEI

DIMENSION B DOES NOT INCLUDE MOLD FLASH.

|     | INCHES    |       | MILLIMETERS |       |

|-----|-----------|-------|-------------|-------|

| DIM | MIN       | MAX   | MIN         | MAX   |

| Α   | 0.744     | 0.783 | 18.90       | 19.90 |

| В   | 0.240     | 0.260 | 6.10        | 6.60  |

| С   | 0.145     | 0.185 | 3.69        | 4.69  |

| D   | 0.015     | 0.021 | 0.38        | 0.53  |

| Е   | 0.050 BSC |       | 1.27 BSC    |       |

| F   | 0.040     | 0.70  | 1.02        | 1.78  |

| G   | 0.100 BSC |       | 2.54 BSC    |       |

| J   | 0.008     | 0.015 | 0.20        | 0.38  |

| κ   | 0.115     | 0.135 | 2.92        | 3.43  |

| Г   | 0.300 BSC |       | 7.62 BSC    |       |

| Μ   | 0°        | 10°   | 0°          | 10°   |

| Ν   | 0.015     | 0.040 | 0.39        | 1.01  |

are trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes ON Semiconductor and without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights or the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### PUBLICATION ORDERING INFORMATION

#### NORTH AMERICA Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: ONlit@hibbertco.com Fax Response Line: 303-675-2167 or 800-344-3810 Toll Free USA/Canada

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

EUROPE: LDC for ON Semiconductor - European Support

- German Phone: (+1) 303-308-7140 (Mon-Fri 2:30pm to 7:00pm CET) Email: ONlit-german@hibbertco.com Phone: (+1) 303–308–7141 (Mon–Fri 2:00pm to 7:00pm CET) French

- Email: ONlit-french@hibbertco.com English Phone: (+1) 303-308-7142 (Mon-Fri 12:00pm to 5:00pm GMT)

- Email: ONlit@hibbertco.com

EUROPEAN TOLL-FREE ACCESS\*: 00-800-4422-3781 \*Available from Germany, France, Italy, UK, Ireland

#### **CENTRAL/SOUTH AMERICA:**

Spanish Phone: 303-308-7143 (Mon-Fri 8:00am to 5:00pm MST) Email: ONlit-spanish@hibbertco.com Toll-Free from Mexico: Dial 01-800-288-2872 for Access -

then Dial 866-297-9322

ASIA/PACIFIC: LDC for ON Semiconductor - Asia Support Phone: 1-303-675-2121 (Tue-Fri 9:00am to 1:00pm, Hong Kong Time) Toll Free from Hong Kong & Singapore: 001-800-4422-3781 Email: ONlit-asia@hibbertco.com

JAPAN: ON Semiconductor, Japan Customer Focus Center 4-32-1 Nishi-Gotanda, Shinagawa-ku, Tokyo, Japan 141-0031 Phone: 81-3-5740-2700 Email: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local Sales Representative.