#### Notice: This is not a final specification. Some parametric limits are subject to change.

# 4518 Group

# SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

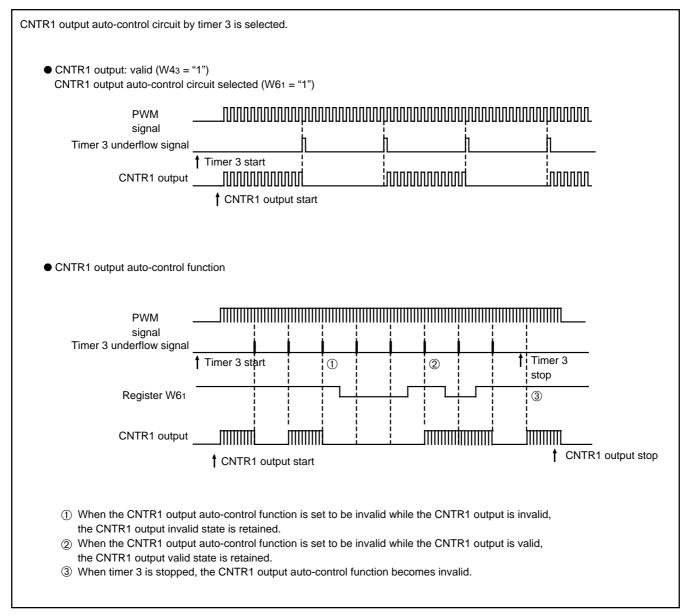

REJ03B0008-0300Z Rev.3.00 2004.07.27

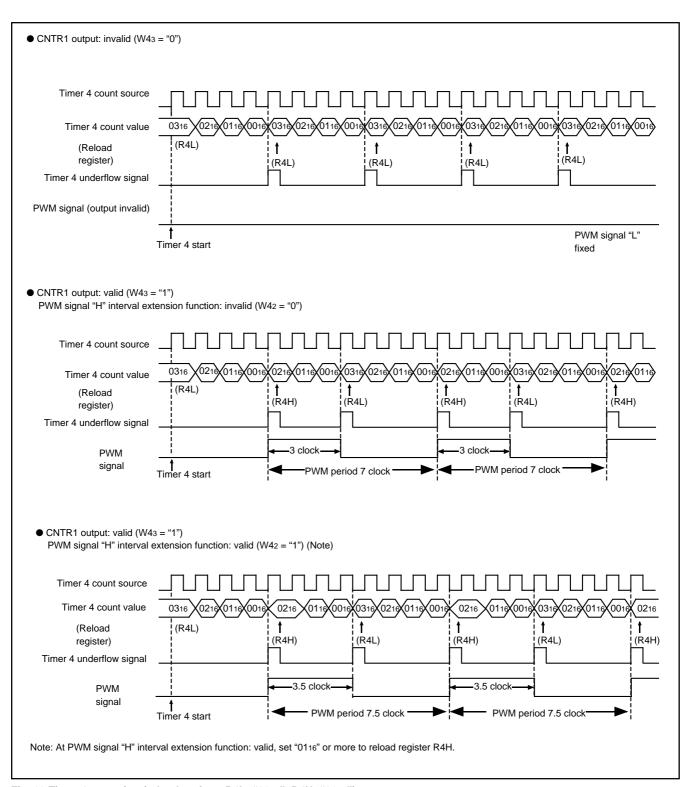

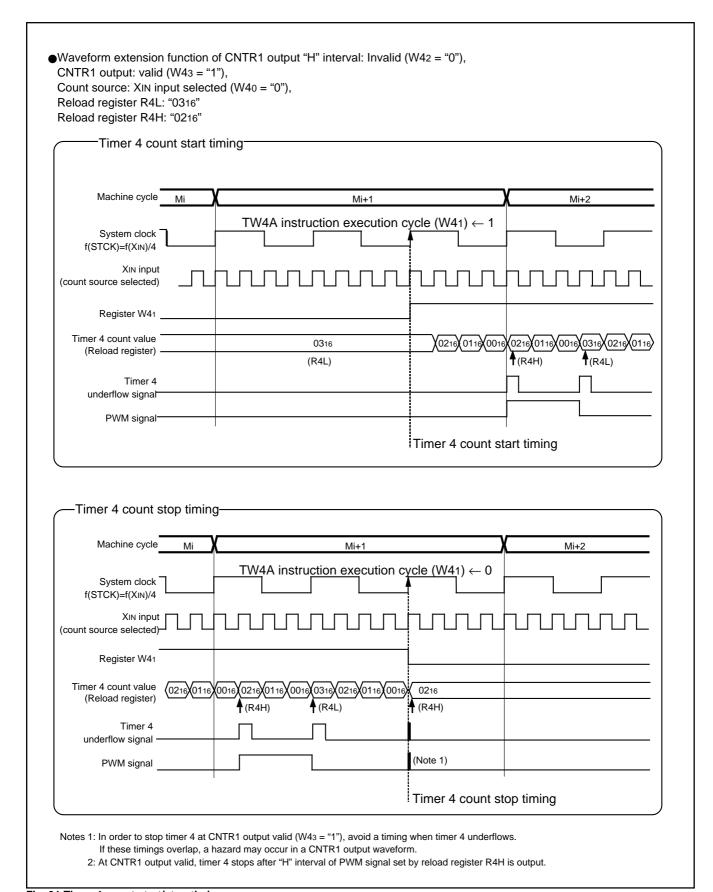

#### **DESCRIPTION**

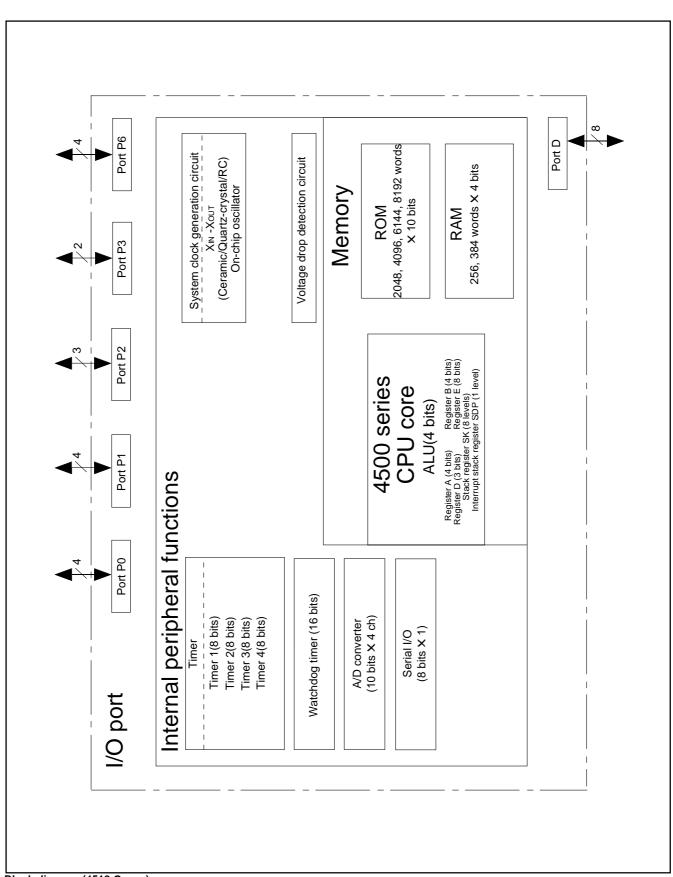

The 4518 Group is a 4-bit single-chip microcomputer designed with CMOS technology. Its CPU is that of the 4500 series using a simple, high-speed instruction set. The computer is equipped with serial I/O, four 8-bit timers (each timer has one or two reload registers), a 10-bit A/D converter, interrupts, and oscillation circuit switch function.

The various microcomputers in the 4518 Group include variations of the built-in memory size as shown in the table below.

#### **FEATURES**

| • | rimers      |                                     |

|---|-------------|-------------------------------------|

|   | Timer 1     | 8-bit timer with a reload register  |

|   | Timer 2     | 8-bit timer with a reload register  |

|   | Timer 3     | 8-bit timer with a reload register  |

|   | Timer 3 8-b | oit timer with two reload registers |

| ●Interrupt 8 sources                                     |

|----------------------------------------------------------|

| ●Key-on wakeup function pins10                           |

| ● Serial I/O                                             |

| ● A/D converter 10-bit successive comparison method, 4ch |

| ■ Voltage drop detection circuit                         |

| Reset occurrence                                         |

| Reset release Typ. 3.7 V (Ta = 25 °C)                    |

| • \A/a talk along the an                                 |

- Watchdog timer

- Clock generating circuit (ceramic resonator/RC oscillation/quartz-crystal oscillation/onchip oscillator)

- ●LED drive directly enabled (port D)

#### **APPLICATION**

Electrical household appliance, consumer electronic products, office automation equipment, etc.

| Part number                | ROM (PROM) size<br>(X 10 bits) | RAM size<br>(X 4 bits) | Package | ROM type      |

|----------------------------|--------------------------------|------------------------|---------|---------------|

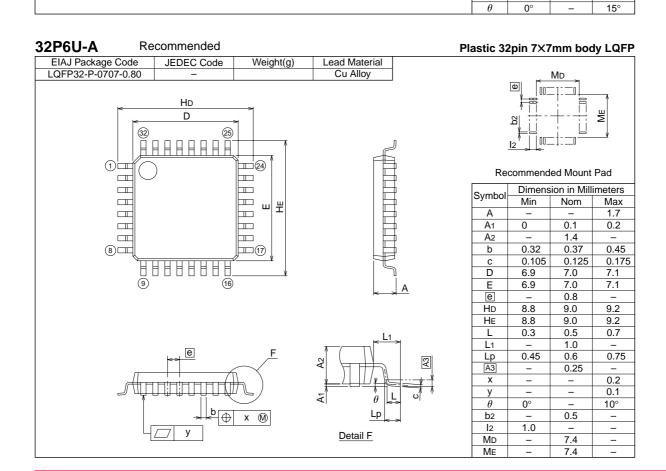

| M34518M2-XXXFP             | 2048 words                     | 256 words              | 32P6U-A | Mask ROM      |

| M34518M2-XXXSP             | 2048 words                     | 256 words              | 32P4B   | Mask ROM      |

| M34518M4-XXXFP             | 4096 words                     | 256 words              | 32P6U-A | Mask ROM      |

| M34518M4-XXXSP             | 4096 words                     | 256 words              | 32P4B   | Mask ROM      |

| M34518M6-XXXFP             | 6144 words                     | 384 words              | 32P6U-A | Mask ROM      |

| M34518M8-XXXFP             | 8192 words                     | 384 words              | 32P6U-A | Mask ROM      |

| M34518E8FP ( <b>Note</b> ) | 8192 words                     | 384 words              | 32P6U-A | One Time PROM |

| M34518E8SP ( <b>Note</b> ) | 8192 words                     | 384 words              | 32P4B   | One Time PROM |

Note: Shipped in blank.

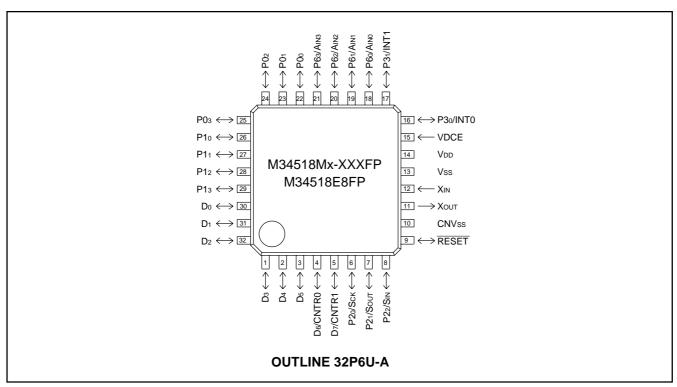

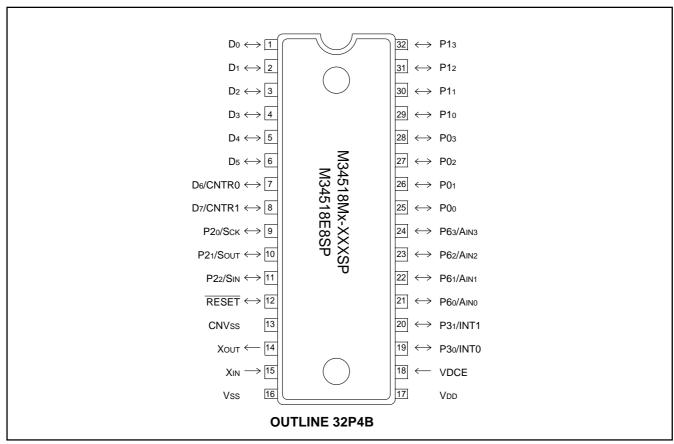

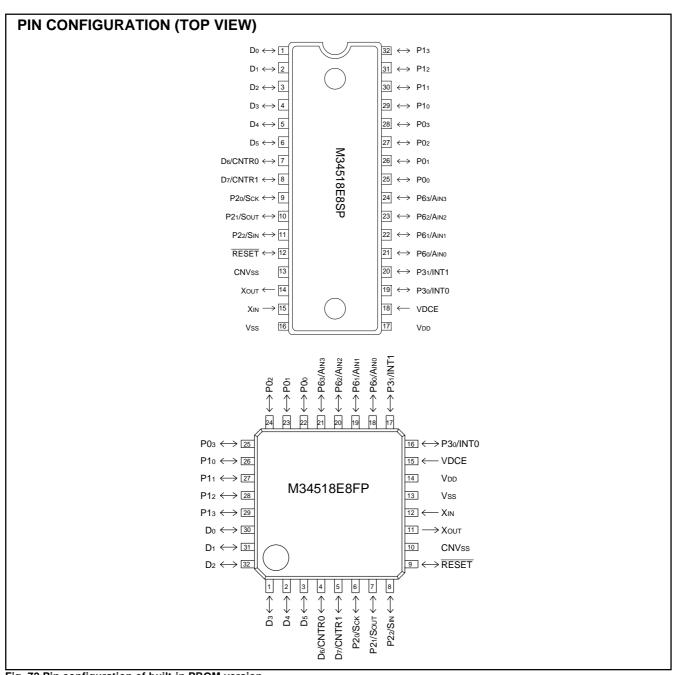

#### **PIN CONFIGURATION**

Pin configuration (top view) (4518 Group)

Pin configuration (top view) (4518 Group)

# **PERFORMANCE OVERVIEW**

| Parameter                          |                  | eter                                           | Function                                                                                                                                   |  |  |

|------------------------------------|------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Number of bas                      | ic instr         | uctions                                        | 148                                                                                                                                        |  |  |

| Minimum instruction execution time |                  |                                                | 0.5 $\mu$ s (at 6.0 MHz oscillation frequency, in XIN through-mode)                                                                        |  |  |

| Memory sizes                       | ROM              | M34518M2                                       | 2048 words X 10 bits                                                                                                                       |  |  |

|                                    |                  | M34518M4                                       | 4096 words X 10 bits                                                                                                                       |  |  |

|                                    |                  | M34518M6                                       | 6144 words X 10 bits                                                                                                                       |  |  |

|                                    |                  | M34518M8/E8                                    | 8192 words X 10 bits                                                                                                                       |  |  |

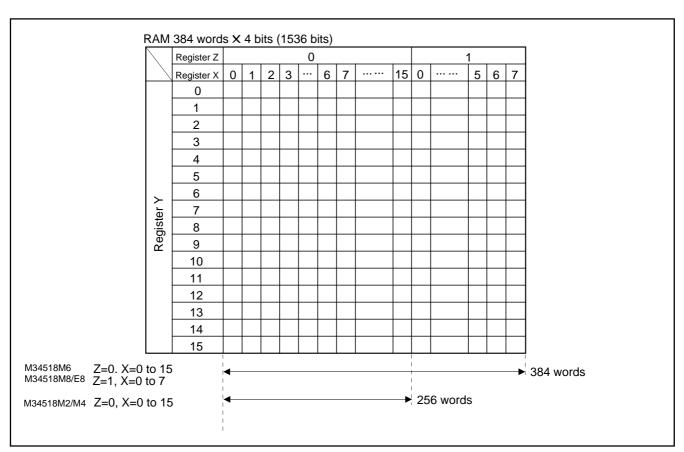

|                                    | RAM              | M34518M2/M4                                    | 256 words X 4 bits                                                                                                                         |  |  |

|                                    |                  | M34518M6/M8/E8                                 | 384 words X 4 bits                                                                                                                         |  |  |

| Input/Output ports                 | D0-D7            | I/O (Input is<br>examined by<br>skip decision) | Eight independent I/O ports; Ports D6 and D7 are also used as CNTR0 and CNTR1, respectively. The output structure is switched by software. |  |  |

|                                    | P00-P            | 03 I/O                                         | 4-bit I/O port; a pull-up function, a key-on wakeup function and output structure can be switched by software.                             |  |  |

|                                    | P10-P            | 13 I/O                                         | 4-bit I/O port; a pull-up function, a key-on wakeup function and output structure can be switched by software.                             |  |  |

|                                    | _                | 22 I/O                                         | 3-bit I/O port; ports P20, P21 and P22 are also used as SCK, SOUT and SIN, respectively.                                                   |  |  |

|                                    |                  | 31 I/O                                         | 2-bit I/O port; ports P30 and P31 are also used as INT0 and INT1, respectively.                                                            |  |  |

|                                    | P60-P            | 63 I/O                                         | 4-bit I/O port; ports P60–P63 are also used as AIN0–AIN3, respectively.                                                                    |  |  |

| Timers                             | rs Timer 1       |                                                | 8-bit timer with a reload register is also used as an event counter.                                                                       |  |  |

|                                    |                  |                                                | Also, this is equipped with a period/pulse width measurement function.                                                                     |  |  |

|                                    | Timer 2          |                                                | 8-bit timer with a reload register.                                                                                                        |  |  |

|                                    | Timer 3          |                                                | 8-bit timer with a reload register is also used as an event counter.                                                                       |  |  |

|                                    | Timer 4          |                                                | 8-bit timer with two reload registers and PWM output function.                                                                             |  |  |

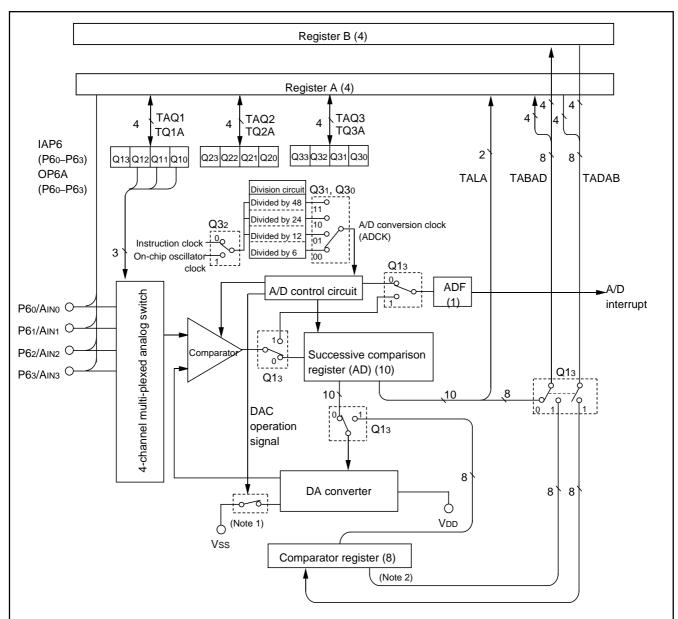

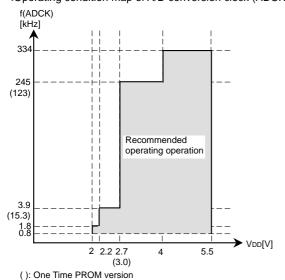

| A/D converter                      |                  |                                                | 10-bit wide X 4 ch, This is equipped with an 8-bit comparator function.                                                                    |  |  |

| Serial I/O                         |                  |                                                | 8-bit X 1                                                                                                                                  |  |  |

| Interrupt                          | Source           | es                                             | 8 (two for external, four for timer, one for A/D, and one for serial I/O)                                                                  |  |  |

|                                    | Nestin           | g                                              | 1 level                                                                                                                                    |  |  |

| Subroutine nes                     | sting            |                                                | 8 levels                                                                                                                                   |  |  |

| Device structu                     | re               |                                                | CMOS silicon gate                                                                                                                          |  |  |

| Package                            |                  |                                                | 32-pin plastic molded LQFP (32P6U-A)/SDIP (32P4B)                                                                                          |  |  |

| Operating tem                      | peratur          | e range                                        | −20 °C to 85 °C                                                                                                                            |  |  |

| Supply voltage                     | Mask             | ROM version                                    | 1.8 V to 5.5 V (It depends on operation source clock, oscillation frequency and operating mode.)                                           |  |  |

|                                    | One T            | me PROM version                                | 2.5 V to 5.5 V (It depends on operation source clock, oscillation frequency and operating mode.)                                           |  |  |

| Power                              | Active           | mode                                           | 2.8 mA (Ta=25 °C, VDD=5V, f(XIN)=6 MHz, f(STCK)=f(XIN), on-chip oscillator stop)                                                           |  |  |

| dissipation                        |                  |                                                | 70 μA (Ta=25 °C, VDD=5V, f(XIN)=32 kHz, f(STCK)=f(XIN), on-chip oscillator stop)                                                           |  |  |

| (typical value)                    |                  |                                                | 150 μA (Ta=25 °C, VDD=5V, on-chip oscillator is used, f(STCK)=f(RING), f(XIN) stop)                                                        |  |  |

|                                    | RAM back-up mode |                                                | 0.1 $\mu$ A (Ta=25 °C, VDD = 5 V, output transistors in the cut-off state)                                                                 |  |  |

**PRELIMINARY**

# **PIN DESCRIPTION**

| Pin             | Name                                                 | Input/Output | Function                                                                                                                                                                                                                                                                                                                                                |

|-----------------|------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD             | Power supply                                         | _            | Connected to a plus power supply.                                                                                                                                                                                                                                                                                                                       |

| Vss             | Ground                                               | _            | Connected to a 0 V power supply.                                                                                                                                                                                                                                                                                                                        |

| CNVss           | CNVss                                                | _            | Connect CNVss to Vss and apply "L" (0V) to CNVss certainly.                                                                                                                                                                                                                                                                                             |

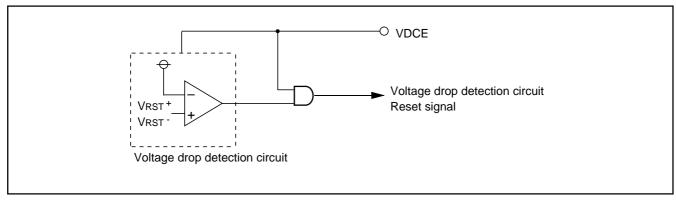

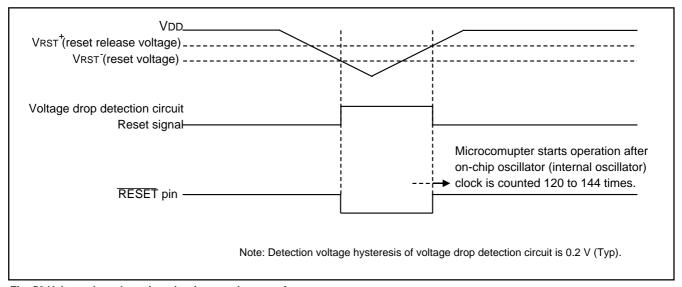

| VDCE            | Voltage drop<br>detection circuit<br>enable          | Input        | This pin is used to operate/stop the voltage drop detection circuit. When "H" level is input to this pin, the circuit starts operating. When "L" level is input to this pin, the circuit stops operating.                                                                                                                                               |

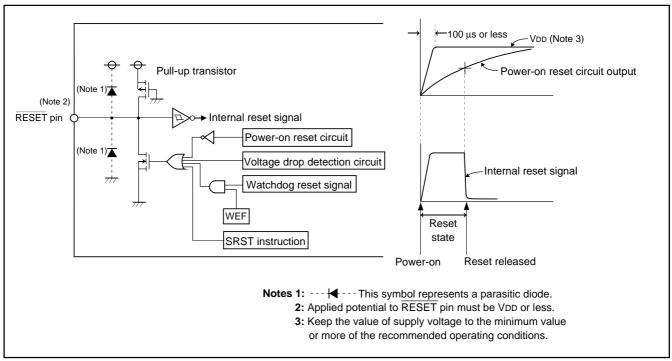

| RESET           | Reset input/output                                   | I/O          | An N-channel open-drain I/O pin for a system reset. When the SRST instruction, watchdog timer, the built-in power-on reset or the voltage drop detection circuit causes the system to be reset, the RESET pin outputs "L" level.                                                                                                                        |

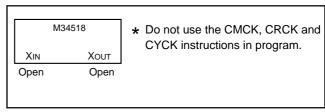

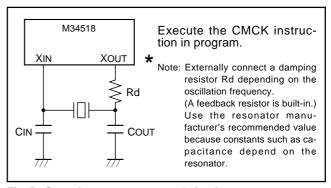

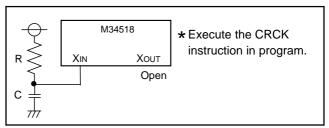

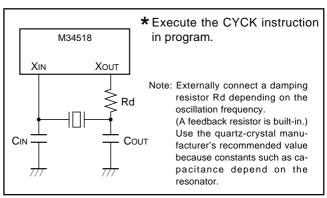

| XIN             | Main clock input                                     | Input        | I/O pins of the main clock generating circuit. When using a ceramic resonator, connect it between pins XIN and XOUT. When using a 32 kHz quartz-crystal oscillator, connect it                                                                                                                                                                          |

| Хоит            | Main clock output                                    | Output       | between pins XIN and XOUT. A feedback resistor is built-in between them. When using the RC oscillation, connect a resistor and a capacitor to XIN, and leave XOUT pin open.                                                                                                                                                                             |

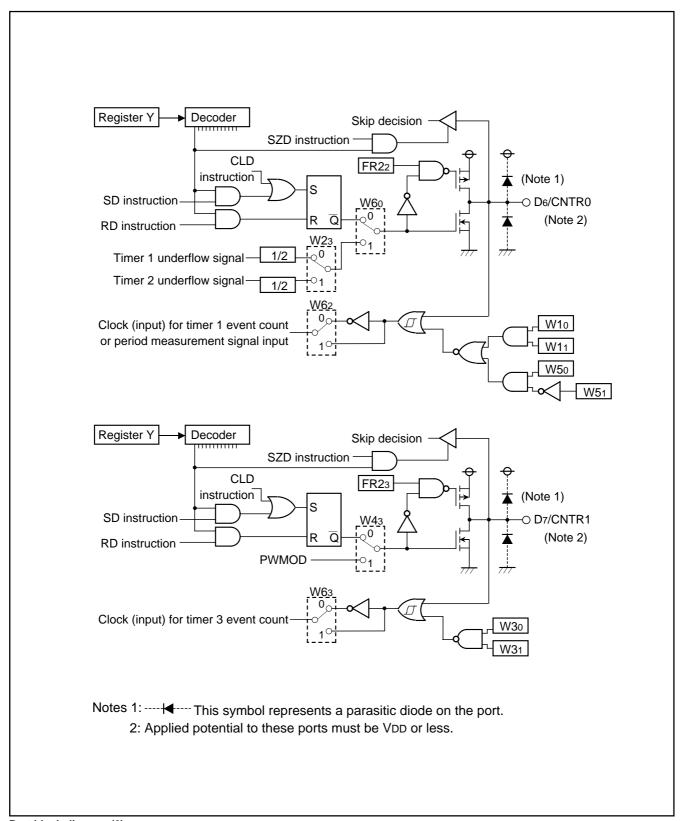

| D0-D7           | I/O port D<br>Input is examined by<br>skip decision. | I/O          | Each pin of port D has an independent 1-bit wide I/O function. The output structure can be switched to N-channel open-drain or CMOS by software. For input use, set the latch of the specified bit to "1" and select the N-channel open-drain. Ports D6, D7 is also used as CNTR0 pin and CNTR1 pin, respectively.                                      |

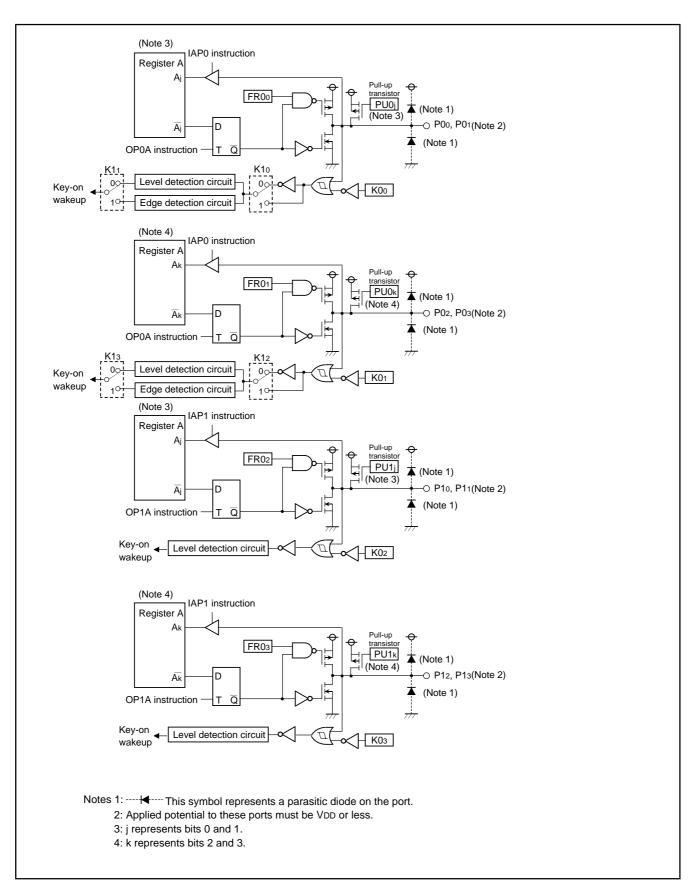

| P00-P03         | I/O port P0                                          | I/O          | Port P0 serves as a 4-bit I/O port. The output structure can be switched to N-channel open-drain or CMOS by software. For input use, set the latch of the specified bit to "1" and select the N-channel open-drain. Port P0 has a key-on wakeup function and a pull-up function. Both functions can be switched by software.                            |

| P10-P13         | I/O port P1                                          | I/O          | Port P1 serves as a 4-bit I/O port. The output structure can be switched to N-channel open-drain or CMOS by software. For input use, set the latch of the specified bit to "1" and select the N-channel open-drain. Port P1 has a key-on wakeup function and a pull-up function. Both functions can be switched by software.                            |

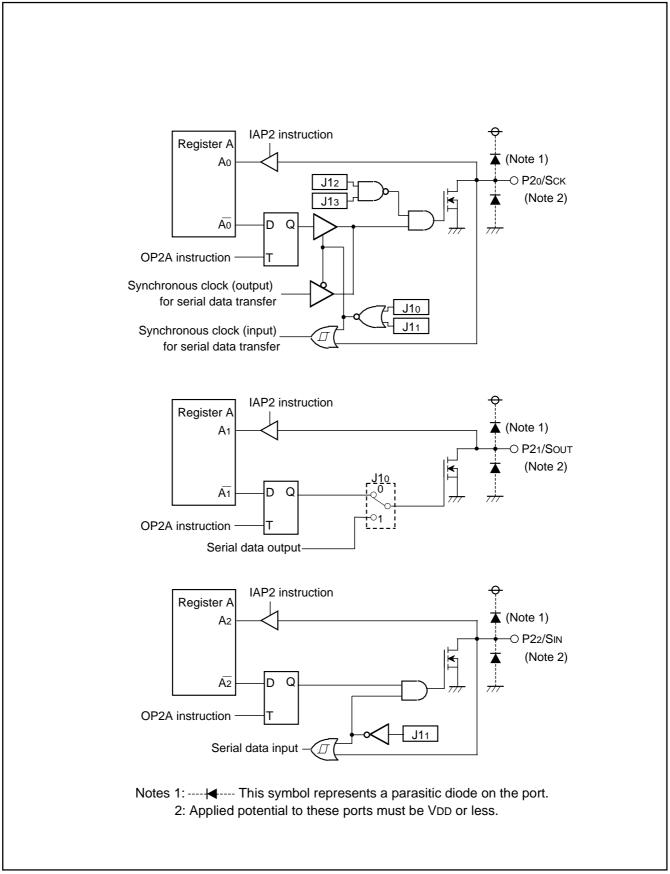

| P20-P23         | I/O port P2                                          | I/O          | Port P2 serves as a 3-bit I/O port. The output structure is N-channel open-drain. For input use, set the latch of the specified bit to "1".  Ports P20–P22 are also used as SCK, SOUT, SIN, respectively.                                                                                                                                               |

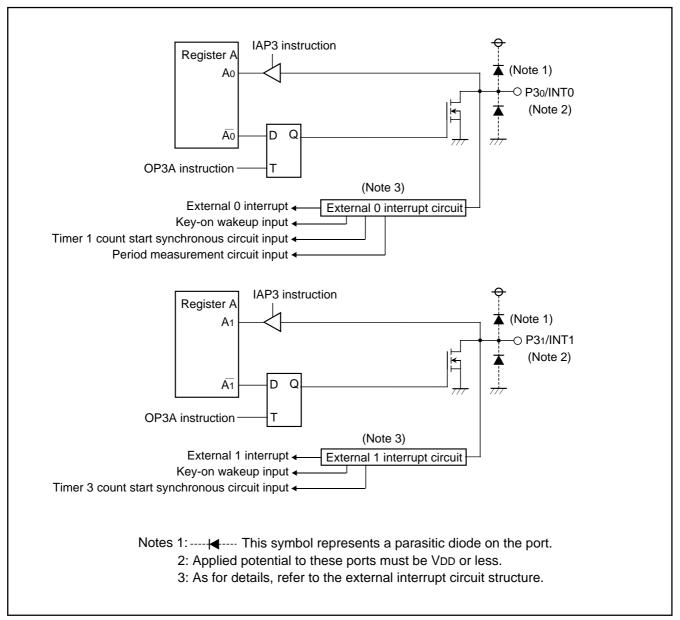

| P30-P33         | I/O port P3                                          | I/O          | Port P3 serves as a 2-bit I/O port. The output structure is N-channel open-drain. For input use, set the latch of the specified bit to "1".  Ports P3o and P31 are also used as INTO pin and INT1 pin, respectively.                                                                                                                                    |

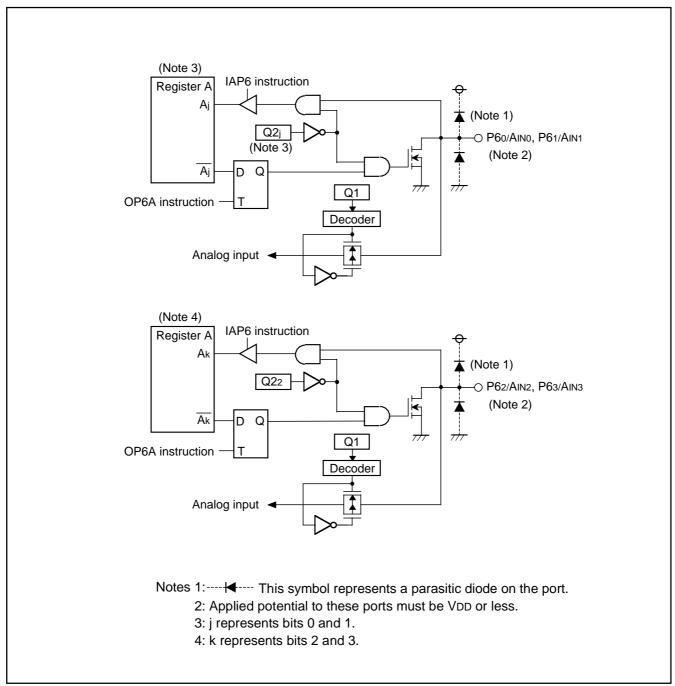

| P60-P63         | I/O port P6                                          | I/O          | Port P6 serves as a 4-bit I/O port. The output structure can be switched to N-channel open-drain. For input use, set the latch of the specified bit to "1". Ports P60–P63 are also used as AIN0–AIN3, respectively.                                                                                                                                     |

| CNTR0,<br>CNTR1 | Timer input/output                                   | I/O          | CNTR0 pin has the function to input the clock for the timer 1 event counter, and to output the timer 1 or timer 2 underflow signal divided by 2. CNTR1 pin has the function to input the clock for the timer 3 event counter, and to output the PWM signal generated by timer 4.CNTR0 pin and CNTR1 pin are also used as Ports D6 and D7, respectively. |

| INTO, INT1      | Interrupt input                                      | Input        | INT0 pin and INT1 pin accept external interrupts. They have the key-on wakeup function which can be switched by software. INT0 pin and INT1 pin are also used as Ports P30 and P31, respectively.                                                                                                                                                       |

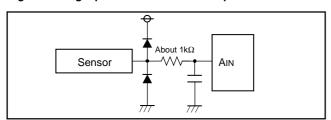

| AIN0-AIN3       | Analog input                                         | Input        | A/D converter analog input pins. AIN0-AIN3 are also used as ports P60-P63, respectively.                                                                                                                                                                                                                                                                |

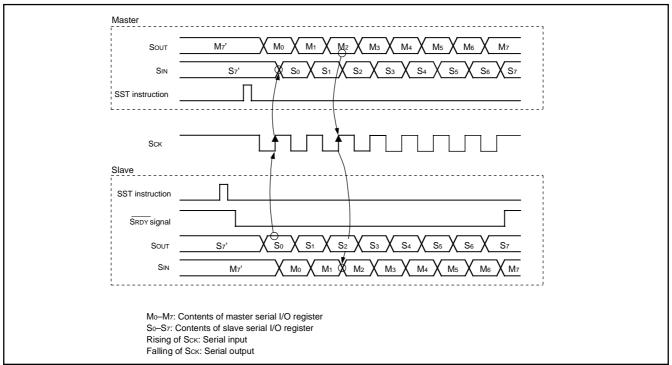

| Sck             | Serial I/O data I/O                                  | I/O          | Serial I/O data transfer synchronous clock I/O pin. SCK pin is also used as port P20.                                                                                                                                                                                                                                                                   |

| Sout            | Serial I/O data output                               | Output       | Serial I/O data output pin. Sout pin is also used as port P21.                                                                                                                                                                                                                                                                                          |

| SIN             | Serial I/O clock input                               | Input        | Serial I/O data input pin. SIN pin is also used as port P22.                                                                                                                                                                                                                                                                                            |

#### **MULTIFUNCTION**

| Pin | Multifunction | Pin   | Multifunction | Pin | Multifunction | Pin  | Multifunction |

|-----|---------------|-------|---------------|-----|---------------|------|---------------|

| D6  | CNTR0         | CNTR0 | D6            | P60 | AIN0          | AIN0 | P60           |

| D7  | CNTR1         | CNTR1 | D7            | P61 | AIN1          | AIN1 | P61           |

| P20 | Sck           | Sck   | P20           | P62 | AIN2          | AIN2 | P62           |

| P21 | Sout          | Sout  | P21           | P63 | AIN3          | AIN3 | P63           |

| P22 | SIN           | SIN   | P22           |     |               |      |               |

| P30 | INT0          | INT0  | P30           |     |               |      |               |

| P31 | INT1          | INT1  | P31           |     |               |      |               |

|     |               |       |               |     |               |      |               |

Notes 1: Pins except above have just single function.

- 2: The input/output of P30 and P31 can be used even when INT0 and INT1 are selected.

- 3: The input of ports P20-P22 can be used even when SIN, SOUT and SCK are selected.

- 4: The input/output of D6 can be used even when CNTR0 (input) is selected.

- 5: The input of D6 can be used even when CNTR0 (output) is selected.

- 6: The input/output of D7 can be used even when CNTR1 (input) is selected.

- 7: The input of D7 can be used even when CNTR1 (output) is selected.

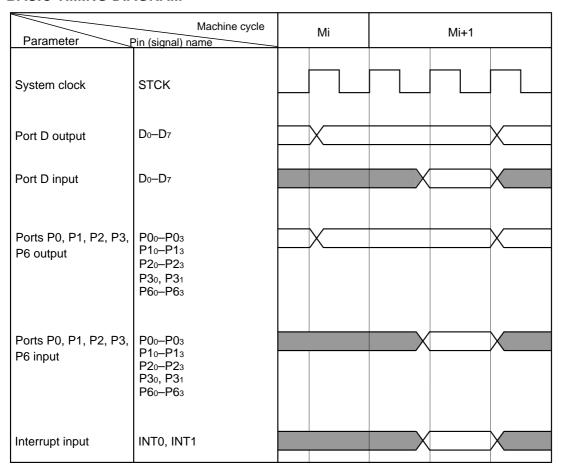

#### **DEFINITION OF CLOCK AND CYCLE**

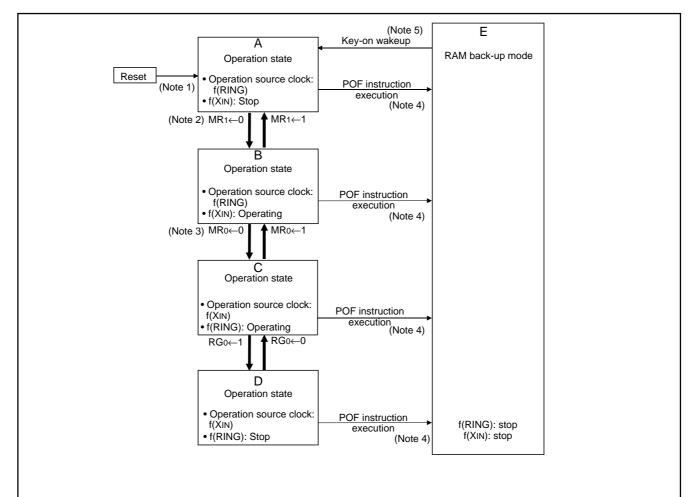

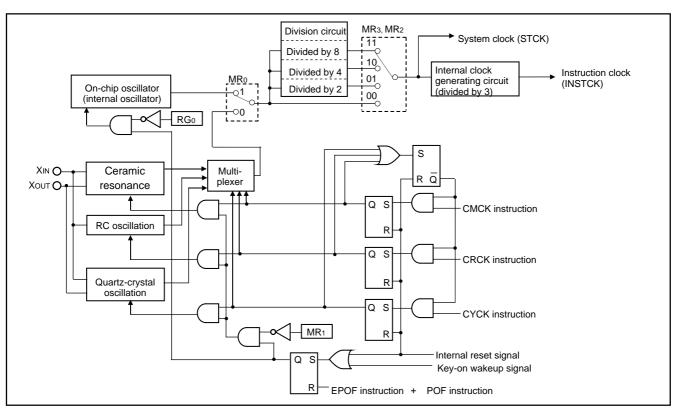

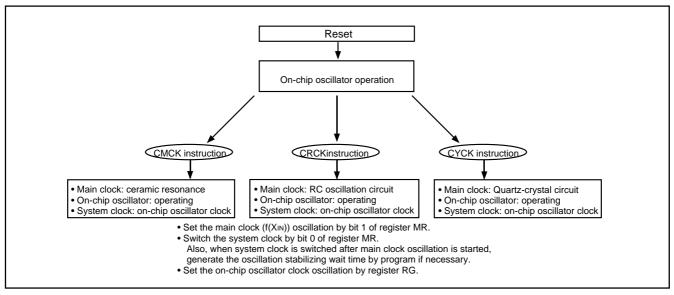

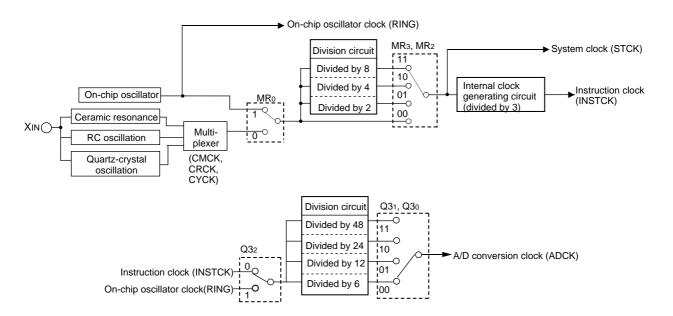

#### Operation source clock

The operation source clock is the source clock to operate this product. In this product, the following clocks are used.

- Clock (f(XIN)) by the external ceramic resonator

- Clock (f(XIN)) by the external RC oscillation

- Clock (f(XIN)) by the external input

- Clock (f(RING)) of the on-chip oscillator which is the internal

- Clock (f(XIN)) by the external quartz-crystal oscillation

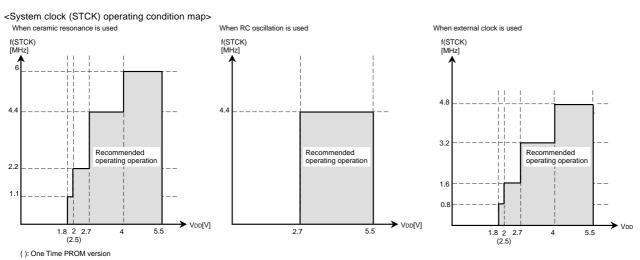

#### System clock (STCK)

The system clock is the basic clock for controlling this product. The system clock is selected by the clock control register MR shown as the table below.

Instruction clock (INSTCK)

The instruction clock is the basic clock for controlling CPU. The instruction clock (INSTCK) is a signal derived by dividing the system clock (STCK) by 3. The one instruction clock cycle generates the one machine cycle.

Machine cycle

The machine cycle is the standard cycle required to execute the instruction.

Table Selection of system clock

|                 | Register MR |     |                 | System clock        | Operation mode         |

|-----------------|-------------|-----|-----------------|---------------------|------------------------|

| MR <sub>3</sub> | MR2         | MR1 | MR <sub>0</sub> |                     |                        |

| 0               | 0           | 0   | 0               | f(STCK) = f(XIN)    | XIN through mode       |

|                 |             | X 1 |                 | f(STCK) = f(RING)   | Ring through mode      |

| 0               | 1           | 0   | 0               | f(STCK) = f(XIN)/2  | XIN divided by 2 mode  |

|                 |             | ×   | 1               | f(STCK) = f(RING)/2 | Ring divided by 2 mode |

| 1               | 0           | 0   | 0               | f(STCK) = f(XIN)/4  | XIN divided by 4 mode  |

|                 | X 1         |     | 1               | f(STCK) = f(RING)/4 | Ring divided by 4 mode |

| 1               | 1 0 0       |     | 0               | f(STCK) = f(XIN)/8  | XIN divided by 8 mode  |

|                 |             | X   | 1               | f(STCK) = f(RING)/8 | Ring divided by 8 mode |

X: 0 or 1

Note: The f(RING)/8 is selected after system is released from reset. When on-chip oscillator clock is selected for main clock, set the on-chip oscillator to be operating state.

**PRELIMINARY**

# Notice: This is not a final specification. Some parametric limits are subject to change.

## **PORT FUNCTION**

| Б.,     | Pin                | Input  | 0                     | I/O  | Control      | Control   |                                |

|---------|--------------------|--------|-----------------------|------|--------------|-----------|--------------------------------|

| Port    |                    | Output | Output structure      | unit | instructions | registers | Remark                         |

| Port D  | D0-D5              | I/O    | N-channel open-drain/ | 1    | SD, RD       | FR1, FR2  | Output structure selection     |

|         | D6/CNTR0           | (8)    | CMOS                  |      | SZD          | W6        | function (programmable)        |

|         | D7/CNTR1           |        |                       |      | CLD          | W4        |                                |

| Port P0 | P00-P03            | I/O    | N-channel open-drain/ | 4    | OP0A         | FR0       | Built-in programmable pull-up  |

|         |                    | (4)    | CMOS                  |      | IAP0         | PU0       | functions, key-on wakeup       |

|         |                    |        |                       |      |              | K0, K1    | functions and output structure |

|         |                    |        |                       |      |              |           | selection functions            |

| Port P1 | P10-P13            | I/O    | N-channel open-drain/ | 4    | OP1A         | FR0       | Built-in programmable pull-up  |

|         |                    | (4)    | CMOS                  |      | IAP1         | PU1       | functions, key-on wakeup       |

|         |                    |        |                       |      |              | K0        | functions and output structure |

|         |                    |        |                       |      |              |           | selection functions            |

| Port P2 | P20/SCK, P21/SOUT  | I/O    | N-channel open-drain  | 3    | OP2A         | J1        |                                |

|         | P22/SIN            | (3)    |                       |      | IAP2         |           |                                |

| Port P3 | P30/INT0, P31/INT1 | I/O    | N-channel open-drain  | 2    | ОР3А         | I1, I2    |                                |

|         |                    | (2)    |                       |      | IAP3         | K2        |                                |

| Port P6 | P60/AIN0-P63/AIN3  | I/O    | N-channel open-drain  | 4    | OP6A         | Q2        |                                |

|         |                    | (4)    |                       |      | IAP6         | Q1        |                                |

#### **CONNECTIONS OF UNUSED PINS**

| Pin               | Connection      | Usage condition                                            |          |  |  |

|-------------------|-----------------|------------------------------------------------------------|----------|--|--|

| XIN               | Open.           | Internal oscillator is selected.                           | (Note 1) |  |  |

| Xout              | Open.           | Internal oscillator is selected.                           | (Note 1) |  |  |

|                   |                 | RC oscillator is selected.                                 | (Note 2) |  |  |

|                   |                 | External clock input is selected for main clock.           | (Note 3) |  |  |

| D0-D5             | Open.           |                                                            |          |  |  |

|                   | Connect to Vss. | N-channel open-drain is selected for the output structure. | (Note 4) |  |  |

| D6/CNTR0          | Open.           | CNTR0 input is not selected for timer 1 count source.      |          |  |  |

|                   | Connect to Vss. | N-channel open-drain is selected for the output structure. | (Note 4) |  |  |

| D7/CNTR1          | Open.           | CNTR1 input is not selected for timer 3 count source.      |          |  |  |

|                   | Connect to Vss. | N-channel open-drain is selected for the output structure. | (Note 4) |  |  |

| P00-P03           | Open.           | The key-on wakeup function is not selected.                | (Note 6) |  |  |

|                   | Connect to Vss. | N-channel open-drain is selected for the output structure. | (Note 5) |  |  |

|                   |                 | The pull-up function is not selected.                      | (Note 4) |  |  |

|                   |                 | The key-on wakeup function is not selected.                | (Note 6) |  |  |

| P10-P13           | Open.           | The key-on wakeup function is not selected.                | (Note 7) |  |  |

|                   | Connect to Vss. | N-channel open-drain is selected for the output structure. | (Note 5) |  |  |

|                   |                 | The pull-up function is not selected.                      | (Note 4) |  |  |

|                   |                 | The key-on wakeup function is not selected.                | (Note 7) |  |  |

| P20/SCK           | Open.           | Scк pin is not selected.                                   |          |  |  |

|                   | Connect to Vss. |                                                            |          |  |  |

| P21/Sout          | Open.           | <del></del>                                                |          |  |  |

|                   | Connect to Vss. |                                                            |          |  |  |

| P22/SIN           | Open.           | SIN pin is not selected.                                   |          |  |  |

|                   | Connect to Vss. |                                                            |          |  |  |

| P3o/INT0          | Open.           | "0" is set to output latch.                                |          |  |  |

|                   | Connect to Vss. |                                                            |          |  |  |

| P31/INT1          | Open.           | "0" is set to output latch.                                |          |  |  |

|                   | Connect to Vss. |                                                            |          |  |  |

| P60/AIN0-P63/AIN3 | Open.           |                                                            |          |  |  |

|                   | Connect to Vss. |                                                            |          |  |  |

Notes 1: After system is released from reset, the internal oscillation (on-chip oscillator) is selected for system clock (RG0=0, MR0=1).

- 2: When the CRCK instruction is executed, the RC oscillation circuit becomes valid. Be careful that the swich of system clock is not executed at oscillation start only by the CRCK instruction execution.

- In order to start oscillation, setting the main clock f(XIN) oscillation to be valid (MR1=0) is required. (If necessary, generate the oscillation stabilizing wait time by software.)

- Also, when the main clock (f(XIN)) is selected as system clock, set the main clock f(XIN) oscillation (MR1=0) to be valid, and select main clock f(XIN) (MR0=0). Be careful that the switch of system clock cannot be executed at the same time when main clock oscillation is started.

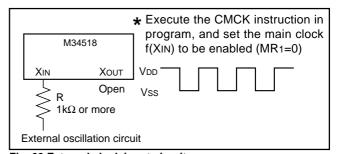

- 3: In order to use the external clock input for the main clock, select the ceramic resonance by executing the CMCK instruction at the beggining of software, and then set the main clock (f(XIN)) oscillation to be valid (MR1=0). Until the main clock (f(XIN)) oscillation becomes valid (MR1=0) after ceramic resonance becomes valid, XIN pin is fixed to "H". When an external clock is used, insert a 1 kΩ resistor to XIN pin in series for limits of current.

- 4: Be sure to select the output structure of ports Do-D5 and the pull-up function of P00-P03 and P10-P13 with every one port. Set the corresponding bits of registers for each port.

- 5: Be sure to select the output structure of ports P00–P03 and P10–P13 with every two ports. If only one of the two pins is used, leave another one open.

- 6: The key-on wakeup function is selected with every two bits. When only one of key-on wakeup function is used, considering that the value of key-on wake-up control register K1, set the unused 1-bit to "H" input (turn pull-up transistor ON and open) or "L" input (connect to Vss, or open and set the output latch to "0").

- 7: The key-on wakeup function is selected with every two bits. When one of key-on wakeup function is used, turn pull-up transistor of the unused one ON and open.

(Note when connecting to Vss and VDD)

Connect the unused pins to Vss and VDD using the thickest wire at the shortest distance against noise.

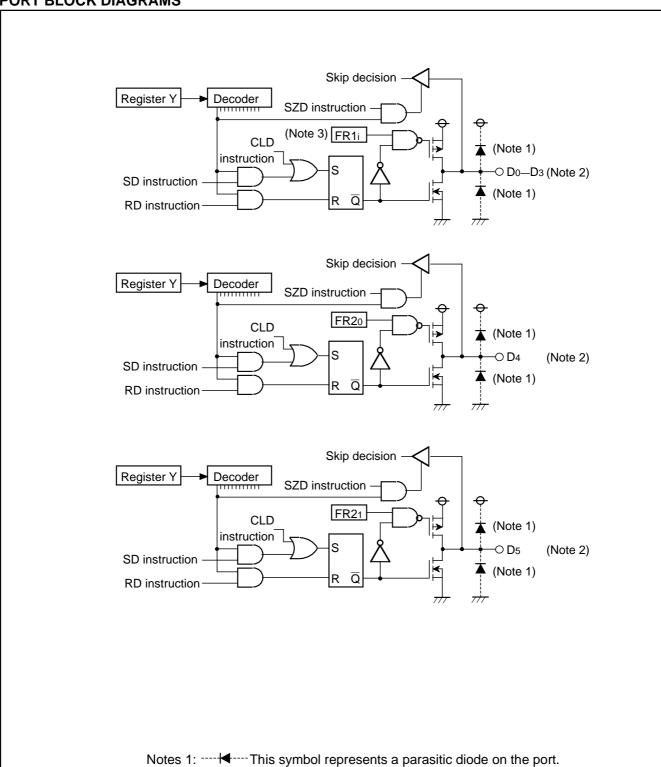

#### PORT BLOCK DIAGRAMS

2: Applied potential to these ports must be VDD or less.

3: i represents bits 0 to 3.

Port block diagram (1)

Port block diagram (2)

Port block diagram (3)

Port block diagram (5)

Port block diagram (6)

Port block diagram (7)

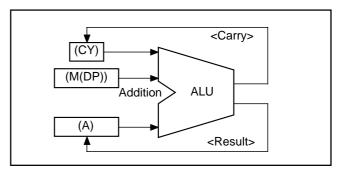

# FUNCTION BLOCK OPERATIONS CPU

### (1) Arithmetic logic unit (ALU)

The arithmetic logic unit ALU performs 4-bit arithmetic such as 4-bit data addition, comparison, AND operation, OR operation, and bit manipulation.

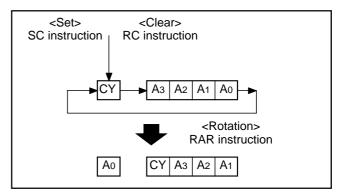

# (2) Register A and carry flag

Register A is a 4-bit register used for arithmetic, transfer, exchange, and I/O operation.

Carry flag CY is a 1-bit flag that is set to "1" when there is a carry with the AMC instruction (Figure 1).

It is unchanged with both A n instruction and AM instruction. The value of Ao is stored in carry flag CY with the RAR instruction (Figure 2).

Carry flag CY can be set to "1" with the SC instruction and cleared to "0" with the RC instruction.

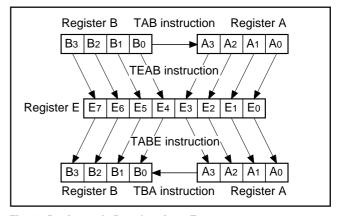

# (3) Registers B and E

Register B is a 4-bit register used for temporary storage of 4-bit data, and for 8-bit data transfer together with register A.

Register E is an 8-bit register. It can be used for 8-bit data transfer with register B used as the high-order 4 bits and register A as the low-order 4 bits (Figure 3).

Register E is undefined after system is released from reset and returned from the RAM back-up. Accordingly, set the initial value.

#### (4) Register D

Register D is a 3-bit register.

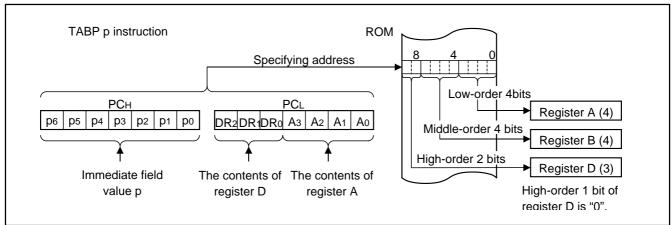

It is used to store a 7-bit ROM address together with register A and is used as a pointer within the specified page when the TABP p, BLA p, or BMLA p instruction is executed. Also, when the TABP p instruction is executed, the high-order 2 bits of the reference data in ROM is stored to the low-order 2 bits of register D, and the contents of the high-order 1 bit of register D is "0". (Figure 4).

Register D is undefined after system is released from reset and returned from the RAM back-up. Accordingly, set the initial value.

Fig. 1 AMC instruction execution example

Fig. 2 RAR instruction execution example

Fig. 3 Registers A, B and register E

Fig. 4 TABP p instruction execution example

### (5) Stack registers (SKs) and stack pointer (SP)

Stack registers (SKs) are used to temporarily store the contents of program counter (PC) just before branching until returning to the original routine when;

- branching to an interrupt service routine (referred to as an interrupt service routine),

- · performing a subroutine call, or

- executing the table reference instruction (TABP p).

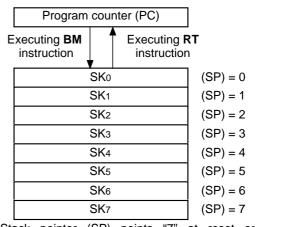

Stack registers (SKs) are eight identical registers, so that subroutines can be nested up to 8 levels. However, one of stack registers is used respectively when using an interrupt service routine and when executing a table reference instruction. Accordingly, be careful not to over the stack when performing these operations together. The contents of registers SKs are destroyed when 8 levels are exceeded.

The register SK nesting level is pointed automatically by 3-bit stack pointer (SP). The contents of the stack pointer (SP) can be transferred to register A with the TASP instruction.

Figure 5 shows the stack registers (SKs) structure.

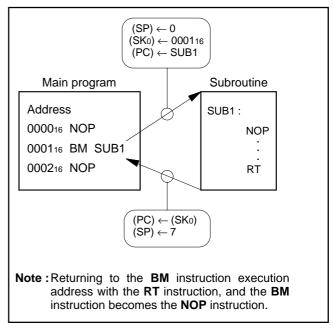

Figure 6 shows the example of operation at subroutine call.

### (6) Interrupt stack register (SDP)

Interrupt stack register (SDP) is a 1-stage register. When an interrupt occurs, this register (SDP) is used to temporarily store the contents of data pointer, carry flag, skip flag, register A, and register B just before an interrupt until returning to the original routine. Unlike the stack registers (SKs), this register (SDP) is not used when executing the subroutine call instruction and the table reference instruction.

#### (7) Skip flag

Skip flag controls skip decision for the conditional skip instructions and continuous described skip instructions. When an interrupt occurs, the contents of skip flag is stored automatically in the interrupt stack register (SDP) and the skip condition is retained.

Stack pointer (SP) points "7" at reset or returning from RAM back-up mode. It points "0" by executing the first BM instruction, and the contents of program counter is stored in SKo. When the BM instruction is executed after eight stack registers are used ((SP) = 7), (SP) = 0 and the contents of SKo is destroyed.

Fig. 5 Stack registers (SKs) structure

Fig. 6 Example of operation at subroutine call

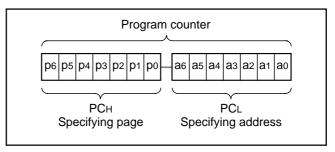

# (8) Program counter (PC)

Program counter (PC) is used to specify a ROM address (page and address). It determines a sequence in which instructions stored in ROM are read. It is a binary counter that increments the number of instruction bytes each time an instruction is executed. However, the value changes to a specified address when branch instructions, subroutine call instructions, return instructions, or the table reference instruction (TABP p) is executed.

Program counter consists of PCH (most significant bit to bit 7) which specifies to a ROM page and PCL (bits 6 to 0) which specifies an address within a page. After it reaches the last address (address 127) of a page, it specifies address 0 of the next page (Figure 7).

Make sure that the PCH does not specify after the last page of the built-in ROM.

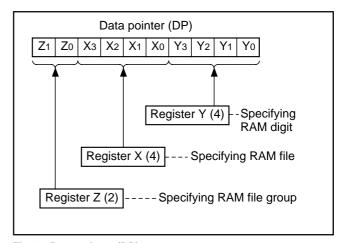

### (9) Data pointer (DP)

Data pointer (DP) is used to specify a RAM address and consists of registers Z, X, and Y. Register Z specifies a RAM file group, register X specifies a file, and register Y specifies a RAM digit (Figure 8).

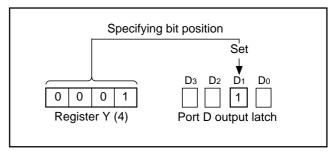

Register Y is also used to specify the port D bit position.

When using port D, set the port D bit position to register Y certainly and execute the SD, RD, or SZD instruction (Figure 9).

#### • Note

Register Z of data pointer is undefined after system is released from reset

Also, registers Z, X and Y are undefined in the RAM back-up. After system is returned from the RAM back-up, set these registers.

Fig. 7 Program counter (PC) structure

Fig. 8 Data pointer (DP) structure

Fig. 9 SD instruction execution example

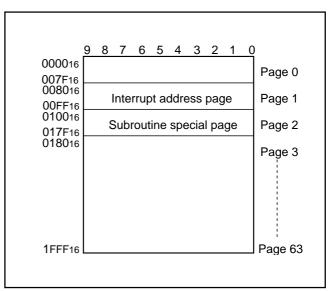

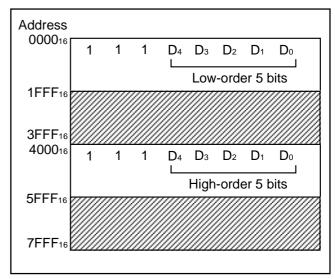

### PROGRAM MEMORY (ROM)

The program memory is a mask ROM. 1 word of ROM is composed of 10 bits. ROM is separated every 128 words by the unit of page (addresses 0 to 127). Table 1 shows the ROM size and pages. Figure 10 shows the ROM map of M34518M8/E8.

Table 1 ROM size and pages

| Part number  | ROM (PROM) size | Pages        |

|--------------|-----------------|--------------|

| T art mamber | (X 10 bits)     | 1 ages       |

| M34518M2     | 2048 words      | 16 (0 to 15) |

| M34518M4     | 4096 words      | 32 (0 to 31) |

| M34518M6     | 6144 words      | 48 (0 to 47) |

| M34518M8/E8  | 8192 words      | 64 (0 to 63) |

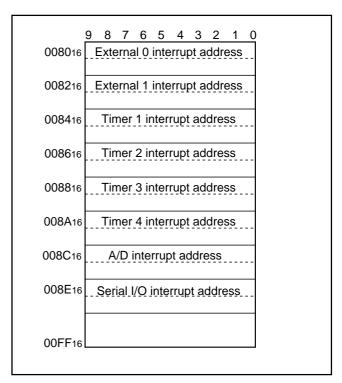

A part of page 1 (addresses 008016 to 00FF16) is reserved for interrupt addresses (Figure 11). When an interrupt occurs, the address (interrupt address) corresponding to each interrupt is set in the program counter, and the instruction at the interrupt address is executed. When using an interrupt service routine, write the instruction generating the branch to that routine at an interrupt address.

Page 2 (addresses 010016 to 017F16) is the special page for subroutine calls. Subroutines written in this page can be called from any page with the 1-word instruction (BM). Subroutines extending from page 2 to another page can also be called with the BM instruction when it starts on page 2.

ROM pattern (bits 9 to 0) of all addresses can be used as data areas with the TABP  $\mbox{\sc p}$  instruction.

Fig. 10 ROM map of M34518M8/E8

Fig. 11 Page 1 (addresses 008016 to 00FF16) structure

## **DATA MEMORY (RAM)**

1 word of RAM is composed of 4 bits, but 1-bit manipulation (with the SB j, RB j, and SZB j instructions) is enabled for the entire memory area. A RAM address is specified by a data pointer. The data pointer consists of registers Z, X, and Y. Set a value to the data pointer certainly when executing an instruction to access RAM (also, set a value after system returns from RAM back-up). Table 2 shows the RAM size. Figure 12 shows the RAM map.

#### • Note

Register Z of data pointer is undefined after system is released from reset.

Also, registers Z, X and Y are undefined in the RAM back-up. After system is returned from the RAM back-up, set these registers.

Table 2 RAM size

| Part number    | RAM size                       |

|----------------|--------------------------------|

| M34518M2/M4    | 256 words X 4 bits (1024 bits) |

| M34518M6/M8/E8 | 384 words X 4 bits (1536 bits) |

Fig. 12 RAM map

# Notice: This is not a final specification. Some parametric limits are subject to change.

#### INTERRUPT FUNCTION

The interrupt type is a vectored interrupt branching to an individual address (interrupt address) according to each interrupt source. An interrupt occurs when the following 3 conditions are satisfied.

- An interrupt activated condition is satisfied (request flag = "1")

- Interrupt enable bit is enabled ("1")

- Interrupt enable flag is enabled (INTE = "1")

Table 3 shows interrupt sources. (Refer to each interrupt request flag for details of activated conditions.)

# (1) Interrupt enable flag (INTE)

The interrupt enable flag (INTE) controls whether the every interrupt enable/disable. Interrupts are enabled when INTE flag is set to "1" with the EI instruction and disabled when INTE flag is cleared to "0" with the DI instruction. When any interrupt occurs, the INTE flag is automatically cleared to "0," so that other interrupts are disabled until the EI instruction is executed.

### (2) Interrupt enable bit

Use an interrupt enable bit of interrupt control registers V1 and V2 to select the corresponding interrupt or skip instruction.

Table 4 shows the interrupt request flag, interrupt enable bit and skip instruction.

Table 5 shows the interrupt enable bit function.

# (3) Interrupt request flag

When the activated condition for each interrupt is satisfied, the corresponding interrupt request flag is set to "1." Each interrupt request flag is cleared to "0" when either;

- an interrupt occurs, or

- the next instruction is skipped with a skip instruction.

Each interrupt request flag is set when the activated condition is satisfied even if the interrupt is disabled by the INTE flag or its interrupt enable bit. Once set, the interrupt request flag retains set until a clear condition is satisfied.

Accordingly, an interrupt occurs when the interrupt disable state is released while the interrupt request flag is set.

If more than one interrupt request flag is set when the interrupt disable state is released, the interrupt priority level is as follows shown in Table 3.

**Table 3 Interrupt sources**

| rable 5 interrupt sources |                      |                                           |                     |  |  |  |  |

|---------------------------|----------------------|-------------------------------------------|---------------------|--|--|--|--|

| Priority<br>level         | Interrupt name       | Activated condition                       | Interrupt address   |  |  |  |  |

| 1                         | External 0 interrupt | Level change of INT0 pin                  | Address 0 in page 1 |  |  |  |  |

| 2                         | External 1 interrupt | Level change of INT1 pin                  | Address 2 in page 1 |  |  |  |  |

| 3                         | Timer 1 interrupt    | Timer 1 underflow                         | Address 4 in page 1 |  |  |  |  |

| 4                         | Timer 2 interrupt    | Timer 2 underflow                         | Address 6 in page 1 |  |  |  |  |

| 5                         | Timer 3 interrupt    | Timer 3 underflow                         | Address 8 in page 1 |  |  |  |  |

| 6                         | Timer 4 interrupt    | Timer 4 underflow                         | Address A in page 1 |  |  |  |  |

| 7                         | A/D interrupt        | Completion of A/D conversion              | Address C in page 1 |  |  |  |  |

| 8                         | Serial I/O interrupt | Completion of serial I/O transmit/receive | Address E in page 1 |  |  |  |  |

Table 4 Interrupt request flag, interrupt enable bit and skip instruction

| 311 4011011          |                        |                  |                      |

|----------------------|------------------------|------------------|----------------------|

| Interrupt name       | Interrupt request flag | Skip instruction | Interrupt enable bit |

| External 0 interrupt | EXF0                   | SNZ0             | V10                  |

| External 1 interrupt | EXF1                   | SNZ1             | V11                  |

| Timer 1 interrupt    | T1F                    | SNZT1            | V12                  |

| Timer 2 interrupt    | T2F                    | SNZT2            | V13                  |

| Timer 3 interrupt    | T3F                    | SNZT3            | V20                  |

| Timer 4 interrupt    | T4F                    | SNZT4            | V21                  |

| A/D interrupt        | ADF                    | SNZAD            | V22                  |

| Serial I/O interrupt | SIOF                   | SNZSI            | V23                  |

|                      |                        |                  | •                    |

#### Table 5 Interrupt enable bit function

| Interrupt enable bit | Occurrence of interrupt | Skip instruction |  |  |

|----------------------|-------------------------|------------------|--|--|

| 1                    | Enabled                 | Invalid          |  |  |

| 0                    | Disabled                | Valid            |  |  |

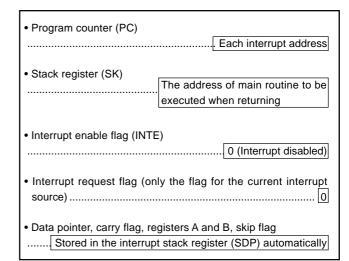

# (4) Internal state during an interrupt

The internal state of the microcomputer during an interrupt is as follows (Figure 14).

- Program counter (PC)

An interrupt address is set in program counter. The address to be executed when returning to the main routine is automatically stored in the stack register (SK).

- Interrupt enable flag (INTE)

INTE flag is cleared to "0" so that interrupts are disabled.

- Interrupt request flag

Only the request flag for the current interrupt source is cleared to "0"

- Data pointer, carry flag, skip flag, registers A and B

The contents of these registers and flags are stored automatically in the interrupt stack register (SDP).

### (5) Interrupt processing

When an interrupt occurs, a program at an interrupt address is executed after branching a data store sequence to stack register. Write the branch instruction to an interrupt service routine at an interrupt address.

Use the RTI instruction to return from an interrupt service routine. Interrupt enabled by executing the EI instruction is performed after executing 1 instruction (just after the next instruction is executed). Accordingly, when the EI instruction is executed just before the RTI instruction, interrupts are enabled after returning the main routine. (Refer to Figure 13)

Fig. 13 Program example of interrupt processing

Fig. 14 Internal state when interrupt occurs

Fig. 15 Interrupt system diagram

# (6) Interrupt control registers

• Interrupt control register V1

Interrupt enable bits of external 0, external 1, timer 1 and timer 2

are assigned to register V1. Set the contents of this register

through register A with the TV1A instruction. The TAV1 instruction

can be used to transfer the contents of register V1 to register A.

Interrupt control register V2

The timer 3, timer 4, A/D and serial I/O interrupt enable bit is assigned to register V2. Set the contents of this register through register A with the TV2A instruction. The TAV2 instruction can be

used to transfer the contents of register V2 to register A.

#### Table 6 Interrupt control registers

| Interrupt control register V1 |                                   | at reset : 00002 |                                                 | at RAM back-up : 00002        | R/W<br>TAV1/TV1A |

|-------------------------------|-----------------------------------|------------------|-------------------------------------------------|-------------------------------|------------------|

| V13                           | Timer 2 interrupt enable bit      | 0                | Interrupt disabled                              | (SNZT2 instruction is valid)  |                  |

| V 13                          | V 13 Timer 2 interrupt enable bit |                  | Interrupt enabled (                             | SNZT2 instruction is invalid) |                  |

| 1/10                          | V12 Timer 1 interrupt enable bit  | 0                | Interrupt disabled (SNZT1 instruction is valid) |                               |                  |

| V 12                          |                                   | 1                | Interrupt enabled (                             | SNZT1 instruction is invalid) |                  |

| V11                           | External 1 interrupt enable bit   | 0                | Interrupt disabled                              | (SNZ1 instruction is valid)   |                  |

| VIII                          | External Timerrupt enable bit     | 1                | Interrupt enabled (                             | SNZ1 instruction is invalid)  |                  |

| V10                           | External 0 interrupt enable bit   | 0                | Interrupt disabled                              | (SNZ0 instruction is valid)   |                  |

| V 10                          | External o interrupt enable bit   | 1                | Interrupt enabled (                             | SNZ0 instruction is invalid)  |                  |

| Interrupt control register V2 |                                     | at reset : 00002 |                                                 | at RAM back-up : 00002        | R/W<br>TAV2/TV2A |

|-------------------------------|-------------------------------------|------------------|-------------------------------------------------|-------------------------------|------------------|

| 1/20                          | Serial I/O interrupt enable bit     | 0                | Interrupt disabled                              | (SNZSI instruction is valid)  |                  |

| V 23                          | V23 Serial I/O interrupt enable bit |                  | Interrupt enabled (                             | SNZSI instruction is invalid) |                  |

| \/Os                          | V22 A/D interrupt enable bit        | 0                | Interrupt disabled (SNZAD instruction is valid) |                               |                  |

| V 22                          |                                     | 1                | Interrupt enabled (                             | SNZAD instruction is invalid) |                  |

| \/O.                          | Timer 4 interrupt enable bit        | 0                | Interrupt disabled                              | (SNZT4 instruction is valid)  |                  |

| V21                           | Timer 4 interrupt enable bit        | 1                | Interrupt enabled (                             | SNZT4 instruction is invalid) |                  |

| \/Oo                          | Timer 3 interrupt enable bit        | 0                | Interrupt disabled                              | (SNZT3 instruction is valid)  |                  |

| V20                           | Timer 3 interrupt enable bit        | 1                | Interrupt enabled (                             | SNZT3 instruction is invalid) |                  |

Note: "R" represents read enabled, and "W" represents write enabled.

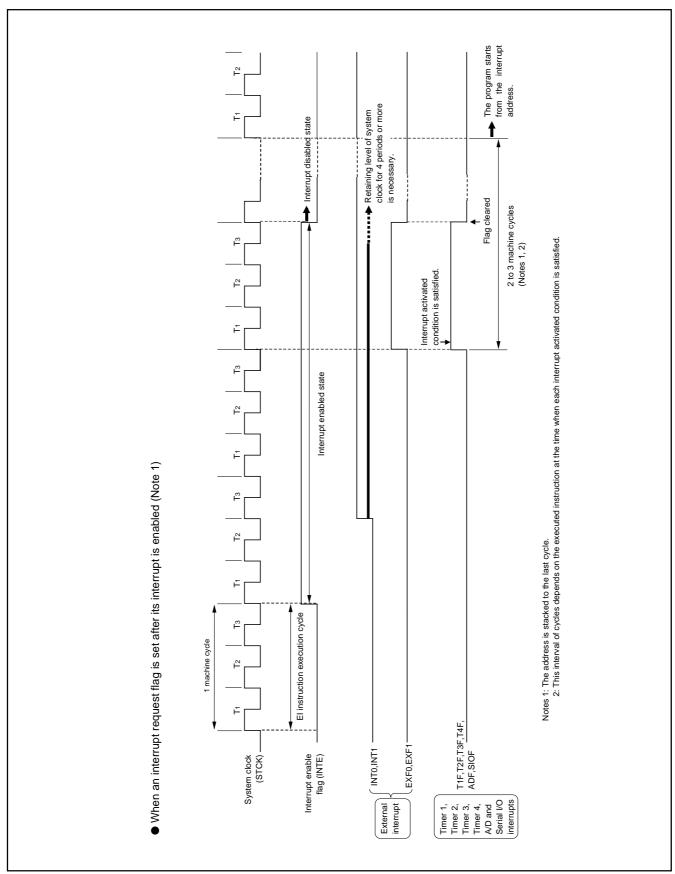

#### (7) Interrupt sequence

Interrupts only occur when the respective INTE flag, interrupt enable bits (V10–V13, V20–V23), and interrupt request flag are "1." The interrupt actually occurs 2 to 3 machine cycles after the cycle in which all three conditions are satisfied. The interrupt occurs after 3 machine cycles only when the three interrupt conditions are satisfied on execution of other than one-cycle instructions (Refer to Figure 16).

Fig. 16 Interrupt sequence

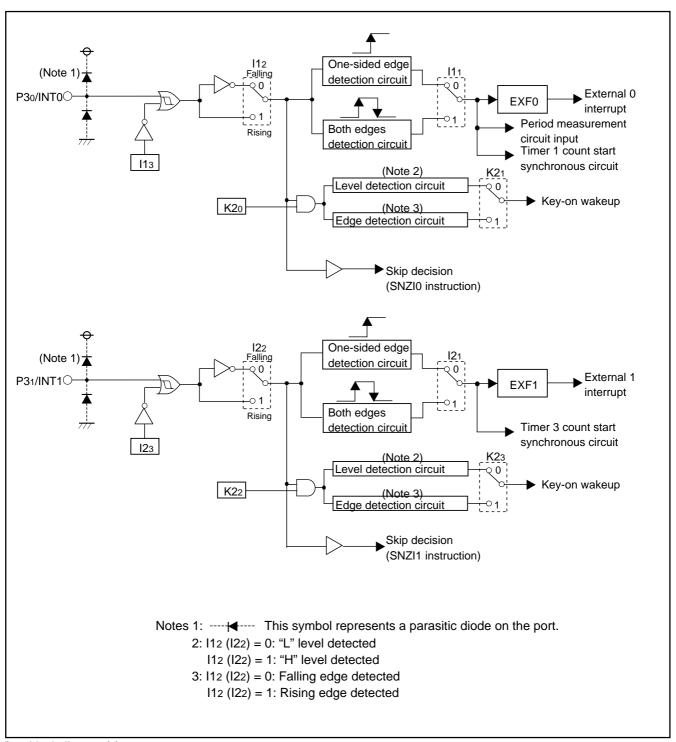

#### **EXTERNAL INTERRUPTS**

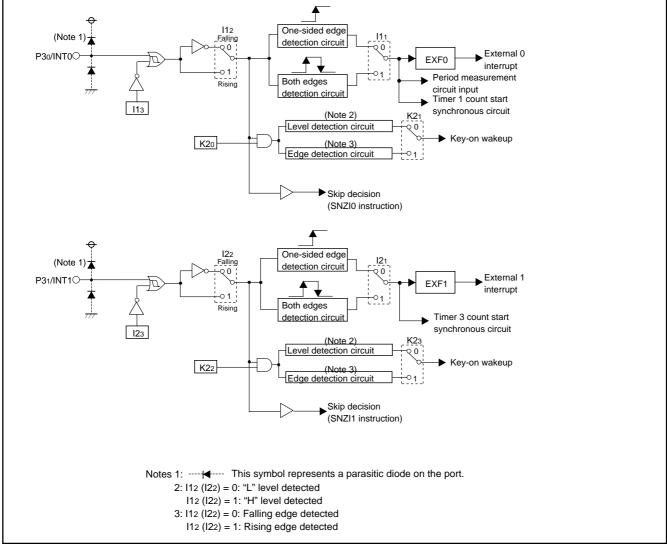

The 4518 Group has the external 0 interrupt and external 1 interrupt.

An external interrupt request occurs when a valid waveform is input to an interrupt input pin (edge detection).

The external interrupt can be controlled with the interrupt control registers I1 and I2.

Table 7 External interrupt activated conditions

| Name                 | Input pin | Activated condition                             | Valid waveform selection bit |

|----------------------|-----------|-------------------------------------------------|------------------------------|

| External 0 interrupt | P30/INT0  | When the next waveform is input to P30/INT0 pin | l11                          |

|                      |           | ■ Falling waveform ("H"→"L")                    | l12                          |

|                      |           | Rising waveform ("L"→"H")                       |                              |

|                      |           | Both rising and falling waveforms               |                              |

| External 1 interrupt | P31/INT1  | When the next waveform is input to P31/INT1 pin | I21                          |

|                      |           | ■ Falling waveform ("H"→"L")                    | I22                          |

|                      |           | Rising waveform ("L"→"H")                       |                              |

|                      |           | Both rising and falling waveforms               |                              |

Fig. 17 External interrupt circuit structure

# (1) External 0 interrupt request flag (EXF0)

External 0 interrupt request flag (EXF0) is set to "1" when a valid waveform is input to P30/INT0 pin.

The valid waveforms causing the interrupt must be retained at their level for 4 clock cycles or more of the system clock (Refer to Figure 16).

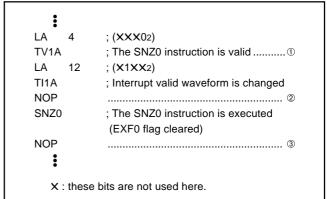

The state of EXF0 flag can be examined with the skip instruction (SNZ0). Use the interrupt control register V1 to select the interrupt or the skip instruction. The EXF0 flag is cleared to "0" when an interrupt occurs or when the next instruction is skipped with the skip instruction.

- External 0 interrupt activated condition

- External 0 interrupt activated condition is satisfied when a valid waveform is input to P3o/INT0 pin.

- The valid waveform can be selected from rising waveform, falling waveform or both rising and falling waveforms. An example of how to use the external 0 interrupt is as follows.

- ① Set the bit 3 of register I1 to "1" for the INT0 pin to be in the input enabled state.

- 2 Select the valid waveform with the bits 1 and 2 of register I1.

- ③ Clear the EXF0 flag to "0" with the SNZ0 instruction.

- Set the NOP instruction for the case when a skip is performed

with the SNZ0 instruction.

- Set both the external 0 interrupt enable bit (V10) and the INTE flag to "1."

The external 0 interrupt is now enabled. Now when a valid waveform is input to the P30/INT0 pin, the EXF0 flag is set to "1" and the external 0 interrupt occurs.

#### (2) External 1 interrupt request flag (EXF1)

External 1 interrupt request flag (EXF1) is set to "1" when a valid waveform is input to P31/INT1 pin.

The valid waveforms causing the interrupt must be retained at their level for 4 clock cycles or more of the system clock (Refer to Figure 16).

The state of EXF1 flag can be examined with the skip instruction (SNZ1). Use the interrupt control register V1 to select the interrupt or the skip instruction. The EXF1 flag is cleared to "0" when an interrupt occurs or when the next instruction is skipped with the skip instruction

- External 1 interrupt activated condition

- External 1 interrupt activated condition is satisfied when a valid waveform is input to P31/INT1 pin.

- The valid waveform can be selected from rising waveform, falling waveform or both rising and falling waveforms. An example of how to use the external 1 interrupt is as follows.

- ① Set the bit 3 of register I2 to "1" for the INT1 pin to be in the input enabled state.

- ② Select the valid waveform with the bits 1 and 2 of register I2.

- ③ Clear the EXF1 flag to "0" with the SNZ1 instruction.

- Set the NOP instruction for the case when a skip is performed

with the SNZ1 instruction.

- Set both the external 1 interrupt enable bit (V11) and the INTE flag to "1."

The external 1 interrupt is now enabled. Now when a valid waveform is input to the P31/INT1 pin, the EXF1 flag is set to "1" and the external 1 interrupt occurs.

# (3) External interrupt control registers

• Interrupt control register I1

Register I1 controls the valid waveform for the external 0 interrupt. Set the contents of this register through register A with the TI1A instruction. The TAI1 instruction can be used to transfer the contents of register I1 to register A.

• Interrupt control register I2

Register I2 controls the valid waveform for the external 1 interrupt. Set the contents of this register through register A with the TI2A instruction. The TAI2 instruction can be used to transfer the contents of register I2 to register A.

Table 8 External interrupt control register

|     | Interrupt control register I1               |   | reset : 00002                                                                   | at RAM back-up : state retained    | R/W<br>TAI1/TI1A |

|-----|---------------------------------------------|---|---------------------------------------------------------------------------------|------------------------------------|------------------|

| l13 | INTO pin input control bit                  | 0 | INT0 pin input disa                                                             | abled                              |                  |

| 113 | in to pin input control bit                 | 1 | INT0 pin input ena                                                              | bled                               |                  |

| l12 | Interrupt valid waveform for INT0 pin/      | 0 | Falling waveform/"L" level ("L" level is recognized with the SNZI0 instruction) |                                    |                  |

| 112 | return level selection bit                  | 1 | Rising waveform/"H" level ("H" level is recognized with the SNZI0 instruction)  |                                    |                  |

| 144 | INTO pin adag detection circuit control bit | 0 | One-sided edge detected                                                         |                                    |                  |

| 111 | Into pin edge detection circuit control bit |   | Both edges detected                                                             |                                    |                  |

| I10 | INT0 pin Timer 1 count start synchronous    | 0 | Timer 1 count start                                                             | t synchronous circuit not selected |                  |

| 110 | circuit selection bit                       | 1 | Timer 1 count start synchronous circuit selected                                |                                    |                  |

| Interrupt control register I2 |                                             | at reset : 00002 |                                                                                | at RAM back-up : state retained                                                 | R/W<br>TAI2/TI2A |  |

|-------------------------------|---------------------------------------------|------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------|--|

| 123                           | INT1 pin input control bit (Note 2)         | 0                | INT1 pin input disa                                                            | bled                                                                            |                  |  |

| 123                           | INT F pin input control bit (Note 2)        | 1                | INT1 pin input ena                                                             | bled                                                                            |                  |  |

| 122                           | Interrupt valid waveform for INT1 pin/      | 0                | Falling waveform/" instruction)                                                | Falling waveform/"L" level ("L" level is recognized with the SNZI1 instruction) |                  |  |

| 122                           | return level selection bit (Note 2)         | 1                | Rising waveform/"H" level ("H" level is recognized with the SNZI1 instruction) |                                                                                 |                  |  |

| 124                           | INT1 pip adge detection circuit central bit | 0                | One-sided edge detected                                                        |                                                                                 |                  |  |

| 121                           | INT1 pin edge detection circuit control bit |                  | Both edges detected                                                            |                                                                                 |                  |  |

| 120                           | INT1 pin Timer 3 count start synchronous    | 0                | Timer 3 count start                                                            | synchronous circuit not selected                                                |                  |  |

| 120                           | circuit selection bit                       | 1                | Timer 3 count start                                                            | synchronous circuit selected                                                    |                  |  |

Notes 1: "R" represents read enabled, and "W" represents write enabled.

<sup>2:</sup> When the contents of I12, I13 I22 and I23 are changed, the external interrupt request flag (EXF0, EXF1) may be set.

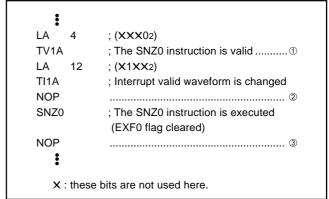

# (4) Notes on External 0 interrupt

- ① Note [1] on bit 3 of register I1

- When the input of the INTO pin is controlled with the bit 3 of register I1 in software, be careful about the following notes.

- Depending on the input state of the P3o/INT0 pin, the external 0 interrupt request flag (EXF0) may be set when the bit 3 of register I1 is changed. In order to avoid the occurrence of an unexpected interrupt, clear the bit 0 of register V1 to "0" (refer to Figure 18 ①) and then, change the bit 3 of register I1. In addition, execute the SNZ0 instruction to clear the EXF0 flag to "0" after executing at least one instruction (refer to Figure 18 ②). Also, set the NOP instruction for the case when a skip is performed with the SNZ0 instruction (refer to Figure 18 ③).

```

LA

; (XXX02)

TV1A

; The SNZ0 instruction is valid ..... ①

LA

; (1XXX2)

TI1A

; Control of INT0 pin input is changed

NOP

SNZ0

; The SNZ0 instruction is executed

(EXF0 flag cleared)

NOP

:

X: these bits are not used here.

```

Fig. 18 External 0 interrupt program example-1

- 2 Note [2] on bit 3 of register I1

- When the bit 3 of register I1 is cleared to "0", the RAM back-up mode is selected and the input of INT0 pin is disabled, be careful about the following notes.

- When the input of INT0 pin is disabled (register I13 = "0"), set the key-on wakeup function to be invalid (register K20 = "0") before system enters to the RAM back-up mode. (refer to Figure 19①).

```

LA 0 ; (XXX02)

TK2A ; Input of INT0 key-on wakeup invalid .. ①

DI

EPOF

POF ; RAM back-up

X: these bits are not used here.

```

Fig. 19 External 0 interrupt program example-2

- 3 Note on bit 2 of register I1

- When the interrupt valid waveform of the P30/INT0 pin is changed with the bit 2 of register I1 in software, be careful about the following notes.

- Depending on the input state of the P3o/INT0 pin, the external 0 interrupt request flag (EXF0) may be set when the bit 2 of register I1 is changed. In order to avoid the occurrence of an unexpected interrupt, clear the bit 0 of register V1 to "0" (refer to Figure 20①) and then, change the bit 2 of register I1. In addition, execute the SNZ0 instruction to clear the EXF0 flag to "0" after executing at least one instruction (refer to Figure 20②). Also, set the NOP instruction for the case when a skip is performed with the SNZ0 instruction (refer to Figure 20③).

Fig. 20 External 0 interrupt program example-3

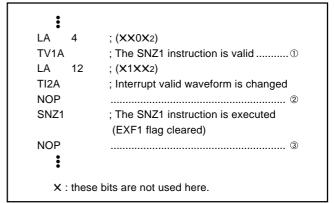

### (5) Notes on External 1 interrupt

① Note [1] on bit 3 of register I2

When the input of the INT1 pin is controlled with the bit 3 of register I2 in software, be careful about the following notes.

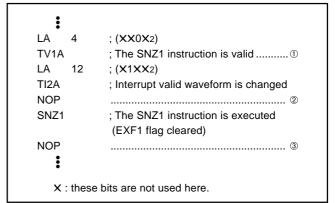

• Depending on the input state of the P31/INT1 pin, the external 1 interrupt request flag (EXF1) may be set when the bit 3 of register I2 is changed. In order to avoid the occurrence of an unexpected interrupt, clear the bit 1 of register V1 to "0" (refer to Figure 21①) and then, change the bit 3 of register I2. In addition, execute the SNZ1 instruction to clear the EXF1 flag to "0" after executing at least one instruction (refer to Figure 21②). Also, set the NOP instruction for the case when a skip is performed with the SNZ1 instruction (refer to Figure 21③).

```

LA

; (XX0X2)

TV1A

; The SNZ1 instruction is valid ..... ①

LA

; (1XXX2)

TI2A

; Control of INT1 pin input is changed

NOP

SNZ1

; The SNZ1 instruction is executed

(EXF1 flag cleared)

NOP

...... 3

:

X: these bits are not used here.

```

Fig. 21 External 1 interrupt program example-1

about the following notes.

- ② Note [2] on bit 3 of register I2

When the bit 3 of register I2 is cleared to "0", the RAM back-up mode is selected and the input of INT1 pin is disabled, be careful

- When the input of INT1 pin is disabled (register I23 = "0"), set the key-on wakeup function to be invalid (register K22 = "0") before system enters to the RAM back-up mode. (refer to Figure 22①).

```

LA 0 ; (X0XX2)

TK2A ; Input of INT1 key-on wakeup invalid .. ①

DI

EPOF

POF ; RAM back-up

X: these bits are not used here.

```

Fig. 22 External 1 interrupt program example-2

- ③ Note on bit 2 of register I2 When the interrupt valid waveform of the P31/INT1 pin is changed with the bit 2 of register I2 in software, be careful about the following notes.

- Depending on the input state of the P31/INT1 pin, the external 1 interrupt request flag (EXF1) may be set when the bit 2 of register I2 is changed. In order to avoid the occurrence of an unexpected interrupt, clear the bit 1 of register V1 to "0" (refer to Figure 23①) and then, change the bit 2 of register I2. In addition, execute the SNZ1 instruction to clear the EXF1 flag to "0" after executing at least one instruction (refer to Figure 23②). Also, set the NOP instruction for the case when a skip is performed with the SNZ1 instruction (refer to Figure 23③).

Fig. 23 External 1 interrupt program example-3

#### **TIMERS**

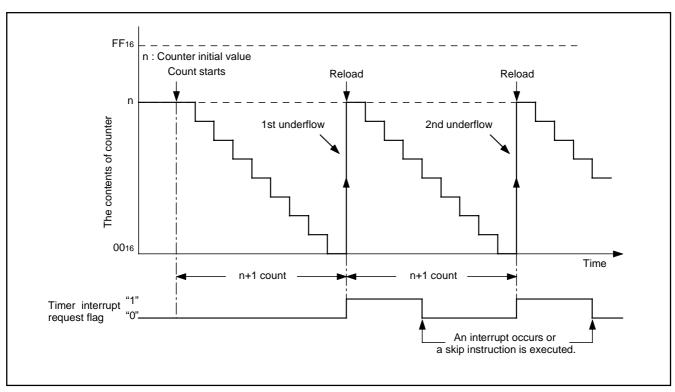

The 4518 Group has the following timers.

· Programmable timer

The programmable timer has a reload register and enables the frequency dividing ratio to be set. It is decremented from a setting value n. When it underflows (count to n + 1), a timer interrupt request flag is set to "1," new data is loaded from the reload register, and count continues (auto-reload function).

Fixed dividing frequency timer

The fixed dividing frequency timer has the fixed frequency dividing ratio (n). An interrupt request flag is set to "1" after every n count of a count pulse.

Fig. 24 Auto-reload function

The 4518 Group timer consists of the following circuits.

- Prescaler : 8-bit programmable timer

- Timer 1: 8-bit programmable timer

- Timer 2: 8-bit programmable timer

- Timer 3: 8-bit programmable timer

- Timer 4: 8-bit programmable timer

- Watchdog timer: 16-bit fixed dividing frequency timer

(Timers 1, 2, 3, and 4 have the interrupt function, respectively)

Prescaler and timers 1, 2, 3, and 4 can be controlled with the timer control registers PA, W1 to W6. The watchdog timer is a free counter which is not controlled with the control register. Each function is described below.

**PRELIMINARY**

Table 9 Function related timers

| Circuit   | Structure             | Count source               | Frequency dividing ratio | Use of output signal                 | Control register |

|-----------|-----------------------|----------------------------|--------------------------|--------------------------------------|------------------|

| Prescaler | 8-bit programmable    | Instruction clock (INSTCK) | 1 to 256                 | • Timer 1, 2, 3, amd 4 count sources | PA               |

|           | binary down counter   |                            |                          |                                      |                  |

| Timer 1   | 8-bit programmable    | Instruction clock (INSTCK) | 1 to 256                 | Timer 2 count source                 | W1               |

|           | binary down counter   | Prescaler output (ORCLK)   |                          | CNTR0 output                         | W2               |

|           | (link to INT0 input)  | XIN input                  |                          | Timer 1 interrupt                    | W5               |

|           | (period/pulse width   | CNTR0 input                |                          |                                      |                  |

|           | measurement function) |                            |                          |                                      |                  |

| Timer 2   | 8-bit programmable    | System clock (STCK)        | 1 to 256                 | Timer 3 count source                 | W2               |

|           | binary down counter   | Prescaler output (ORCLK)   |                          | CNTR0 output                         |                  |

|           |                       | Timer 1 underflow          |                          | Timer 2 interrupt                    |                  |

|           |                       | (T1UDF)                    |                          |                                      |                  |

|           |                       | PWM output (PWMOUT)        |                          |                                      |                  |

| Timer 3   | 8-bit programmable    | PWM output (PWMOUT)        | 1 to 256                 | CNTR1 output control                 | W3               |

|           | binary down counter   | Prescaler output (ORCLK)   |                          | Timer 3 interrupt                    |                  |

|           | (link to INT1 input)  | Timer 2 underflow          |                          |                                      |                  |

|           |                       | (T2UDF)                    |                          |                                      |                  |

|           |                       | CNTR1 input                |                          |                                      |                  |

| Timer 4   | 8-bit programmable    | XIN input                  | 1 to 256                 | Timer 2, 3 count source              | W4               |

|           | binary down counter   | Prescaler output (ORCLK)   |                          | CNTR1 output                         |                  |

|           | (PWM output function) |                            |                          | Timer 4 interrupt                    |                  |

| Watchdog  | 16-bit fixed dividing | Instruction clock (INSTCK) | 65534                    | System reset (count twice)           |                  |

| timer     | frequency             |                            |                          | WDF flag decision                    |                  |

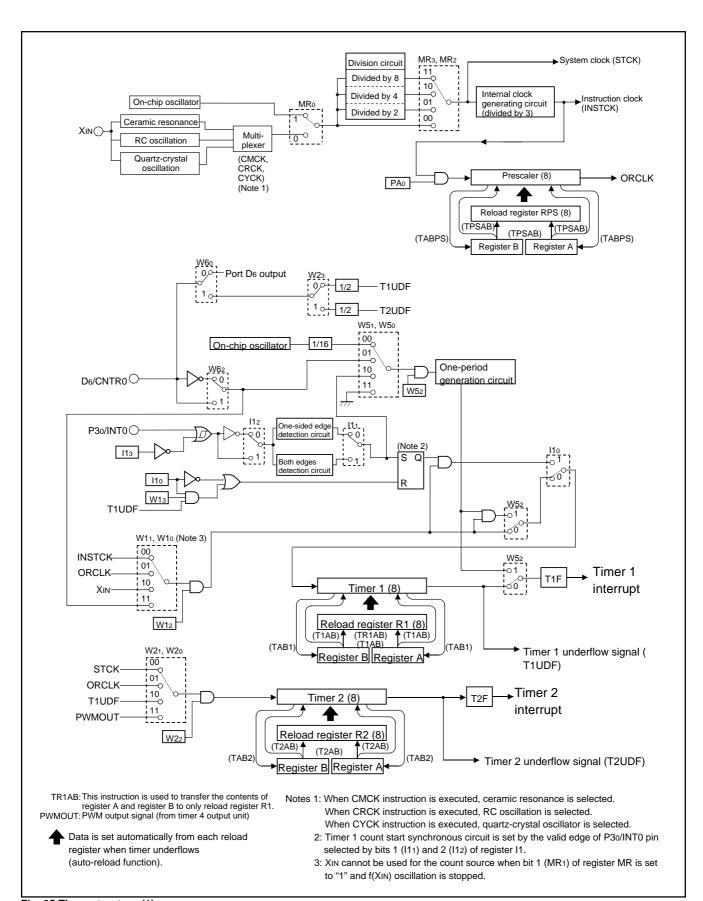

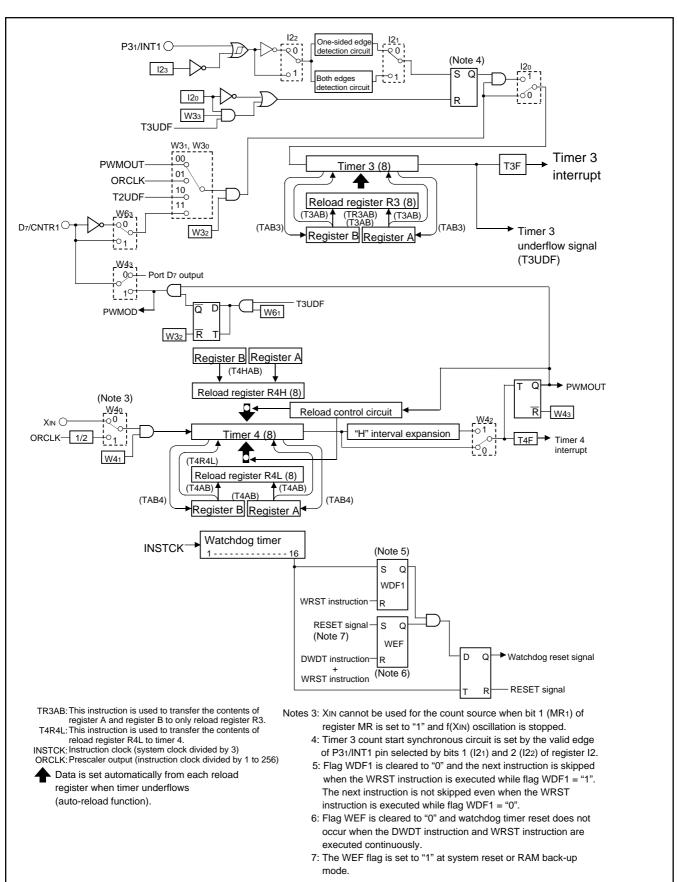

Fig. 25 Timer structure (1)

Fig. 26 Timer structure (2)

# **PRELIMINARY** Notice: This is not a final specification. Some parametric limits are subject to change.

#### Table 10 Timer related registers

| Timer control register PA |                       | at reset : 02 |                          | at RAM back-up : 02 | W<br>TPAA |

|---------------------------|-----------------------|---------------|--------------------------|---------------------|-----------|

| PA <sub>0</sub>           | Prescaler control bit | 0             | Stop (state initialized) |                     |           |

| '^0                       |                       | 1             | Operating                |                     |           |

|       | Timer control register W1                 |     | at reset : 00002 |                                          | at RAM back-up : state retained | R/W<br>TAW1/TW1A |

|-------|-------------------------------------------|-----|------------------|------------------------------------------|---------------------------------|------------------|

| W13   | Timer 1 count auto-stop circuit selection | (   | )                | Timer 1 count auto                       | -stop circuit not selected      | •                |

| 1110  | bit (Note 2)                              | •   | I                | Timer 1 count auto-stop circuit selected |                                 |                  |

| W12   | W10 T 4 11 11                             |     | )                | Stop (state retained)                    |                                 |                  |

| VV 12 | Timer 1 control bit                       | 1   |                  | Operating                                |                                 |                  |

|       |                                           | W11 | W10              | Count source                             |                                 |                  |

| W11   |                                           | 0   | 0                | Instruction clock (II                    | NSTCK)                          |                  |

|       | Timer 1 count source selection bits       | 0   | 1                | Prescaler output (ORCLK)                 |                                 |                  |

| W10   |                                           | 1   | 0                | XIN input                                |                                 |                  |

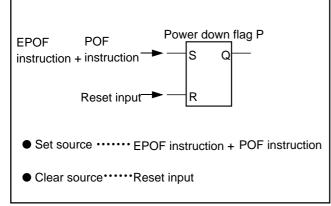

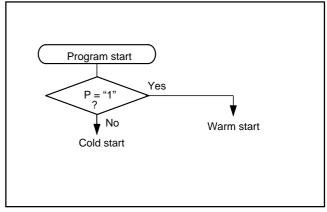

|       |                                           | 1   | 1                | CNTR0 input                              |                                 |                  |