# (Dot Matrix Liquid Crystal GraphicDisplay Column Driver)

# HITACHI

ADE-207-273(Z) '99.9 Rev. 0.0

### Description

HD61202U is a column (segment) driver for dot matrix liquid crystal graphic display systems. It stores the display data transferred from a 8-bit micro controller in the internal display RAM and generates dot matrix liquid crystal driving signals.

Each bit data of display RAM corresponds to on/off state of a dot of a liquid crystal display to provide more flexible than character display.

As it is internally equipped with 64 output drivers for display, it is available for liquid crystal graphic displays with many dots.

The HD61202U, which is produced in the CMOS process, can complete portable battery drive equipment in combination with a CMOS micro-controller, utilizing the liquid crystal display's low power dissipation.

Moreover it can facilitate dot matrix liquid crystal graphic display system configuration in combination with the row (common) driver HD61203U.

### Features

- Dot matrix liquid crystal graphic display column driver incorporating display RAM

- RAM data direct display by internal display RAM

- RAM bit data 1: On

- RAM bit data 0: Off

- Display RAM capacity: 512 bytes (4096 bits)

- 8-bit parallel interface

- Internal liquid crystal display driver circuit: 64

- Display duty cycle Drives liquid crystal panels with 1/32–1/64 duty cycle multiplexing

- Wide range of instruction function Display data read/write, display on/off, set address, set display start line, read status

- Power supply: V<sub>CC</sub>: 2.7V~5.5V

- Liquid crystal display driving voltage: 8V to 16V

### **Ordering Information**

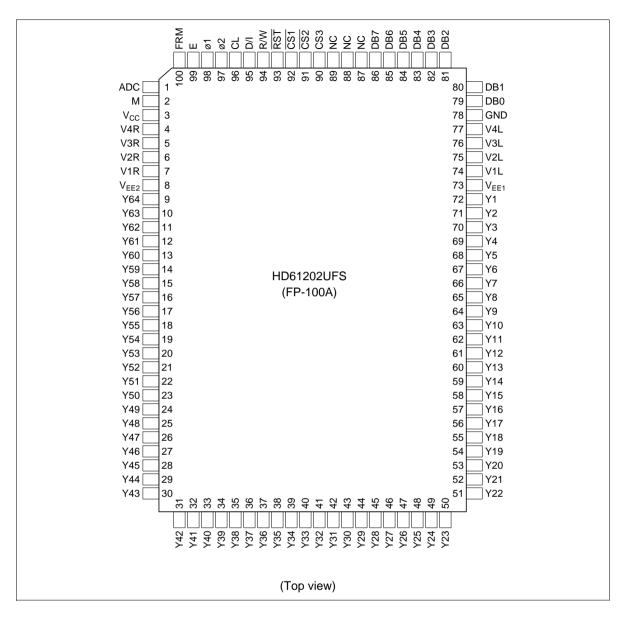

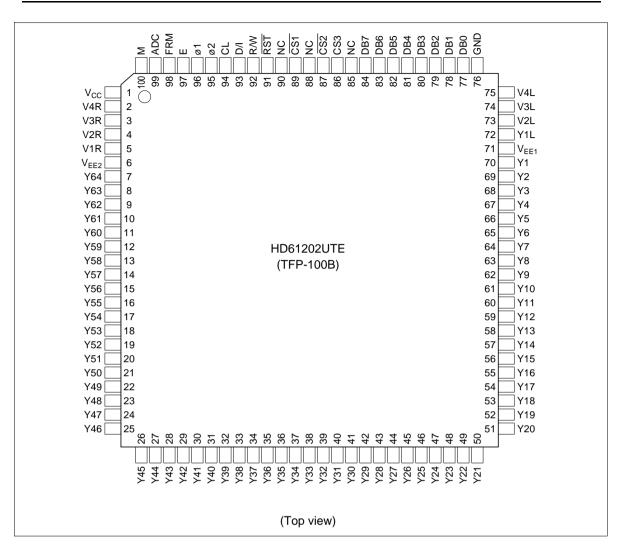

| Туре No.   | Package                             |

|------------|-------------------------------------|

| HD61202UFS | 100-pin plastic QFP (FP-100A)       |

| HD61202UTE | 100-pin thin plastic QFP (TFP-100B) |

| HCD61202U  | Chip                                |

### **Pin Arrangement**

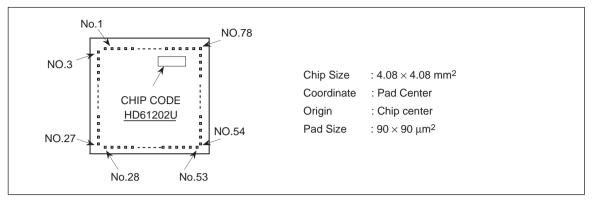

### HCD61202U PAD Arrangement

### HCD61202U Pad Location Coordinates

|     | PAD              | Coord |       |     | PAD  |       | dinate |     | PAD              |      | dinate |     | PAD  |       | dinate |

|-----|------------------|-------|-------|-----|------|-------|--------|-----|------------------|------|--------|-----|------|-------|--------|

| No. | Name             | Х     | Y     | No. | Name | Х     | Y      | No. | Name             | Х    | Y      | No. | Name | Х     | Y      |

| 1   | ADC              | -1493 | 1756  | 26  | Y47  | -1789 | -1508  | 51  | Y22              | 1452 | -1789  | 76  | V3L  | 1789  | 1442   |

| _ 2 | Μ                | -1649 | 1756  | 27  | Y46  | -1789 | -1653  | 52  | Y21              | 1604 | -1789  | _77 | V4L  | 1789  | 1590   |

| 3   | $V_{CC}$         | -1789 | 1689  | 28  | Y45  | -1764 | -1789  | 53  | Y20              | 1764 | -1789  | 78  | GND  | 1789  | 1756   |

| 4   | V4R              | -1789 | 1445  | 29  | Y44  | -1604 | -1789  | 54  | Y19              | 1789 | -1654  | 79  | DB0  | 1495  | 1756   |

| _ 5 | V3R              | -1789 | 1293  | 30  | Y43  | -1452 | -1789  | 55  | Y18              | 1789 | -1507  | 80  | DB1  | 1335  | 1756   |

| 6   | V2R              | -1789 | 1148  | 31  | Y42  | -1312 | -1789  | 56  | Y17              | 1789 | -1369  | 81  | DB2  | 1176  | 1756   |

| 7   | V1R              | -1789 | 1011  | 32  | Y41  | -1171 | -1789  | 57  | Y16              | 1789 | -1230  | 82  | DB3  | 1016  | 1756   |

| 8   | $V_{\text{EE2}}$ | -1789 | 869   | 33  | Y40  | -976  | -1789  | 58  | Y15              | 1789 | -1100  | 83  | DB4  | 854   | 1756   |

| 9   | Y64              | -1789 | 721   | 34  | Y39  | -846  | -1789  | 59  | Y14              | 1789 | -970   | 84  | DB5  | 694   | 1756   |

| 10  | Y63              | -1789 | 591   | 35  | Y38  | -716  | -1789  | 60  | Y13              | 1789 | -840   | 85  | DB6  | 535   | 1756   |

| 11  | Y62              | -1789 | 461   | 36  | Y37  | -586  | -1789  | 61  | Y12              | 1789 | -710   | 86  | DB7  | 375   | 1756   |

| 12  | Y61              | -1789 | 331   | 37  | Y36  | -456  | -1789  | 62  | Y11              | 1789 | -580   | 87  | NC   |       |        |

| 13  | Y60              | -1789 | 201   | 38  | Y35  | -326  | -1789  | 63  | Y10              | 1789 | -450   | 88  | NC   |       |        |

| 14  | Y59              | -1789 | 71    | 39  | Y34  | -196  | -1789  | 64  | Y9               | 1789 | -320   | 89  | NC   |       |        |

| 15  | Y58              | -1789 | -60   | 40  | Y33  | -65   | -1789  | 65  | Y8               | 1789 | -190   | 90  | CS3  | 218   | 1756   |

| 16  | Y57              | -1789 | -190  | 41  | Y32  | 65    | -1789  | 66  | Y7               | 1789 | -60    | 91  | CS2  | 62    | 1756   |

| 17  | Y56              | -1789 | -320  | 42  | Y31  | 195   | -1789  | 67  | Y6               | 1789 | 71     | 92  | CS1  | -94   | 1756   |

| 18  | Y55              | -1789 | -450  | 43  | Y30  | 325   | -1789  | 68  | Y5               | 1789 | 201    | 93  | RST  | -249  | 1756   |

| 19  | Y54              | -1789 | -580  | 44  | Y29  | 455   | -1789  | 69  | Y4               | 1789 | 331    | 94  | R/W  | -405  | 1756   |

| 20  | Y53              | -1789 | -710  | 45  | Y28  | 585   | -1789  | 70  | Y3               | 1789 | 461    | 95  | D/I  | -560  | 1756   |

| 21  | Y52              | -1789 | -840  | 46  | Y27  | 715   | -1789  | 71  | Y2               | 1789 | 591    | 96  | CL   | -716  | 1756   |

| 22  | Y51              | -1789 | -970  | 47  | Y26  | 845   | -1789  | 72  | Y1               | 1789 | 721    | 97  | ø2   | -871  | 1756   |

| 23  | Y50              | -1789 | -1100 | 48  | Y25  | 975   | -1789  | 73  | $V_{\text{EE1}}$ | 1789 | 1024   | 98  | ø1   | -1027 | 1756   |

| 24  | Y49              | -1789 | -1230 | 49  | Y24  | 1170  | -1789  | 74  | V1L              | 1789 | 1153   | 99  | E    | -1182 | 1756   |

| 25  | Y48              | -1789 | -1369 | 50  | Y23  | 1311  | -1789  | 75  | V2L              | 1789 | 1293   | 100 | FRM  | -1338 | 1756   |

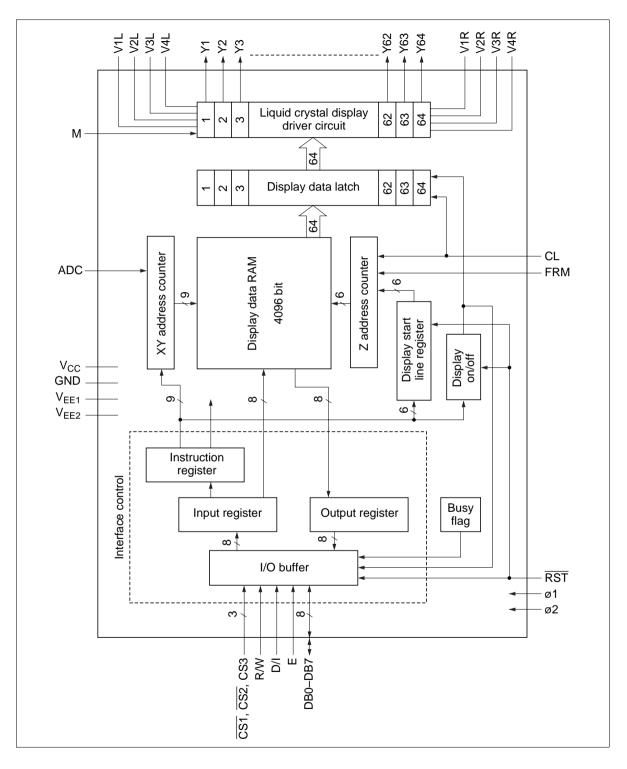

### **Block Diagram**

| Terminal<br>Name     | Number of<br>Terminals | I/O | Connected to | Functions                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------|------------------------|-----|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>cc</sub>      | 2                      |     | Power supply | Power supply for internal logic.                                                                                                                                                                                                                                                                                                                                                      |

| GND                  |                        |     |              | Recommended voltage is:                                                                                                                                                                                                                                                                                                                                                               |

|                      |                        |     |              | GND = 0V<br>$V_{cc} = 2.7$ to 5.5V                                                                                                                                                                                                                                                                                                                                                    |

| $V_{\text{EE1}}$     | 2                      |     | Power supply | Power supply for liquid crystal display drive circuit.                                                                                                                                                                                                                                                                                                                                |

| V <sub>EE2</sub>     |                        |     |              | Recommended power supply voltage is $V_{cc}-V_{EE} = 8$ to<br>16V. Connect the same power supply to $V_{EE1}$ and $V_{EE2}$ .<br>$V_{EE1}$ and $V_{EE2}$ are not connected each other in the LSI.                                                                                                                                                                                     |

| V1L, V1R             | 8                      |     | Power supply | Power supply for liquid crystal display drive.                                                                                                                                                                                                                                                                                                                                        |

| V2L, V2R<br>V3L, V3R |                        |     |              | Apply the voltage specified depending on liquid crystals within the limit of $V_{\text{EE}}$ through $V_{\text{CC}}.$                                                                                                                                                                                                                                                                 |

| V4L, V4R             |                        |     |              | V1L (V1R), V2L (V2R): Selection level<br>V3L (V3R), V4L (V4R): Non-selection level                                                                                                                                                                                                                                                                                                    |

|                      |                        |     |              | Power supplies connected with V1L and V1R (V2L & V2R, V3L & V3R, V4L & V4R) should have the same voltages.                                                                                                                                                                                                                                                                            |

| CS1                  | 3                      | I   | MPU          | Chip selection.                                                                                                                                                                                                                                                                                                                                                                       |

| CS2<br>CS3           |                        |     |              | Data can be input or output when the terminals are in the following conditions:                                                                                                                                                                                                                                                                                                       |

|                      |                        |     |              | Terminal name CS1 CS2 CS3                                                                                                                                                                                                                                                                                                                                                             |

|                      |                        |     |              | Condition L L H                                                                                                                                                                                                                                                                                                                                                                       |

| E                    | 1                      | I   | MPU          | Enable.                                                                                                                                                                                                                                                                                                                                                                               |

|                      |                        |     |              | At write (R/W = low): Data of DB0 to DB7 is latched at the foll of $\Gamma$                                                                                                                                                                                                                                                                                                           |

|                      |                        |     |              | the fall of E.<br>At read (R/W = high):Data appears at DB0 to DB7 while<br>E is at high level.                                                                                                                                                                                                                                                                                        |

| R/W                  | 1                      | I   | MPU          | Read/write.                                                                                                                                                                                                                                                                                                                                                                           |

|                      |                        |     |              | $\label{eq:RW} \begin{array}{l} R/W = High: \ Data \ appears \ at \ DB0 \ to \ DB7 \ and \ can \ be \\ read \ by \ the \ MPU. \\ When \ E = high, \ \overline{CS1}, \ \overline{CS2} = low \ and \\ CS3 = high. \\ R/W = Low: \ \begin{array}{c} DB0 \ to \ DB7 \ can \ accept \ at \ fall \ of \ E \ when \\ \overline{CS1}, \ \overline{CS2} = low \ and \ CS3 = high. \end{array}$ |

| D/I                  | 1                      | I   | MPU          | Data/instruction.                                                                                                                                                                                                                                                                                                                                                                     |

|                      |                        |     |              | D/I = High: Indicates that the data of DB0 to DB7 is                                                                                                                                                                                                                                                                                                                                  |

|                      |                        |     |              | display data.<br>D/I = Low: Indicates that the data of DB0 to DB7 is<br>display control data.                                                                                                                                                                                                                                                                                         |

# **Terminal Functions**

| Terminal<br>Name | Number of<br>Terminals | I/O | Connected to          | Functions                                                                                                                                            |

|------------------|------------------------|-----|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC              | 1                      | I   | V <sub>cc</sub> /GND  | Address control signal to determine the relation between<br>Y address of display RAM and terminals from which the<br>data is output.                 |

|                  |                        |     |                       | ADC = High: Y1: H'0, Y64: H'63<br>ACD = Low: Y64: H'0, Y1: H'63                                                                                      |

| DB0–DB7          | 8                      | I/O | MPU                   | Data bus, three-state I/O common terminal.                                                                                                           |

| М                | 1                      | I   | HD61203U              | Switch signal to convert liquid crystal drive waveform into AC.                                                                                      |

| FRM              | 1                      | Ι   | HD61203U              | Display synchronous signal (frame signal).                                                                                                           |

|                  |                        |     |                       | Presets the 6-bit display line counter and synchronizes<br>the common signal with the frame timing when the FRM<br>signal becomes high.              |

| CL               | 1                      | I   | HD61203U              | Synchronous signal to latch display data. The rising CL signal increments the display output address counter and latches the display data.           |

| ø1, ø2           | 2                      | Ι   | HD61203U              | 2-phase clock signal for internal operation.                                                                                                         |

|                  |                        |     |                       | The ø1 and ø2 clocks are used to perform operations (I/O of display data and execution of instructions) other than display.                          |

| Y1–Y64           | 64                     | 0   | Liquid crystal        | Liquid crystal display column (segment) drive output.                                                                                                |

|                  |                        |     | display               | The outputs at these pins are at the light-on level when<br>the display RAM data is 1, and at the light-off level when<br>the display RAM data is 0. |

|                  |                        |     |                       | Relation among output level, M, and display data (D) is                                                                                              |

|                  |                        |     |                       | as follows:<br>M1_0                                                                                                                                  |

|                  |                        |     |                       | D 1 0 1 0                                                                                                                                            |

|                  |                        |     |                       | Output V1 V3 V2 V4<br>level V1 V3 V2 V4                                                                                                              |

| RST              | 1                      | I   | MPU or<br>external CR | The following registers can be initialized by setting the $\overline{\text{RST}}$ signal to low level.                                               |

|                  |                        |     |                       | 1. On/off register 0 set (display off)                                                                                                               |

|                  |                        |     |                       | <ol> <li>Display start line register line 0 set (displays from line 0)</li> </ol>                                                                    |

|                  |                        |     |                       | After releasing reset, this condition can be changed only by instruction.                                                                            |

| NC               | 3                      |     | Open                  | Unused terminals. Don't connect any lines to these terminals.                                                                                        |

Note: 1 corresponds to high level in positive logic.

### **Function of Each Block**

#### **Interface Control**

I/O Buffer: Data is transferred through 8 data bus lines (DB0–DB7).

DB7: MSB (most significant bit) DB0: LSB (least significant bit)

Data can neither be input nor output unless  $\overline{CS1}$  to CS3 are in the active mode. Therefore, when  $\overline{CS1}$  to CS3 are not in active mode it is useless to switch the signals of input terminals except  $\overline{RST}$  and ADC; that is namely, the internal state is maintained and no instruction excutes. Besides, pay attention to  $\overline{RST}$  and ADC which operate irrespectively of  $\overline{CS1}$  to CS3.

**Register:** Both input register and output register are provided to interface to an MPU whose speed is different from that of internal operation. The selection of these registers depend on the combination of R/W and D/I signals (Table 1).

1. Input register

The input register is used to store data temporarily before writing it into display data RAM.

The data from MPU is written into input register, then into display data RAM automatically by internal operation. When  $\overline{CS1}$  to CS3 are in the active mode and D/I and R/W select the input register as shown in Table 1, data is latched at the fall of the E signal.

2. Output register

The output register is used to store data temporarily that is read from display data RAM. To read out the data from the output register,  $\overline{CS1}$  to CS3 should be in the active mode and both D/I and R/W should be 1. With the read display data instruction, data stored in the output register is output while E is high level. Then, at the fall of E, the display data at the indicated address is latched into the output register and the address is increased by 1.

The contents in the output register are rewritten by the read display data instruction, but are held by address set instruction, etc.

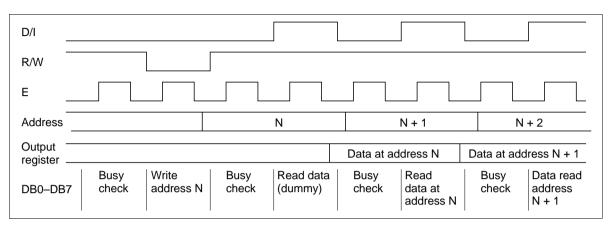

Therefore, the data of the specified address cannot be output with the read display data instruction right after the address is set, but can be output at the second read of data. That is to say, one dummy read is necessary. Figure 1 shows the MPU read timing.

| D/I | R/W | Operation                                                                                                |

|-----|-----|----------------------------------------------------------------------------------------------------------|

| 1   | 1   | Reads data out of output register as internal operation (display data RAM $\rightarrow$ output register) |

| 1   | 0   | Writes data into input register as internal operation (input register $\rightarrow$ display data RAM)    |

| 0   | 1   | Busy check. Read of status data.                                                                         |

| 0   | 0   | Instruction                                                                                              |

#### Table 1 Register Selection

#### **Busy Flag**

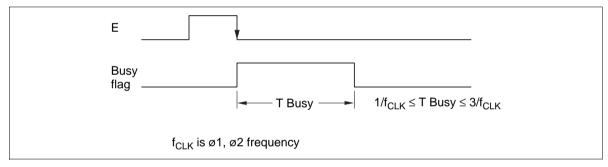

Busy flag = 1 indicates that HD61202U is operating and no instructions except status read instruction can be accepted. The value of the busy flag is read out on DB7 by the status read instruction. Make sure that the busy flag is reset (0) before issuing instructions.

Figure 1 MPU Read Timing

Figure 2 Busy Flag

#### **Display On/Off Flip/Flop**

The display on/off flip/flop selects one of two states, on state and off state of segments Y1 to Y64. In on state, the display data corresponding to that in RAM is output to the segments. On the other hand, the display data at all segments disappear in off state independent of the data in RAM. It is controlled by display on/off instruction.  $\overline{RST}$  signal = 0 sets the segments in off state. The status of the flip/flop is output to DB5 by status read instruction. Display on/off instruction does not influence data in RAM. To control display data latch by this flip/flop, CL signal (display synchronous signal) should be input correctly.

#### **Display Start Line Register**

The display start line register specifies the line in RAM which corresponds to the top line of LCD panel, when displaying contents in display data RAM on the LCD panel. It is used for scrolling of the screen.

6-bit display start line information is written into this register by the display start line set instruction. When high level of the FRM signal starts the display, the information in this register is transferred to the Z address counter, which controls the display address, presetting the Z address counter.

#### X, Y Address Counter

A 9-bit counter which designates addresses of the internal display data RAM. X address counter (upper 3 bits) and Y address counter (lower 6 bits) should be set to each address by the respective instructions.

1. X address counter

Ordinary register with no count functions. An address is set by instruction.

2. Y address counter

An Address is set by instruction and is increased by 1 automatically by R/W operations of display data. The Y address counter loops the values of 0 to 63 to count.

#### **Display Data RAM**

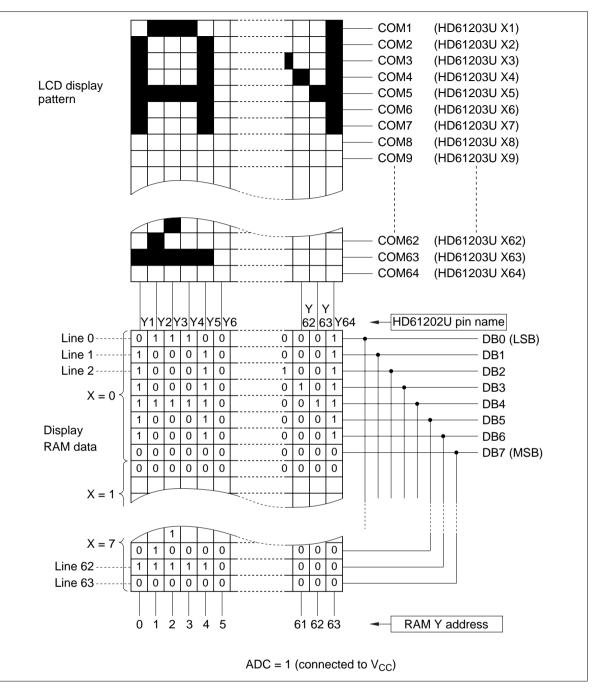

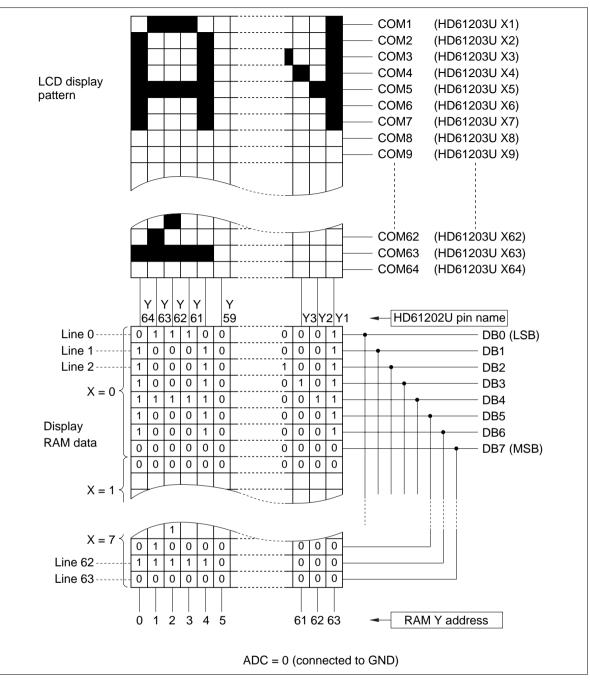

Stores dot data for display. 1-bit data of this RAM corresponds to light on (data = 1) and light off (data = 0) of 1 dot in the display panel. The correspondence between Y addresses of RAM and segment pins can be reversed by ADC signal.

As the ADC signal controls the Y address counter, reversing of the signal during the operation causes malfunction and destruction of the contents of register and data of RAM. Therefore, never fail to connect ADC pin to  $V_{CC}$  or GND when using.

Figure 3 shows the relations between Y address of RAM and segment pins in the cases of ADC = 1 and ADC = 0 (display start line = 0, 1/64 duty cycle).

Figure 3 Relation between RAM Data and Display

Figure 3 Relation between RAM Data and Display (cont)

#### Z Address Counter

The Z address counter generates addresses for outputting the display data synchronized with the common signal. This counter consists of 6 bits and counts up at the fall of the CL signal. At the high level of FRM, the contents of the display start line register is present at the Z counter.

#### **Display Data Latch**

The display data latch stores the display data temporarily that is output from display data RAM to the liquid crystal driving circuit. Data is latched at the rise of the CL signal. The display on/off instruction controls the data in this latch and does not influence data in dicsplay data RAM.

#### Liquid Crystal Display Driver Circuit

The combination of latched display data and M signal causes one of the 4 liquid crystal driver levels, V1, V2, V3, and V4 to be output.

#### Reset

The system can be initialized by setting  $\overline{RST}$  terminal at low level when turning power on.

- 1. Display off

- 2. Set display start line register line 0.

While  $\overline{RST}$  is low level, no instruction except status read can be accepted. Therefore, execute other instructions after making sure that DB4 = 0 (clear RESET) and DB7 = 0 (ready) by status read instruction.

### **Display Control Instructions**

#### Outline

Table 2 shows the instructions. Read/write (R/W) signal, data/instruction (D/I) signal, and data bus signals (DB0 to DB7) are also called instructions because the internal operation depends on the signals from the MPU.

These explanations are detailed in the following pages. Generally, there are following three kinds of instructions:

- 1. Instruction to set addresses in the internal RAM

- 2. Instruction to transfer data from/to the internal RAM

- 3. Other instructions

In general use, the second type of instruction is used most frequently. Since Y address of the internal RAM is increased by 1 automatically after writing (reading) data, the program can be shortened. During the execution of an instruction, the system cannot accept instructions other than status read instruction. Send instructions from MPU after making sure that the busy flag is 0, which is proof that an instruction is not being executed.

|                                                                          |                                  |         |                                                                            |              | ŏ           | Code                      |              |             |      |     |                                                                                                                                    |                     |

|--------------------------------------------------------------------------|----------------------------------|---------|----------------------------------------------------------------------------|--------------|-------------|---------------------------|--------------|-------------|------|-----|------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Instructions                                                             | RW                               | D/I     | DB7                                                                        | DB6          | DB5         | DB4                       | DB3          | DB2         | DB1  | DB0 | Functions                                                                                                                          |                     |

| Display on/off                                                           | 0                                | 0       | 0                                                                          | 0            | <del></del> | <del>~</del>              | <del>~</del> | <del></del> | -    | 1/0 | Controls display on/off. RAM data and internal status are not affected. 1: on, 0: off.                                             | nal                 |

| Display start line                                                       | 0                                | 0       | -                                                                          | <del>~</del> | Displa      | Display start line (0–63) | line (0      | -63)        |      |     | Specifies the RAM line displayed at the top of the screen.                                                                         | of the              |

| Set page (X address)                                                     | 0                                | 0       | -                                                                          | 0            | ~           | -                         | -            | Page (0–7)  | (07) |     | Sets the page (X address) of RAM at the page (X address) register.                                                                 | age                 |

| Set Y address                                                            | 0                                | 0       | 0                                                                          | ~            | Y add       | Y address (0–63)          | H63)         |             |      |     | Sets the Y address in the Y address counter.                                                                                       | er.                 |

| Status read                                                              | -                                | 0       | Busy                                                                       | 0            | /NO         | Reset 0                   | 0            | 0           | 0    | 0   | Reads the status.                                                                                                                  |                     |

|                                                                          |                                  |         |                                                                            |              | OFF         |                           |              |             |      |     | RESET 1: Reset<br>0: Normal                                                                                                        |                     |

|                                                                          |                                  |         |                                                                            |              |             |                           |              |             |      |     | ON/OFF 1: Display off<br>0: Display on                                                                                             |                     |

|                                                                          |                                  |         |                                                                            |              |             |                           |              |             |      |     | Busy 1: Internal operation<br>0: Ready                                                                                             |                     |

| Write display data                                                       | 0                                | -       | Write data                                                                 | data         |             |                           |              |             |      |     | Writes data DB0 (LSB)Has access to the<br>address of the display<br>data bus into displayRAMRAM specified in<br>advance. After the | he<br>display<br>in |

| Read display data                                                        | -                                | ~       | Read data                                                                  | data         |             |                           |              |             |      |     | Reads data DB0 (LSB) access, Y address is to DB7 (MSB) from the display RAM to the data bus.                                       | ess is              |

| Note: Busy time varies with the $(1/f_{CLK} \le T_{BUSY} \le 3/f_{CLK})$ | s with th<br>≤ 3/f <sub>CL</sub> | he freq | the frequency (f <sub>CLK</sub> ) of $\emptyset$ 1, and $\emptyset$ 2.:Lk) | cLK) of      | ø1, an      | d ø2.                     |              |             |      |     |                                                                                                                                    |                     |

### Table 2Instructions

16

#### **Detailed Explanation**

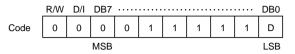

#### **Display On/Off**

The display data appears when D is 1 and disappears when D is 0. Though the data is not on the screen with D = 0, it remains in the display data RAM. Therefore, you can make it appear by changing D = 0 into D = 1.

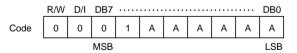

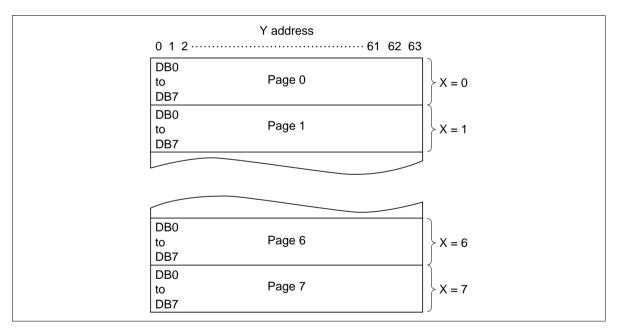

#### **Display Start Line**

|      | R/W | D/I | DB7 |   |   |   | •••• |   |   | DB0 |  |

|------|-----|-----|-----|---|---|---|------|---|---|-----|--|

| Code | 0   | 0   | 1   | 1 | А | А | А    | А | А | А   |  |

|      |     |     | MSB |   |   |   |      |   |   | LSB |  |

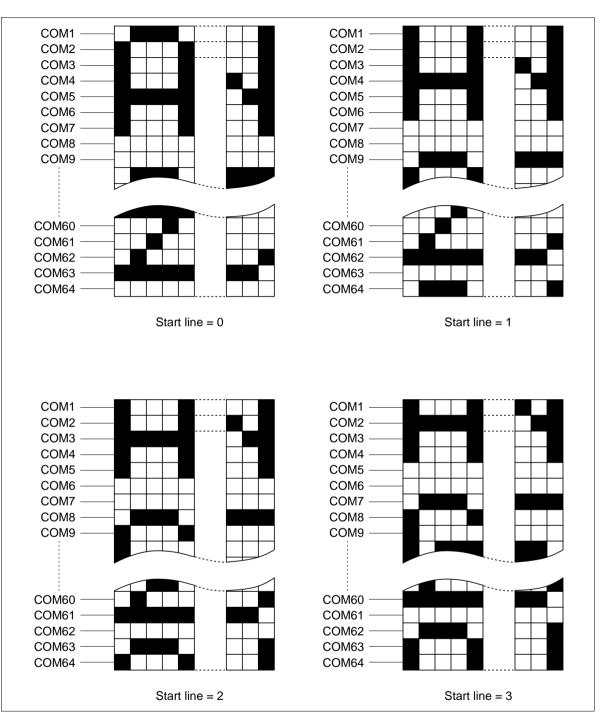

Z address AAAAAA (binary) of the display data RAM is set in the display start line register and displayed at the top of the screen. Figure 4 shows examples of display (1/64 duty cycle) when the start line = 0-3. When the display duty cycle is 1/64 or more (ex. 1/32, 1/24 etc.), the data of total line number of LCD screen, from the line specified by display start line instruction, is displayed.

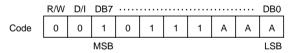

#### Set Page (X Address)

X address AAA (binary) of the display data RAM is set in the X address register. After that, writing or reading to or from MPU is executed in this specified page until the next page is set. See Figure 5.

#### Set Y Address

Y address AAAAAA (binary) of the display data RAM is set in the Y address counter. After that, Y address counter is increased by 1 every time the data is written or read to or from MPU.

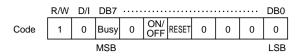

#### Status Read

#### • Busy

When busy is 1, the LSI is executing internal operations. No instructions are accepted while busy is 1, so you should make sure that busy is 0 before writing the next instruction.

• ON/OFF

Shows the liquid crystal display conditions: on condition or off condition.

When on/off is 1, the display is in off condition.

When on/off is 0, the display is in on condition.

RESET

RESET = 1 shows that the system is being initialized. In this condition, no instructions except status read can be accepted.

RESET = 0 shows that initializing has finished and the system is in the usual operation condition.

Figure 4 Relation between Start Line and Display

#### Write Display Data

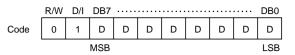

Writes 8-bit data DDDDDDDD (binary) into the display data RAM. Then Y address is increased by 1 automatically.

#### **Read Display Data**

|      | R/W | D/I | DB7 | •••• |   | • • • • • • | • • • • • • | ••••• | • • • • • | DB0 |  |

|------|-----|-----|-----|------|---|-------------|-------------|-------|-----------|-----|--|

| Code | 1   | 1   | D   | D    | D | D           | D           | D     | D         | D   |  |

|      |     |     | MSB |      |   |             |             |       |           | LSB |  |

Reads out 8-bit data DDDDDDDD (binary) from the display data RAM. Then Y address is increased by 1 automatically.

One dummy read is necessary right after the address setting. For details, refer to the explanation of output register in "Function of Each Block".

Figure 5 Address Configuration of Display Data RAM

### Use of HD61202U

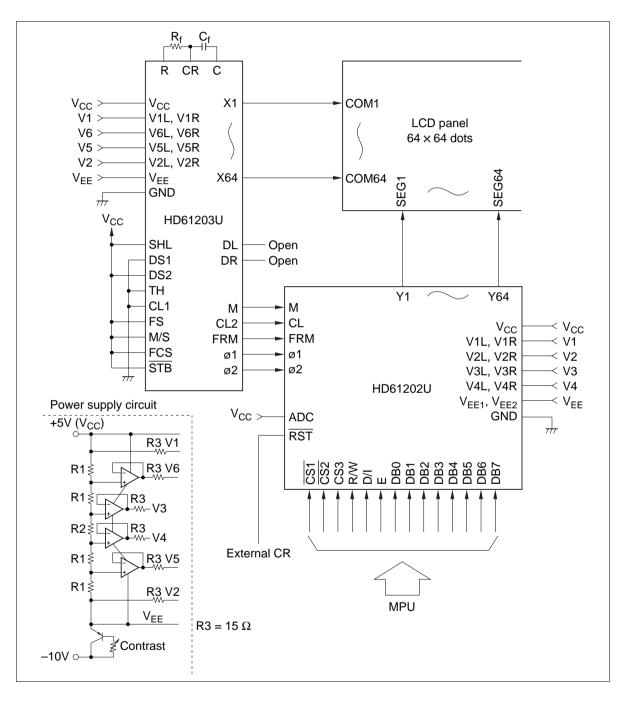

#### Interface with HD61203 (1/64 Duty Cycle)

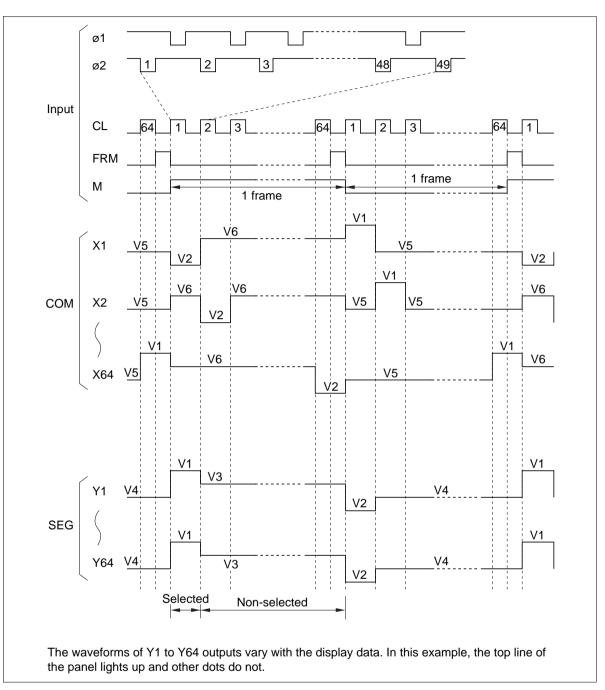

Figure 6 LCD Driver Timing Chart (1/64 Duty Cycle)

# Interface with CPU

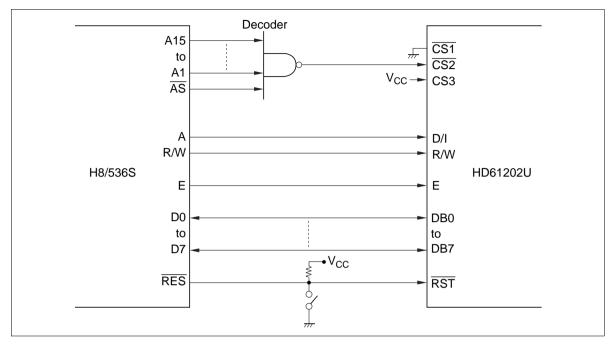

### 1. Example of Connection with H8/536S

Figure 7 Example of Connection with H8/536S

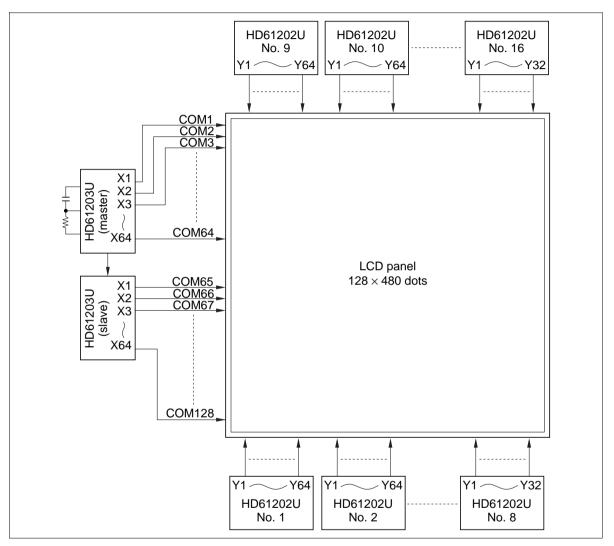

### **Example of Application**

In this example, two HD61203s output the equivalent waveforms. So, stand-alone operation is possible. In this case, connect COM1 and COM65 to X1, COM2 and COM66 to X2, ..., and COM64 and COM128 to X64. However, for the large screen display, it is better to drive in 2 rows as in this example to guarantee the display quality.

Figure 8 Application Example

### **Absolute Maximum Ratings**

| Item                  | Symbol                               | Value                                                                  | Unit | Note |

|-----------------------|--------------------------------------|------------------------------------------------------------------------|------|------|

| Supply voltage        | V <sub>cc</sub>                      | -0.3 to +7.0                                                           | V    | 2    |

|                       | $V_{\text{EE1}}$<br>$V_{\text{EE2}}$ | $V_{cc}$ – 17.0 to $V_{cc}$ + 0.3                                      | V    | 3    |

| Terminal voltage (1)  | VT1                                  | $V_{\mbox{\scriptsize EE}}$ – 0.3 to $V_{\mbox{\scriptsize CC}}$ + 0.3 | V    | 4    |

| Terminal voltage (2)  | VT2                                  | -0.3 to V <sub>cc</sub> + 0.3                                          | V    | 2, 5 |

| Operating temperature | T <sub>opr</sub>                     | -30 to +75                                                             | °C   |      |

| Storage temperature   | T <sub>stg</sub>                     | -55 to +125                                                            | °C   |      |

Notes: 1. LSIs may be destroyed if they are used beyond the absolute maximum ratings. In ordinary operation, it is desirable to use them within the recommended operation conditions. Useing them beyond these conditions may cause malfunction and poor reliability.

2. All voltage values are referenced to GND = 0V.

3. Apply the same supply voltage to  $V_{\mbox{\scriptsize EE1}}$  and  $V_{\mbox{\scriptsize EE2}}.$

4. Applies to V1L, V2L, V3L, V4L, V1R, V2R, V3R, and V4R.

Maintain

$V_{\text{CC}} \geq V1L = V1R \geq V3L = V3R \geq V4L = V4R \geq V2L = V2R \geq V_{\text{EE}}$

5. Applies to M, FRM, CL, RST, ADC, ø1, ø2, CS1, CS2, CS3, E, R/W, D/I, and DB0–DB7.

Electrical Characteristics (GND = 0V,  $V_{CC} = 2.7 \sim 5.5V$ ,  $V_{CC} - V_{EE} = 8.0$  to 16.0V, Ta =  $-30 \sim +75^{\circ}C$ )<sup>\*8</sup>

|                                       |                     |              | Limi | t               |      |                                                                     |       |

|---------------------------------------|---------------------|--------------|------|-----------------|------|---------------------------------------------------------------------|-------|

| Item                                  | Symbol              | Min          | Тур  | Max             | Unit | <b>Test Condition</b>                                               | Notes |

| Input high voltage                    | VIHC                | $0.7 V_{cc}$ | _    | V <sub>cc</sub> | V    | $V_{cc} = 2.7V \sim 5.5V$                                           | 1     |

|                                       | VIHT                | $0.7 V_{cc}$ |      | $V_{cc}$        | V    | $V_{cc} = 2.7V \sim 4.5V$                                           | 2     |

|                                       |                     | 2.0          |      | $V_{cc}$        | V    | $V_{cc} = 4.5V \sim 5.5V$                                           | 2     |

| Input low voltage                     | VILC                | 0.0          |      | $0.3V_{cc}$     | V    | $V_{cc} = 2.7V \sim 5.5V$                                           | 1     |

|                                       | VILT                | 0.0          |      | 0.5             | V    | $V_{cc} = 2.7V \sim 4.5V$                                           | 2     |

|                                       |                     | 0.0          |      | 0.8             | V    | $V_{cc} = 4.5V \sim 5.5V$                                           | 2     |

| Output high voltage                   | VOH                 | $0.75V_{cc}$ | —    | —               | V    | I <sub>OH</sub> = -100 μA,<br>V <sub>CC</sub> = 2.7V~4.5V           | 3     |

|                                       |                     | 2.4          | —    | —               | V    | I <sub>OH</sub> = -205 μA<br>V <sub>CC</sub> = 4.5V~5.5V            | 3     |

| Output low voltage                    | VOL                 | _            |      | $0.2V_{\rm cc}$ | V    | I <sub>OL</sub> = 100 uA,<br>V <sub>CC</sub> = 2.7V~4.5V            | 3     |

|                                       |                     | _            | _    | 0.4             | V    | I <sub>OL</sub> = 1.2mA,<br>V <sub>CC</sub> = 4.5V~5.5V             | 3     |

| Input leakage current                 | I <sub>IL</sub>     | -1           | _    | 1               | μΑ   | $Vin = GND \sim V_{cc}$                                             | 4     |

| Three-state (off) input current       | I <sub>TSL</sub>    | -5           | —    | 5               | μΑ   | $Vin = GND \sim V_{cc}$                                             | 5     |

| Liquid crystal supply leakage current | I <sub>LSL</sub>    | -2           | —    | 2               | μΑ   | $Vin = V_{EE} - V_{CC}$                                             | 6     |

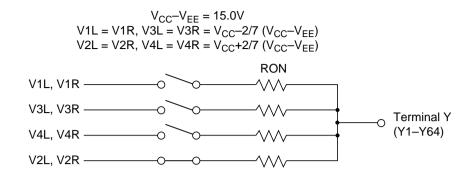

| Driver on resistance                  | R <sub>on</sub>     | _            | _    | 7.5             | kΩ   | $\pm I_{LOAD} = 0.1 \text{ mA},$<br>$V_{CC} - V_{EE} = 15 \text{V}$ | 8     |

| Dissipation current                   | I <sub>cc</sub> (1) |              | _    | 100             | μΑ   | During display                                                      | 7     |

|                                       | I <sub>cc</sub> (2) | _            | —    | 500             | μΑ   | During access,<br>Cycle = 1MHz                                      | 7     |

Notes: 1. Applies to M, FRM, CL, RST, ø1, and ø2.

2. Applies to CS1, CS2, CS3, E, R/W, D/I, and DB0-DB7.

- 3. Applies to DB0–DB7.

- 4. Applies to terminals except for DB0–DB7.

- 5. Applies to DB0–DB7 at high impedance.

- 6. Applies to V1L–V4L and V1R–V4R.

7. Specified when LCD is in 1/64 duty cycle mode.

Operation frequency:  $f_{CLK} = 250$  kHz (ø1 and ø2 frequency)

Frame frequency:  $f_{M} = 70 \text{ Hz}$  (FRM frequency)

Specified in the state of

Output terminal: Not loaded

Input level:  $VIH = V_{cc} (V)$

VIL = GND(V)

Measured at  $V_{\rm cc}$  terminal

8. Specified at +75°C for die products.

Resistance between terminal Y and terminal V (one of V1L, V1R, V2L, V2R, V3L, V3R, V4L, and V4R) when load current flows through one of the terminals Y1 to Y64. This value is specified under the following condition:

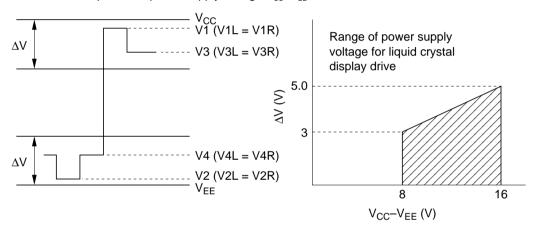

The following is a description of the range of power supply voltage for liquid crystal display drive. Apply positive voltage to V1L = V1R and V3L = V3R and negative voltage to V2L = V2R and V4L = V4R within the  $\Delta V$  range. This range allows stable impedance on driver output (RON). Notice that  $\Delta V$  depends on power supply voltage V<sub>CC</sub>-V<sub>FE</sub>.

Correlation between driver output waveform and power supply voltages for liquid crystal display drive Correlation between power supply voltage V\_{CC}–V\_{EE} and  $\Delta V$

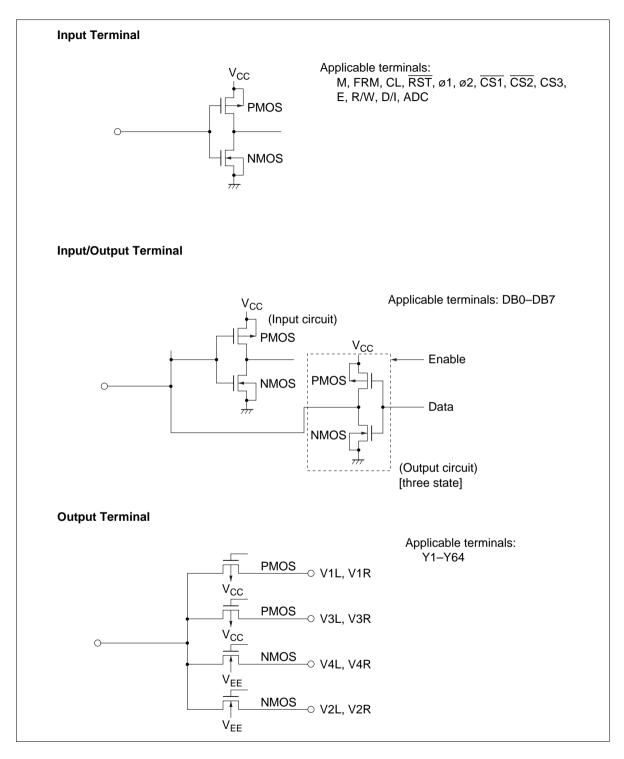

### **Terminal Configuration**

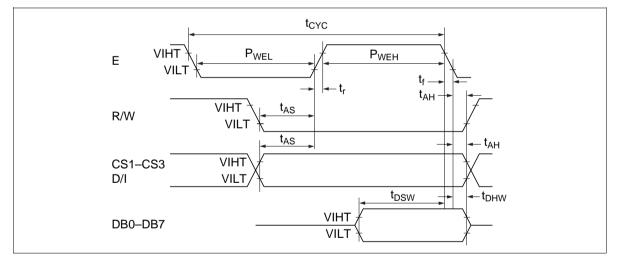

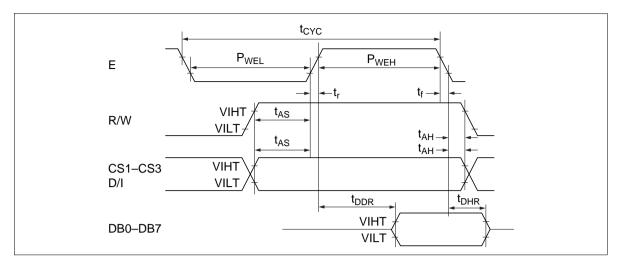

#### **Interface AC Characteristics**

| Item                   | Symbol           | Min  | Тур | Max | Unit | Note             |

|------------------------|------------------|------|-----|-----|------|------------------|

| E cycle time           | t <sub>CYC</sub> | 1000 | —   |     | ns   | Fig. 10, Fig. 11 |

| E high level width     | P <sub>WEH</sub> | 450  | _   | _   | ns   |                  |

| E low level width      | P <sub>WEL</sub> | 450  | _   | _   | ns   |                  |

| E rise time            | t,               | _    | _   | 25  | ns   |                  |

| E fall time            | t <sub>f</sub>   | _    | _   | 25  | ns   |                  |

| Address setup time     | t <sub>AS</sub>  | 140  | _   | _   | ns   |                  |

| Address hold time      | t <sub>AH</sub>  | 10   | _   |     | ns   |                  |

| Data setup time        | t <sub>DSW</sub> | 200  | _   |     | ns   | Fig. 10          |

| Data delay time        | t <sub>DDR</sub> | _    | _   | 320 | ns   | Fig. 11, Fig. 12 |

| Data hold time (write) | t <sub>DHW</sub> | 10   | _   | _   | ns   | Fig. 10          |

| Data hold time (read)  | t <sub>DHR</sub> | 20   | _   | _   | ns   | Fig. 11          |

### MPU Interface (GND = 0V, $V_{CC}$ = 2.7 to 5.5V, Ta = -30 to +75°C)<sup>\*</sup>

Note: Specified at +75°C for die products.

Figure 9 MPU Write Timing

Figure 10 MPU Read Timing

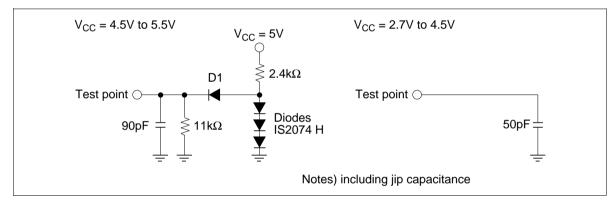

Figure 11 DB0–DB7: Load Circuit

### Clock Timing (GND = 0V, $V_{CC}$ = 2.7 to 5.5V, Ta = -30 to +75°C)\*

|                        |                         |      | Limit |     |      |                       |

|------------------------|-------------------------|------|-------|-----|------|-----------------------|

| Item                   | Symbol                  | Min  | Тур   | Max | Unit | <b>Test Condition</b> |

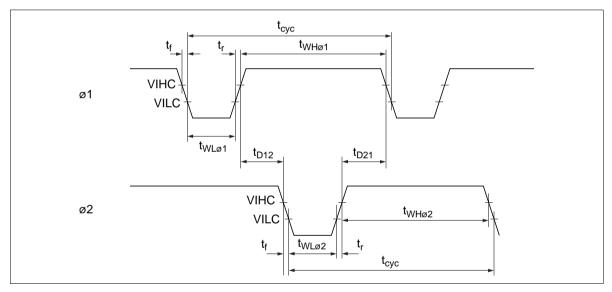

| ø1, ø2 cycle time      | t <sub>cyc</sub>        | 2.5  |       | 20  | μs   | Fig. 13               |

| ø1 low level width     | $t_{_{WL arepsilon 1}}$ | 625  | —     | —   | ns   |                       |

| ø2 low level width     | $t_{_{WLø2}}$           | 625  | —     | —   | ns   |                       |

| ø1 high level width    | t <sub>WHø1</sub>       | 1875 |       | —   | ns   |                       |

| ø2 high level width    | $t_{_{WH\emptyset2}}$   | 1875 | —     | —   | ns   |                       |

| ø1–ø2 phase difference | t <sub>D12</sub>        | 625  | —     | —   | ns   |                       |

| ø2–ø1 phase difference | t <sub>D21</sub>        | 625  |       | —   | ns   |                       |

| ø1, ø2 rise time       | t,                      | _    |       | 150 | ns   |                       |

| ø1, ø2 fall time       | t <sub>f</sub>          | _    |       | 150 | ns   |                       |

Note: Specified at +75°C for die products.

Figure 12 External Clock Waveform

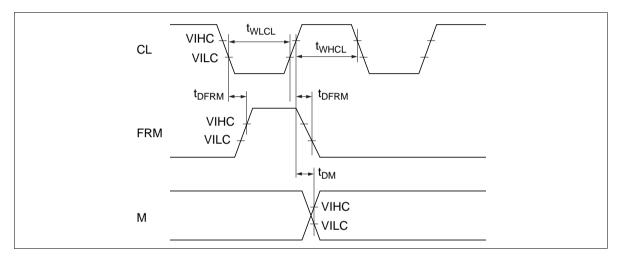

### Display Control Timing (GND = 0V, $V_{CC}$ = 2.7 to 5.5V, Ta = -30 to +75°C)<sup>\*</sup>

|                     |                   |     | Limit |     |      |                       |

|---------------------|-------------------|-----|-------|-----|------|-----------------------|

| Item                | Symbol            | Min | Тур   | Max | Unit | <b>Test Condition</b> |

| FRM delay time      | t <sub>DFRM</sub> | -2  | —     | +2  | μs   | Fig. 14               |

| M delay time        | t <sub>DM</sub>   | -2  | _     | +2  | μs   |                       |

| CL low level width  | t <sub>wLCL</sub> | 35  | _     | —   | μs   |                       |

| CL high level width | t <sub>whcL</sub> | 35  | _     | _   | μs   |                       |

Note: Specified at +75°C for die products.

Figure 13 Display Control Signal Waveform

Reset Timing (GND = 0V,  $V_{CC}$  = 2.7 to 5.5V, Ta = -30 to +75°C)\*

| Item                                                                                                                                            | Symbol           | Min | Тур              | Мах | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|------------------|-----|------|

| Reset time                                                                                                                                      | t <sub>RST</sub> | 1.0 | —                | —   | μs   |

| Do not fail to set the system again because RESET during operation may destroy the data in all the registers except on/off register and in RAM. |                  |     |                  |     |      |

|                                                                                                                                                 |                  |     | t <sub>RST</sub> |     |      |

Figure 14 Reset Timing

### Cautions

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

# HITACHI Hitachi, Ltd.

|  | Semiconductor & Integrated Circuits.<br>Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan<br>Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109            |                                                                             |                                                                                                                               |                         |                                                                                                                                                                         |                                                                                                                                                                                                                                         |  |  |

|--|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|  | E<br>A<br>A<br>A                                                                                                                                                       | orthAmerica<br>urope<br>sia (Singapo<br>sia (Taiwan)<br>sia (HongKo<br>apan | ore) :  <br>                                                                                                                  | http://www.hitachi.com. | om/hel/ecg<br>com.sg/grp3/sicd/index.htm<br>tw/E/Product/SICD_Frame.htr<br>hk/eng/bo/grp3/index.htm                                                                     | n                                                                                                                                                                                                                                       |  |  |

|  | For further informatic<br>Hitachi Semiconductor<br>(America) Inc.<br>179 East Tasman Drive,<br>San Jose (CA 95134<br>Tel: <1> (408) 433-1990<br>Fax: <1>(408) 433-0223 |                                                                             | br Hitachi Europe GmbH<br>Electronic components Group<br>Ve, Dornacher Straße 3<br>D-85622 Feldkirchen, Munich<br>990 Germany |                         | Hitachi Asia Pte. Ltd.<br>16 Collyer Quay #20-00<br>Hitachi Tower<br>Singapore 049318<br>Tel: 535-2100<br>Fax: 535-1533                                                 | Hitachi Asia (Hong Kong) Ltd.<br>Group III (Electronic Components)<br>7/F., North Tower, World Finance Centre,<br>Harbour City, Canton Road, Tsim Sha Tsui,<br>Kowloon, Hong Kong<br>Tel: <852> (2) 735 9218<br>Fax: <852> (2) 730 0281 |  |  |

|  |                                                                                                                                                                        |                                                                             |                                                                                                                               |                         | Hitachi Asia Ltd.<br>Taipei Branch Office<br>3F, Hung Kuo Building. No.167,<br>Tun-Hwa North Road, Taipei (105)<br>Tel: <886> (2) 2718-3666<br>Fax: <886> (2) 2718-8180 | Telex: 40815 HITEC HX                                                                                                                                                                                                                   |  |  |

|  |                                                                                                                                                                        |                                                                             |                                                                                                                               | · · · / · · · · ·       |                                                                                                                                                                         |                                                                                                                                                                                                                                         |  |  |

Copyright © Hitachi, Ltd., 1998. All rights reserved. Printed in Japan.