## M64110WG

**PRELIMINARY**

REJ03F0002-0110Z Rev.1.10 2003.05.20

BLUETOOTH BASEBAND LSI (Under Development)

### **Description**

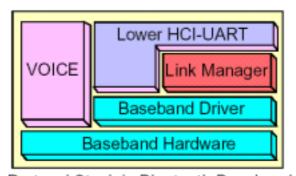

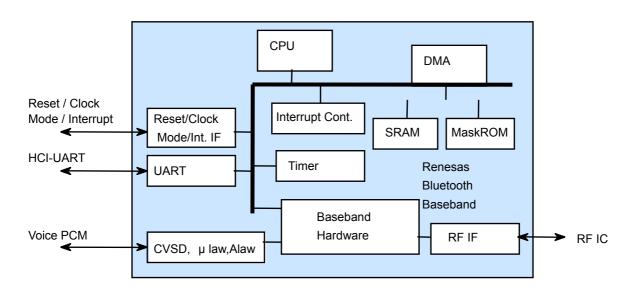

The Renesas Bluetooth Baseband provides the full functionality of HCI, Link Manager and Baseband, compliant with Bluetooth specification V1.1. ACL links support DM1, DH1, DM3, DH3, DM5, DH5 and AUX packets, whereas SCO links for voice channels support HV1, HV2, HV3 and DV packets. Flexible connections can be configured by switch of master slave role and piconet. The baseband operates at 16MHz and reduces power dissipation using low frequency oscillator at 32.768kHz in Sniff, Hold and Park modes. On the transceiver side the Renesas radio IC is supported.

The host interface is built based on HCI-UART and has some vendor-specific commands for selecting Radio IC type, 79-hop or 23-hop system, Write BD ADDR and so on.

Protocol Stack in Bluetooth Baseband

#### **Features**

- Bluetooth V1.1 compliant

- HCI, Link Manager and Baseband functions

- Inquiry and Paging

- ACL link for command and data transfer

- SCO link for voice transfer (one channel)

- CRC, FEC, whitening and ARQ

- Authentication and Encryption

- Switch of master slave role

- Piconet (up to 7 devices)

- Sniff, Hold and Park mode operations

- Power control with low frequency oscillator at 32.768kHz

- Bluetooth test mode

- Radio interface for Renesas Radio IC

- Supports 79-hop and 23-hop systems

- 14-bit linear PCM interface for voice

- CVSD, µlaw and Alaw voice codecs

- Internal microprocessor running at 16MHz

- UART for HCI interface

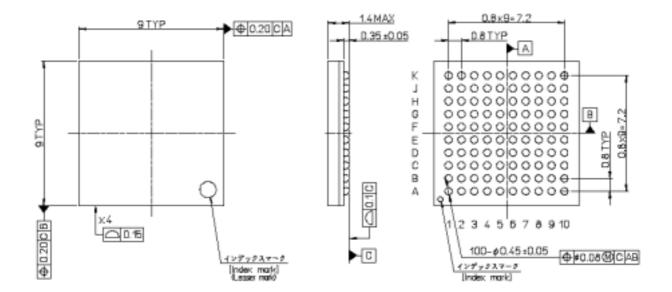

- 100-pin FBGA 0.8mm ball pitch, 9mm x 9mm

- Operating Temperature Range -40 to 85 °C

- Digital supply voltage 1.8 to 2.0V for internal circuit Digital supply voltage 2.7 to 3.3V for I/O ports Analog supply voltage 2.7 to 3.3V

# Functional Block Diagram

Bluetooth and Bluetooth logos are owned by its proprietor and used by Renesas Technology Corporation under license. This is not a final specification. Some parameters limits are Subject to change.

## **Device Pinout Diagram (100-pin FBGA)**

# Orientation from top of device

|   | 1         | 2          | 3      | 4       | 5         | 6      | 7       | 8       | 9          | 10      |  |

|---|-----------|------------|--------|---------|-----------|--------|---------|---------|------------|---------|--|

|   |           |            |        |         |           |        |         |         |            |         |  |

| Α | NU        | MODE[0]    | VUDATA | VBITCLK | NU        | DVSS18 | MODE[2] | AVSS3   | AVDD3      | RSSIA   |  |

| В | NU        | MODE[1]    | VDDATA | DVSS3   | NU        | NU     | AVSS3   | AVDD3   | O<br>AVSS3 | AVDD3   |  |

| С | URXD      | NU         | NU     | EXIREQ  | DVDD3     | NU     | AVDD3   | AVSS3   | PLLON      | TXGATE  |  |

| D | DVDD3     | UTXD       | DVSS3  | UCTS    | V8KFP     | NU     | RXDATA  | NU      | NU         | RXON    |  |

| E | INTOUT    | DVSS18     | DVDD18 | URTS (  | CLK16MSEL | DVDD18 | NU      | TXON    | DVDD18     | DVSS18  |  |

| F | CLK16MXIN | CLK16MXOUT | DVSS3  | DVDD3   | NU        | DVDD3  | TXDATA  | RXANT   | TXANT      | DVSS3   |  |

| G | CLK16MOUT | CLK16MREQ  | RSTIN  | NU      | DVDD3     | NU     | SERLE   | SERDATA | SERCLK     | TXDBASE |  |

| Н | CLK16MIN  | CLKTHR     | NU     | NU      | DVSS3     | NU     | NU      | NU      | NU         | RXDBASE |  |

| J | XRDY      | CLK32KSEL  | NU     | NU      | NU        | DVSS18 | NU      | NU      | NU         | NU      |  |

| κ | CLK32KXIN | CLK32KXOUT | NU     | NU      | NU        | DVDD18 | NU      | NU      | NU         | NU      |  |

|   |           |            |        |         |           |        |         |         |            |         |  |

TOP VIEW

### Pin Description for 100-pin FBGA

| Pin Nan   | ne for 100-pin | Туре | Dir    | Description                                           |

|-----------|----------------|------|--------|-------------------------------------------------------|

| HCI-UART  | UTXD           | Dig  | Out    | Transmit data                                         |

|           | URXD           | Dig  | In     | Receive data                                          |

|           | URTS           | Dig  | Out    | Request to send                                       |

|           | UCTS           | Dig  | In     | Clear to send                                         |

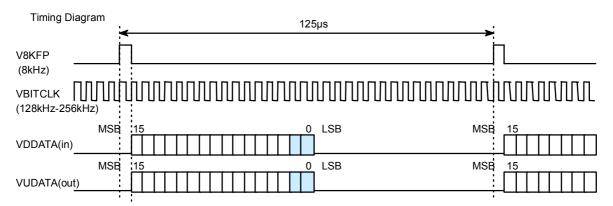

| Voice     | VBITCLK        | Dig  | In/Out | Voice bit clock                                       |

| Interface | V8KFP          | Dig  | In/Out | Voice 8kHz frame pulse                                |

|           | VDDATA         | Dig  | In     | Voice downstream data                                 |

|           | VUDATA         | Dig  | Out    | Voice upstream data                                   |

| RF        | TXDATA         | Dig  | Out    | Transmit data                                         |

| Interface | TXGATE         | Dig  | Out    | Transmit gate                                         |

|           | RXDATA         | Ana  | In     | Receive data                                          |

|           | PLLON          | Dig  | Out    | PLL power on                                          |

|           | TXANT          | Dig  | Out    | Transmitter antenna select                            |

|           | TXON           | Dig  | Out    | Transmitter power on                                  |

|           | RXANT          | Dig  | Out    | Receiver antenna select                               |

|           | RXON           | Dig  | Out    | Receiver power on                                     |

|           | SERCLK         | Dig  | Out    | Serial interface clock                                |

|           | SERLE          | Dig  | Out    | Serial interface control                              |

|           | SERDATA        | Dig  | Out    | Serial interface data in                              |

|           | RSSIA          | Ana  | In     | RSSI(Reserved)                                        |

|           | TXDBASE        | Dig  | Out    | Transmit data for Baseband connection(for Test/Debug) |

|           | RXDBASE        | Dig  | In     | Receive data for Baseband connection(for Test/Debug)  |

| Mode      | MODE[2:0]      | Dig  | In     | Mode select                                           |

| Interrupt | EXIREQ         | Dig  | In     | External interrupt request in                         |

|           | INTOUT         | Dig  | Out    | Interrupt out                                         |

| Reset     | RSTIN          | Dig  | In     | External reset in                                     |

| Clock     | XRDY           | Dig  | In     | Oscillator circuit ready                              |

|           | CLKTHR         | Dig  | In     | 16MHz clock source select                             |

|           | CLK16MSEL      | Dig  | In     | 16MHz clock source select(TCXO or Oscillator)         |

|           | CLK16MREQ      | Dig  | Out    | External 16MHz clock request                          |

|           | CLK16MIN       | Dig  | In     | External 16MHz clock in                               |

|           | CLK16MXIN      | Xin  | In     | 16MHz crystal in                                      |

|           | CLK16MXOUT     | Xout | Out    | 16MHz crystal out                                     |

|           | CLK16MOUT      | Dig  | Out    | External 16MHz clock out                              |

|           | CLK32KSEL      | Dig  | In     | 32.768KHz clock source select                         |

|           | CLK32KXIN      | Xin  | In     | 32.768kHz crystal in                                  |

|           | CLK32KXOUT     | Xout | Out    | 32.768kHz crystal out                                 |

### M64110WG

| Pin Name for 100-pin |        | Туре | Dir | Description                             |

|----------------------|--------|------|-----|-----------------------------------------|

| Power                | DVDD3  | VDD  | -   | Digital power supply for I/O ports      |

| Ground               | DVSS3  | GND  | -   | Digital ground for I/O ports            |

| DVDD18 VD            |        | VDD  | -   | Digital power supply for internal logic |

|                      | DVSS18 | GND  | -   | Digital ground for internal logic       |

|                      | AVDD3  | VDD  | -   | Analog Power Supply                     |

|                      | AVSS3  | GND  | -   | Analog Ground                           |

(Note1) NU pins should be opened.

### M64110WG

**Absolute Maximum Ratings**

| Symbol  | Item                | Condition | Rating            | Unit |

|---------|---------------------|-----------|-------------------|------|

| VDD3    | Supply Voltage      |           | -0.3 to 4.2       | V    |

| (Note1) |                     |           |                   |      |

| VDD18   | Supply Voltage      |           | -0.3 to 2.5       | V    |

| (Note2) |                     |           |                   |      |

| VI      | Input Voltage       | CLK16MIN  | -0.3 to VDD18+0.3 | V    |

| VI      | Input Voltage       | Except    | -0.3 to VDD3+0.3  | V    |

|         | _                   | CLK16MIN  |                   |      |

| VO      | Output Voltage      |           | -0.3 to VDD3+0.3  | V    |

| Tstg    | Storage Temperature |           | -55 to +125       | °C   |

(Note1) DVDD3, AVDD3 (Note2) DVDD18

**Recommended Operating Condition**

| Symbol  | Item                        | Condition |            | Unit |     |    |

|---------|-----------------------------|-----------|------------|------|-----|----|

|         |                             |           | Min        | Тур  | Max |    |

| VDD3    | Supply Voltage              |           | 2.7        | 3.0  | 3.3 | V  |

| (Note1) |                             |           |            |      |     |    |

| VDD18   | Supply Voltage              |           | 1.8        | 1.9  | 2.0 | V  |

| (Note2) |                             |           |            |      |     |    |

| VIH     | 'H' Level Input Voltage     | Except    | 0.7 x VDD3 |      |     | V  |

| VIL     | 'L' Level Input Voltage     | CLK16MIN  |            |      | 0.8 | V  |

| Topr    | Operating Temperature range |           | -40        |      | 85  | °C |

(Note1) DVDD3, AVDD3 (Note2) DVDD18 Electrical Characteristics (Unless otherwise stated: VDD3=2.7 to 3.3V,VDD18=1.8 to 2.0V,Topr=-40°C to +85°C)

| Symbol | Iten                              |                                                        | Measurement         |          | Rating | 10 00 07 | Unit |

|--------|-----------------------------------|--------------------------------------------------------|---------------------|----------|--------|----------|------|

|        |                                   |                                                        | Condition           | Min      | Тур    | Max      |      |

| VOH1   | 'H' Level Output Voltage          | UTXD,URTS,VBITCLK                                      | IOH=-1mA            | VDD3-0.4 |        |          | V    |

|        |                                   | V8KFP,VUDATA,PLLON                                     |                     |          |        |          |      |

|        |                                   | TXGATE,TXON,RXON                                       |                     |          |        |          |      |

|        |                                   | SERLE,SERCLK                                           |                     |          |        |          |      |

| VOL1   | 'L' Level Output Voltage          | SERDATA,TXDBASE                                        | IOL=+1mA            |          |        | 0.4      | V    |

|        |                                   | CLK16MREQ,INTOUT                                       |                     |          |        |          |      |

|        |                                   | MODE[2:0]                                              |                     |          |        |          |      |

|        |                                   | TESTOUT[11:0]                                          |                     |          |        |          |      |

| VOH2   | 'H' Level Output Voltage          | CLK16MOUT                                              | IOH=-2mA            | VDD3-0.4 |        |          | V    |

| VOL2   | 'L' Level Output Voltage          |                                                        | IOL=+2mA            |          |        | 0.4      | V    |

| VOH3   | 'H' Level Output Voltage          | TXDATA,TXANT,RXANT                                     | IOH=-4mA            | VDD3-0.4 |        |          | V    |

| VOL3   | 'L' Level Output Voltage          |                                                        | IOL=+4mA            |          |        | 0.4      | V    |

| IIH1   | High State Input Current (Note 1) | URXD,UCTS,VBITCLK<br>V8KFP,VDDATA,RSTIN<br>XRDY,CLKTHR | VIH=VDD3            |          |        | 1        | μA   |

| IIL1   | Low State Input Current (Note 1)  | CLK16MSEL,INTOUT<br>CLK32KSEL                          | VIL=0V              | -1       |        |          | μA   |

| IIH2   | High State Input Current          | EXIREQ                                                 | VIH=VDD3            |          |        | 1        | μA   |

| IIL2   | Low State Input Current           |                                                        | VDD3=3V<br>VIL=0V   | -30      | -15    | -10      | μA   |

| IIH3   | High State Input Current (Note 1) | RXDBASE,<br>TSTMODE[5:1]<br>TESTOUT[11:0]              | VDD3=3V<br>VIH=VDD3 | 10       | 15     | 30       | μA   |

| IIL3   | Low State Input Current (Note 1)  | 0.1.1.5                                                | VIH=0V              | -1       |        |          | μA   |

(Note 1) In/Out pins were measured with Output off.

Timing Requirements (Unless otherwise stated: VDD3=2.7 to 3.3V,VDD18=1.8 to 2.0V)

|           | ( )                         |           | ,               |     |        |      |     |

|-----------|-----------------------------|-----------|-----------------|-----|--------|------|-----|

| Symbol    | Item                        | Condition | Rating          |     |        | Unit |     |

|           |                             |           |                 | Min | Тур    | Max  |     |

| fCLK16MIN | 16MHz Clock Input Frequency | CLK16MIN  | Within +/-20ppm |     | 16     |      | MHz |

| fCLK32KIN | 32kHz Clock Input Frequency | CLK32XIN  |                 |     | 32.768 |      | kHz |

| fDUTY     | Clock Input Duty            | CLK16MIN  |                 | 40  |        | 60   | %   |

|           | , ,                         | CLK32XIN  |                 |     |        |      |     |

| tr        | Clock Input Rise Time       | CLK16MIN  |                 |     |        | 5    | ns  |

| tf        | Clock Input Fall Time       | CLK16MIN  |                 |     |        | 5    | ns  |

| tw(RSTIN) | Reset Input 'L' Pulse width | RSTIN     |                 | 2   |        |      | ms  |

| (Note1)   |                             |           |                 |     |        |      |     |

(Note1) When power on, sufficient reset period is needed.

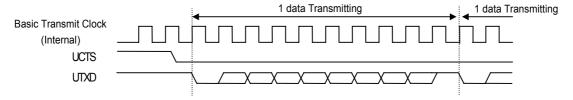

### Example of UART Interface behavior Transmit Timing

#### Notes)

- If the UCTS input pin changes to 'H' during the transmission of data byte and active UCTS function, the transmission stops after finishing the current transmission.

- Start and stop of transmission and UCTS function are executed by internal processing of Baseband.

- Basic clock is determined by the value set by internal baud rate.

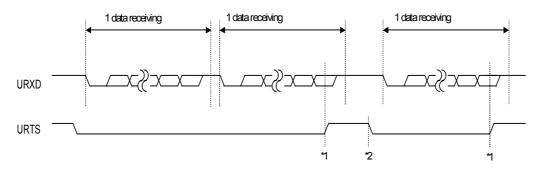

### **Receive Timing**

#### Notes)

- The above timing chart shows the status when 2 bytes data are received, 1 of 2 bytes received data is read, and then the next receiving are executed.

- If the most significant bit of the new data is received before reading received data from the received data register, the URTS pin becomes 'H'

- When the URTS pin is 'H', the UART becomes receive data storage status. Although receive operation is completed, the contents of receive shift buffer is not stored in the received data register. (\*1)

- When the URTS pin is 'H', if the received data register is read, then the data of receive shift buffer in receive data storage status is stored in the received data register, and then each receive error flag and receive buffer flag for receive data stored at that time are set cumulatively, and then the URTS pin becomes 'L' (\*2).

- If negative edge (level sense) is fed into the URXD input pin, receive control circuit judge that it is start bit and then sampling is executed around center of start bit. If the sampling input is 'L', receive sequence is started.

### Example of Voice Interface's behavior

Last2 bits shall be discarded

### Notes)

- VBITCLK can use the frequencies between 128Hz and 8kHz in steps of 8kHz.

- Last 2 bits of VDDATA and VUDATA will be discarded.

### Package Diagram (100FHE)

Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Keep safety first in your circuit designs!

Renesses Technology Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- Notes regarding these materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corporation or a third party.

Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors.

Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation or considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these materials.

If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

http://www.renesas.com

Copyright © 2003. Renesas Technology Corporation, All rights reserved. Printed in Japan.

# **REVISION HISTORY**

# M64110WG Data Sheet

| Rev. | Date        |       | Description                                                                |

|------|-------------|-------|----------------------------------------------------------------------------|

|      |             | Page  | Summary                                                                    |

| 1.00 | Apr. 1,2002 | _     | First Edition                                                              |

| 1.10 | Feb.11.2003 | 1,5,6 | Digital supply voltage for I/O ports and analog supply voltage 2.7 to 3.3V |

|      |             | 1,5,6 | Operating Temperature Range -40 to 85 °C                                   |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |

|      |             |       |                                                                            |