D/631A/1 May 1998

## **Features and Applications**

- Detects 12kHz or 16kHz SPM Frequencies

- Tone Follower and Packet Mode Outputs

- High Speech-Band Rejection

Properties

- Low Power Operation (2.7V <0.8mA)</li>

# CMX631A Low Voltage SPM Detector

**Provisional Information**

- Call Charge Applications on PABX Line Cards

- Complex and/or Simple Telephone Systems

- Remote Telephone/Payphones

## **Brief Description**

The CMX631A is a low-power, system-selectable Subscriber Pulse Metering (SPM) detector that indicates the presence of either 12kHz or 16kHz telephone call-charge frequencies on a telephone line.

Deriving its input directly from the telephone line, input amplitude/sensitivities are component adjustable to the user's national 'Must/Must-Not Decode' specifications via an on-chip input amplifier. The 12kHz and 16kHz frequency limits are accurately defined by the use of an external 3.579545MHz telephone-system Xtal or clock-pulse input.

The CMX631A demonstrates exceptional 12kHz and 16kHz performance in the presence of both voice and noise. This device may operate from a single or differential analogue signal input, from which two individual logic outputs will be produced; a Tone Follower Output and a Packet Mode Output.

This system (12kHz/16kHz) selectable integrated circuit, requires a 2.7V to 5.5V power supply which may be line-powered, is available in the following packages: 24-pin SSOP (CMX631AD5), 16-pin SOIC (CMX631AD4), and 16-pin PDIP (CMX631AP3). Additional package styles may be available to meet specific design requirements.

#### CONTENTS

| Section                                  | Page |

|------------------------------------------|------|

| Features and Applications                | 1    |

| Brief Description                        | 1    |

| 1 Block Diagram                          | 3    |

| 2 Signal List                            | 4    |

| 3 External Components                    | 5    |

| 4 General Description                    | 6    |

| 4.1 Tone Follower Mode                   | 6    |

| 4.2 Packet Mode                          | 6    |

| 4.3 Sensitivity Setting                  | 7    |

| 4.4 'WILL'/'WILL-NOT' Detect Frequencies | 9    |

| 5 Applications                           | 9    |

| 5.1 Input Configurations                 | 9    |

| 5.1.1 Protection Against High Voltages   | 9    |

| 5.1.2 Aliasing                           |      |

| The 'Clock-Out' Pin                      |      |

| 6 Performance Specification              | 11   |

| 6.1 Electrical Specifications            |      |

| 6.1.1 Absolute Maximum Ratings           |      |

| 6.1.2 Operating Limits                   |      |

| 6.1.3 Operating Characteristics          |      |

| 6.2 Packages                             | 14   |

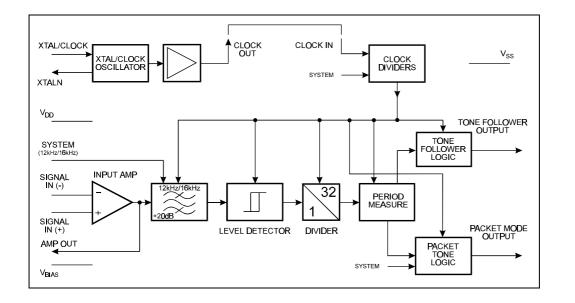

## 1 Block Diagram

Figure 1: Block Diagram

<sup>© 1998</sup> Consumer Microcircuits Limited

## 2 Signal List

| Packages                                     |        | Signal                     |       | Description                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------|--------|----------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D5                                           | D4/P3  | Name                       | Туре  |                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1                                            | 1      | Xtal/Clock                 | I/P   | The input to the on-chip clock oscillator; for use with a 3.579545MHz Xtal in conjunction with the Xtal output; circuit components are on-chip. When using a Xtal input, the Clock Out pin should be connected directly to the Clock In pin. If a clock pulse input is used at the Clock In pin, this (Xtal/Clock) pin must be connected directly to VDD . See Figure 2 and Section 3 - External Components. |

| 4                                            | 2      | XtalN                      | O/P   | The output of the on-chip clock oscillator inverter.                                                                                                                                                                                                                                                                                                                                                         |

| 5                                            | 3      | Clock Out                  | O/P   | A clock signal derived from the on-chip Xtal oscillator. If the<br>on-chip oscillator is used, this pin should be connected<br>directly to the Clock In pin. This output should not be used to<br>clock other devices                                                                                                                                                                                        |

| 6                                            | 4      | Clock In                   | I/P   | The 3.579545MHz clock pulse input to the internal clock dividers. If an externally generated clock pulse is used, the Xtal/Clock input pin should be connected to V <sub>DD</sub> . See Section 3 External Components.                                                                                                                                                                                       |

| 8                                            | 7      | V <sub>BIAS</sub>          | Power | The output of the on-chip bias circuitry. Held internally at $V_{DD}/2$ , this pin should be de-coupled to $V_{SS}$ . See Figure 2.                                                                                                                                                                                                                                                                          |

| 12                                           | 8      | V <sub>SS</sub>            | Power | Negative supply (GND).                                                                                                                                                                                                                                                                                                                                                                                       |

| 13                                           | 9      | Signal In +                | I/P   | The positive input to the input gain adjusting signal amplifier.<br>See Section 4.3, Sensitivity Setting and 4.4, 'Will'/'Will Not'<br>Detect Frequencies.                                                                                                                                                                                                                                                   |

| 17                                           | 10     | Signal In -                | I/P   | The negative input to the input gain adjusting signal amplifier. See Section 4.3, Sensitivity Setting and 4.4, 'Will'/'Will Not' Detect Frequencies.                                                                                                                                                                                                                                                         |

| 18                                           | 11     | Amp Out                    | O/P   | The output of the input gain adjusting signal amplifier. See Section 4.3, Sensitivity Setting and 4.4, 'Will'/'Will Not' Detect Frequencies.                                                                                                                                                                                                                                                                 |

| 19                                           | 13     | Tone<br>Follower<br>Output | O/P   | This output provides a logic '0' for the period of a detected tone and a logic '1' for a NOTONE detection. See 4.1, Tone Follower Mode and Figure 3.                                                                                                                                                                                                                                                         |

| 20                                           | 14     | Packet<br>Mode<br>Output   | O/P   | This output provides a logic '0' for a detected tone and a logic 1 for NOTONE detection and will ignore a small fluctuation or fade during the tone signal. See Section 4.2, Packet Mode and Figure 3.                                                                                                                                                                                                       |

| 21                                           | 15     | System                     | I/P   | This logic input selects the device operation to either 12kHz (logic 1) or 16kHz (logic '0') SPM systems. This input has an internal 1M $\Omega$ pull-up resistor (12kHz).                                                                                                                                                                                                                                   |

| 24                                           | 16     | V <sub>DD</sub>            | Power | Positive supply. A single, stable power supply is required.<br>Critical levels and voltages within the CMX631A are<br>dependent upon this supply. This pin should be de-coupled<br>to $V_{SS}$ by a capacitor mounted close to the pin. Note: If this<br>device is line powered, the resulting power supply must be<br>stable. See Section 5.1.1 - Protection against High Voltages.                         |

| 2, 3, 7, 9, 10,<br>11, 14, 15,<br>16, 22, 23 | 5,6,12 | N/C                        |       | No internal connection; leave open circuit.                                                                                                                                                                                                                                                                                                                                                                  |

© 1998 Consumer Microcircuits Limited

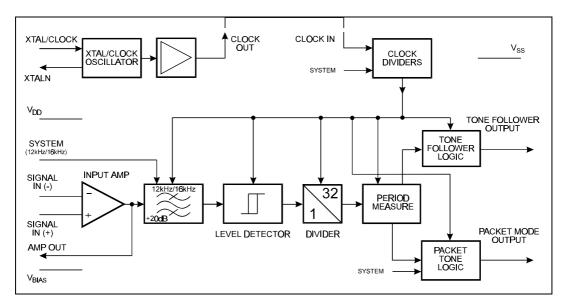

## 3 External Components

Figure 2: Recommended External Components

| R1 | Note 1 | R <sub>FEEDBACK</sub> | C1 |              | 1.0µF              | ±20% |

|----|--------|-----------------------|----|--------------|--------------------|------|

| R2 | Note 1 | R <sub>IN(-)</sub>    | C2 |              | 1.0µF              | ±20% |

| R3 | Note 1 | R <sub>IN(+)</sub>    | C3 |              | C <sub>IN(-)</sub> |      |

| R4 | Note 1 | R <sub>BIAS</sub>     | C4 |              | C <sub>IN(+)</sub> |      |

|    |        |                       | X1 | Note 2, 3, 4 | 3.579545MHz        |      |

#### **Table 2: Recommended External Components**

#### **Recommended External Component Notes:**

- 1. When calculating input gain components, for correct operation R1 and R4 should always be  $\geq 33k\Omega$ .

- For best results, a crystal oscillator design should drive the clock inverter input with signal levels of at least 40% of V<sub>DD</sub>, peak to peak. Tuning fork crystals generally cannot meet this requirement. To obtain crystal oscillator design assistance, consult your crystal manufacturer.

- 3. The on-chip crystal circuitry includes a feedback resistor (nominally  $2M\Omega$ ) between pins 1 and 2 and load capacitors on pins 1 and 2 (nominally 10pF each, excluding package and board parasitics).

- 4. When using an external clock input, X1 should be removed, Pin 1 (Xtal/Clock) should be tied to V<sub>DD</sub>, the Clock In and Clock Out jumper should be removed, and the external clock signal applied to Clock In.

<sup>© 1998</sup> Consumer Microcircuits Limited

## 4 General Description

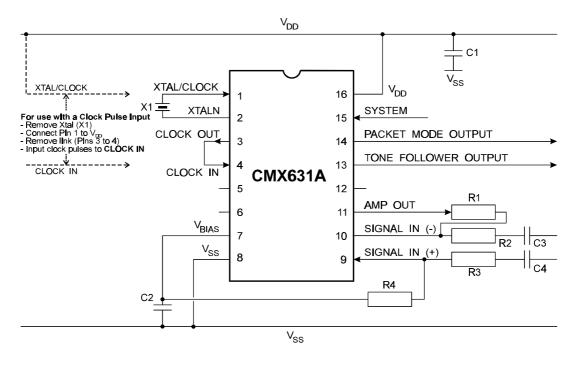

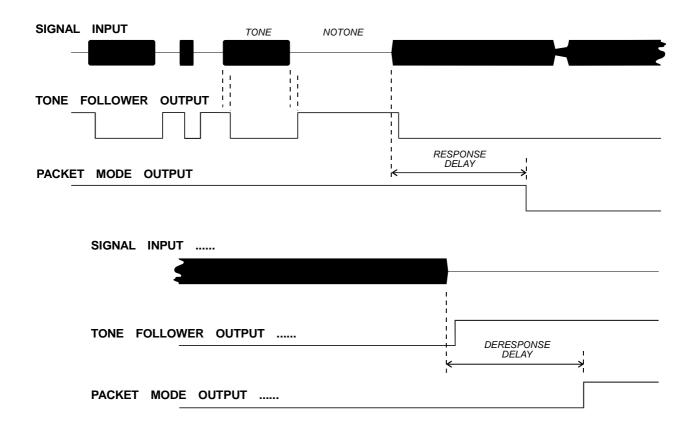

## 4.1 Tone Follower Mode

The Tone Follower Output produces a logic '0' when a valid signal is detected. A logic '1' signifies a NOTONE or bad decode. See Figure 3.

## 4.2 Packet Mode

The Packet (Cumulative Tone) Mode Output will respond and/or de-respond after a cumulative 40ms of good tone (or NOTONE) in any 48ms period by providing a Logic level output. See Figure 3.

This process will ignore small fluctuations or fades of a valid frequency input and is available for µProcessor 'wake-up', Minimum tone detection, NOTONE indication or transient avoidance.

Figure 3: Tone Follower and Packet Mode Outputs

## 4.3 Sensitivity Setting

The CMX631A input sensitivity can be accurately adjusted and set to support many national 12kHz and 16kHz SPM specifications.

#### 4.3.1 Input Gain Calculation

The input amplifier, with external circuitry, is used to set the sensitivity of the CMX631A to conform to the user's national level specification with regard to 'Must' and 'Must-Not' decode signal levels.

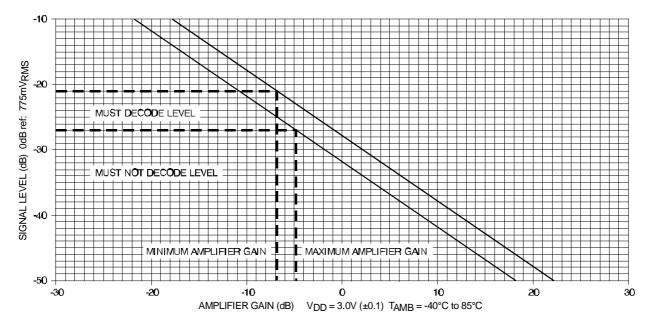

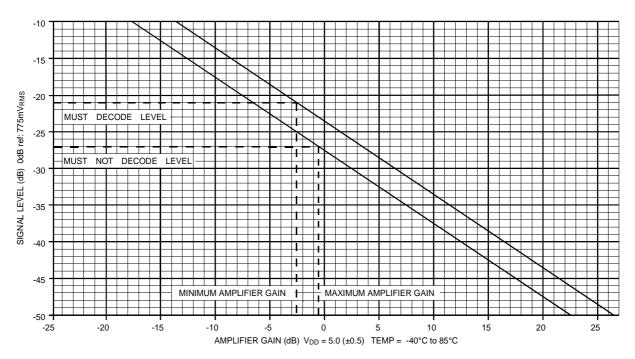

With reference to the graphs in Figure 4 and Figure 5, the following steps will assist in the determination of the required gain/attenuation.

- 1. Draw two horizontal lines from the Y-axis [Signal Level (dB)] in Figure 4 and Figure 5. The upper line represents the required 'Must' decode level. The lower line represents the required 'Must-Not' decode level

- 2. Mark the intersection of the upper horizontal line and the upper sloping line; drop a vertical line from this point to the X-axis [Amplifier Gain (dB)]. The point where the vertical line meets the X-axis indicates the minimum Input Amp gain required for reliable decoding of valid signals.

- 3. Mark the intersection of the lower horizontal line and the lower sloping line; drop a vertical line from this point to the X-axis. The point where the vertical line meets the X-axis will indicate the maximum allowable Input Amp gain. Input signals at or below the 'Must-Not' decode level will not be detected as long as the amplifier gain is no higher than this level.

Figure 4: Input Gain Calculation Graph for  $V_{DD} = 3.0V$

Figure 5: Input Gain Calculation Graph for  $V_{DD} = 5.0V$

#### 4.3.2 Input Gain Components

Refer to the gain components found in Table 2 and Figure 2. The user should calculate and select external components (R1/R2/C3 and R3/R4/C4) to provide amplifier gain within the limits obtained in 4.3.1 Input Gain Calculation.

Component tolerances should not move the gain-figure outside these limits. The graphs Figure 4 and Figure 5 are for the calculation of input gain components for a CMX631A using a  $V_{DD}$  of 3.0 (±0.1) or  $V_{DD}$  of 5.0 (±0.5).

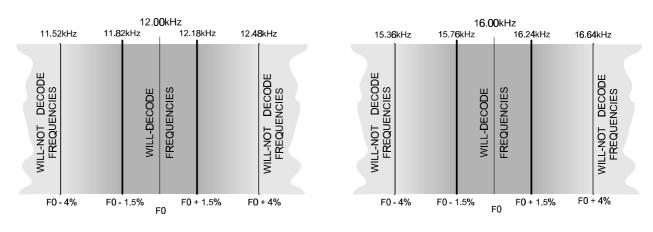

## 4.4 'WILL'/'WILL-NOT' Detect Frequencies

Figure 6: 'WILL'/'WILL-NOT' Detect Frequencies

## **5** Applications

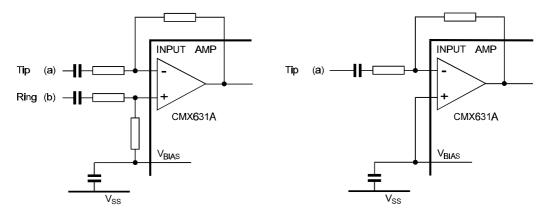

## 5.1 Input Configurations

Figure 7: Input Configurations

#### 5.1.1 Protection Against High Voltages

Telephone systems may have high DC and AC voltages present on the line. If the CMX631A is a part of host equipment that has its own signal input protection circuitry, there will be no need for further protection as long as the voltage on any pin is limited to within  $V_{DD}$  +0.3V and  $V_{SS}$  -0.3V.

If the host system does not have input protection, or there are signals present outside the device's specified limits, the CMX631A will require protection diodes at its signal inputs (+ and -). The breakdown voltage of the capacitors and the peak inverse voltage of the diodes must be sufficient to withstand the sum of the DC voltages plus all expected signal peaks.

<sup>© 1998</sup> Consumer Microcircuits Limited

#### 5.1.2 Aliasing

Due to the sampling nature of switched-capacitor filters used in the CMX631A, high frequency noise or unwanted signals can alias into the passband, disrupting detection. External components must be chosen carefully to avoid alias effects.

Possible Alias Frequencies:

If other filtering in the system has not attenuated these alias frequencies, capacitors should be employed across resistors R1 and R4 to provide anti-alias filtering.

The low-pass cutoff frequency should be chosen to be approximately 20kHz to 25kHz for a 12kHz system, or 25kHz to 30kHz for a 16kHz system.

i.e.

$$C = \frac{1}{2 x \pi x f_0 x (R1 \text{ or } R4)}$$

When anti-alias capacitors are used, an allowance must be made for reduced gain at the SPM frequency (12kHz or 16kHz).

#### The 'Clock-Out' Pin

The Clock-Out pin is intended to drive the CMX631A Clock-In pin only. It is not recommended that it be used to clock other devices within the host equipment.

## 6 Performance Specification

## 6.1 Electrical Specifications

### 6.1.1 Absolute Maximum Ratings

Exceeding the maximum rating can result in device damage.

| Parameter                                            | Min. | Тур. | Max.                    | Unit  |

|------------------------------------------------------|------|------|-------------------------|-------|

| Supply Voltage (V <sub>DD</sub> -V <sub>SS</sub> )   | -0.3 |      | 7.0                     | V     |

| Voltage on any pin to V <sub>SS</sub>                | -0.3 |      | (V <sub>DD</sub> + 0.3) | V     |

| Current into                                         |      |      |                         |       |

| V <sub>DD</sub>                                      | -30  |      | 30                      | mA    |

| V <sub>SS</sub>                                      | -30  |      | 30                      | mA    |

| Any other pin                                        | -20  |      | 20                      | mA    |

| D4 / P3 Packages                                     | Min. | Тур. | Max.                    | Unit  |

| Total allowable device dissipation at $T_{AMB}$ 25°C |      |      | 800                     | mW    |

| Derating above T <sub>AMB</sub> 25°C                 |      |      | 13                      | mW/°C |

| Operating Temperature                                | -40  |      | 85                      | °C    |

| Storage Temperature                                  | -40  |      | 85                      | °C    |

| D5 Package                                           | Min. | Тур. | Max.                    | Unit  |

| Total allowable device dissipation at $T_{AMB}$ 25°C |      |      | 550                     | mW    |

| Derating above T <sub>AMB</sub> 25°C                 |      |      | 9                       | mW/°C |

| Operating Temperature                                | -40  |      | 85                      | °C    |

| Storage Temperature                                  | -40  |      | 85                      | °C    |

## 6.1.2 Operating Limits

Correct Operation of the device outside these limits is not implied.

| Parameter                         | Min.     | Тур.    | Max.     | Unit |

|-----------------------------------|----------|---------|----------|------|

| Supply Voltage (V <sub>DD</sub> ) | 2.7      | 3.0/5.0 | 5.5      | V    |

| Operating Temperature             | -40      |         | 85       | °C   |

| Xtal/Clock Frequency              | 3.558918 |         | 3.589368 | MHz  |

#### 6.1.3 Operating Characteristics

All device characteristics are measured under the following conditions unless otherwise specified:

$\label{eq:VDD} \begin{array}{l} V_{DD} = 3.0 V \mbox{ to } 5.0 V \ensuremath{@} T_{AMB} = -40^\circ C \mbox{ to } 85^\circ C \\ \mbox{Audio Level 0dB (ref.)} = 775 m V_{RMS}, \mbox{ Noise Bandwidth} = 50 \mbox{ kHz} \\ \mbox{Xtal/Clock Frequency} = 3.579545 \mbox{MHz}, \mbox{ System Setting} = 12 \mbox{ kHz or } 16 \mbox{ kHz} \end{array}$

|                                          |               | Notes | Min.     | Тур.  | Max.     | Units            |

|------------------------------------------|---------------|-------|----------|-------|----------|------------------|

| Supply Current                           |               |       |          |       |          |                  |

| $V_{DD} = 3.0V$                          |               |       | -        | -     | 0.8      | mA               |

| $V_{DD} = 5.0 V$                         |               |       | -        | -     | 2.2      | mA               |

| Logic Inputs/Outputs                     |               |       |          |       |          |                  |

| Input Logic '1'                          |               |       | 70.0     | -     | -        | %V <sub>DD</sub> |

| Input Logic '0'                          |               |       | -        | -     | 30.0     | %V <sub>DD</sub> |

| Output Logic '1'                         |               |       | 90.0     | -     | -        | %V <sub>DD</sub> |

| Output Logic '0'                         |               |       | -        | -     | 10.0     | %V <sub>DD</sub> |

| Xtal/Clock or Clock In Frequency         |               |       | 3.558918 | -     | 3.589368 | MHz              |

| External Clock Pulse Width               |               |       | 0.000010 |       | 0.000000 |                  |

| High                                     |               |       | 100      | -     | -        | ns               |

| Low                                      |               |       | 100      | -     | -        | ns               |

| Input Amplifier                          |               |       |          |       |          |                  |

| D. C. Gain                               |               |       | 60.0     | -     | -        | dB               |

| Bandwidth (-3dB)                         |               |       | -        | 100   | -        | Hz               |

| Input Impedance                          |               |       | -        | 1.0   |          | MΩ               |

| Logic Impedances                         |               |       |          |       |          |                  |

| Input                                    |               |       |          |       |          |                  |

| System                                   |               |       | 0.7      | -     | 3.8      | MΩ               |

| Clock In                                 |               |       | 10.0     | -     | -        | MΩ               |

| Output                                   |               |       | -        | 14.0  | 30.0     | kΩ               |

| Overall Performance                      |               |       |          |       |          |                  |

| 12kHz Detect Bandwidth                   |               | 1     | 11.820   | -     | 12.180   | kHz              |

| 12kHz Not-detect Frequencies             | (below 12kHz) | 1     | -        | -     | 11.520   | kHz              |

| 12kHz Not-detect Frequencies             | (above 12kHz) | 1     | 12.480   | -     | -        | kHz              |

| 16kHz Detect Bandwidth                   |               | 1     | 15.760   | -     | 16.240   | kHz              |

| 16kHz Not-detect Frequencies             | (below 16kHz) | 1     | -        | -     | 15.360   | kHz              |

| 16kHz Not-detect Frequencies             | (above 16kHz) | 1     | 16.640   | -     | -        | kHz              |

| Sensitivity                              |               | 2     | 07.0     |       | 24.0     | dDm              |

| $V_{DD} = 3.0V \pm 0.1V$                 |               | 2     | -27.8    | -     | -31.8    | dBm              |

| $V_{DD} = 5.0 \text{V} \pm 0.5 \text{V}$ |               | 2     | -23.5    | -     | -27.5    | dBm              |

| Tone Operating Characteristics           |               |       |          |       |          |                  |

| Signal-to-Noise Requirements             | (Amp Input)   |       | 22.0     | 20.0  | -        | dB               |

| Signal-to-Voice Requirements             | (Amp Input)   |       | -36.0    | -40.0 | -        | dB               |

| Signal-to-Voice Requirements             | (Amp Output)  | 5, 6  | -25.0    | -     | -29.0    | dB               |

| Tone Follower Mode                       |               | 1, 8  |          |       | 40.0     |                  |

| Response and De-Response Time            |               | 1 0   |          |       | 10.0     | ms               |

| Packet Mode                              |               | 1, 8  | 40.0     |       | 19.0     | me               |

| Response and De-Response Time            |               |       | 40.0     | -     | 48.0     | ms               |

#### **Operating Characteristics Notes:**

- 1. With adherence to Signal-to-Voice and Signal-to-Noise specifications.

- 2. With Input Amplifier gain set to unity gain. See Section 4.3 for description of sensitivity setting.

- 3. Common Mode SPM and balanced voice signal.

- 4. Immune to false responses.

- 5. Immune to false de-responses.

- 6. With SPM and voice signal amplitudes balanced. To avoid false de-responses due to saturation, the peak to peak voice+noise level at the output of the Input Amp (12/16kHz Filter Input) should be no greater than the dynamic range of the device.

- 7. Maximum voice frequencies = 3.4kHz.

- 8. Response, De-Response and Power-up Response timing.

### 6.2 Packages

The CMX631A is available in the following packages. Additional package styles may be available to meet specific design requirements.

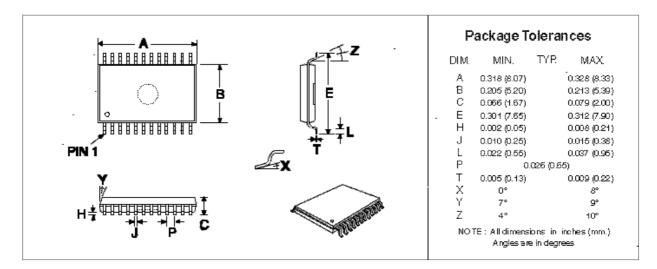

Figure 8: 24-pin SSOP Mechanical Outline: order as part no. CMX631AD5

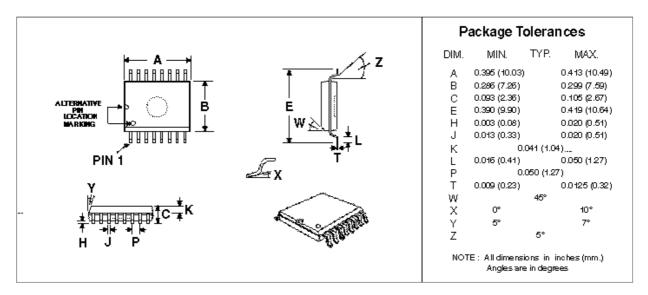

Figure 9: 16-pin SOIC Mechanical Outline: order as part no. CMX631AD4

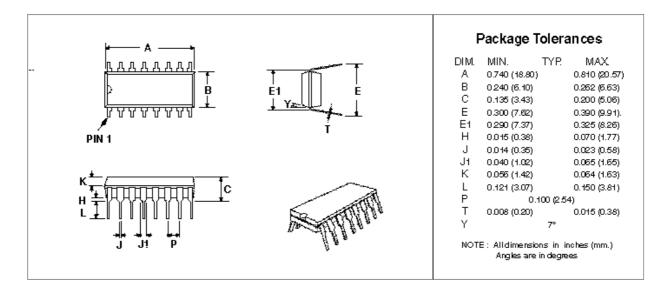

Figure 10: 16-pin PDIP Mechanical Outline: order as part no. CMX631AP3

Handling precautions: This product includes input protection, however, precautions should be taken to prevent device damage from electro-static discharge. CML does not assume any responsibility for the use of any circuitry described. No IPR or circuit patent licences are implied. CML reserves the right at any time without notice to change the said circuitry and this product specification. CML has a policy of testing every product shipped using calibrated test equipment to ensure compliance with this product specification. Specific testing of all circuit parameters is not necessarily performed.

1 WHEATON ROADTelephone: +44 1376 513833WITHAM - ESSEXTelefax: +44 1376 518247CM8 3TD - ENGLANDe-mail:sales@cmImicro.co.ukwebsite:http://www.cmImicro.co.uk

## **CML Product Data**

In the process of creating a more global image, the three standard product semiconductor companies of CML Microsystems Plc (*Consumer Microcircuits Limited (UK), MX-COM, Inc (USA) and CML Microcircuits (Singapore) Pte Ltd)* have undergone name changes and, whilst maintaining their separate new names (*CML Microcircuits (UK) Ltd, CML Microcircuits (USA) Inc and CML Microcircuits (Singapore) Pte Ltd*), now operate under the single title CML Microcircuits.

These companies are all 100% owned operating companies of the CML Microsystems Plc Group and these changes are purely changes of name and do not change any underlying legal entities and hence will have no effect on any agreements or contacts currently in force.

#### **CML Microcircuits Product Prefix Codes**

Until the latter part of 1996, the differentiator between products manufactured and sold from MXCOM, Inc. and Consumer Microcircuits Limited were denoted by the prefixes MX and FX respectively. These products use the same silicon etc. and today still carry the same prefixes. In the latter part of 1996, both companies adopted the common prefix: CMX.

This notification is relevant product information to which it is attached.

Company contact information is as below:

Oval Park, Langford, Maldon, Essex, CM9 6WG, England Tel: +44 (0)1621 875500 Fax: +44 (0)1621 875600 uk.sales@cmlmicro.com www.cmlmicro.com

COMMUNICATION SEMICONDUCTORS

4800 Bethania Station Road, Winston-Salem, NC 27105, USA Tel: +1 336 744 5050, 0800 638 5577 Fax: +1 336 744 5054 us.sales@cmlmicro.com www.cmlmicro.com

No 2 Kallang Pudding Road, 09-05/ 06 Mactech Industrial Building, Singapore 349307 Tel: +65 7450426 Fax: +65 7452917 sg.sales@cmlmicro.com www.cmlmicro.com