## **TOSHIBA**

TOSHIBA Original CMOS 16-Bit Microcontroller

# TLCS-900/L1 Series

TMP91C820A

## **TOSHIBA CORPORATION**

Semiconductor Company

## **Preface**

Thank you very much for making use of Toshiba microcomputer LSIs. Before use this LSI, refer the section, "Points of Note and Restrictions". Especially, take care below cautions.

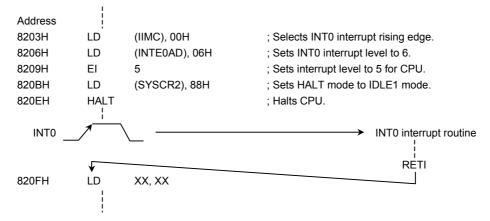

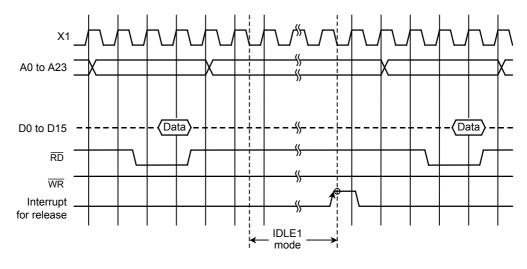

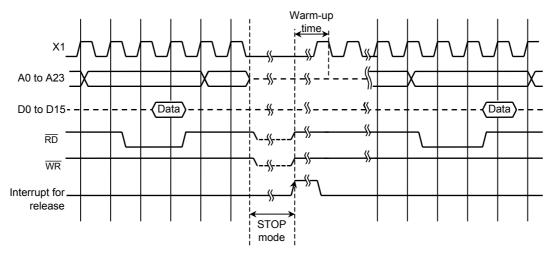

# \*\*CAUTION\*\* How to release the HALT mode

Usually, interrupts can release all halts status. However, the interrupts =  $(\overline{\text{NMI}}, \text{INT0 to INT3}, \text{INTRTC}, \text{INTALM0 to INTALM4}, \text{INTKEY})$ , which can release the HALT mode may not be able to do so if they are input during the period CPU is shifting to the HALT mode (for about 5 clocks of  $f_{\text{FPH}}$ ) with IDLE1 or STOP mode (IDLE2 is not applicable to this case). (In this case, an interrupt request is kept on hold internally.)

If another interrupt is generated after it has shifted to HALT mode completely, halt status can be released without difficultly. The priority of this interrupt is compare with that of the interrupt kept on hold internally, and the interrupt with higher priority is handled first followed by the other interrupt.

## CMOS 16-Bit Microcontrollers TMP91C820AF/JT5AW4-S

#### Outline and Features 1.

TMP91C82OA/JT5AW4 is a highnspelble of desit gmi ecol foot the co mid-tolarge-scale equipment.

TMP91C82OAF comes in a 1a4) e. pliTr5fAlWalt pacoknes in a 144-pad c Listed beloware the features.

(1) High-speed 16-bit CPU (900/L1 CPU)

Instruction mne modic cosmpate iulpolwa with TLCS-90

16 Mbytes of linear address space

General - purpose registers and register banks

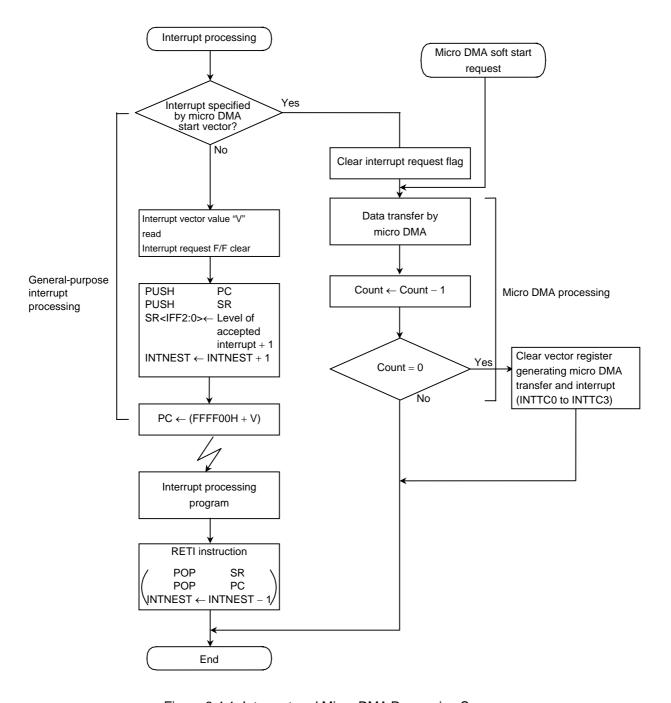

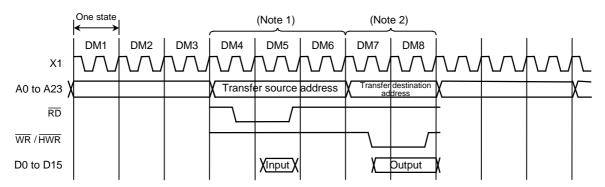

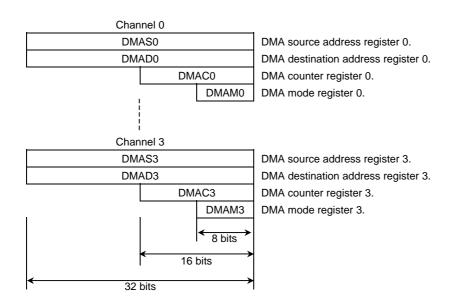

16-bit multiplication and division instructions; bit Mi cro DMA: 4channels (432ns/2bytes at 36 MHz)

- (2) Minimuminstruction execution time: 111ns (at 36 MHz)

- (3) Built-in RAM: 8 Kbytes

Built-in ROM: 8 Kbytes (However, 9999 (ROM code) has no

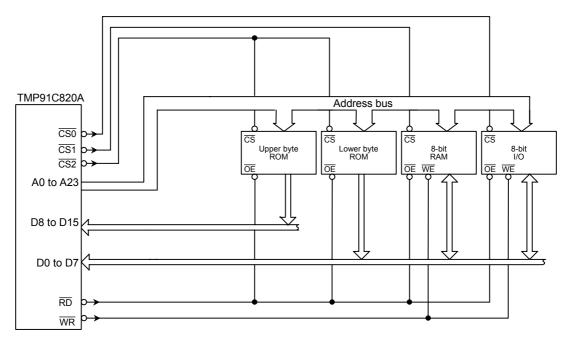

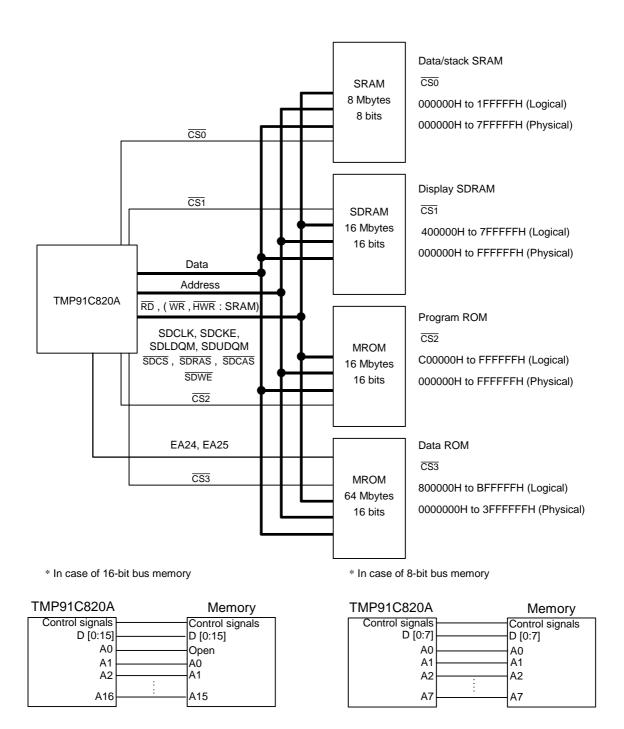

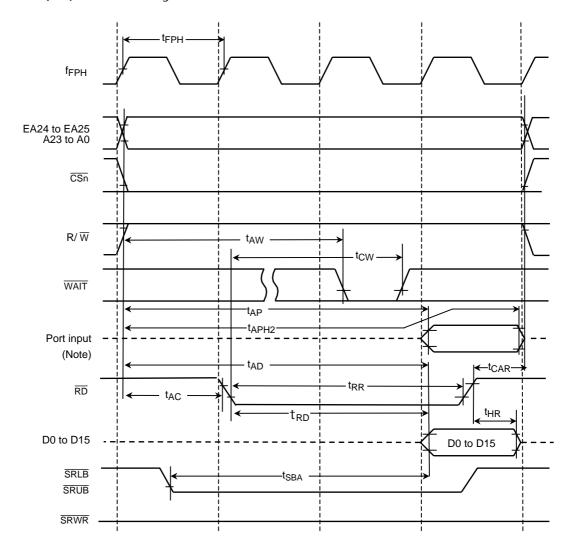

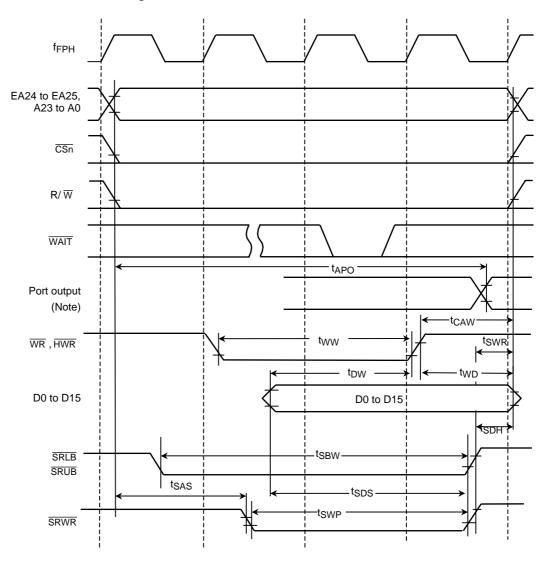

- (4) External memory expansion

- Expandable up to 136 Mbytes (Shared program/data are

- Can si mul taneous ly support 8- or 16- bit width extern ... Dynami c data bus syzi ng

- Separate bus system

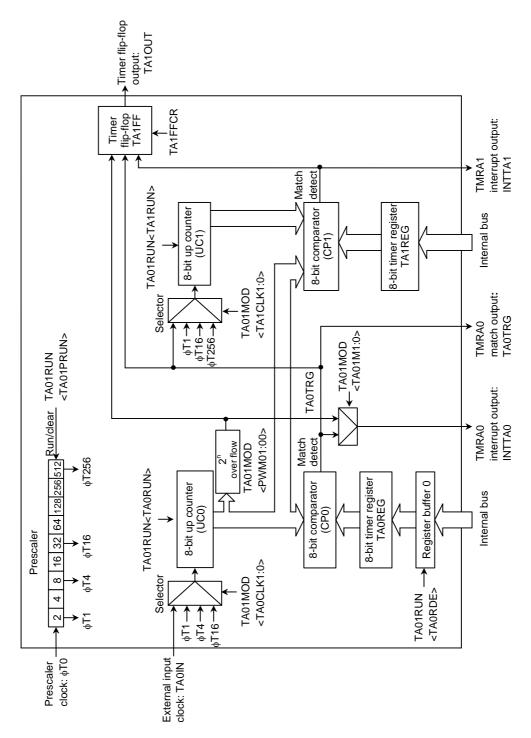

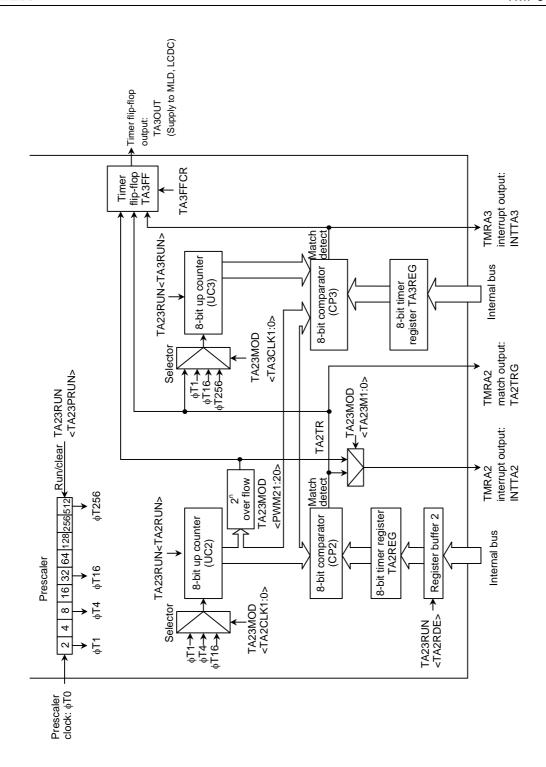

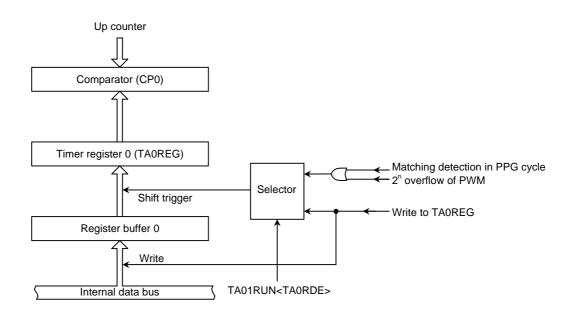

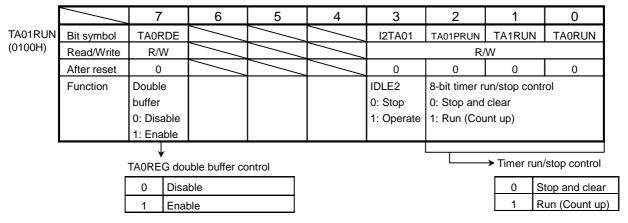

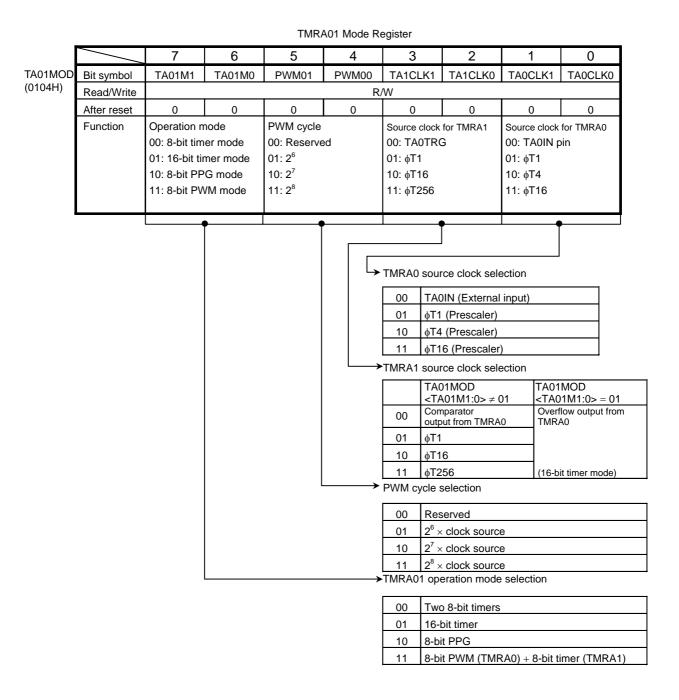

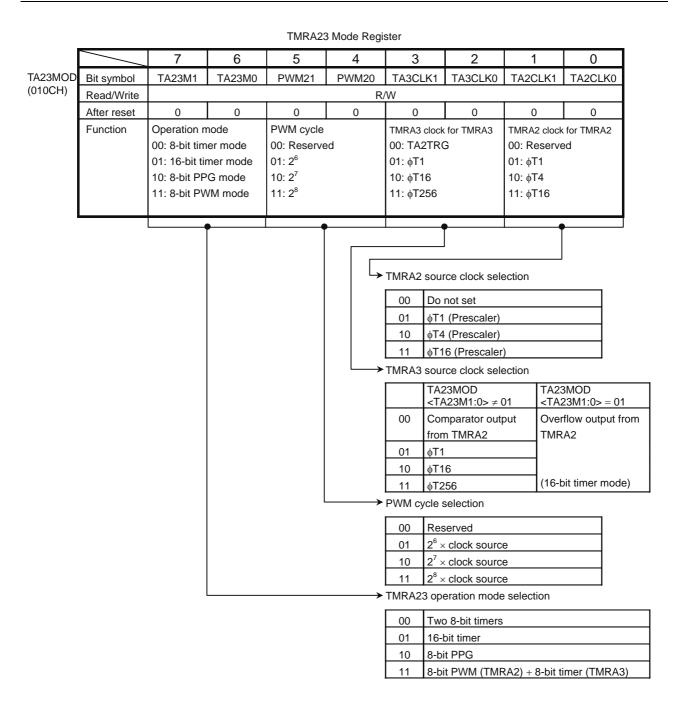

- (5) 8-bittimers: 4channels

- (6) 16-bittimer/event counter: 1 channel

- (7) General punpesésce: alchannel s

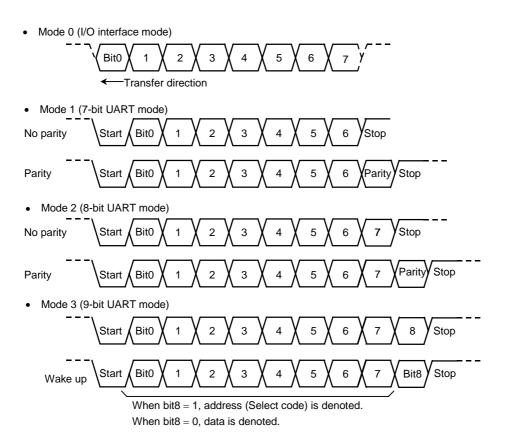

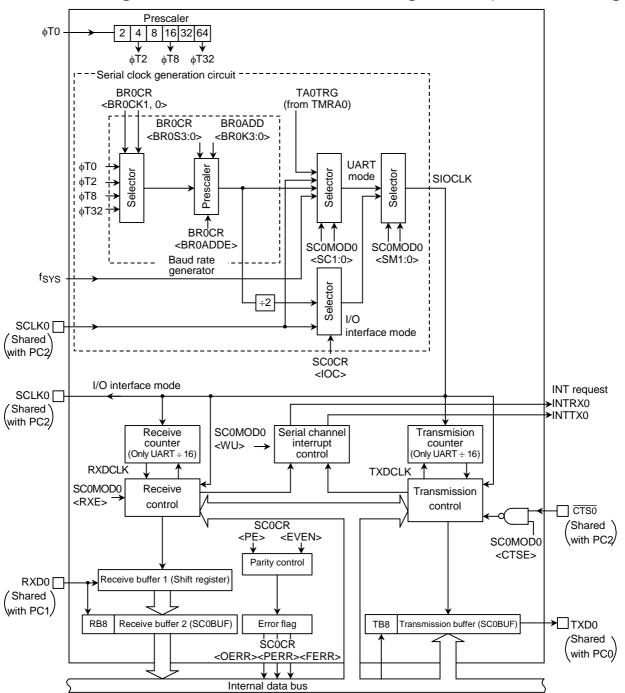

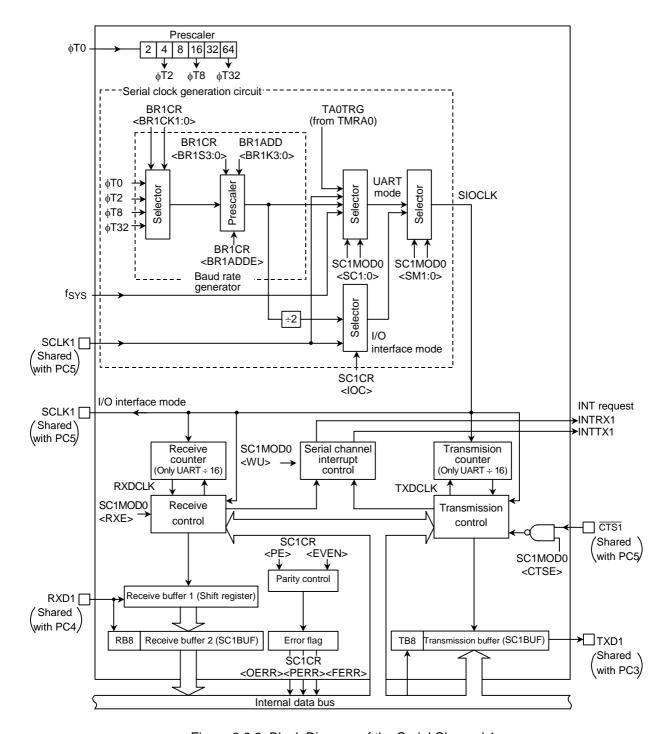

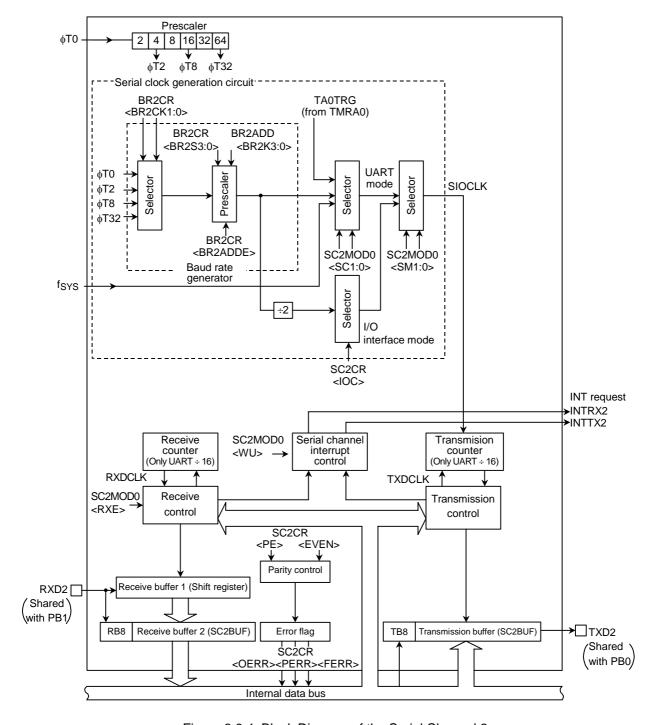

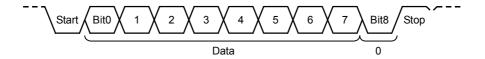

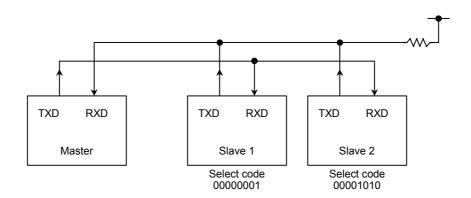

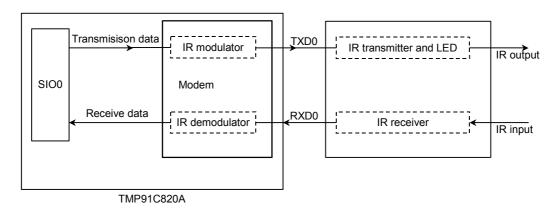

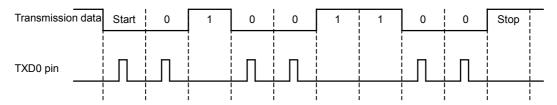

- UART/synchrodenous m

- IrDA

- The information contained herein is subject to change without notice.

- The information contained herein is subject to change without notice.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to cally with the standards of safety in making a safe design for the entire system, and to avoid in the patents of the patents. situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal semiconductor). These TOSHIBA products are

- equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are intended for usage in equipment, office equipment, appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunctionor failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- TOSHIBA products should not be embedded to the downstream products which are prohibited to be produced and sold, under any law and regulations.

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

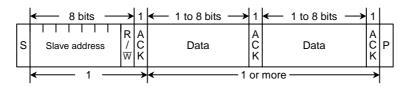

Purchase of T<sup>2</sup>OSddImBAohents com vseyusnalericth 2C Plaitein pt sRI ghts to us these componerACssysnterm, I provided that the syAStSetmandonforms Specification as defined by Philips.

> 2004-02-16 91C820A-1

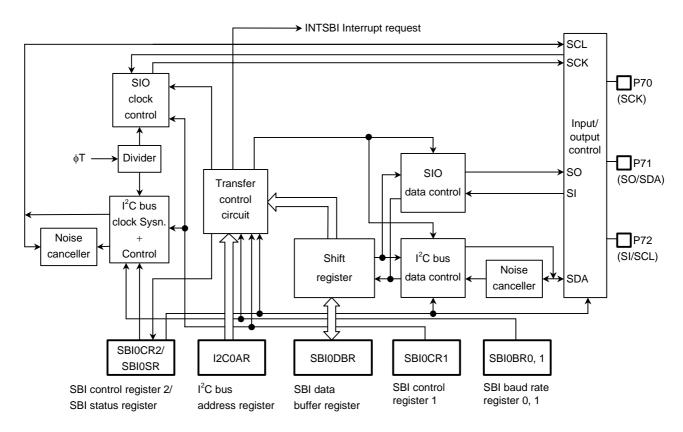

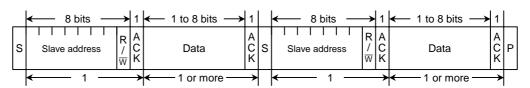

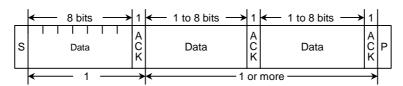

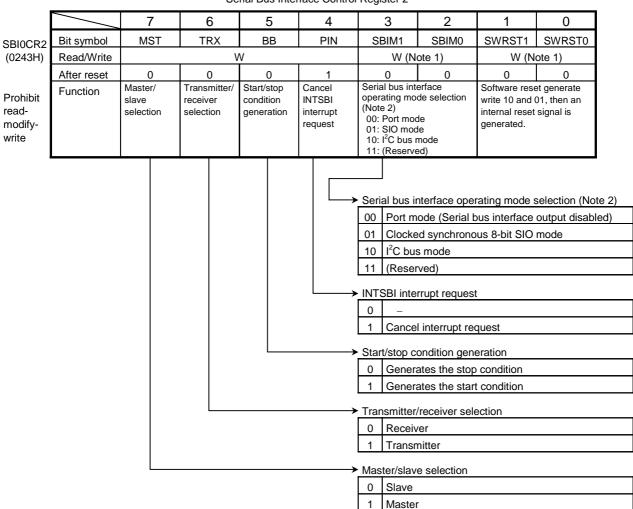

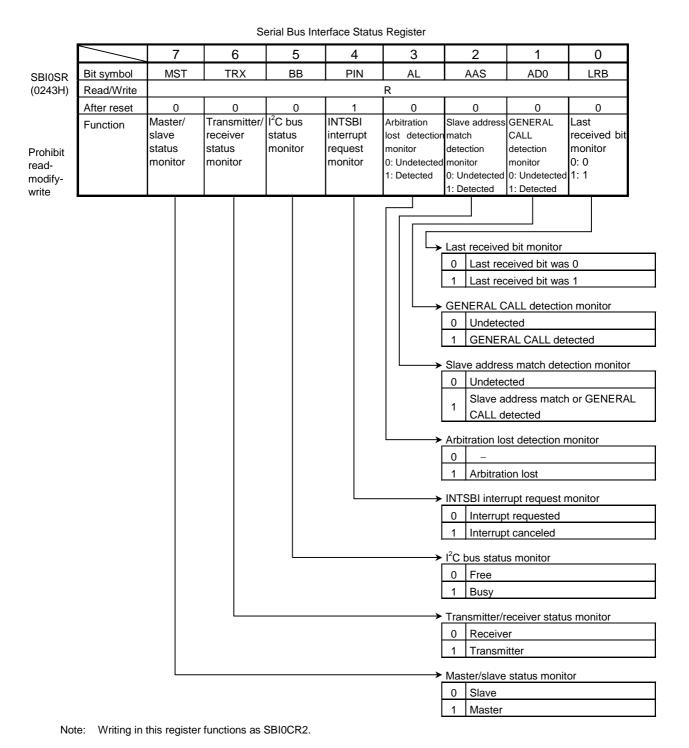

- (8) Serial businterface: 1 channel I2C bus mode/chrocorkosuysnscelect mode

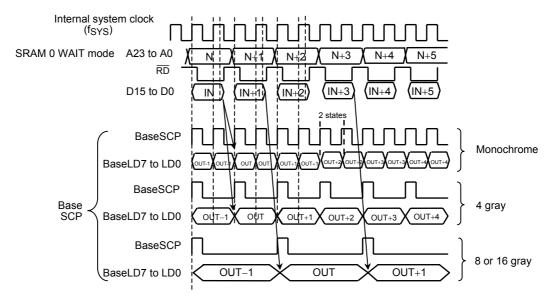

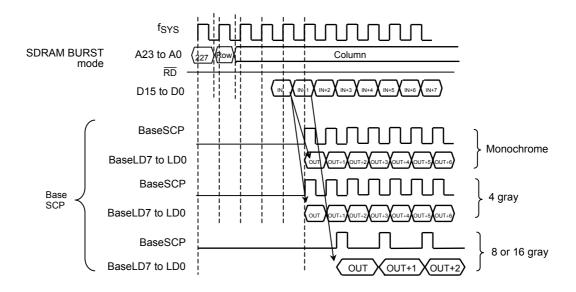

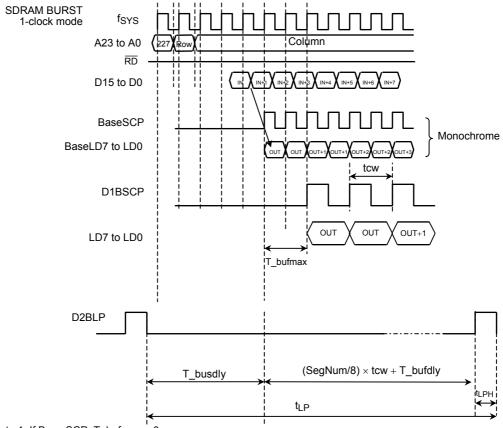

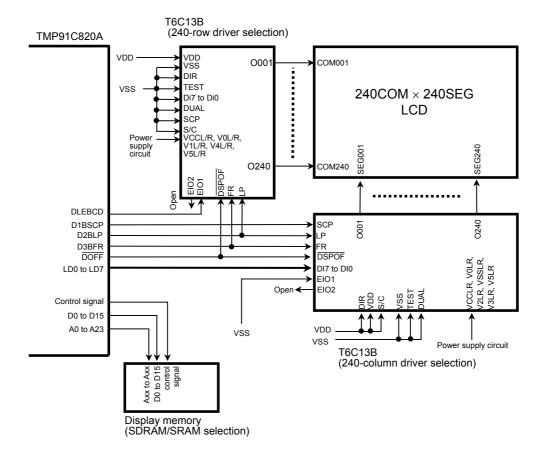

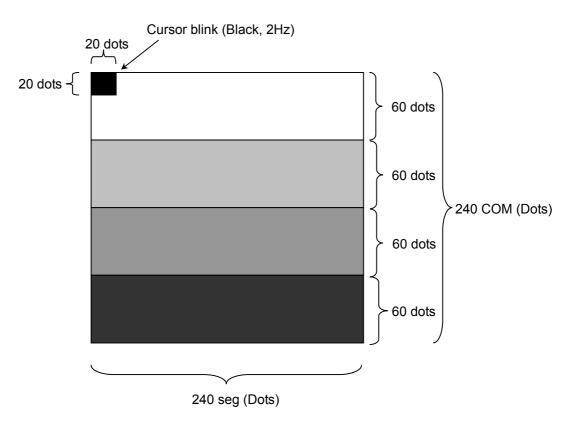

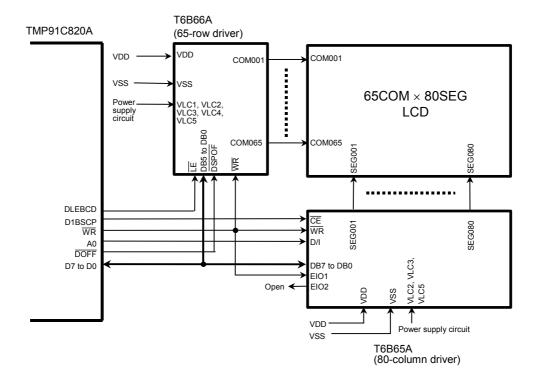

- (9) LCDcontroller

- Shiftregister/built-inRAMLCDdriver

- Supported 16, 8 and 4 gray levels and black and white

- Hardware blinking cursor

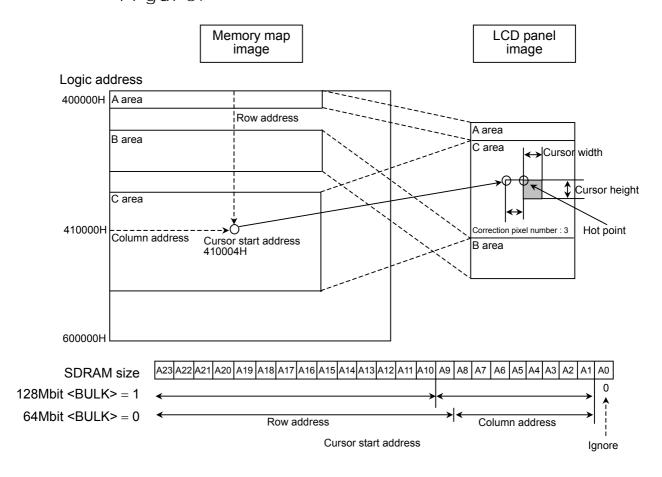

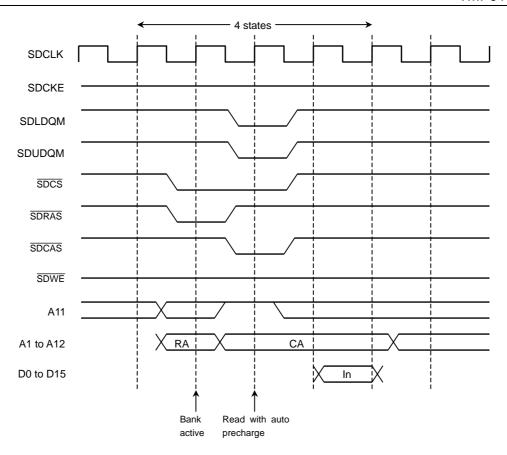

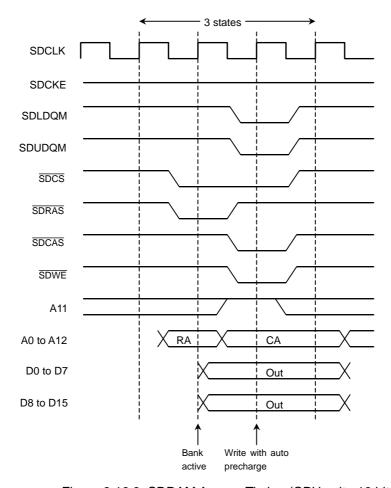

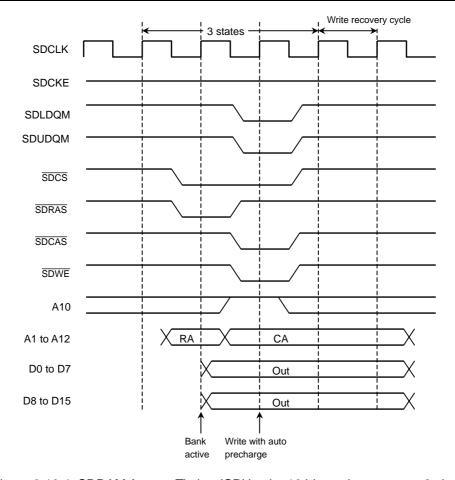

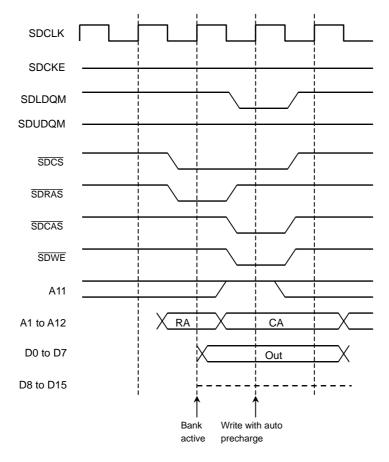

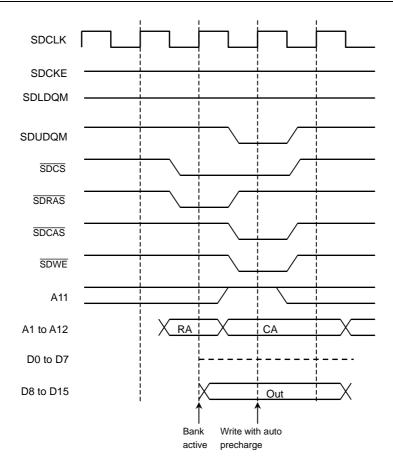

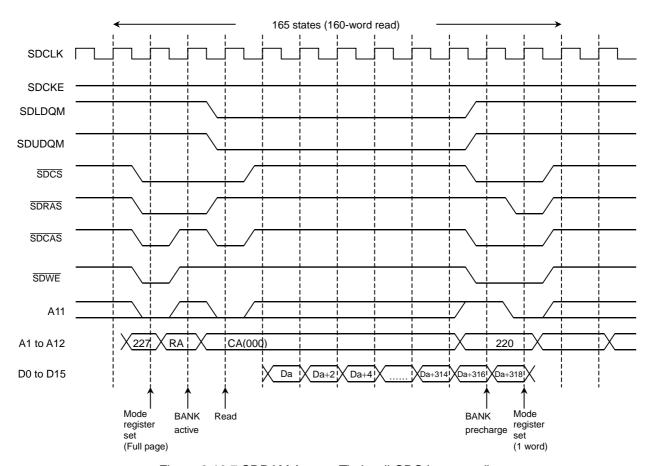

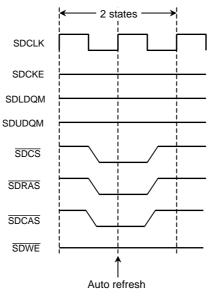

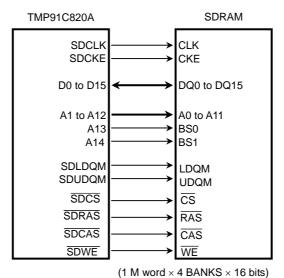

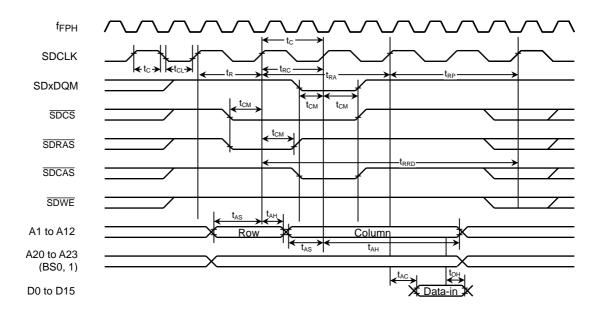

- (10) SDRAMcontroller

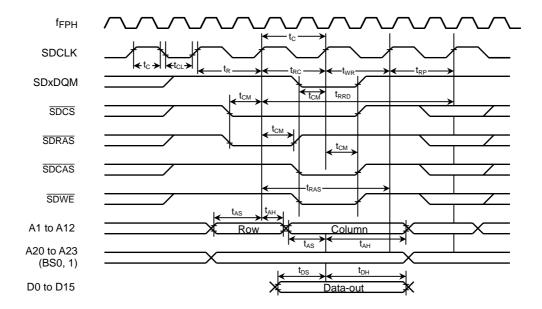

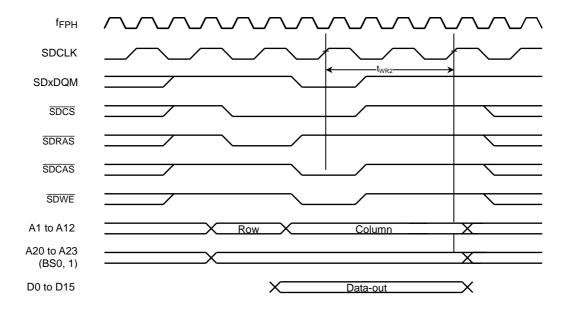

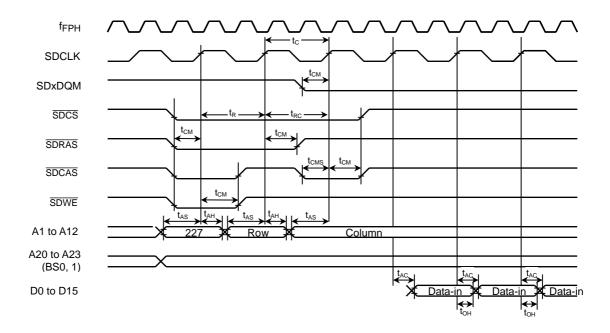

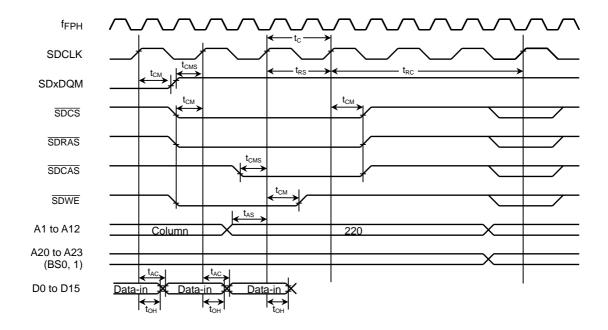

Supported 16-M, 64-Mand 128-Mbi t SDRAM with 16-bit dat

- (11) Ti mertiformerceaolck (RTC)

- Based on TC8521A

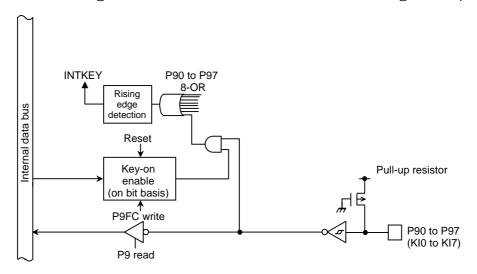

- (12) Key-on wakeup (Interrupt keyinput)

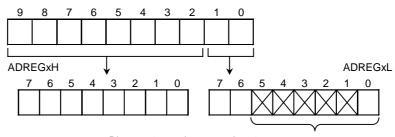

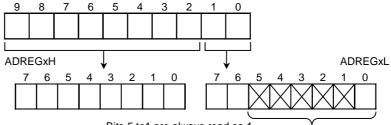

- (13) 10-bit ADconverter: 8channels

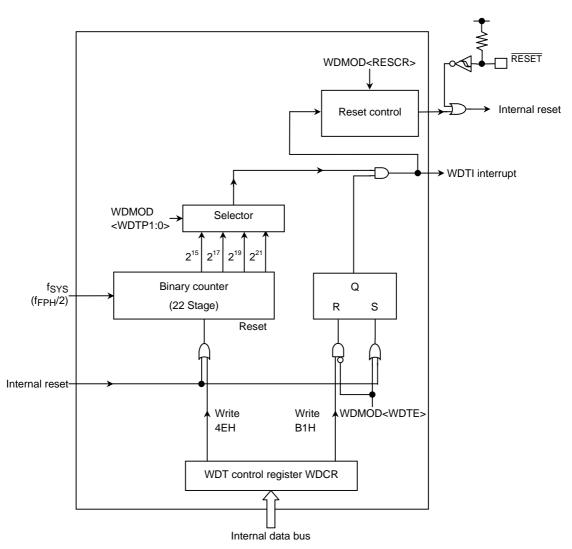

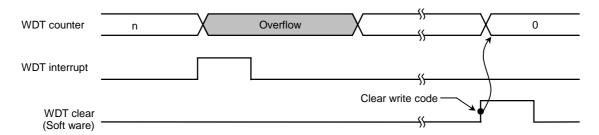

- (14) Watchdog ti mer

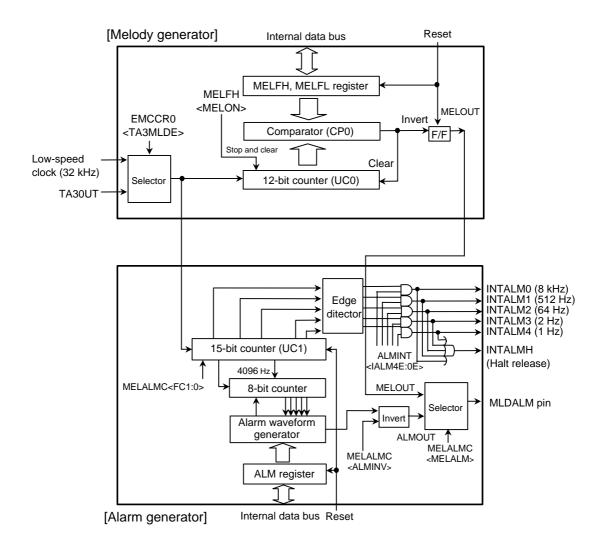

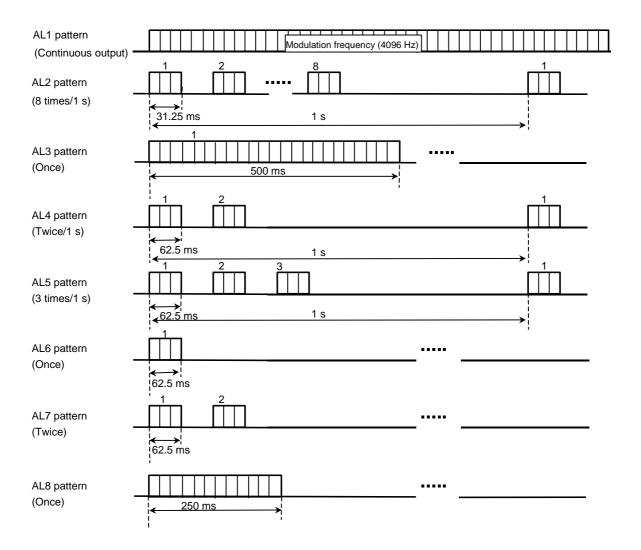

- (15) Melody/alarmgenerator

- Melody: Output of clock 4 to 5461 Hz

- Alarm: Output of the 8ki nds of alarmpattern

- Output of the 5ki nds of interval interrupt

- (16) Chipselect/wait controller: 4 channels

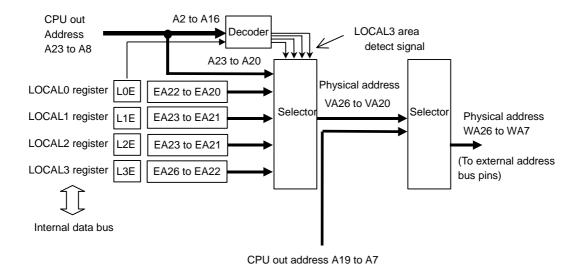

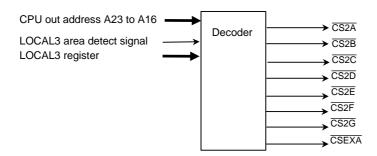

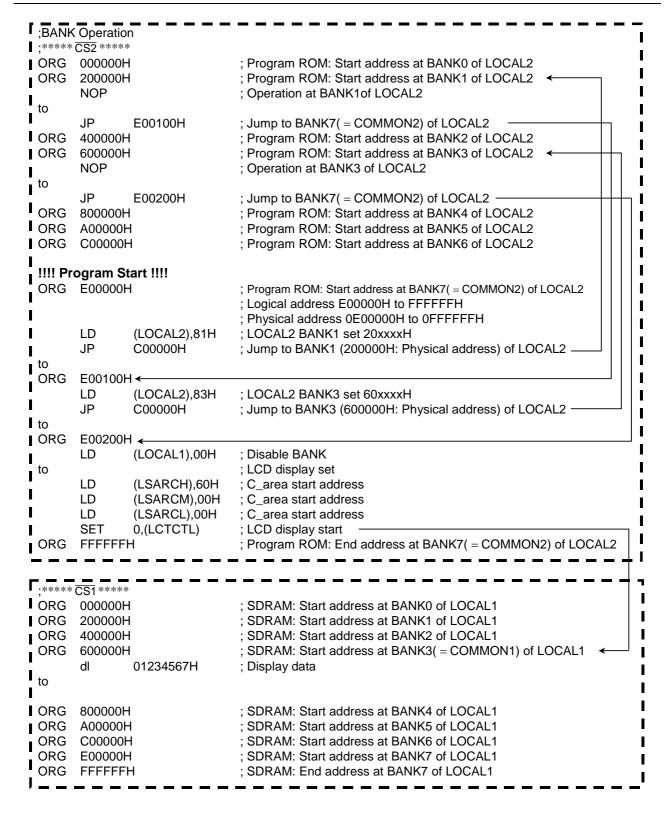

- (17) MMU

- Expandable up to 136 Mbytes (4 local area/8-bank meth

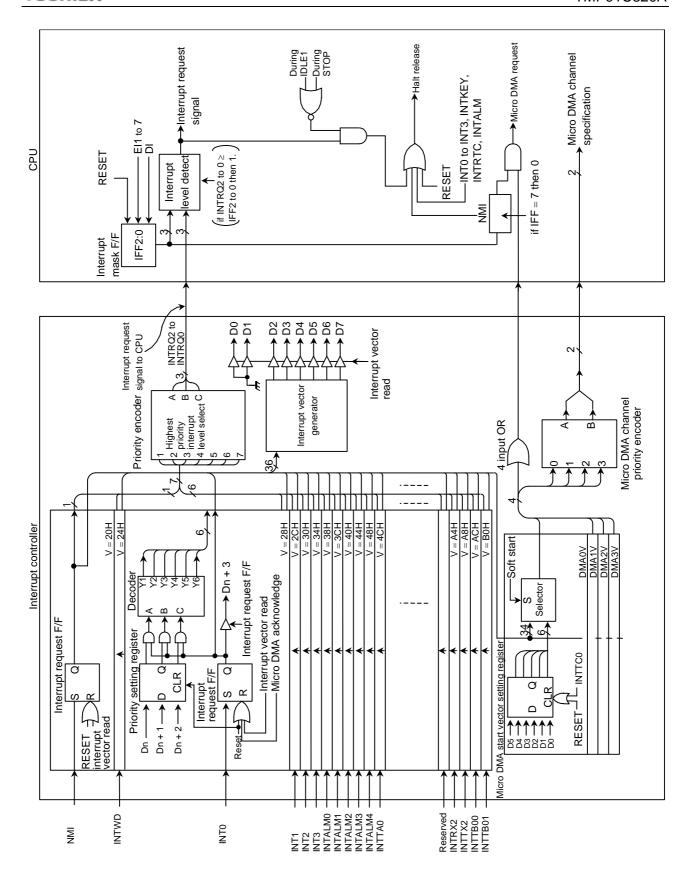

- (18) Interrupts: 46 interrupts

- 9CPUinterrupts: Softwareinterruptinstruction and

- 31 internal interrupts: Sevenselectable priorityle

- 6 external interrupts: Seven selectable priority leg

- (19) Input/outputtpeorttesr:n 27 pli6n spi(tadatabus memory)

- (20) Standby function

Three HALT modes: IDLE2 (Programmable), IDLE1, STOP

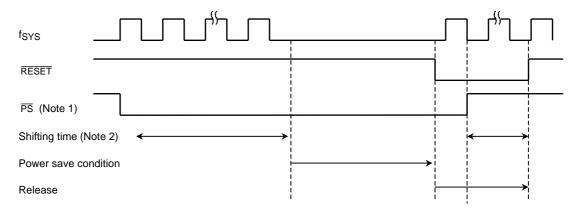

- (21) Hardware standby function (Power save function)

- (22) Triple-clock controller

- Clock doubler (DFM)

- Clock gear function: Select a high-frequency clock fctRTC (=f352.768 kHz)

- (23) Operating voltage

- VCG 2. 7 V to 3 = 257/MHfzc)

- VCG-3. OV to 3. 6=√3(6fMtHnza)x

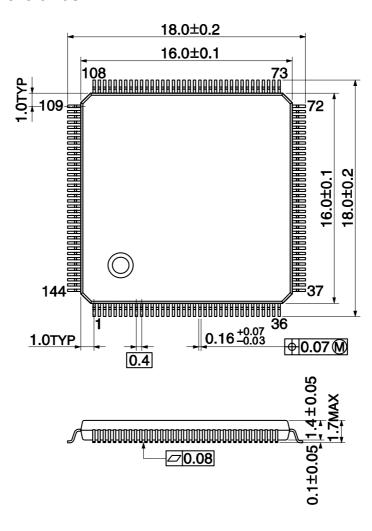

- (24) Package

- 144-pinQFP: P-LQFP144-1616-0. 40C

- Chip form supply also atvalalsabbentaont of eur local representative.

Note: When ROM code is 9999, it has no ROM.

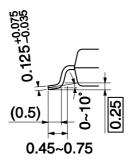

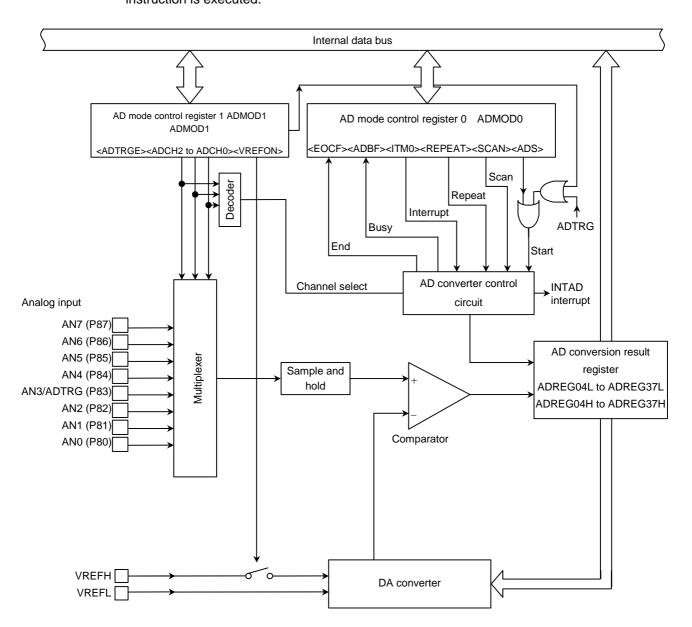

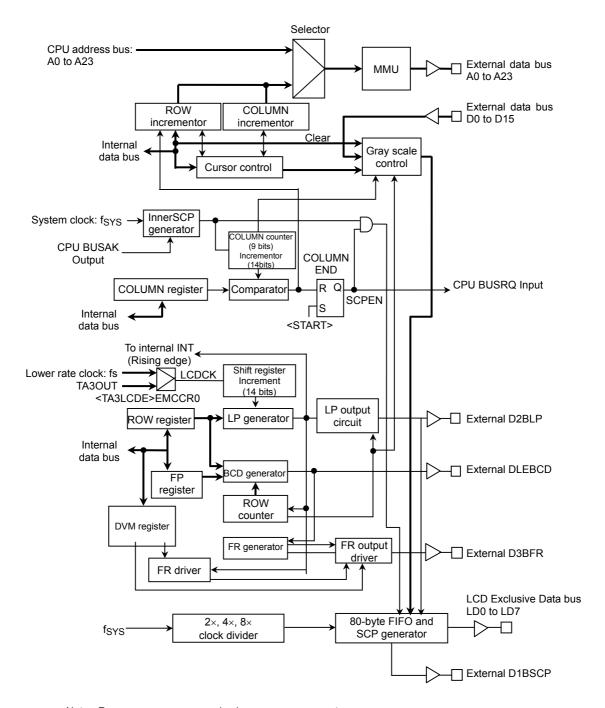

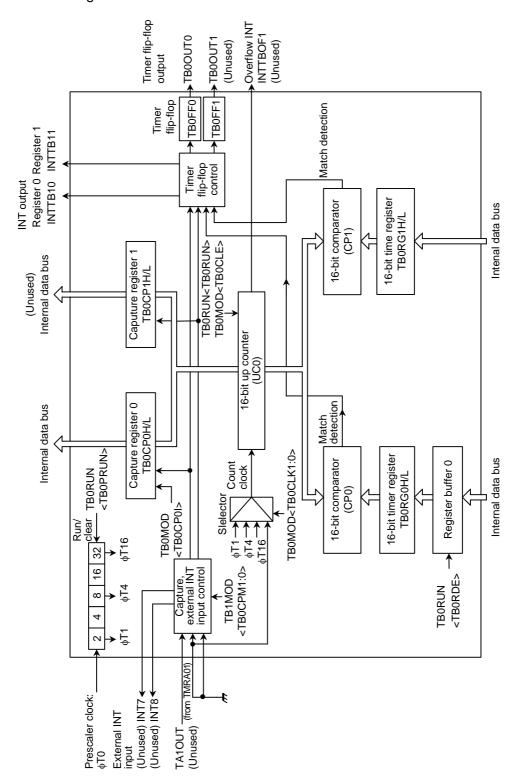

Figure 1.1 TMP91C820A Block Diagram

## 2. Pin Assignment and Pin Functions

The assignment of input/output pins for the TMP91C82OA follows:

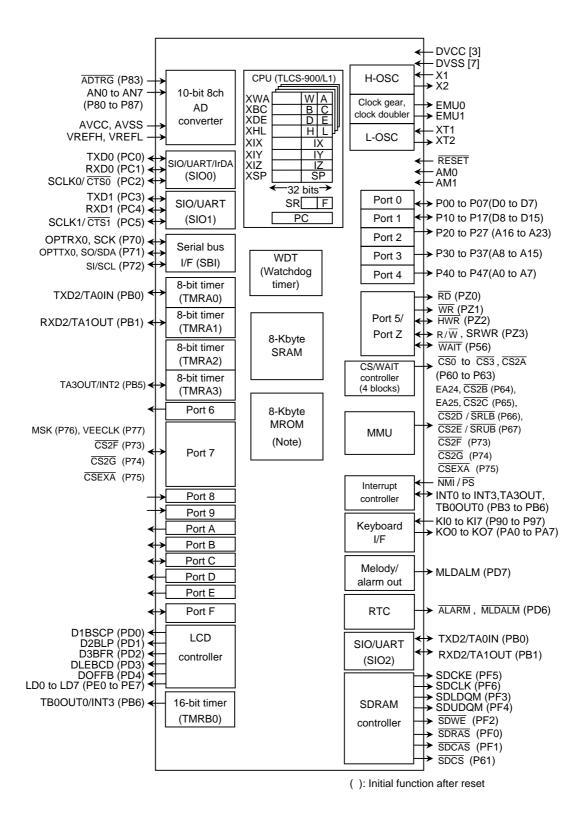

#### 2.1 Pin Assignment Diagram

Figure 2. 1. 1 shows the pinassi gnment of the TMP91C820.

Figure 2.1.1 Pin Assignment Diagram (144-pin QFP)

## 2.2 PAD layout

(Chip size 5.75 mm  $\times$  5.63 mm)

Unit: µm

| (Chip Siz | ze 5.75 mm $	imes$ | 5.63 mm)       |                          |     |       |         |                |     |       |         | Unit: μm |

|-----------|--------------------|----------------|--------------------------|-----|-------|---------|----------------|-----|-------|---------|----------|

| PIN       |                    |                |                          | PIN |       |         |                | PIN |       |         |          |

| No.       | Name               | X Point        | Y Point                  | No. | Name  | X Point | Y Point        | No. | Name  | X Point | Y Point  |

| 1         | P81                | -2742          | 2128                     | 49  | XT2   | -485    | -2682          | 97  | P37   | 2736    | 758      |

| 2         | P82                | -2742          | 2004                     | 50  | EMU0  | -370    | -2682          | 98  | DVCC2 | 2736    | 872      |

| 3         | P83                | -2742          | 1888                     | 51  | EMU1  | -256    | -2682          | 99  | P20   | 2736    | 986      |

| 4         | P84                | -2742          | 1774                     | 52  | PD1   | -142    | -2682          | 100 | DVSS5 | 2736    | 1202     |

| 5         | P85                | -2742          | 1660                     | 53  | PD2   | -28     | -2682          | 101 | P21   | 2736    | 1318     |

| 6         | P86                | -2742          | 1546                     | 54  | PD3   | 86      | -2682          | 102 | P22   | 2736    | 1432     |

| 7         | P87                | -2742          | 1432                     | 55  | PD4   | 200     | -2682          | 103 | P23   | 2736    | 1546     |

| 8         | AVSS               | -2742          | 1318                     | 56  | PE0   | 314     | -2682          | 104 | P24   | 2736    | 1660     |

| 9         | AVCC               | -2742          | 1204                     | 57  | PE1   | 428     | -2682          | 105 | P25   | 2736    | 1774     |

| 10        | P92                | -2742          | 892                      | 58  | PE2   | 542     | -2682          | 106 | P26   | 2736    | 1888     |

| 11        | P93                | -2742          | 778                      | 59  | PE3   | 656     | -2682          | 107 | P27   | 2736    | 2004     |

| 12        | P94                | -2742          | 664                      | 60  | PE4   | 770     | -2682          | 108 | PZ0   | 2736    | 2128     |

| 13        | P95                | -2742          | 550                      | 61  | PE5   | 884     | -2682          | 109 | PZ1   | 2188    | 2676     |

| 14        | P96                | -2742          | 436                      | 62  | PE6   | 998     | -2682          | 110 | PZ2   | 2062    | 2676     |

| 15        | P97                | -2742          | 322                      | 63  | PE7   | 1112    | -2682          | 111 | PZ3   | 1948    | 2676     |

| 16        | PA0                | -2742          | 208                      | 64  | DVSS3 | 1246    | -2682          | 112 | P56   | 1834    | 2676     |

| 17        | PA1                | -2742          | 94                       | 65  | P00   | 1378    | -2682          | 113 | P60   | 1720    | 2676     |

| 18        | PA2                | -2742          | -20                      | 66  | P01   | 1492    | -2682          | 114 | P61   | 1606    | 2676     |

| 19        | PA3                | -2742<br>-2742 | -134                     | 67  | P02   | 1606    | -2682          | 115 | P62   | 1492    | 2676     |

| 20        | PA4                | -2742<br>-2742 | -13 <del>4</del><br>-248 | 68  | P03   | 1720    | -2682<br>-2682 | 116 | DVSS6 | 1378    | 2676     |

| 21        | PA4<br>PA5         |                |                          | 69  | P03   |         |                |     | P63   | 1264    |          |

|           |                    | -2742          | -362                     |     |       | 1834    | -2682          | 117 |       |         | 2676     |

| 22        | PA6                | -2742          | -476<br>500              | 70  | P05   | 1948    | -2682          | 118 | P64   | 1150    | 2676     |

| 23        | PA7                | -2742          | -590<br>-704             | 71  | P06   | 2062    | -2682          | 119 | P65   | 1036    | 2676     |

| 24        | PB0                | -2742          | -704                     | 72  | P07   | 2188    | -2682          | 120 | P66   | 922     | 2676     |

| 25        | PB1                | -2742          | -818                     | 73  | P10   | 2736    | -2134          | 121 | P67   | 808     | 2676     |

| 26        | PB3                | -2742          | -932                     | 74  | P11   | 2736    | -2010          | 122 | P70   | 694     | 2676     |

| 27        | PB4                | -2742          | -1046                    | 75  | P12   | 2736    | -1894          | 123 | P71   | 580     | 2676     |

| 28        | DVSS1              | -2742          | -1210                    | 76  | P13   | 2736    | -1780          | 124 | P72   | 382     | 2676     |

| 29        | PB5                | -2742          | -1324                    | 77  | P14   | 2736    | -1666          | 125 | DVCC3 | 268     | 2676     |

| 30        | PB6                | -2742          | -1438                    | 78  | P15   | 2736    | -1552          | 126 | P73   | 68      | 2676     |

| 31        | PC0                | -2742          | -1552                    | 79  | P16   | 2736    | -1438          | 127 | P74   | -46     | 2676     |

| 32        | PC1                | -2742          | -1666                    | 80  | DVSS4 | 2736    | -1318          | 128 | P75   | -160    | 2676     |

| 33        | PC2                | -2742          | -1780                    | 81  | P17   | 2736    | -1066          | 129 | P76   | -274    | 2676     |

| 34        | PC3                | -2742          | -1894                    | 82  | P40   | 2736    | -952           | 130 | P77   | -388    | 2676     |

| 35        | PC4                | -2742          | -2010                    | 83  | P41   | 2736    | -838           | 131 | PD6   | -520    | 2676     |

| 36        | PC5                | -2742          | -2134                    | 84  | P42   | 2736    | -724           | 132 | PD7   | -634    | 2676     |

| 37        | PF0                | -2194          | -2682                    | 85  | P43   | 2736    | -610           | 133 | PF3   | -748    | 2676     |

| 38        | PF1                | -2068          | -2682                    | 86  | P44   | 2736    | -496           | 134 | PF4   | -862    | 2676     |

| 39        | PF2                | -1954          | -2682                    | 87  | P45   | 2736    | -382           | 135 | PF5   | -976    | 2676     |

| 40        | PD0                | -1840          | -2682                    | 88  | P46   | 2736    | -268           | 136 | DVSS7 | -1090   | 2676     |

| 41        | AM0                | -1726          | -2682                    | 89  | P47   | 2736    | -154           | 137 | PF6   | -1204   | 2676     |

| 42        | DVCC1              | -1612          | -2682                    | 90  | P30   | 2736    | -40            | 138 | PF7   | -1318   | 2676     |

| 43        | X2                 | -1410          | -2682                    | 91  | P31   | 2736    | 74             | 139 | P90   | -1432   | 2676     |

| 44        | DVSS2              | -1244          | -2682                    | 92  | P32   | 2736    | 188            | 140 | P91   | -1546   | 2676     |

| 45        | X1                 | -1079          | -2682                    | 93  | P33   | 2736    | 302            | 141 | NMI   | -1660   | 2676     |

| 46        | AM1                | -963           | -2682                    | 94  | P34   | 2736    | 416            | 142 | VREFL | -1954   | 2676     |

| 47        | RESET              | -849           | -2682                    | 95  | P35   | 2736    | 530            | 143 | VREFH | -2068   | 2676     |

| 48        | XT1                | -734           | -2682                    | 96  | P36   | 2736    | 644            | 144 | P80   | -2194   | 2676     |

## 2.3 Pin Names and Functions

The names of the input/output pins and their functions

Table 2.3.1 Pin Names and Functions (1/4)

| Pin Name               | Number of Pins | I/O        | Functions                                                                                              |

|------------------------|----------------|------------|--------------------------------------------------------------------------------------------------------|

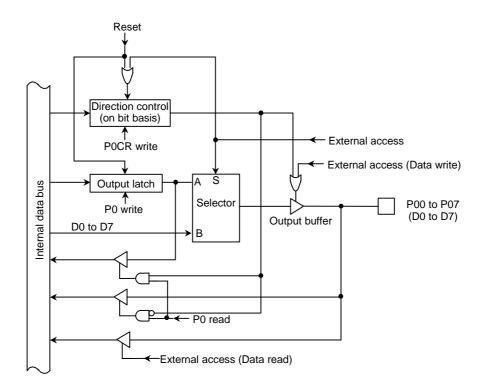

| P00 to P07<br>D0 to D7 | 8              | I/O<br>I/O | Port 0: I/O port that allows I/O to be selected at the bit level Data (Lower): Bits 0 to 7 of data bus |

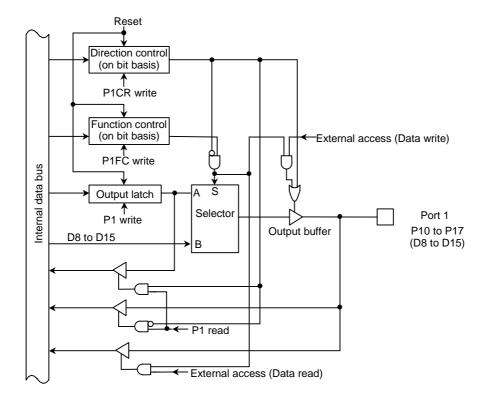

| P10 to P17             | 8              | I/O        | Port 1: I/O port that allows I/O to be selected at the bit level (When used to the external 8-bit bus) |

| D8 to D15              |                | I/O        | Data (Upper): Bits 8 to15 of data bus                                                                  |

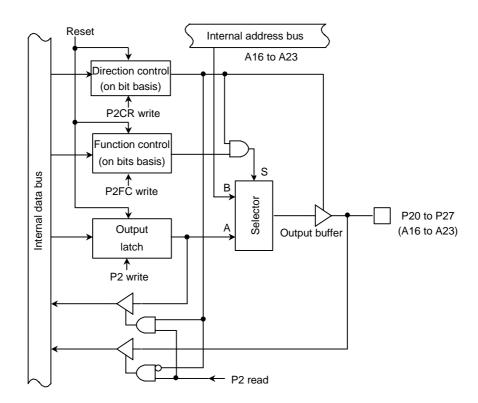

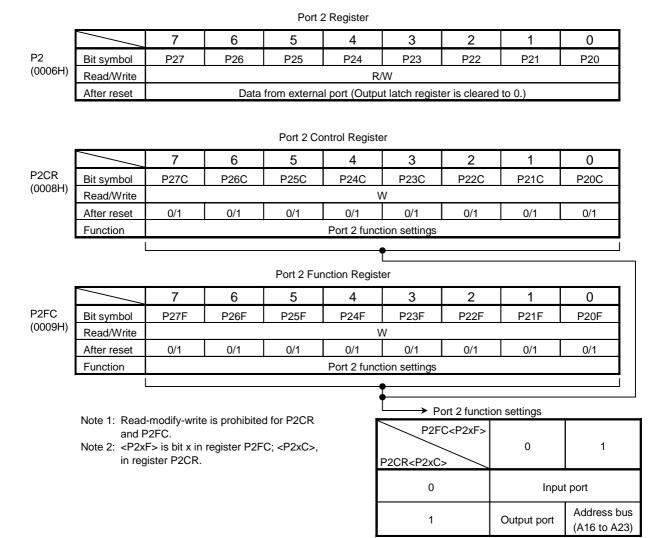

| P20 to P27             | 8              | Output     | Port 2: I/O port                                                                                       |

| A16 to A23             |                | Output     | Address: Bits 16 to 23 of address bus                                                                  |

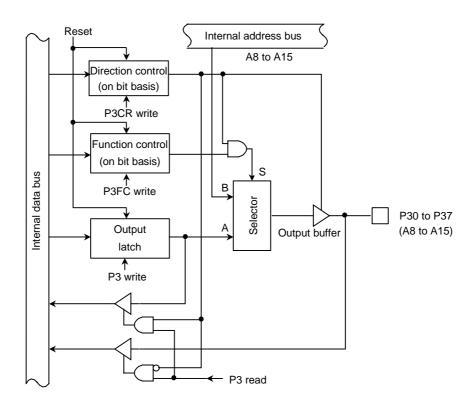

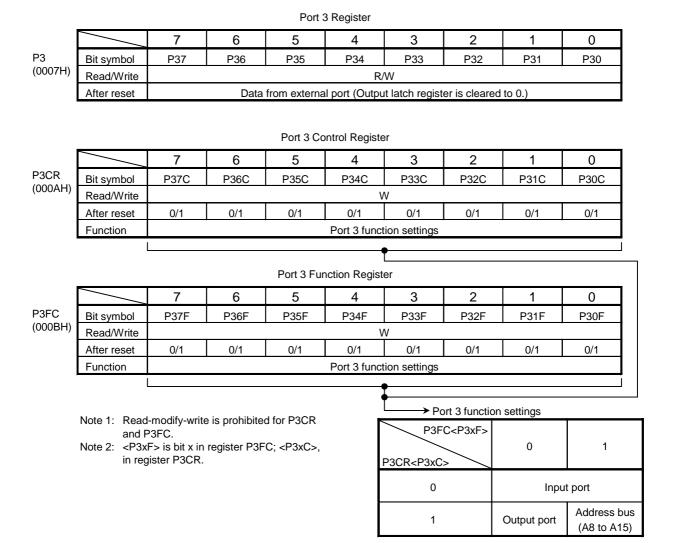

| P30 to P37             | 8              | Output     | Port 3: I/O port                                                                                       |

| A8 to A15              |                | Output     | Address: Bits 8 to 15 of address bus                                                                   |

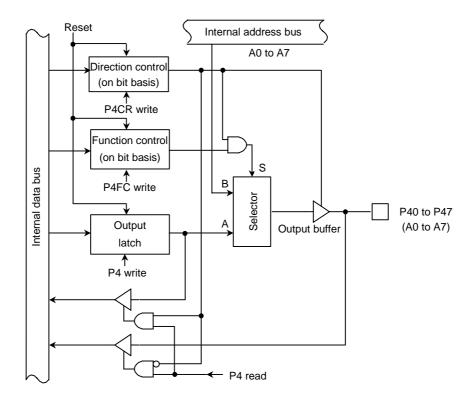

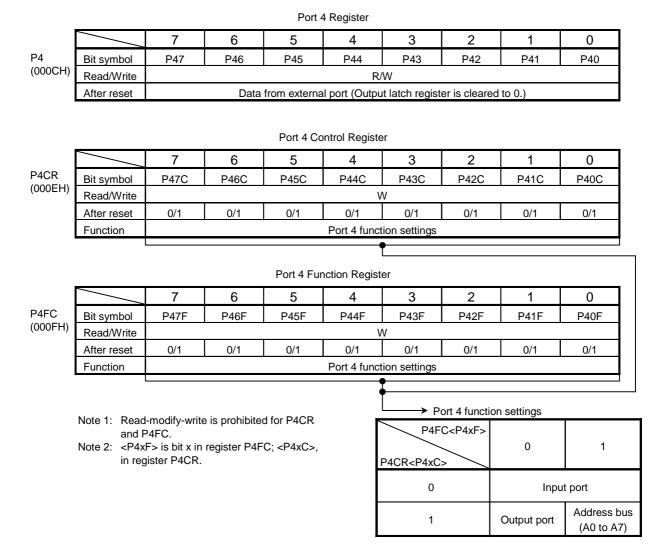

| P40 o P47              | 8              | Output     | Port 4: I/O port                                                                                       |

| A0 to A7               |                | Output     | Address: Bits 0 to 7 of address bus                                                                    |

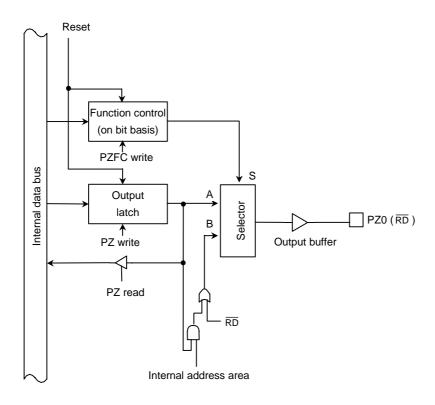

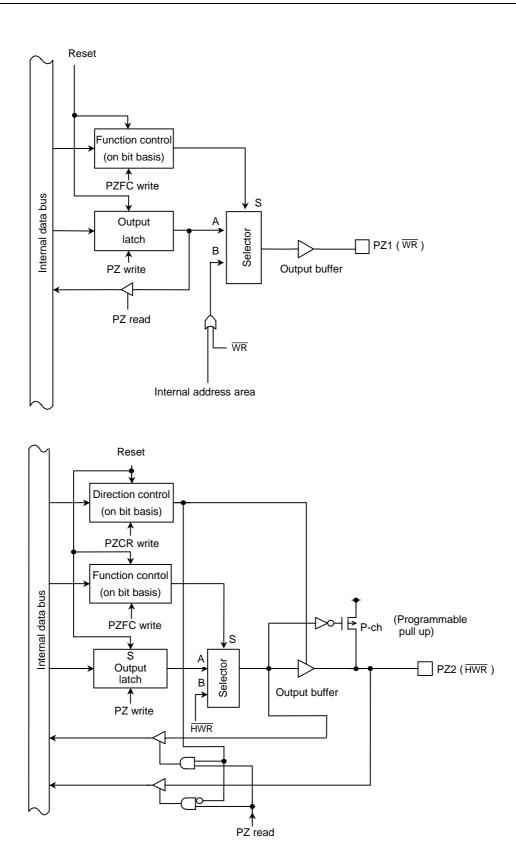

| PZ0                    | 1              | Output     | Port Z0: Output port                                                                                   |

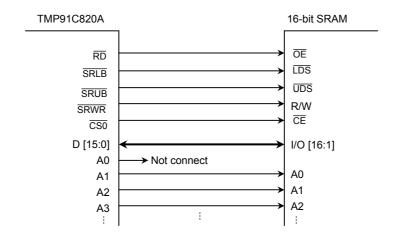

| RD                     |                | Output     | Read: Strobe signal for reading external memory                                                        |

| PZ1                    | 1              | Output     | Port Z1: Output port                                                                                   |

| WR                     |                | Output     | Write: Strobe signal for writing data to pins D0 to D7                                                 |

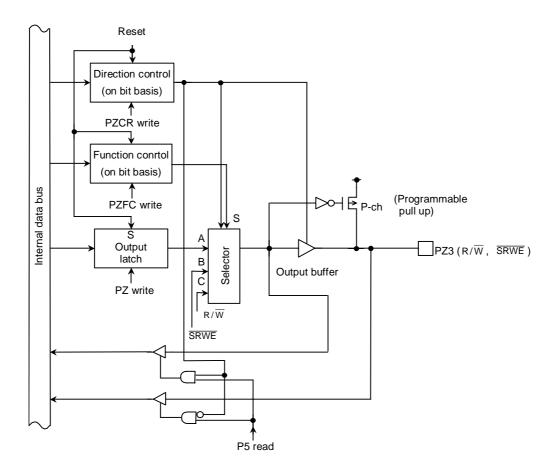

| PZ2                    | 1              | I/O        | Port Z2: I/O port (with pull-up resistor)                                                              |

| HWR                    |                | Output     | High write: Strobe signal for writing data to pins D8 to D15                                           |

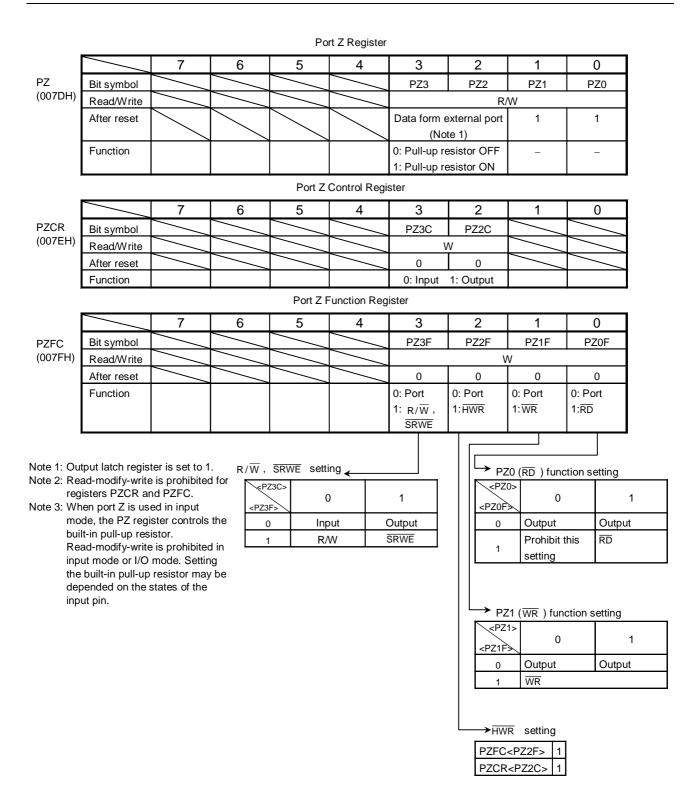

| PZ3                    | 1              | I/O        | Port Z3: I/O port (with pull-up resistor)                                                              |

| $R/\overline{W}$       |                | Output     | Read/write: 1 represents read or dummy cycle; 0 represents write cycle.                                |

| SRWR                   |                | Output     | Write for SRAM: Strobe signal for writing data.                                                        |

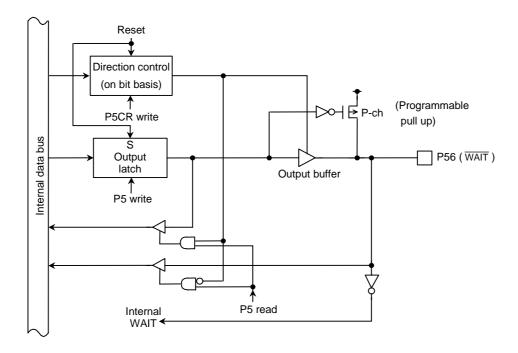

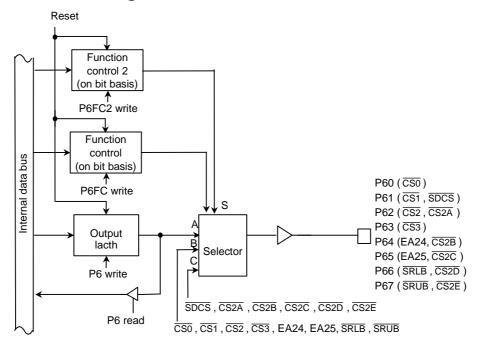

| P56                    | 1              | I/O        | Port 56: I/O port (with pull-up resistor)                                                              |

| WAIT                   |                | Input      | Wait: Pin used to request CPU bus wait                                                                 |

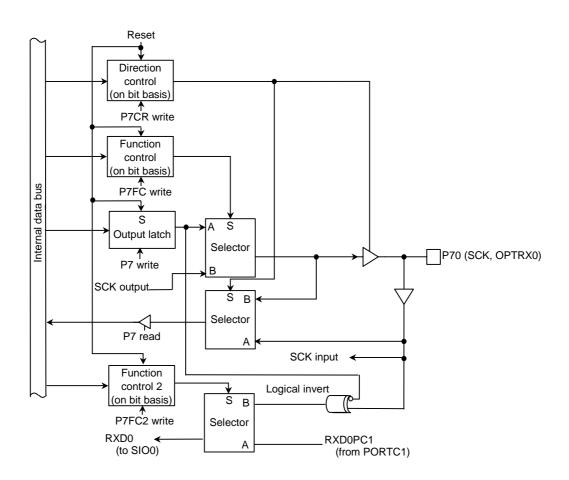

| P60                    | 1              | Output     | Port 60: Output port                                                                                   |

| CS0                    |                | Output     | Chip select 0: Outputs 0 when address is within specified address area.                                |

| P61                    | 1              | Output     | Port 61: Output port                                                                                   |

| CS1                    |                | Output     | Chip select 1: Outputs 0 when address is within specified address area                                 |

| SDCS                   |                | Output     | Chip select for SDRAM: Outputs 0 when address is within SDRAM address area                             |

| P62                    | 1              | Output     | Port 62: Output port                                                                                   |

| CS2                    |                | Output     | Chip select 2: Outputs 0 when address is within specified address area                                 |

| CS2A                   |                | Output     | Expand chip select 2A: Outputs 0 when address is within specified address area                         |

| P63                    | 1              | Output     | Port 63: Output port                                                                                   |

| CS3                    |                | Output     | Chip select 3: Outputs 0 when address is within specified address area                                 |

| P64                    | 1              | Output     | Port 64: Output port                                                                                   |

| EA24                   |                | Output     | Chip select 24: Outputs 0 when address is within specified address area                                |

| CS2B                   |                |            | Expand chip select 2B: Outputs 0 when address is within specified address area                         |

| P65                    | 1              | Output     | Port 65: Output port                                                                                   |

| EA25                   |                | Output     | Chip select 25: Outputs 0 when address is within specified address area                                |

| CS2C                   |                | Output     | Expand chip select 2C: Outputs 0 when address is within specified address area                         |

| P66                    | 1              | Output     | Port 66: Output port                                                                                   |

| CS2D                   |                | Output     | Expand chip select 2D: Outputs 0 when address is within specified address area                         |

| SRLB                   |                | Output     | Lower byte enable for SRAM: Outputs 0 when lower data is enable.                                       |

| P67                    | 1              | Output     | Port 67: Output port                                                                                   |

| CS2E                   |                | Output     | Expand chip select 2E: Outputs 0 when address is within specified address area                         |

| SRUB                   |                | Output     | Upper byte enable for SRAM: Outputs 0 when upper data is enable.                                       |

Table 2.3.2 Pin Names and Functions (2/4)

| Pin Name   | Number of Pins | I/O    | Functions                                                                                 |

|------------|----------------|--------|-------------------------------------------------------------------------------------------|

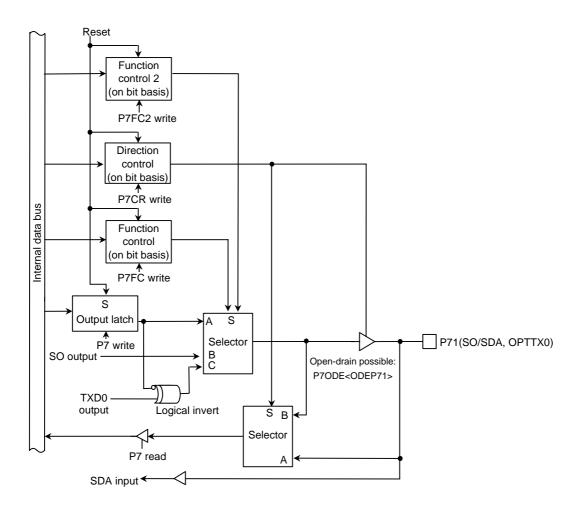

| P70        | 1              | I/O    | Port 70: I/O port                                                                         |

| SCK        |                | I/O    | Serial bus interface clock I/O data at SIO mode                                           |

| OPTRX0     |                | Input  | Serial 0 recive data                                                                      |

| P71        | 1              | I/O    | Port 71: I/O port                                                                         |

| S0         |                | Output | Serial bus interface send data at SIO mode                                                |

| SDA        |                | I/O    | Serial bus interface send/recive data at I <sup>2</sup> C bus mode                        |

|            |                |        | Open-drain output mode by programmable                                                    |

| OPTRX0     |                | Output | Serial 0 send data                                                                        |

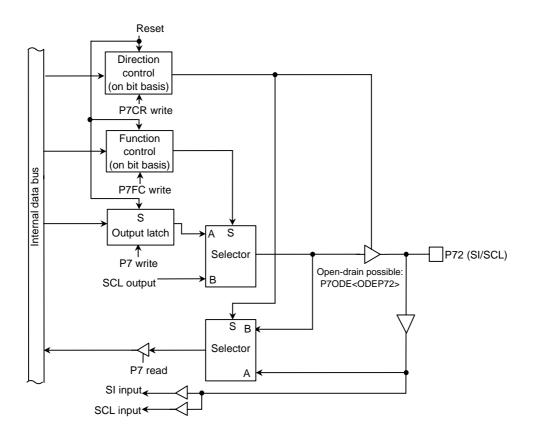

| P72        | 1              | I/O    | Port 72: I/O port                                                                         |

| SI         |                | Input  | Serial bus interface recive data at SIO mode                                              |

| SCL        |                | I/O    | Serial bus interface clock I/O data at I <sup>2</sup> C bus mode                          |

|            |                |        | Open-drain output mode by programmable                                                    |

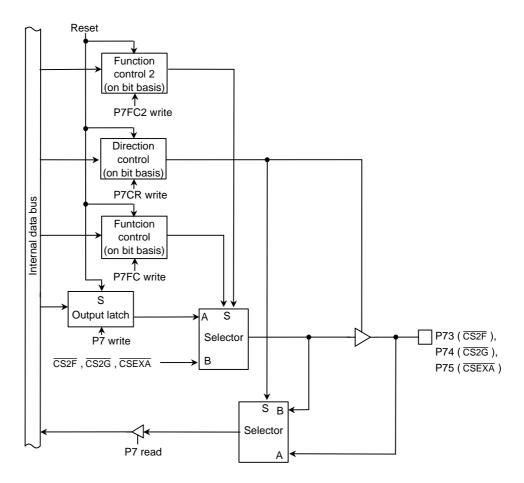

| P73        | 1              | I/O    | Port 73: I/O port                                                                         |

| CS2F       |                | Output | Expand chip select 2F: Outputs 0 when address is within specified address area            |

| P74        | 1              | I/O    | Port 74: I/O port                                                                         |

| CS2G       |                | Output | Expand chip select 2G: Outputs 0 when address is within specified address area            |

| P75        | 1              | I/O    | Port 75: I/O port                                                                         |

| CSEXA      |                | Output | Expand chip select EXA: Outputs 0 when address is within specified address area           |

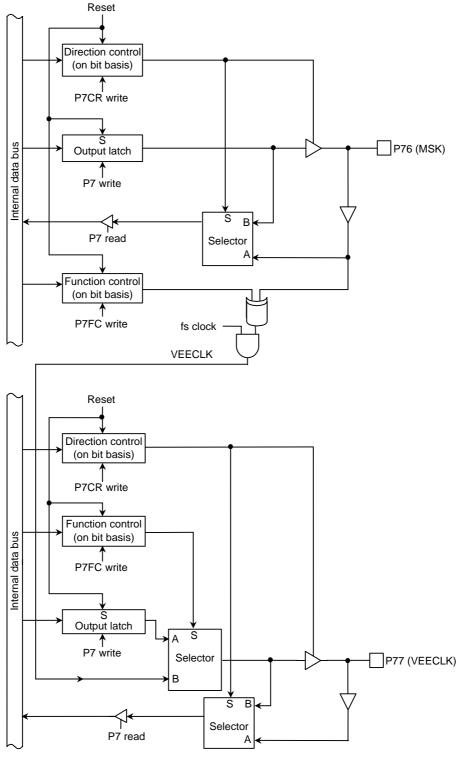

| P76        | 1              | I/O    | Port 76: I/O port                                                                         |

| MSK        |                | Input  | Mask: Use for disable to output VEECLK for LCD driver                                     |

| P77        | 1              | I/O    | Port 77: I/O port                                                                         |

| VEECLK     |                | Output | Output 32.768 kHz clock to LCD driver. (Can be disabled by MSK pin.)                      |

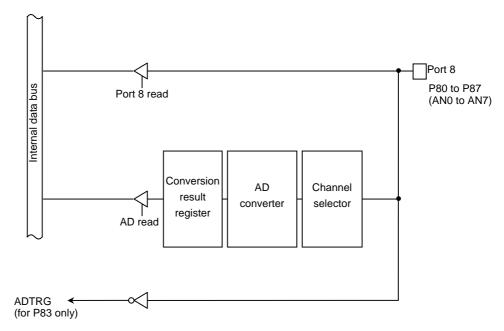

| P80 to P87 | 8              | Input  | Port 80 to 87: Pin used to input ports                                                    |

| AN0 to AN7 |                | Input  | Analog input 0 to 7: Pin used to input to AD conveter                                     |

| ADTRG      |                | Input  | AD trigger: Signal used to request AD start (with used to P83)                            |

| P90 to P97 | 8              | Input  | Port 90 to 97: Pin used to input ports                                                    |

| KI0 to KI7 |                | Input  | Key input 0 to 7: Pin used of key-on wakeup 0 to 7                                        |

|            |                |        | (Schmitt input, with pull-up resistor)                                                    |

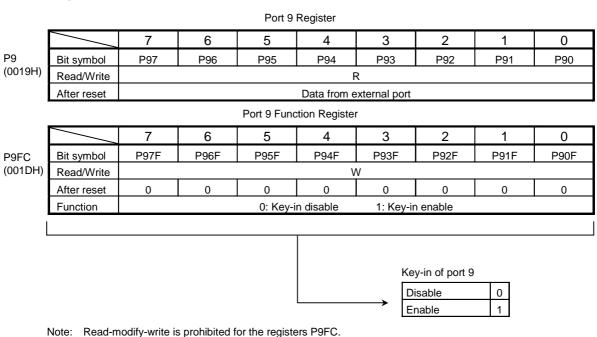

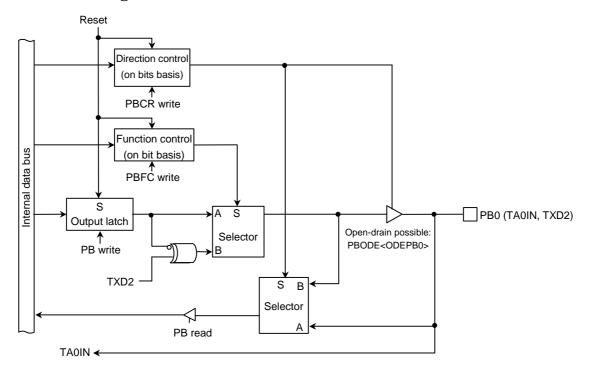

| PA0 to PA7 | 8              | Output | Port A0 to A7: Pin used to output ports                                                   |

| KO0 to KO7 |                | Output | Key output 0 to 7: Pin used of key-scan strobe 0 to 7                                     |

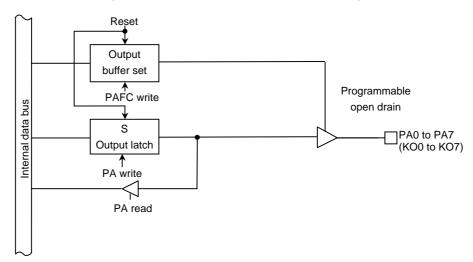

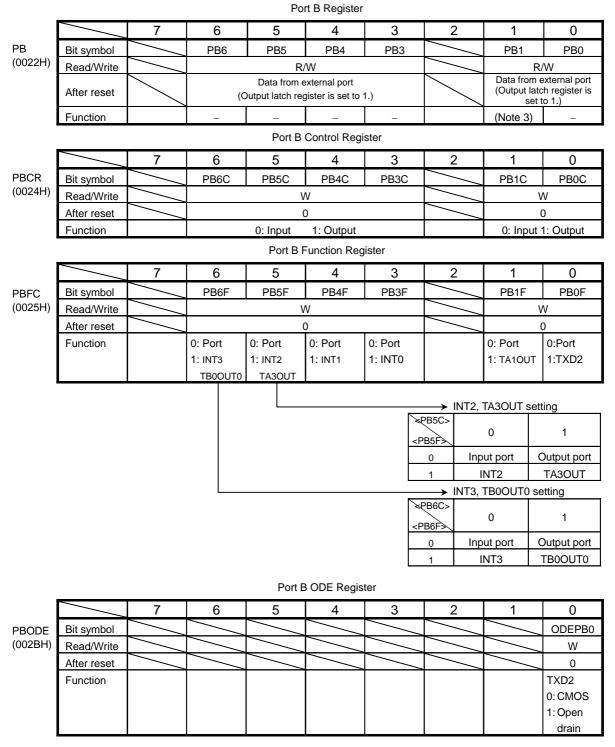

| PB0        | 1              | I/O    | Port B0: I/O port                                                                         |

| TAOIN      |                | Input  | 8-bit timer 0 input: Timer 0 input                                                        |

| TXD2       |                | Output | Serial 2 send data: Open-drain output pin by programmable                                 |

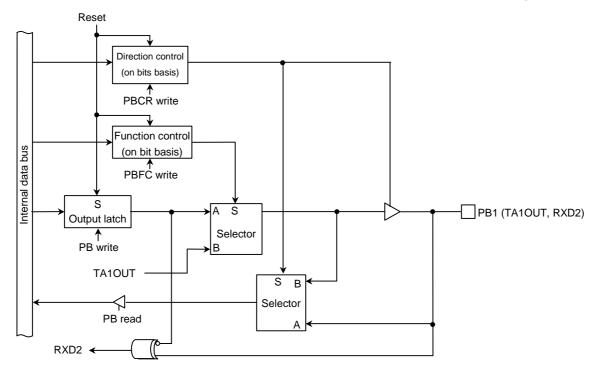

| PB1        | 1              | I/O    | Port B1: I/O port                                                                         |

| TA1OUT     |                | Output | 8-bit timer 1 output: Timer 1 output                                                      |

| RXD2       |                | Input  | Serial 2 receive data                                                                     |

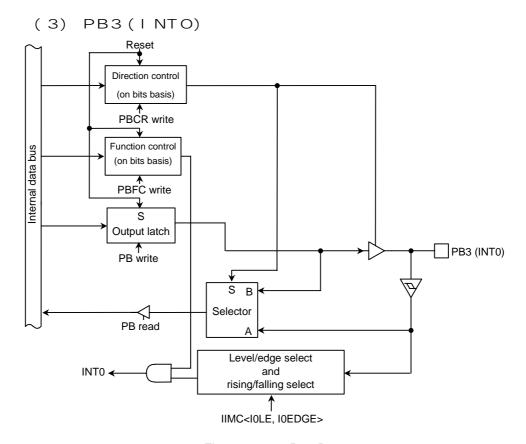

| PB3        | 1              | I/O    | Port B3: I/O port                                                                         |

| INT0       |                | Input  | Interrupt request pin0: Interrupt request pin with programmable level/rising/falling edge |

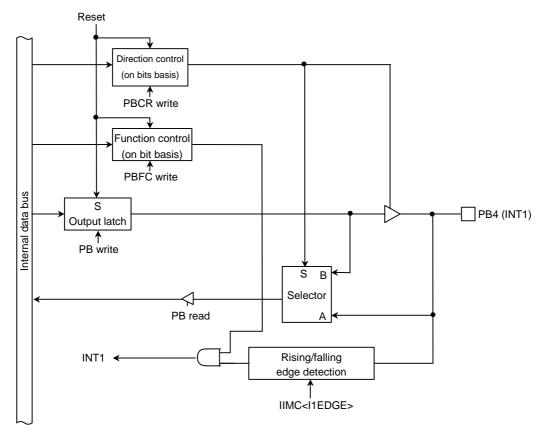

| PB4        | 1              | I/O    | Port B4: I/O port                                                                         |

| INT1       |                | Input  | Interrupt request pin1: Interrupt request pin with programmable rising/falling edge       |

Table 2.3.3 Pin Names and Functions (3/4)

| Pin Name   | Number of Pins | I/O    | Functions                                                                             |

|------------|----------------|--------|---------------------------------------------------------------------------------------|

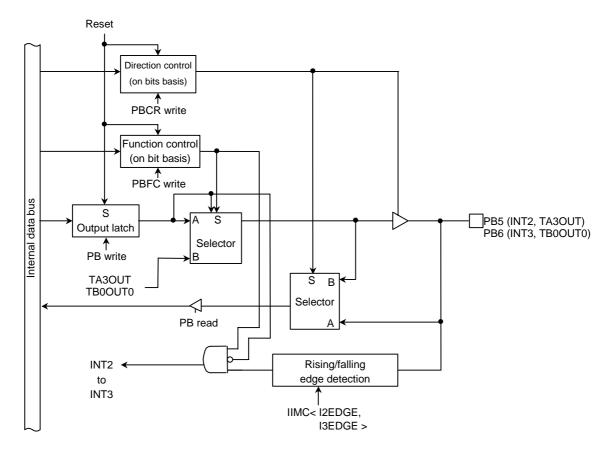

| PB5        | 1              | I/O    | Port B5: I/O port                                                                     |

| INT2       |                | Input  | Interrupt request pin2: Interrupt request pin with programmable rising/falling edge   |

| TA3OUT     |                | Output | 8-bit timer 3 output: Timer 3 output                                                  |

| PB6        | 1              | I/O    | Port B6: I/O port                                                                     |

| INT3       |                | Input  | Interrupt request pin3: Interrupt request pin with programmable rising/falling edge   |

| TB0OUT0    |                | Outout | Timer B0 output                                                                       |

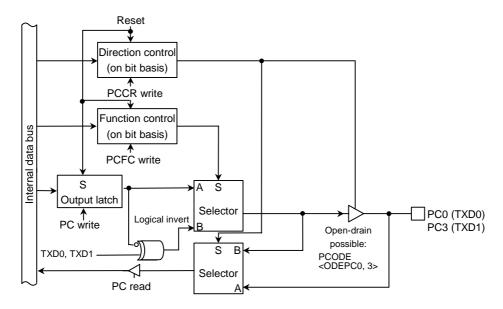

| PC0        | 1              | I/O    | Port C0: I/O port                                                                     |

| TXD0       |                | Output | Serial 0 send data: Open-drain output pin by programmable                             |

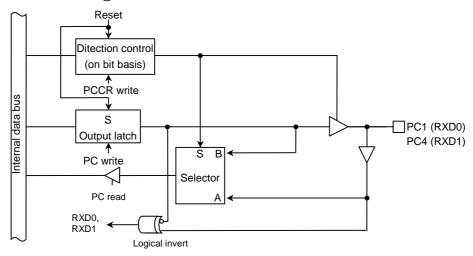

| PC1        | 1              | I/O    | Port C1: I/O port                                                                     |

| RXD0       |                | Input  | Serial 0 receive data                                                                 |

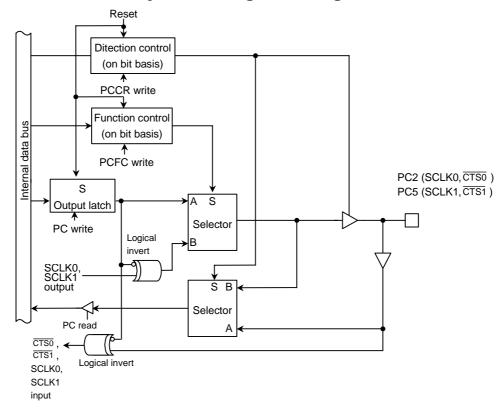

| PC2        | 1              | I/O    | Port C2: I/O port                                                                     |

| SCLK0      |                | I/O    | Serial 0 clock I/O                                                                    |

| CTS0       |                | Input  | Serial 0 data send enable (Clear to send)                                             |

| PC3        | 1              | I/O    | Port C3: I/O port                                                                     |

| TXD1       |                | Output | Serial 1 send data                                                                    |

|            |                | ·      | Open-drain output pin by programmable                                                 |

| PC4        | 1              | I/O    | Port C4: I/O port                                                                     |

| RXD1       |                | Input  | Serial 1 receive data                                                                 |

| PC5        | 1              | I/O    | Port C5: I/O port                                                                     |

| SCLK1      |                | I/O    | Serial 1 clock I/O                                                                    |

| CTS1       |                | Input  | Serial 1 data send enable (Clear to send)                                             |

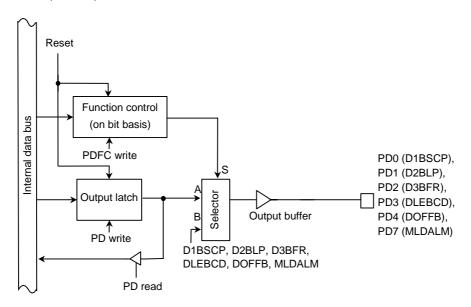

| PD0        | 1              | Output | Port D0: Output port                                                                  |

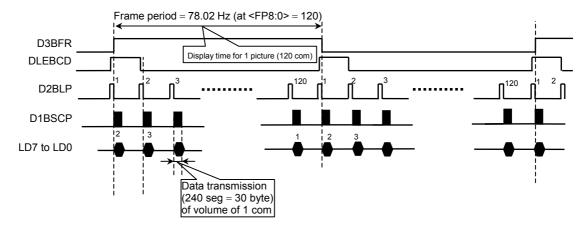

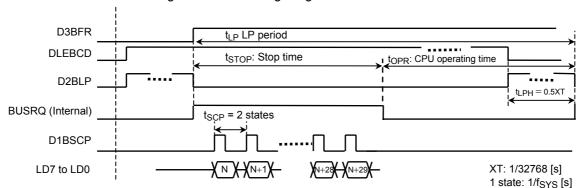

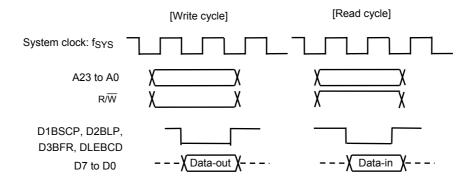

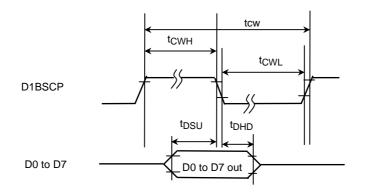

| D1BSCP     |                | Output | LCD driver output pin                                                                 |

| PD1        | 1              | Output | Port D1: Output port                                                                  |

| D2BLP      |                | Output | LCD driver output pin                                                                 |

| PD2        | 1              | Output | Port D2: Output port                                                                  |

| D3BFR      |                | Output | LCD driver output pin                                                                 |

| PD3        | 1              | Output | Port D3: Output port                                                                  |

| DLEBCD     |                | Output | LCD driver output pin                                                                 |

| PD4        | 1              | Output | Port D4: Output port                                                                  |

| DOFFB      |                | Output | LCD driver output pin                                                                 |

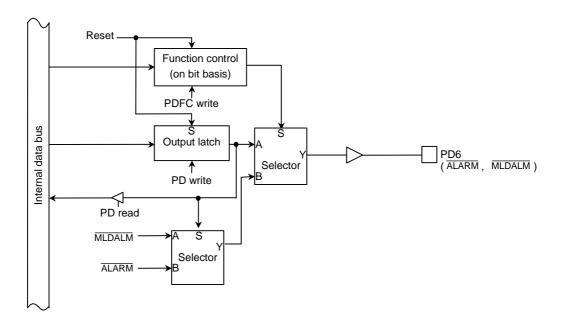

| PD6        | 1              | Output | Port D6: Output port                                                                  |

| ALARM      |                | Output | RTC alarm output pin                                                                  |

| MLDALM     |                | Output | Melody/alarm output pin (Inverted)                                                    |

| PD7        | 1              | Output | Port D7: Output port                                                                  |

| MLDALM     |                | Output | Melody/alarm output pin                                                               |

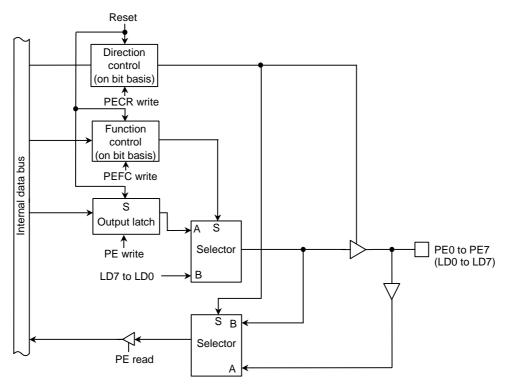

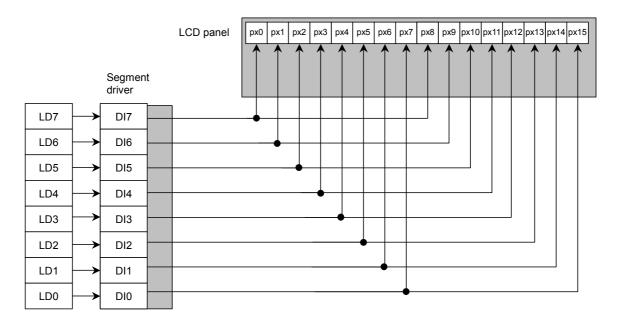

| PE0 to PE7 | 8              | I/O    | Port E0 to E7: I/O port                                                               |

| LD0 to LD7 |                | Output | Data bus for LCD driver                                                               |

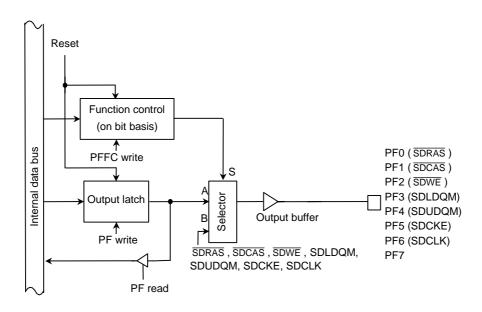

| PF0        | 1              | I/O    | Port F0: Output port                                                                  |

| SDRAS      |                | Output | Row address storobe for SDRAM: Outputs 0 when address is within SDRAM address area    |

| PF1        | 1              | I/O    | Port F1: Output port                                                                  |

| SDCAS      | <u> </u>       | Output | Column address storobe for SDRAM: Outputs 0 when address is within SDRAM address area |

Table 2.3.4 Pin Names and Functions (4/4)

|            | 1              |        |                                                                                                           |

|------------|----------------|--------|-----------------------------------------------------------------------------------------------------------|

| Pin Name   | Number of Pins | I/O    | Functions                                                                                                 |

| PF2        | 1              | Output | Port F2: Output port                                                                                      |

| SDWE       |                | Output | Write enable for SDRAM                                                                                    |

| PF3        | 1              | Output | Port F3: Output port                                                                                      |

| SDLDQM     |                | Output | Lower data enable for SDRAM                                                                               |

| PF4        | 1              | Output | Port F4: Output port                                                                                      |

| SDUDQM     |                | Output | Upper data enable for SDRAM                                                                               |

| PF5        | 1              | Output | Port F5: Output port                                                                                      |

| SDCKE      |                | Output | Clock enable for SDRAM                                                                                    |

| PF6        | 1              | Output | Port F6: Output port                                                                                      |

| SDCLK      |                | Output | Clock for SDRAM                                                                                           |

| PF7        | 1              | Output | Port F7: Output port                                                                                      |

| PS         | 1              | Input  | Power save mode setting terminal                                                                          |

| NMI        |                | Input  | Non-maskable interrupt request: Interrupt request pin with programmable                                   |

| (Note)     |                |        | falling edge level or with both edge levels programmable                                                  |

| AM0 to AM1 | 2              | Input  | Operation mode:                                                                                           |

|            |                |        | Fixed to AM1 = 1, AM0 = 1 when using internal ROM (when ROM code is 9999, setting is prohibitted).        |

|            |                |        | Fixed to AM1 = 0, AM0 = 1 when using external ROM by 16-bit external bus, or 8- or 16-bit dynamic sizing. |

|            |                |        | Fixed to AM1 = 0, AM0 = 0 when using external ROM by 8-bit external bus.                                  |

| EMU0       | 1              | Output | Open pin                                                                                                  |

| EMU1       | 1              | Output | Open pin                                                                                                  |

| RESET      | 1              | Input  | Reset: Initializes TMP91C820A (with pull-up resistor).                                                    |

| VREFH      | 1              | Input  | Pin for reference voltage input to AD converter (H)                                                       |

| VREFL      | 1              | Input  | Pin for reference voltage input to AD converter (L)                                                       |

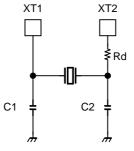

| X1/X2      | 2              | I/O    | High-frequency oscillator connection pins                                                                 |

| XT1/XT2    | 2              | I/O    | Low-frequency oscillator connection pins                                                                  |

| AVCC       | 1              |        | Power supply pin for AD converter                                                                         |

| AVSS       | 1              |        | GND pin for AD converter (0 V)                                                                            |

| DVCC       | 3              |        | Power supply pins (All VCC pins should be connecyed with the power supply pin).                           |

| DVSS       | 7              |        | GND pins (All pins should be connected with GND (0 V).)                                                   |

Note: Please input 1 into  $\overline{NMI}/\overline{PS}$  pin, because  $\overline{NMI}/\overline{PS} = 0$  means power save mode after reset.

## 3. Operation

This following describes block by block the functions ar Notes and restrictions for eatch book are outlined in 6 "end of this manual.

#### 3.1 CPU

The TMP91C82OA incorporatnese at 16 is ght poemuf (oTrhne 900/L1CP) operation, see the "TLCS-900/L1CPU".

The following describe the unique function of the CPL functions are not covered in the TLCS-900/L1 CPU section

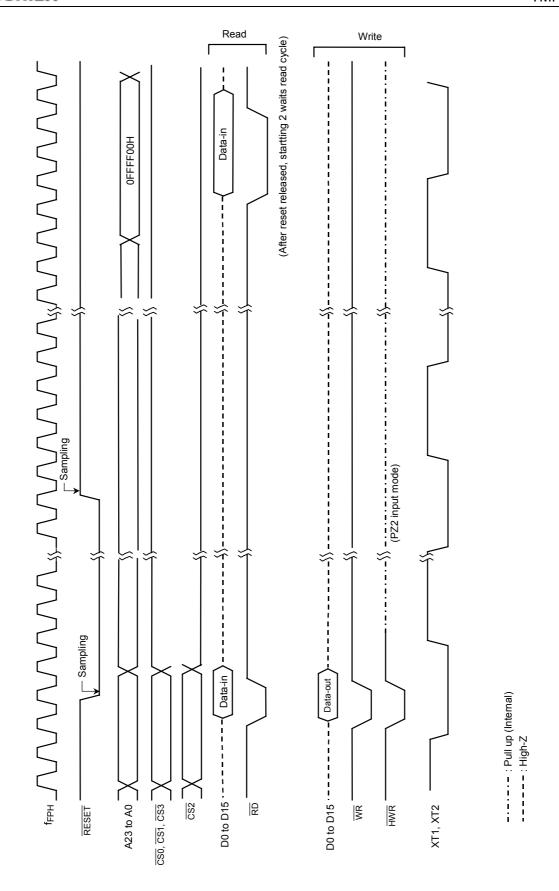

#### 3.1.1 Reset

When resetting the TMP9108,20A smircer obboth through one wer supis within the operating voltage range, and that their stabilized. Threshe in opdithelow level for at lease satt 140 sys MHz).

Thus, when turn on the sewpictworder, stouch ty twoot thage is within voltage range, and that the internal high-frequency of RESET nput to low level at least for 10 system clocks.

Clock gear is initialize ple1r/a1t6 mode by meesetthat the mode of set teff cc//18622).

When the reset is accept, the CPU:

Sets as follows the program counter (PC) in accord at address FFFFOOH to FFFFO2H:

PC<7: O→ Value at FFFFOOHaddress

PC<15: ⊌ ¥al ue at FFFFO1 Haddress

PC<23: 46/al ue at FFFFO2Haddress

- Sets the stack pointer (XSP) to 100H.

- Sets bits <IFF2: O> of the status register (SR) to register to level 7).

- Sets the <MAX> bit of the status register to 1 (MAX (Note: As this product does not support MI N mode, or

- Clears bits < RFP2: O> of the status register to OOO When reset is released with englo Plustrau of the corescinaccor program counter setting ter CSP to the the notable media bove downenthe reset is released.

When the reset is accepited that CP/LOs eptos ts, and of ollows.

Initializes the internal I/Oregisters.

Sets the port pins, inclsuedaiontgatsnie mpt ennsntahlalt/aO, to ge input or output port mode.

Note: The CPU internal register (except to PC, SR, XSP) and internal RAM data do not change by resetting.

Figure 3. 1. 1 is a reset timing of the TMP 91 C8 20 A - 9

**TOSHIBA**

Figure 3.1.1 TMP91C820A-9999 Reset Timing Example (The case of using external ROM)

## 3.2 Memory Map

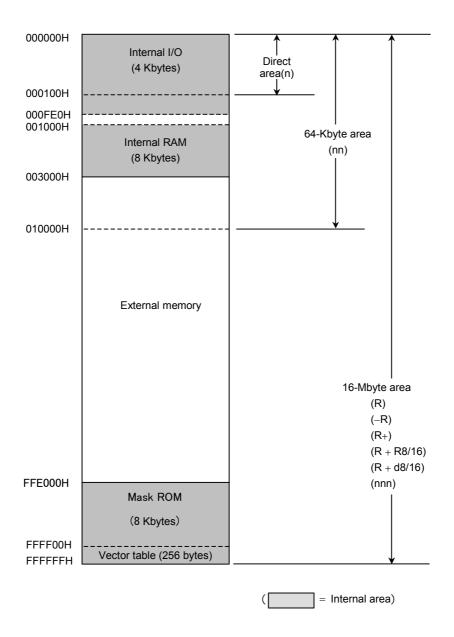

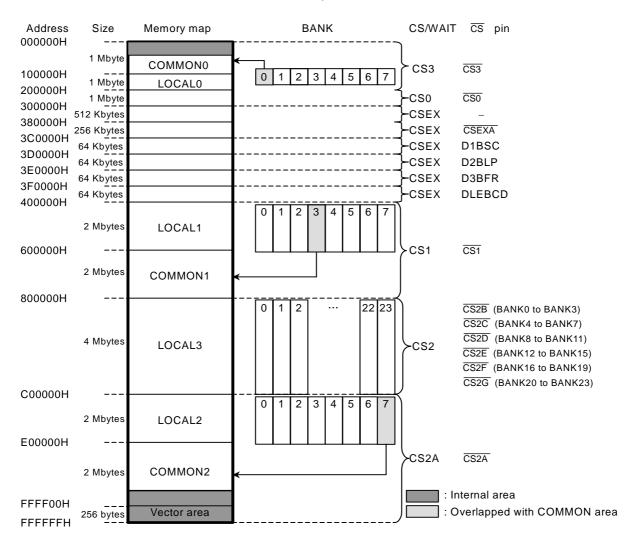

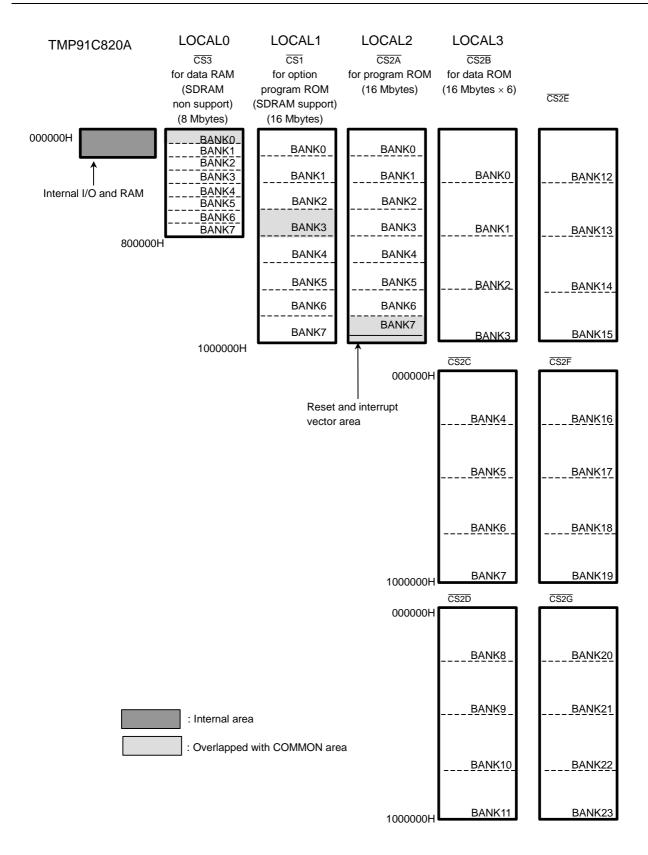

Figure 3. 2. 1 is a memory map of the TMP91C82OA.

Figure 3.2.1 Memory Map

Note: Address 000FE0H to 000FFFH is assigned for the external memory area of built-in RAM type LCD driver.

And when ROM code is 9999, internal mask ROM area also defines external memory area.

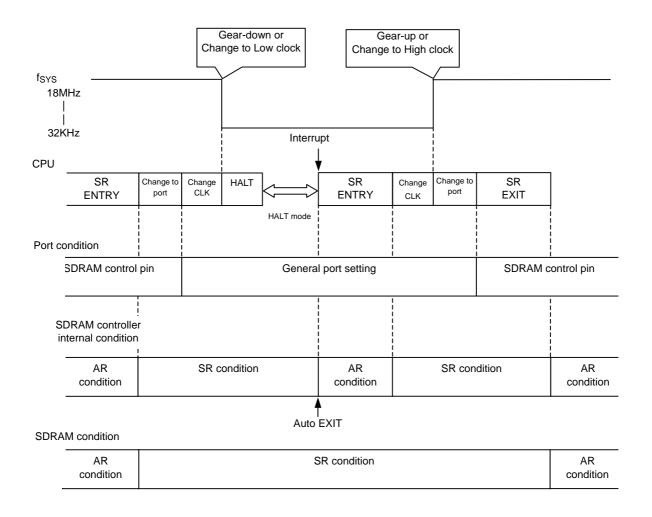

## 3.3 Triple Clock Function and Standby Function

TMP91C82OA contains (1) Clock gear, (2) Clock doubler (4) Noise-reducing circuit. It is used for low-power, I This chapter is organized as follows:

- 3. 3. 1 Block Diagram of System Clock

- 3. 3. 2 SFRs

- 3. 3. 3 SystemClock Controller

- 3. 3. 4 Prescaler Clock Controller

- 3. 3. 5 Clock Doubler (DFM)

- 3. 3. 6 Noise Reduction Circuits

- 3. 3. 7 Standby Controller

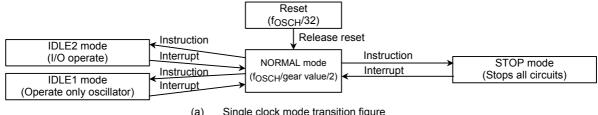

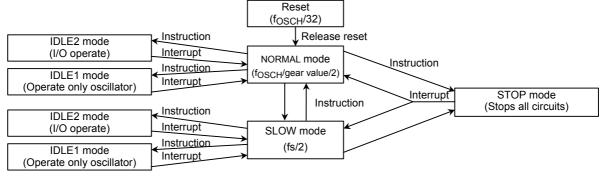

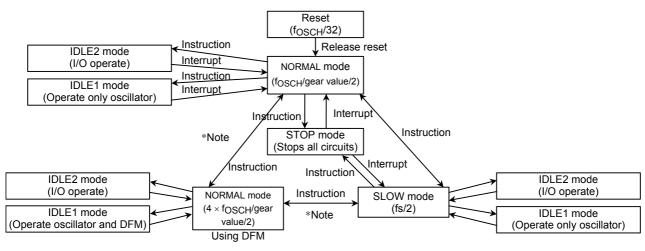

The clock operating modes are castlo mbd exs(:X(1a)X 2ipnigns on clock mode (X1, X2, XT1 and XT2pi osk mode (C) HerX1, X2, XT1 and DFM).

Figure 3. 3. 1 shows a transition figure.

Single clock mode transition figure

Dual clock mode transition fiigure (b)

- Triple clock mode transition figure

- Note 1: It's prohibited to control DFM in SLOW mode when shifting from SLOW mode to NORMAL mode with use of DFM. (DFM start up/stop/change write to DFMCR0<ACT1:0> register.)

- Note 2: If you shift from NORMAL mode with use of DFM to NORMAL mode, the instruction should be separated into two procedures as below. Change CPU clock → Stop DFM circuit.

- Note 3: It's prohibited to shift from NORMAL mode with use of DFM to STOP mode directly. You should set NORMAL mode once, and then shift to STOP mode. (You should stop high frequency oscillator after you stop DFM.)

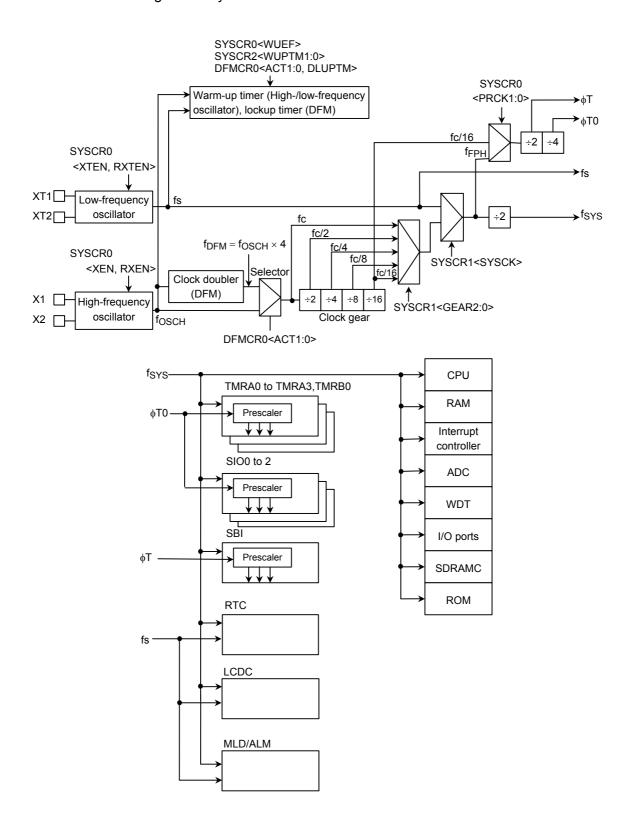

Figure 3.3.1 System Clock Block Diagram

The clock frequency inputnfsricosmotable 1261dafrocda Xh2dptihe clock f from the XT1 and XT2 pins is called fs. The clock frequer called the sympthe Timbed so you sk t fearn is is colored fineable avisit the discrepance knowledge of the colored colored the colored colored the colored colored colored the colored colored colored the colored col one cycycycs osfdfefined to as one state.

## 3.3.1 Block Diagram of System Clock

Figure 3.3.2 Block Diagram of System Clock

### 3.3.2 SFRs

|         |             | 7                                                          | 6                                                                 | 5                                                                                                       | 4                                                                                                     | 3                                                                        | 2                                                                                                      | 1                                                                                       | 0                                                                                |

|---------|-------------|------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| SYSCR0  | Bit symbol  | XEN                                                        | XTEN                                                              | RXEN                                                                                                    | RXTEN                                                                                                 | RSYSCK                                                                   | WUEF                                                                                                   | PRCK1                                                                                   | PRCK0                                                                            |

| (00E0H) | Read/Write  |                                                            |                                                                   |                                                                                                         | R/                                                                                                    | W                                                                        |                                                                                                        |                                                                                         |                                                                                  |

|         | After reset | 1                                                          | 1                                                                 | 1                                                                                                       | 0                                                                                                     | 0                                                                        | 0                                                                                                      | 0                                                                                       | 0                                                                                |

|         | Function    | 0: Stop                                                    | Low-<br>frequency<br>oscillator (fs)<br>0: Stop<br>1: Oscillation | High-<br>frequency<br>oscillator (fc)<br>after release<br>of STOP<br>mode<br>0: Stop<br>1: Oscillation  | Low-<br>frequency<br>oscillator (fs)<br>after release<br>of STOP<br>mode<br>0: Stop<br>1: Oscillation | Selects clock<br>after release<br>of STOP<br>mode<br>0: fc<br>1: fs      | Warm-up timer  0: Write don't care 1: Write start timer 0: Read end warm up 1: Read do not end warm up | Select presca<br>00: f <sub>FPH</sub> (Not<br>01: Reserved<br>10: fc/16<br>11: Reserved |                                                                                  |

|         |             | 7                                                          | 6                                                                 | 5                                                                                                       | 4                                                                                                     | 3                                                                        | 2                                                                                                      | 1                                                                                       | 0                                                                                |

| SYSCR1  | Bit symbol  |                                                            |                                                                   |                                                                                                         |                                                                                                       | SYSCK                                                                    | GEAR2                                                                                                  | GEAR1                                                                                   | GEAR0                                                                            |

| (00E1H) | Read/Write  | $\bigg  \bigg $                                            |                                                                   |                                                                                                         |                                                                                                       | 0.00.K                                                                   |                                                                                                        | W                                                                                       | 02/1110                                                                          |

|         | After reset |                                                            |                                                                   |                                                                                                         |                                                                                                       | 0                                                                        | 1                                                                                                      | 0                                                                                       | 0                                                                                |

|         | Function    |                                                            |                                                                   |                                                                                                         |                                                                                                       | Select<br>system clock<br>0: fc<br>1: fs                                 |                                                                                                        | ed)                                                                                     | quency (fc)                                                                      |

|         |             | 7                                                          | 6                                                                 | 5                                                                                                       | 4                                                                                                     | 3                                                                        | 2                                                                                                      | 1                                                                                       | 0                                                                                |

| SYSCR2  | Bit symbol  | PSENV                                                      |                                                                   | WUPTM1                                                                                                  | WUPTM0                                                                                                | HALTM1                                                                   | HALTM0                                                                                                 | SELDRV                                                                                  | DRVE                                                                             |

| (00E2H) | Read/Write  | R/W                                                        |                                                                   | R/W                                                                                                     | R/W                                                                                                   | R/W                                                                      | R/W                                                                                                    | R/W                                                                                     | R/W                                                                              |

|         | After reset | 0                                                          |                                                                   | 1                                                                                                       | 0                                                                                                     | 1                                                                        | 1                                                                                                      | 0                                                                                       | 0                                                                                |

|         | Function    | 1:Disable<br>0:Power<br>save<br>mode<br>enable<br>(Note 3) |                                                                   | Warm-up time<br>00: Reserved<br>01: 2 <sup>8</sup> inputted<br>10:2 <sup>14</sup><br>11:2 <sup>16</sup> |                                                                                                       | HALT mode<br>00: Reserved<br>01: STOP mo<br>10: IDLE1 mo<br>11: IDLE2 mo | de                                                                                                     | <drve><br/>mode<br/>select<br/>1: STOP<br/>0: IDLE1<br/>(Note 4)</drve>                 | Pin state control in STOP/IDLE1 mode 0: I/O off 1: Remains the state before halt |

Note 1: By reset, low-frequency oscillator is enabled.

Note 2: It's prohibit to use to fc/16 prescaler clock when SBI block use. (I<sup>2</sup>C bus and clock synchronous.)

Note 3: When use  $\overline{\text{NMI}}/\overline{\text{PS}}$  pin as  $\overline{\text{NMI}}$  function, set <PSENV> to 1.

Note 4: 0 means IDLE1, and 1 means STOP. Please be careful because this setting is sometimes different from others.

Figure 3.3.3 SFR for System Clock

| Symbol | Name                         | Address  | 7                                     |                          | 6                                           | 5                                             | 4                                                                        | 3   | 2              | 1   | 0   |

|--------|------------------------------|----------|---------------------------------------|--------------------------|---------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------|-----|----------------|-----|-----|

|        |                              |          | ACT1                                  |                          | ACT0                                        | DLUPFG                                        | DLUPTM                                                                   |     |                |     |     |

|        |                              |          | R/W                                   |                          | R/W                                         | R                                             | R/W                                                                      |     |                |     |     |

|        |                              |          | 0                                     |                          | 0                                           | 0                                             | 0                                                                        |     |                |     |     |

| DFMCR0 | DFM<br>control<br>register 0 | E8H      | 00 STOP<br>01 RUN<br>10 RUN<br>11 RUN | STC<br>RUN<br>STC<br>STC | P FOSCH OP FOSCH OP FOSCH OP FOSCH OP FOSCH | Lockup<br>status flag<br>0: End<br>1: Not end | Lockup<br>time<br>0: 2 <sup>12</sup> /fosch<br>1: 2 <sup>10</sup> /fosch |     |                |     |     |

|        |                              |          | D7                                    |                          | fosch<br>D6                                 | D5                                            | D4                                                                       | D3  | D2             | D1  | D0  |

|        | DFM                          | trol E9H | R/W                                   |                          | R/W                                         | R/W                                           | R/W                                                                      | R/W | R/W            | R/W | R/W |

| DFMCR1 | control                      |          | 0                                     |                          | 0                                           | 0                                             | 1                                                                        | 0   | 0              | 1   | 1   |

|        | register 1                   |          |                                       | •                        | Inpu                                        | ıt frequency                                  | DFM re<br>4 to 9 MHz (a                                                  |     | .6 V): Write ( | 0BH |     |

Figure 3.3.4 SFR for DFM

#### Li mi tati on poi nt on the use of DFM

- 1. It's prohi bited to execute DFMenable/disable contr (Write to DFMCR⊖∜AOT): Of soushould control DFM in the N

- 2. If you stop DFM operation during us-i"nlopDFM \( D \) DEMOROU4 \( D \) execute that chaom-gymeolops and obsolved the DFM at the same time the above executions should be separated into two provides the same of the same of the above executions.

LD (DFMCR0), C0H ; Change the clock  $f_{DFM}$  to  $f_{OSCH}$ .

LD (DFMCR0), 00H ; DFM stop.

3. If you stop high-tforredpureinrogy wossichigh DaM (DFMCRO): A GyTo1u should stop DFM before you stop high-frequency oscill

Pleaserefer to &u &l. & " (CD low) k" for the details

|         |             | 7            | 6                      | 5                       | 4                      | 3               | 2              | 1               | 0              |

|---------|-------------|--------------|------------------------|-------------------------|------------------------|-----------------|----------------|-----------------|----------------|

| EMCCR0  | Bit symbol  | PROTECT      | TA3LCDE                | AHOLD                   | TA3MLDE                | -               | EXTIN          | DRVOSCH         | DRVOSCL        |

| (00E3H) | Read/Write  | R            | R/W                    | R/W                     | R/W                    | R/W             | R/W            | R/W             | R/W            |

|         | After reset | 0            | 0                      | 0                       | 0                      | 0               | 0              | 1               | 1              |

|         | Function    | Protect flag | LCDC                   | Address                 | Melody/alarm           | Always fixed    | 1: External    | fc oscillator   | fs oscillator  |

|         |             | 0: OFF       | Source clock           | hold (Note)             | source clock           | to "0".         | clock          | driver ability  | driver ability |

|         |             | 1: ON        | 0: 32 kHz<br>1: TA3OUT | 0: Disable<br>1: Enable | 0: 32 kHz<br>1: TA3OUT |                 |                | 1: Normal       | 1: Normal      |

|         |             |              | 1: TA3001              | 1: Enable               | 1: TA3001              |                 |                | 0: Weak         | 0: Weak        |

| EM0004  | Bit symbol  |              |                        |                         |                        |                 |                |                 |                |

| EMCCR1  | Read/Write  |              |                        |                         |                        |                 |                |                 |                |

| (00E4H) | After reset |              | Switching              | the protect (           | ON/OFF by v            | vrite to follow | ing 1st-KEY,   | 2nd-KEY         |                |

|         | Function    |              | ŭ                      | •                       | = 5AH, EMC             |                 |                |                 |                |

| EMCCR2  | Bit symbol  |              | 2nd-KE                 | Y: EMCCR1               | I = A5H, EM            | CCR2 = 5AH      | in succession  | n write         |                |

| (00E5H) | Read/Write  |              |                        |                         |                        |                 |                |                 |                |

|         | After reset |              |                        |                         |                        |                 |                |                 |                |

|         | Function    |              |                        |                         | _                      | _               |                |                 |                |

| EMCCR3  | Bit symbol  |              | ENFROM                 | ENDROM                  | ENPROM                 |                 | FFLAG          | DFLAG           | PFLAG          |

| (00E6H) | Read/Write  |              | R/W                    | R/W                     | R/W                    |                 | R/W            | R/W             | R/W            |

| (,      | After reset |              | 0                      | 0                       | 0                      |                 | 0              | 0               | 0              |

|         | Function    |              | CS1A area              | CS2B 2G                 | CS2A area              |                 | CS1A write     | CS2B 2G         | CS2A write     |

|         |             |              | detect                 | area detect             | detect                 |                 | operation flag | write operation | operation flag |

|         |             |              | control                | control                 | control                |                 |                | flag            | 9              |

|         |             |              | 0: Disable             | 0: Disable              | 0: Disable             |                 | When readi     | ng              |                |

|         |             |              | 1: Enable              | 1: Enable               | 1: Enable              |                 | 0: Not writte  | en              |                |

|         |             |              |                        |                         |                        |                 | 1: Written     |                 |                |

|         |             |              |                        |                         |                        |                 | When writin    | ŭ               |                |

|         |             |              |                        |                         |                        |                 | 0: Clear flag  | 9               |                |

Note: When getting access to the logic address 000000H to 000FDFH, 001000H to 002FFFH and FFE000H to FFFFFFH, A0 to A23 holds the previous address of external access.

Figure 3.3.5 SFR for Noise Reducing

#### 3.3.3 System Clock Controller

The system clock cantesothless yestness of ook sting of the cantesothless yestness of the containts the control of the containts of the control of th

The combination of settkiXntostXDxXESNYSS-QX and < GEARO: 2> 100 will cause thessylvable to be called to the control of the co

For exangly is es, sfet to O. 5 MHz when the 16-MHz oscillato and X2 pins.

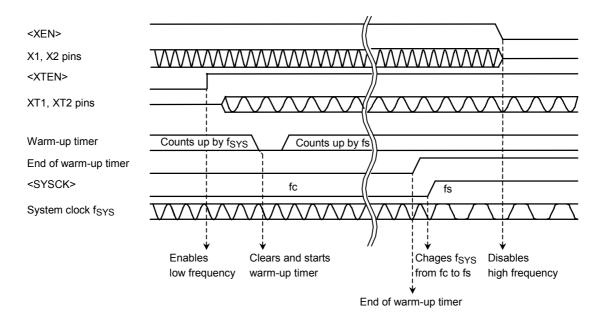

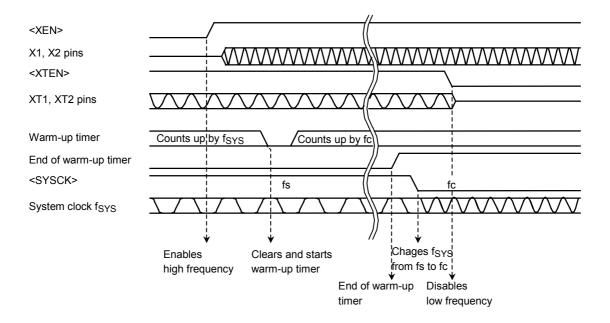

(1) Switchingfrom NORMAL mode to SLOW mode

When the resonator is connected to the X1 and X2 pir the warm-up timer can bet be experienced in a configuration as the compensation of the compensation and the compensation of the compensation and the compensation of the comp

The warm-up ti mected beisred &YSCR2<WUPTMO: 1>.

This warm-up timer can be programmed to start and sexamples 1 and 2.

Table 3. 3. 1 shows the warm-uptimes.

Note 1: When using an oscillator (Other than a resonator) with stable oscillation, a warm-up timer is not needed.

Note 2: The warm-up timer is operated by an oscillation clock. Hence, there may be some variation in warm-up time.

| Warm-up Time<br>SYSCR2<br><wuptm1:0></wuptm1:0> | Change to<br>NORMAL Mode | Change to<br>SLOW Mode |

|-------------------------------------------------|--------------------------|------------------------|

| 01 (28/frequency)                               | 16 [μs]                  | 7.8 [ms]               |

| 10 (2 <sup>14</sup> /frequency)                 | 1.024 [ms]               | 500 [ms]               |

| 11 (2 <sup>16</sup> /frequency)                 | 4.096 [ms]               | 2000 [ms]              |

Table 3.3.1 Warm-up Times

at  $f_{OSCH} = 16 \text{ MHz}$ ,  $f_{S} = 32.768 \text{ kHz}$

Example 1: Setting the clock Changing from high frequency (fc) to low frequency (fs). SYSCR0 00E0H SYSCR1 00E1H EQU SYSCR2 EQU 00E2H LD (SYSCR2), -X11---B; Sets warm-up time to  $2^{16}$ /fs. SET 6, (SYSCR0) Enables low-frequency oscillation. SET 2, (SYSCR0) Clears and starts warm-up timer. WUP: 2, (SYSCR0) BIT Detects stopping of warm-up timer. JR NZ, WUP SET 3, (SYSCR1) Changes f<sub>SYS</sub> from fc to fs. RES 7, (SYSCR0) Disables high-frequency oscillation.

X: Don't care, -: No change

Example 2: Setting the clock Changing from low frequency (fs) to high frequency (fc). SYSCR0 EQU 00E0H SYSCR1 00E1H EQU SYSCR2 EQU 00E2H LD (SYSCR2), -X10---B; Sets warm-up time to  $2^{14}$ /fc. SET 7, (SYSCR0) ; Enables high-frequency oscillation. 2, (SYSCR0) Clears and starts warm-up timer. SET WUP: 2, (SYSCR0) BIT Detects stopping of warm-up timer. JR NZ, WUP RES 3, (SYSCR1) Changes f<sub>SYS</sub> from fs to fc. **RES** 6, (SYSCR0) Disables low-frequency oscillation.

X: Don't care, -: No change

#### (2) Clock gear controller

When the high-frequency teodoby setsing 50% FR1<SYS is set according to the genitesets of the gics town SYSCR1 either fc, fc/2, fc/4,hec/8ck genitesets of the grand solselle part a lower educes power consumption.

Example 3: Changing to a high-frequency gear

SYSCR1 EQU 00E1H

LD (SYSCR1), XXXX0000B ; Changes  $f_{SYS}$  to fc/2. LD (SYSCR1), XXXX0100B ; Changes  $f_{SYS}$  to fc/32.

X: Don't care

(High-speed clock gear changing)

To change the clock gear, write the register value to to necessary the warm-upntgiam fet went wirlick hanggtihe register value. There is the possibility xtthatothe ich ock word to change in gexecuted by the clock gear before changing. To execute switching instruction by an to be record, oich kpount at the afortum most in the cycle).

(Example)

SYSCR1 EQU 00E1H

Instruction to be executed after clock gear has changed.

#### 3.3.4 Prescaler Clock Controller

For the internal I/O (TMRAtOol StloOTIMRS/AB23), t5hle@@isaprescandivide the clock.

The Tclock input to the prescape of visces of by 2 to bret to lecond kodi vided by 2. The setting of the SYSCRO < PRCKO: 1 > registion is input. When it's use of interpretable of the Syschology of the Syscholog

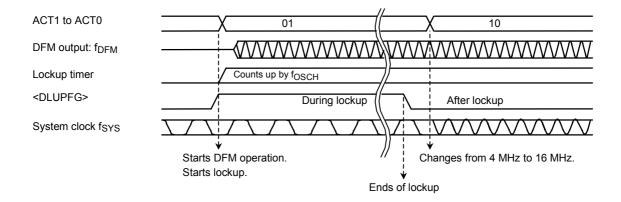

#### 3.3.5 Clock Doubler (DFM)

DFM output psychleotik signal, which is foscurittione is usefalse low-frequency oscillator, even though the internal of Areset initializes DFM to stop status, setting to DF Like an oscillator, thitsocsitraduiltize quli hriessitsioneelled to The following example shows how DFM is used.

| DFMCR0 | EQU | 00E8H               |     |                                                                                        |

|--------|-----|---------------------|-----|----------------------------------------------------------------------------------------|

| DFMCR1 | EQU | 00E9H               |     |                                                                                        |

|        | LD  | (DFMCR1), 0BH       | ;   | Parameter setting.                                                                     |

|        | LD  | (DFMCR0), 01X0XXXXB | ;   | Set lockup time to 2 <sup>12</sup> /4 MHz.<br>Enables DFM operation and starts lockup. |

| LUP:   | BIT | 5, (DFMCR0)         | ; ] | Detects end of lockup.                                                                 |

|        | JR  | NZ, LUP             | ; } | Detects end of lockup.                                                                 |

|        | LD  | (DFMCR0), 10X0XXXXB | ;   | Changes fc from 4 MHz to 16 MHz.                                                       |

#### X: Don't care

Note: Input frequency limitation and correction for DFM.

Recommend to use input frequency (High-speed oscillation) for DFM in the following condition.

f<sub>OSCH</sub> = 4 MHz to 9 MHz (Vcc = 2.7 V to 3.6 V): Write 0BH to DFMCR1.

#### Li mi tati on poi nt on the use of DFM

1. It's prohi bited to execute DFMenable/disable contr (Write to DFMCR⊖<AOT): Ø⊗u should control DFMin the N

2. If you stop DFM operation during using Open DF, My DDF MC Ook execute the commands that the time. Therefore the above execution should be separated below.

```

LD (DFMCR0), C0H ; Change the clock f_{DFM} to f_{OSCH}.

```

LD (DFMCR0), 00H ; DFM stop.

If you stop high-frequency oscillator duft Ohg, uş bag should stop DFM before you stop high-frequency oscill

Examples roofssærtet below.

(1) Start up/change control

(OK) Low-frequency oscillator operation mede (fs High-frequency os-€Hildy hatforresqueent cuyposcillosto) per → DFM star-\*tDFM use mood () (f

```

(SYSCR0),\, 11---1-B \qquad ; \qquad \text{High-frequency oscillator start-up/warm-up start}.

WUP:

BIT

2, (SYSCR0)

Check for the flag of lockup end.

JR

NZ, WUP

(SYSCR1), ----0---B ; Change the system clock fs to fosch.

ΙD

(DFMCR0), 01-0---B; DFM start-up/lockup start.

ΙD

LUP:

BIT

5, (DFMCR0)

Check for the flag of lockup end.

JR

NZ, LUP

ΙD

(DFMCR0), 10-0---B; Change the system clock.

```

(OK) Low-frequency oscillator operation mode opera+Hei)gh-frequency oscillosto)## DPMsatati-\*\*DFMode (fuse mode) (f

(Error) Low-frequency oscillator operation mode

→ High-frequency os-eDFMastar—stDtFpMtusepmoode) (f

```

ΙD

(SYSCR0), 11---1--B; High-frequency oscillator start-up/warm-up start.

WUP:

BIT

2, (SYSCR0)

Check for the flag of lockup end.

JR

NZ, WUP

LD

; DFM start-up/lockup start.

(DFMCR0), 01-0---B

LUP:

BIT

5, (DFMCR0)

Check for the flag of lockup end.

JR

NZ, LUP

LD

(DFMCR0), 10-0---B; Change the internal clock f<sub>OSCH</sub> to f<sub>DFM</sub>.

(SYSCR1), ---0--B ; Change the system clock f_S to f_{DFM}.

LD

```

```

(2) Change/stopcontrol

(OK) DFM use om row death (figh-frequency oscillosto) and operation

DFMst-olpow-frequency oscillat-olhiopherfateiopune modyeo & c

stop

(DFMCR0), 11----B \, ; Change the system clock fDFM to fOSCH.

LD

(DFMCR0), 00-----B ; DFM stop.

ΙD

LD

(SYSCR1), ----1---B ; Change the system clock f<sub>OSCH</sub> to fs.

LD

(SYSCR0), 0----B; High-frequency oscillator stop.

(Error) DFM uppen/modew(-ffrequency oscillator oper

DFMst-⊕pdigh-frequency oscillator stop

(SYSCR1), ----1---B \;\; ; \;\; Change the system clock f_{\mbox{\scriptsize DFM}} to fs.

LD

LD

(DFMCR0), 11----B ; Change the internal clock (fc) f_{DFM} to f_{OSCH}.

LD

(DFMCR0), 00-----B ; DFM stop.

(SYSCR0), 0----B; High-frequency oscillator stop.

LD

(OK) DFM use myn)d+eS(eft the STOP) Hologh-frequency osc

operations model to the state of the state o

(SYSCR2), ----01--B ; Set the STOP mode.

(This command can execute before use of DFM.)

ΙD

(DFMCR0), 11----B ; Change the system clock f<sub>DFM</sub> to f<sub>OSCH</sub>.

LD

(DFMCR0), 00----B; DFM stop.

HALT

: Shift to STOP mode.

(Error) DFM uspen/man Stet (the STOP) it indicated (High-frequence)

oscillator stop)

(SYSCR2), ----01--B; Set the STOP mode.

(This command can execute before use of DFM.)

```

; Shift to STOP mode.

HALT

#### 3.3.6 Noise Reduction Circuits

Noi se reducti on circui ts are builtin, allowing i mpl

- (1) Reduced drigyha-bfirleiotyyefnooryhoiscillator

- (2) Reduced drill over-bifit eighy efroory oscillator

- (3) Singledrive for high-frequency oscillator

- (4) Runaway provision with SFR protection register

- (5) Runaway provision with ROM protection register

The above functions are performed by making the apprto EMCCR3 registers.

## (1) Reduced drhiv@nhoifitetoyufeorcy oscillator

(Purpose)

Reduces noi se and power for oscillator when a reso

(Block diagram)

(Settingmethod)

The drivability of the oscillator is reduced by w register. By reset, <DRVOSCH> is initialized to 1 a by normal drivability when the power supply is on.

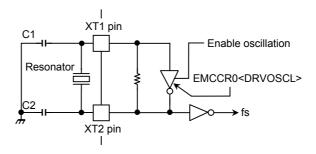

(2) Reduced drli ov war bif it ė ot pyrefroory oscillator (Purpose)

Reduces noi se and power for oscillator when a reso

(Block diagram)

(Settingmethod)

The drivability of the oscillator is reduced by wriregister. By reset, < DRVOSCL > is initialized to 1.

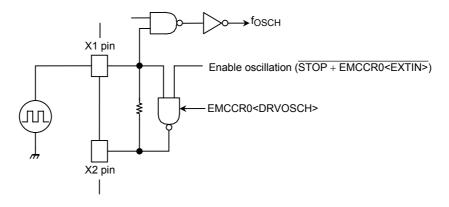

(3) Singledrive for high-frequency oscillator (Purpose)

Not need twi n-dri ve and protect mi stake operation the external oscillator is used.

(Block diagram)

(Settingmethod)

The oscillator is discaphelreadtiaonnal asstabrutfsfer by wri EMCCRO<EXTIN>regniisstearwaXy2spoiutputted 1.

By reset, <EXTIN>isinitialized to O.

(4) Runaway provi si on wi th SFR protecti on regi ster (Pur pose)

Provision in runaway of program by noise mixing.

Write operation to specified SFR is prohibited so prevents that it is it if net to the strap to swihlb iclhiitsy by sto memory control region terro (ICSe/rWAMMU) is changed.

And error handling imes easy bet to Ointerruption.

#### Specified SFRIist

- CS/WAIT controller BOCS, B1CS, B2CS, B3CS, BEXCS, MSARO, MSAR1, MSAR2, MSAR3, MAMRO, MAMR1, MAMR2, MAMR3

- 2. MMU LOCALO/1/2/3

- 3. Clock gear SYSCRO, SYSCR1, SYSCR2, EMCCRO, EMCCR3

- 4. DFM

DFMCRO/1

(Operation explanation)

Execute and release of protection (Write operation by setting up a double key to EMCCR1 and EMCCR2 regist (Double key)

1st-KEY: Succession writes in 5AHat EMCCR1 a 2nd-KEY: Succession writes in A5Hat EMCCR1 a

A state of protection can be confirmed by reading E By reset, protection becomes OFF.

And INTPOinterruption occurs when write operation with protection on state.

(5) Runaway provision with ROM protection register (Purpose)

Provision in runaway of program by noise mixing.

(Operation explanation)

When writes operation was executed for external the program, INTP1 is occurred and detects runaway fund.

Three kinds of ROMishf R $\otimes$  kand (aptficornfphrackgram ROM), deprogram ROM are as follows on the logical address me

- 1. Flash ROWs sA41000000H to 7FFFFFH

- 2. Data ROME: s As dB: dD TO O O O O H to B F F F F F H

- 3. Program ROM: Address COOOOOH to FFFFFFH

For these address, admission/prohibition of determined the two services of the transfer of the services of the

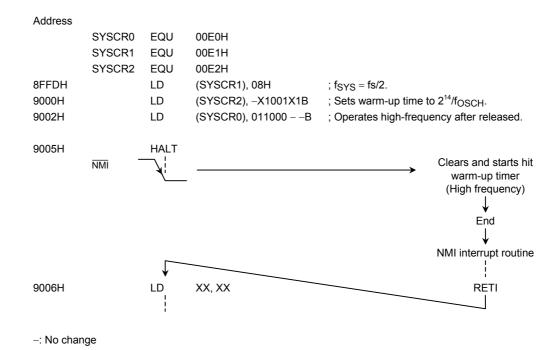

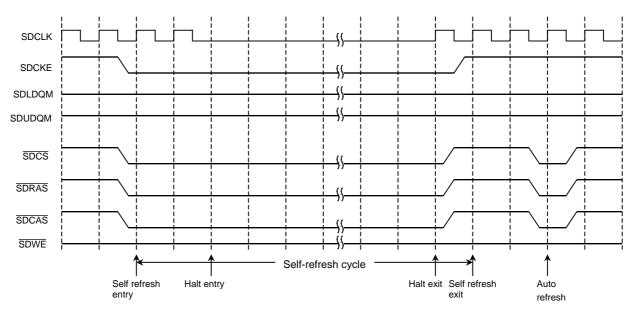

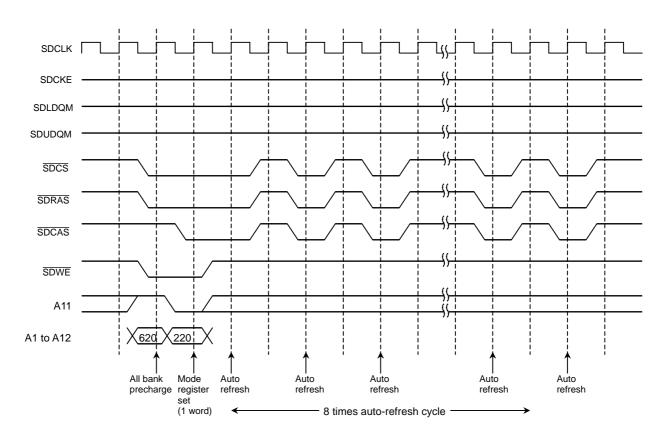

### 3.3.7 Standby Controller

#### (1) HALT modes

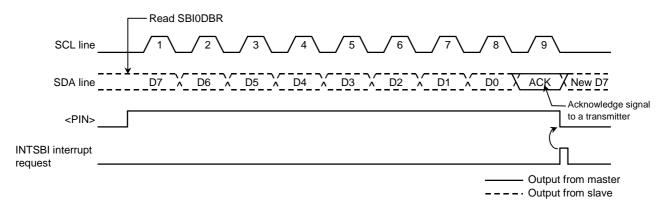

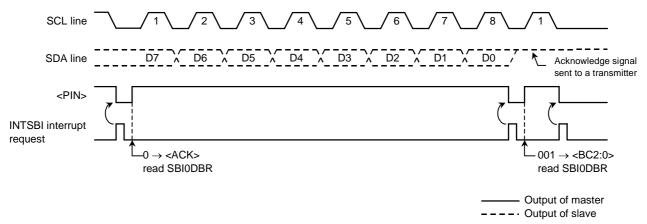

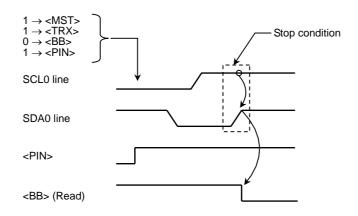

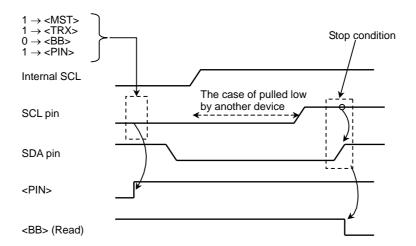

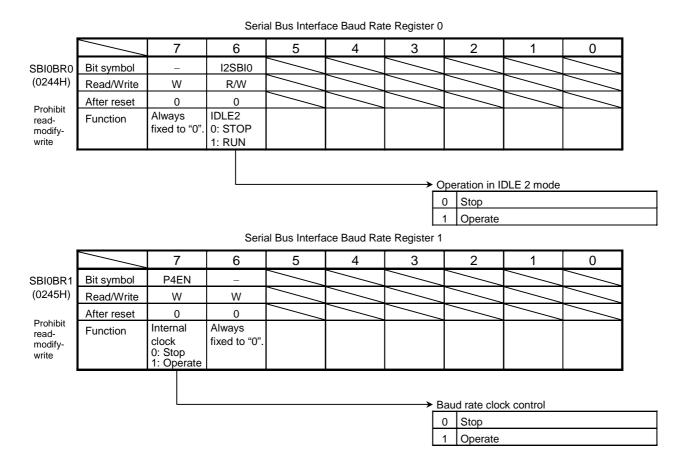

SBI

When the HALT instruction is executed, the operal DLE1 or STOP mode, depending on the contents of register.

The subsequent actions performed in each mode are

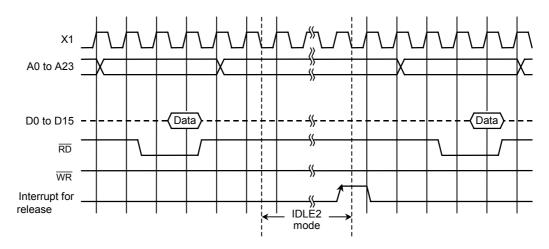

a. IDLE 2: Only the CPU halts.

The internal I/Ois available to select oper setting the following register.

Table 3. 3. 2 shows the registers of setting o

| <u> </u>     | <u> </u>                  |

|--------------|---------------------------|

| Internal I/O | SFR                       |

| TMRA01       | TA01RUN <i2ta01></i2ta01> |

| TMRA23       | TA23RUN <i2ta23></i2ta23> |

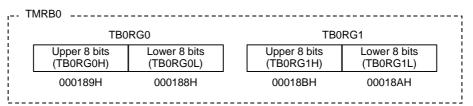

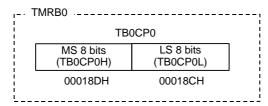

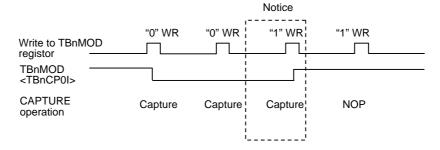

| TMRB0        | TB0RUN <i2tb0></i2tb0>    |