### SATELLITE SOUND AND VIDEO PROCESSOR

#### SOUND

- TWO INDEPENDENT SOUND DEMODULATORS

- PLL DEMODULATION WITH 5-10MHz FREQUENCY SYNTHESIS

- PROGRAMMABLE FM DEMODULATOR

BANDWIDTH ACCOMODATING FM

DEVIATIONS FROM ±30kHz TILL ±400kHz

- PROGRAMMABLE 50/75µs, J17 OR NO DEEMPHASIS

- WEGENER PANDA SYSTEM

- TWO AUXILIARY AUDIO INPUTS AND OUTPUTS

- GAIN CONTROLLED AND MUTEABLE AUDIO OUTPUTS

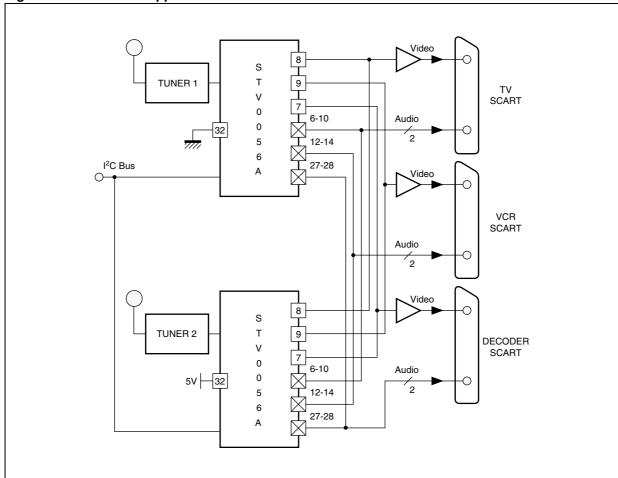

- HIGH IMPEDANCE MODE AUDIO OUTPUTS FOR TWIN TUNER APPLICATIONS

### **VIDEO**

- COMPOSITE VIDEO 6-bit 0 to 12.7dB GAIN CONTROL

- COMPOSITE VIDEO SELECTABLE INVERTER

- TWO SELECTABLE VIDEO DE-EMPHASIS NETWORKS

- 6 x 3 VIDEOMATRIX

- BLACK LEVEL ADJUSTABLE OUTPUT FOR ON-BOARD VIDEOCRYPT DECODER

- HIGH IMPEDANCE MODE VIDEO OUTPUTS FOR TWIN TUNER APPLICATIONS

### **MISCELLANEOUS**

- 22kHz TONE GENERATION FOR LNB CONTROL

- I<sup>2</sup>C BUS CONTROL

- CHIP ADDRESSES = 06<sub>HEX</sub> OR 46<sub>HEX</sub>

- LOW POWER STAND-BY MODE WITH ACTIVE

- AUDIO AND VIDEO MATRIXES

Figure 1. Package

Figure 2. Pin Connections

REV. 2

June 2004 1/34

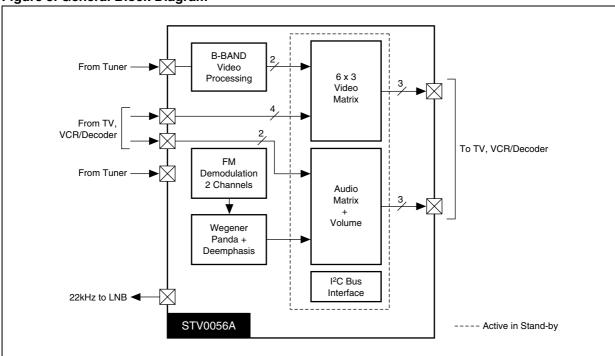

### **DESCRIPTION**

The STV0056A BICMOS integrated circuit realizes all the necessary signal processing from the

tuner to the Audio/Video input and output connectors regardless of the satellite system.

**Table 1. PIN ASSIGNMENT**

| Pin Number | Name          | Function                                    |

|------------|---------------|---------------------------------------------|

| 1          | FC R          | Audio Roll-off Right                        |

| 2          | PK IN R       | Noise Reduction Peak Detector Input Right   |

| 3          | LEVEL R       | Noise Reduction Level Right                 |

| 4          | S1 VID RTN    | TV-Scart 1 Video Return                     |

| 5          | S3 VID RTN    | Decoder-Scart Video Return                  |

| 6          | VOL R         | Volume Controlled Audio Out Right           |

| 7          | S3 VID OUT    | Decoder-Scart Video Output                  |

| 8          | S1 VID OUT    | TV-Scart 1 Video Output                     |

| 9          | S2 VID OUT    | VCR-Scart 2 Video Output                    |

| 10         | VOL L         | Volume Controlled Audio Out Left            |

| 11         | S2 VID RTN    | VCR-Scart 2 Video Return                    |

| 12         | S2 OUT L      | Fixed Level Audio Output Left (to VCR)      |

| 13         | CLAMP IN      | Sync-Tip Clamp Input                        |

| 14         | S2 OUT R      | Fixed Level Audio Output Right (to VCR)     |

| 15         | UNCL DEEM     | Unclamped De-emphasized Video Output        |

| 16         | VIDEEM2/22kHz | Video De-emphasis 2 or 22kHz Output         |

| 17         | V 12V         | Video 12V Supply                            |

| 18         | VIDEEM1       | Video De-emphasis 1                         |

| 19         | V GND         | Video Ground                                |

| 20         | B-BAND IN     | Base Band Input                             |

| 21         | S2 RTN L      | Auxiliary Audio Return Left (from VCR)      |

| 22         | S2 RTN R      | Auxiliary Audio Return Right (from VCR)     |

| 23         | FM IN         | FM Demodulator Input                        |

| 24         | S3 RTN L      | Auxiliary Audio Return Left (from decoder)  |

| 25         | S3 RTN R      | Auxiliary Audio Return Right (from decoder) |

| 26         | AGC L         | AGC Peak Detector Capacitor Left            |

| 27         | S3 OUT L      | Auxiliary Audio Output L (to decoder)       |

| 28         | S3 OUT R      | Auxiliary Audio Output R (to decoder)       |

| 29         | I/O/22kHz     | Digital Input/Output or 22kHz Output        |

| 30         | SCL           | I <sup>2</sup> C Bus Clock                  |

|            |               |                                             |

| 31         | SDA           | I <sup>2</sup> C Bus Data                   |

| Pin Number | Name             | Function                                   |

|------------|------------------|--------------------------------------------|

| 33         | J17 R            | J17 De-emphasis Time Constant Right        |

| 34         | J17 L            | J17 De-emphasis Time Constant Left         |

| 35         | XTL              | 4/8MHz Quartz Crystal or Clock Input       |

| 36         | VDD 5V           | Digital 5V Power Supply                    |

| 37         | GND 5V           | Digital Power Ground                       |

| 38         | CPUMP L          | FM PLL Charge Pump Capacitor Left          |

| 39         | DET L            | FM PLL Filter Left                         |

| 40         | U75 L            | De-emphasis Time Constant Left             |

| 41         | AMPLK L          | Amplitude Detector Capacitor Left          |

| 42         | AGC R            | AGC Peak Detector Capacitor Right          |

| 43         | A GND L          | Audio Ground                               |

| 44         | $V_{REF}$        | 2.4V Reference                             |

| 45         | A 12V            | Audio 12V Supply                           |

| 46         | AMPLK R          | Amplitude Detector Capacitor Left          |

| 47         | DET R            | FM PLL Filter Right                        |

| 48         | U75 R            | De-emphasis Time Constant Right            |

| 49         | CPUMP R          | FM PLL Charge Pump Capacitor Right         |

| 50         | I <sub>REF</sub> | Current Reference Resistor                 |

| 51         | PK OUT R         | Noise Reduction Peak Detector Output Right |

| 52         | PK OUT L         | Noise Reduction Peak Detector Output Left  |

| 53         | LEVEL L          | Noise Reduction Level Left                 |

| 54         | PK IN L          | Noise Reduction Peak Detector Input        |

| 55         | FC L             | Audio Roll-off Left                        |

| 56         | A GND R          | Audio Ground                               |

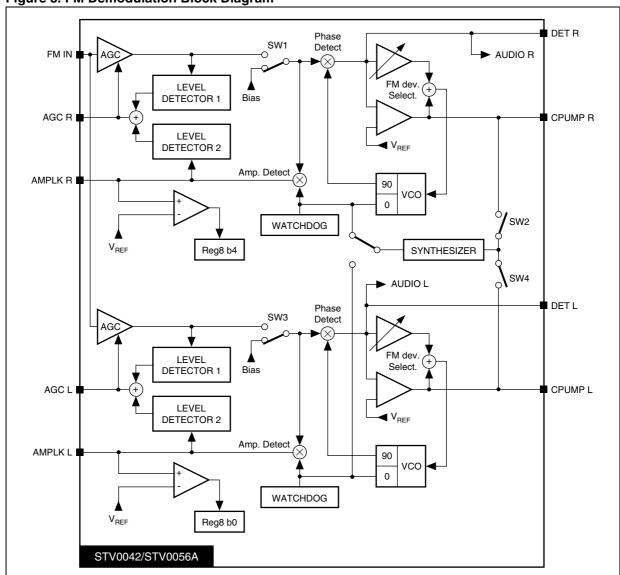

### **SOUND DETECTION**

#### **FMIN**

This is the input to the two FM demodulators. It feeds two AGC amplifiers with a band width of at least 5-10MHz. There is one amplifier for each channel both with the same input. The AGC amplifiers have a 0dB to +40dB range.

$Z_{IN} = 5k\Omega$ , Min input =  $2mV_{PP}$  per sub carrier.

Max input =  $500 \text{mV}_{PP}$  (max when all inputs are added together, when their phases coincide).

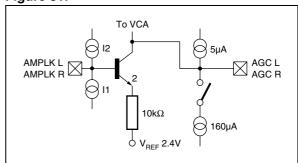

### AGC L, AGC R

AGC amplifiers peak detector capacitor connections.

The output current has an attack/decay ratio of 1:32. That is the ramp up current is approximately

5μA and decay current is approximately 160μA. 11V gives maximum gain. These pins are also driven by a circuit monitoring the voltage on AM-PLK L and AMPLK R respectively.

### AMPLK L, AMPLK R

The outputs of amplitude detectors LEFT and RIGHT. Each requires a capacitor and a resistor to GND. The voltage across this is used to decide whether there is a signal being received by the FM detector. The level detector output drives a bit in the detector I<sup>2</sup>C bus control block.

AMPLK L and AMPLK R drive also respectively AGC L and AGC R. For instance when the voltage

on AMPLKL is >  $(V_{REF} + 1 \ V_{BE})$  it sinks current to  $V_{REF}$  from pin AGCL to reduce the AGC gain.

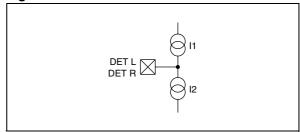

#### DET L, DET R

Respectively the outputs of the FM phase detector left and right.

This is for the connection of an external loop filter for the PLL. The output is a push-pull current source.

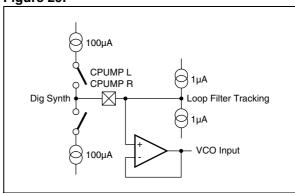

#### CPUMP L, CPUMPR

The output from the frequency synthesizer is a push-pull current source which requires a capacitor to ground to derive a voltage to pull the VCO to the target frequency. The output is  $\pm 100\mu A$  to achieve lock and  $\pm 2\mu A$  during lock to provide a tracking time constant of approximately 10Hz.

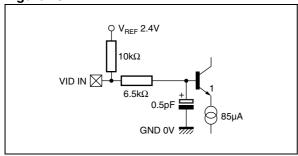

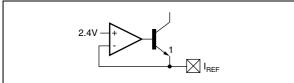

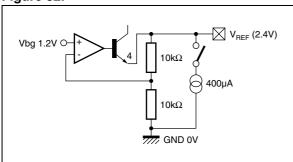

### **V<sub>REF</sub>**

This is the audio processor voltage reference used through out the FM/audio section of the chip. As such it is essential that it is well decoupled to ground to reduce as far as possible the risk of crosstalk and noise injection. This voltage is derived directly from the band gap reference of 2.4V.

The V<sub>REF</sub> output can sink up to 500μA in normal operation and 100μA when in stand-by.

### IREF

This is a buffered  $V_{REF}$  output to an off-chip resistor to produce an accurate current reference, with in the chip, for the biasing of amplifiers with current outputs into filters. It is also required for the Noise reduction circuit to provide accurate roll-off frequencies.

This pin should not be decoupled as it would inject current noise. The target current is  $50\mu A \pm 2\%$  thus a  $47.5k\Omega \pm 1\%$  is required.

#### **A 12V**

Double bonded main power pin for the audio/FM section of the chip. The two bond connections are to the ESD and to power the circuit and on chip regulators/references.

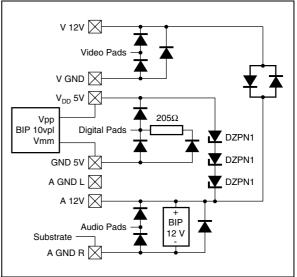

#### A GND L

This ground pin is double bonded:

- 1. to channel LEFT: RF section & VCO,

- to both AGC amplifiers, channel LEFT and RIGHT audio filter section.

#### A GND R

This ground pin is double bonded:

- 1. to the volume control, noise reduction system, ESD + Mux + V<sub>REF</sub>

- 2. to channel right: RF section & VCO BASEBAND AUDIO PROCESSING

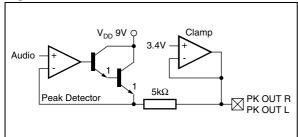

### PK OUT L, PK OUT R, PK OUT

The noise reduction control loop peak detector output requires a capacitor to ground from this pin,

and a resistor to  $V_{REF}$  pin to give some accurate decay time constant. An on chip  $5k\Omega$  ±25% resistor and external capacitor give the attack time.

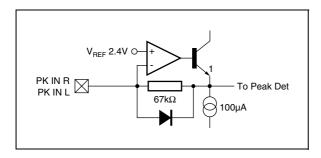

### PK IN L, PK IN R or PK IN

Each of these pins is an input to a control loop peak detector and is connected to the output of the off chip control loop band pass filter.

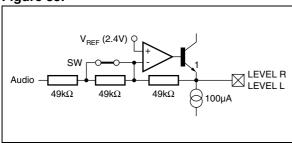

#### LEVEL L, LEVELR

Respectively the audio left and right signals of the FM demodulators are output to level L and level R pins through an input follower buffer. The off-chip filters driven by these pins must include AC coupling to the next stage (PK IN L and PK IN R pins respectively).

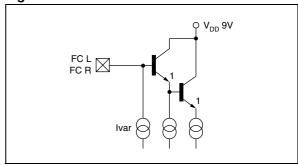

### FC L, FC R

The variable bandwidth transconductance amplifier has a current output which is variable depending on the input signal amplitude as defined by the control loop of the noise reduction. The output current is then dumped into an off-chip capacitor which together with the accurate current reference define the min/max roll off frequencies. A resistor in series with a capacitor is connected to ground from these two pins.

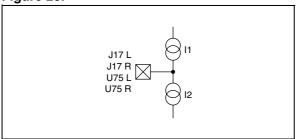

### J17 L, J17R

The external J17 de-emphasis networks for channels left and right. The amplifier for this filter is voltage input, current output. Output with  $\pm 500 \text{mV}$  input will be  $\pm 55 \mu A$ .

To perform J17 de-emphasis with the STV0042, an external circuit is required.

### U75 L, U75 R

External de-emphasis networks for channels left and right. For each channel a capacitor and resistor in parallel of 75 $\mu$ s time constant are connected between here and  $V_{REF}$  to provide 75 $\mu$ s de-emphasis.

Internally selectable is an internal resistor that can be programmed to be added in parallel thereby converting the network to approx 50µs de-emphasis (see control block map). The value of the internal resistors is  $54k\Omega$   $\pm30\%$ . The amplifier for this filter is voltage input, current output; with  $\pm500\text{mV}$  input the output will be  $\pm55\mu\text{A}$ .

### **VOL L, VOL R**

The main audio output from the volume control amplifier the signal to get output signals as high as  $2V_{RMS}$  (+12dB) on a DC bias of 4.8V. Control is from +12dB to -26.75dB plus Mute with 1.25dB steps.This amplifier has short circuit protection and is intended to drive a SCART connector directly via AC coupling and meets the standard SCART drive requirements. These outputs feature high impedance mode for parallel connection.

### S2 OUT L, S2 OUTR, S3 OUT L, S3 OUT R

These audio outputs are sourced directly from the audio MUX, and as a result do not include any volume control function. They will output a  $1V_{RMS}$  signal biased at 4.8V. They are short circuit protected.

These outputs feature high impedance mode for parallel connection and meet SCART drive requirement

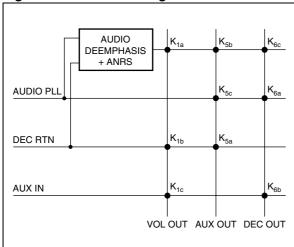

### S2 RTN L, S2 RTN R, S3 RTN L, S3 RTN R

These pins allow auxiliary audio signals to be connected to the audio processor and hence makes use of the on-chip volume control. For additional details please refer to the audio switching table.

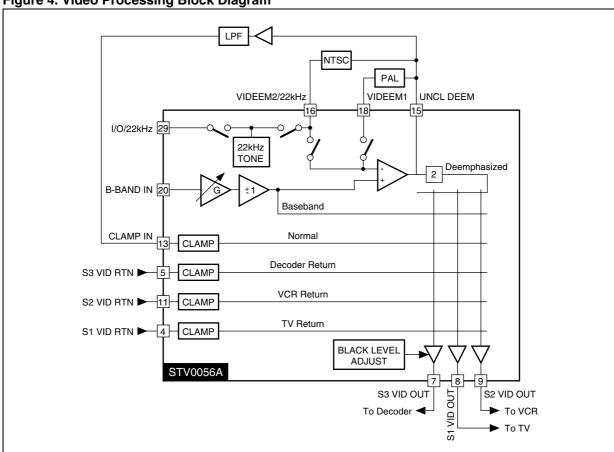

#### **VIDEO PROCESSING**

### **B-BAND IN**

AC-coupled video input from a tuner.

$Z_{IN}$  > 10k $\Omega$  ±25%. This drives an on-chip video amplifier. The other input of this amp is AC grounded by being connected to an internal V<sub>REF</sub>. The video amplifier has selectable gain from 0dB to 12.7dB in 63 steps and its output signal can be selected normal or inverted.

#### **UNCL DEEM**

De-emphasized still unclamped output. It is also an input of the video matrix.

#### VIDEEM1

Connected to an external de-emphasis network (for instance 625 lines PAL de-emphasis).

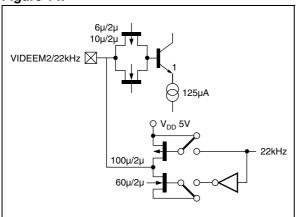

### VIDEEM2 / 22kHz

Connected to an external de-emphasis network (for instance 525 lines NTSC or other video de-emphasis).

Alternatively a precise 22kHz tone may be output by  $I^2C$  bus control.

### **CLAMP IN**

This pin clamps the most negative extreme of the input (the sync tips) to 2.7V<sub>DC</sub> (or appropriate voltage).

The video at the clamp input is only 1VPP.

This clamped video which is de-emphasized, filtered and clamped (energy dispersal removed) is normal, negative syncs, video. This signal drives the Video Matrix input called Normal Video.

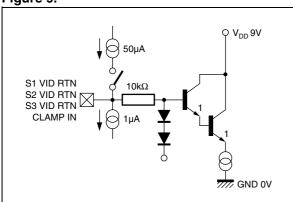

It has a weak (1.0 $\mu$ A ±15%) stable current source pulling the input towards GND. Otherwise the input impedance is very high at DC to 1kHz  $Z_{IN}$  > 2M $\Omega$ .

Video bandwidth through this is -1dB at 5.5MHz.

The CLAMP input DC restore voltage is then used as a means for getting the correct DC voltage on the SCART outputs.

#### S3 VIDRTN

This input can be driven for instance by the decoder. This input has a DC restoration clamp on its input. The clamp sink current is 1 $\mu$ A ±15% with the buffer  $Z_{IN} > 1$ M $\Omega$ .

#### S2 VID RTN. S1 VID RTN

External video input 1.0V<sub>PP</sub> AC coupled 75 $\Omega$  source impedance. This input has a DC restoration clamp on its input. The clamp sink current is 1 $\mu$ A ±15% with the buffer  $Z_{IN} > 1M\Omega$ . This signal is an input to the Video Matrix.

### S1 VID OUT, S2 VID OUT

Video drivers for SCART 1 and SCART 2. An external emitter follower buffer is required to drive a  $150\Omega$  load. The average DC voltage to be 1.5V on the O/P. The signal is video  $2.0V_{PP}$  5.5MHz BW with sync tip = 1.2V. These pins get signals from the Video Matrix. The signal selected from the Video Matrix for output on this pin is controlled by a control register. This output also feature a high impedance mode for parallel connection.

#### S3 VID OUT

This output can drive for instance a decoder. Also it is able to pass 10MHz;  $Z_{OUT} < 75\Omega$ . Video on this pin will be  $2V_{PP}$ . The black level of the output video signal can be adjusted through I<sup>2</sup>C bus control to easily interface with on-board Videocrypt decoder. This output feature an high impedance mode for parallel connection.

#### V 12V

+12V double bonded: ESD+guard rings and video circuit power.

### V GND

Doubled bonded.Clean VID IN GND. Strategically placed video power ground connection to reduce video currents getting into the rest of the circuit.

### **CONTROL BLOCK**

### **GND 5V**

The main power ground connection for the control logic, registers, the I<sup>2</sup>C bus interface, synthesizer & watchdog and XTLOSC.

#### $V_{DD}$ 5V

Digital +5V power supply.

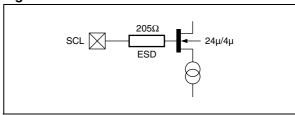

#### SCL

This is the I<sup>2</sup>C bus clock line. Clock = DC to 100kHz. Requires external pull up eg.  $10k\Omega$  to 5V.

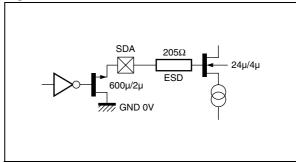

#### SDA

This is the  $I^2C$  bus data line. Requires external pull up eg.  $10k\Omega$  to 5V.

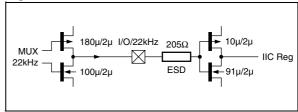

#### I/O / 22kHz

General purpose input output pin or 22kHz output.

477

### XTL

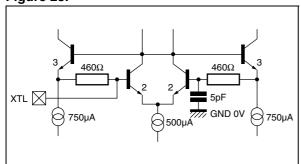

This pin allows for the on-chip oscillator to be either used with a crystal to ground of 4MHz or 8MHz, or to be driven by an external clock source. The external source can be either 4MHz or 8MHz.

A programmable bit in the control block removes a  $\div$  2 block when the 4MHz option is selected.

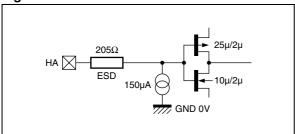

#### HA

Hardware address with internal 135 $\mu$ A pull down. Chip address is 06 when this pin is grounded and chip address is 46 when connected to  $V_{DD}$ .

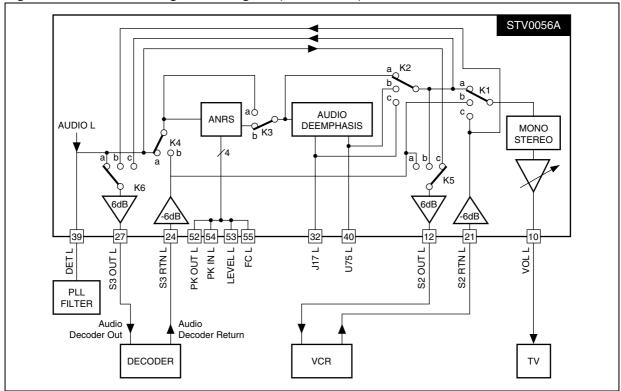

Figure 3. General Block Diagram

Figure 4. Video Processing Block Diagram

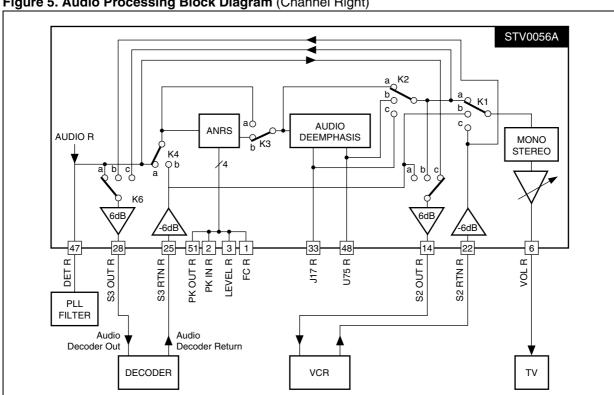

Figure 5. Audio Processing Block Diagram (Channel Right)

Figure 6. Audio Processing Block Diagram (Channel Left)

47/ 8/34

Figure 7. Audio Switching

$\begin{array}{ll} \text{K4:} & \text{a} \rightarrow \text{ANRS input non-scrambled audio} \\ & \text{b} \rightarrow \text{ANRS input descrambled audio} \end{array}$

**Table 2. ANRS Selection**

| K <sub>2</sub> | K <sub>3</sub> |                                                  |

|----------------|----------------|--------------------------------------------------|

| a<br>b1        | а              | No ANRS, No De-emphasis<br>No ANRS, 50ms         |

| b1<br>b2       | a<br>a         | No ANRS, 75ms                                    |

| C              | a              | No ANRS, J17                                     |

| a<br>b1<br>b2  | b<br>b<br>b    | ANRS, No De-emphasis<br>ANRS, 50ms<br>ANRS, 75ms |

| С              | b              | ANRS, J17                                        |

Figure 8. FM Demodulation Block Diagram

### **CIRCUIT DESCRIPTION**

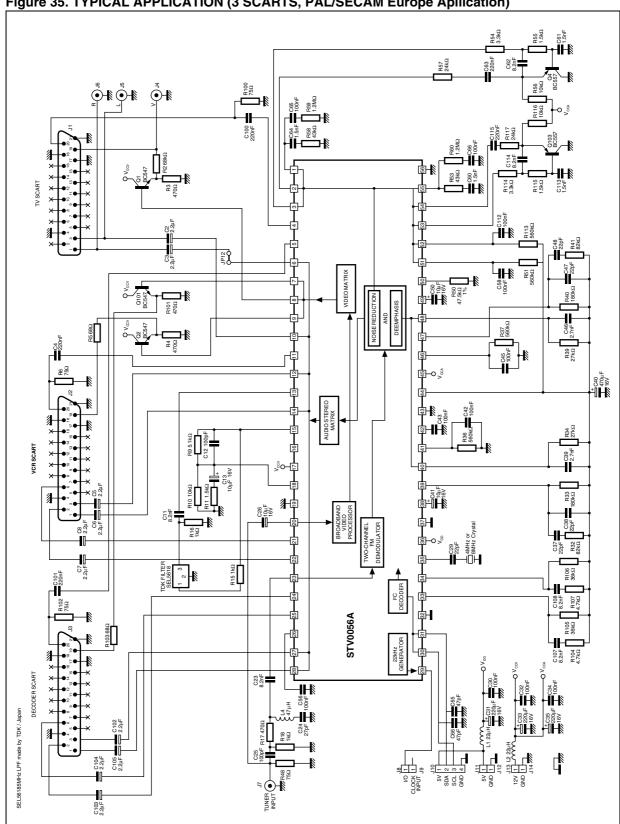

#### Video Section

The composite video is first set to a standard level by means of a 64 step gain controlled amplifier. In the case that the modulation is negative, an inverter can be switched in.

One of two different external video de-emphasis networks (for instance PAL and NTSC) is selectable by an integrated bus controlled switch.

Then energy dispersal is removed by a sync tip clamping circuit, which is used on all inputs to a video switching matrix, thus making sure that no DC steps occur when switching video sources.

The matrix can be used to feed video to and from decoders, VCR's and TV's.

A bus controlled black level adjustment circuit is provided on the decoder output allowing a direct connection to an on-board Videocrypt decoder.

Additionally all the video outputs are tristate type (high impedance mode is supported), allowing a simple parallel connections to the scarts (Twin tuner applications).

#### **Audio Section**

The two audio channels are totally independent except for the possibility given to output on both

channels only one of the selected input audio channels.

To allow a very cost effective application, each channel uses PLL demodulation. Neither external complex filter nor ceramic filters are needed.

The frequency of the demodulated subcarrier is chosen by a frequency synthesizer which sets the frequency of the internal local oscillator by comparing its phase with the internally generated reference. When the frequency is reached, the microprocessor switches in the PLL and the demodulation starts.

At any moment the microprocessor can read from the device (watchdog registers) the actual frequency to which the PLL is locked. It can also verify that a carrier is present at the wanted frequency (by reading AMPLK status bit) thanks to a synchronous amplitude detector, which is also used for the audio input AGC.

In order to maintain constant amplitude of the recovered audio regardless of variations between satellites or subcarriers, the PLL loop gain may be programmed from 56 values.

Any frequency deviation can be accommodated (from ±30kHz till ±400kHz).

Two different networks can be permanently connected for either 75ms or J17 de-emphasis. If 50ms de-emphasis is required, this can be insert-

ed by an internal switch, thus allowing a worldwide application.

The STV0056A is intended to be compatible with Wegener Panda System.

Two types of audio outputs are provided: one is a fixed  $1V_{RMS}$  and the other is a gain controlled  $2V_{RMS}$  max. The control range being from +12dB to -26.75dB with 1.25dB steps.This output can also be muted.

A matrix is implemented to feed audio to and from decoders VCR's and TV's.

Noise reduction system and de-emphasis can be inserted or by-passed through bus control.

Also all the audio outputs are tristate-type (high impedance mode is supported), allowing a simple parallel connections to the scarts (Twin tuner applications).

### **Others**

A 22kHz tone is generated for LNB control.

It is selectable by bus control and available on one of the two pins connected to the external video deemphasis networks. One general purpose I/O is also available on the STV0056A.

By means of the I<sup>2</sup>C bus there is the possibility to drive the ICs into a low power consumption mode with active audio and video matrixes. Independently from the main power mode, each individual audio and video output can be driven to high impedance mode.

**Table 3. Absolute Maximum Ratings**

| Symbol                             | Parameter                     | Value             | Unit   |

|------------------------------------|-------------------------------|-------------------|--------|

| V <sub>CC</sub><br>V <sub>DD</sub> | Supply Voltage                | 15<br>7.0         | V<br>V |

| P <sub>tot</sub>                   | Total Power Dissipation       | 900               | mW     |

| T <sub>oper</sub>                  | Operating Ambient Temperature | 0, +70            | °C     |

| T <sub>stg</sub>                   | Storage Temperature           | <b>−</b> 55, +150 | °C     |

Table 4. Thermal Data

| Symbol               | Parameter                           |     | Value | Unit |

|----------------------|-------------------------------------|-----|-------|------|

| R <sub>th(j-a)</sub> | Thermal Resistance Junction-ambient | Max | 55    | °C/W |

477

**Table 5. DC and AC Electrical Characteristics**

| Symbol                               | Parameter                        | Test Conditions                                            | Min.         | Тур.      | Max.         | Unit     |

|--------------------------------------|----------------------------------|------------------------------------------------------------|--------------|-----------|--------------|----------|

| V <sub>CC</sub><br>V <sub>DD</sub>   | Supply Voltage                   |                                                            | 11.4<br>4.75 | 12<br>5.0 | 12.6<br>5.25 | V<br>V   |

| IQ <sub>CC</sub><br>IQ <sub>DD</sub> | Supply Current                   | All audio and all video outputs activated                  |              | 55<br>8   | 70<br>15     | mA<br>mA |

| IQLP <sub>CC</sub>                   | Supply Current at Low Power Mode | All audio and all video outputs are in high impedance mode |              | 27<br>6   | 35<br>9      | mA<br>mA |

### **Table 6. Audio Demodulator**

| Symbol | Parameter                                                                         | Test Conditions                                                                               | Min. | Тур. | Max. | Unit             |

|--------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------|------|------|------------------|

| FMIN   | FM Subcarrier Input Level<br>(Pin FMIN for AGC action)                            | VCO locked on carrier at 6MHz $560k\Omega$ load on AMPLOCK Pins $180k\Omega$ load on DET Pins | 5    |      | 500  | mV <sub>PP</sub> |

| DETH   | Detector 1 and 2 (AMPLOCK Pins)<br>(Threshold for activating Level<br>Detector 2) | 8mV <sub>PP</sub> ≤ FMIN ≤ 500mV <sub>PP</sub><br>Carrier without modulation                  | 2.90 | 3.10 | 3.30 | ٧                |

| VCOMI  | VCO Mini Frequency                                                                | V <sub>CC</sub> : 11.4 to 12.6V,<br>Tamb: 0 to 70°C                                           |      |      | 5    | MHz              |

| VCOMA  | VCO Maxi Frequency                                                                |                                                                                               | 10   |      |      | MHz              |

| AP50   | 1kHz Audio Level at PLL output (DET Pins)                                         | 0.5V <sub>PP</sub> 50kHz dev. FM input,<br>Coarse deviation set to 50kHz<br>(Reg. 05 = 36HEX) | 0.6  | 1    | 1.35 | V <sub>PP</sub>  |

| APA50  | 1kHz Audio Level at PLL output (DET Pins)                                         | 0.5V <sub>PP</sub> 50kHz dev. FM input,<br>Coarse and fine settings used                      | 0.92 | 1    | 1.08 | V <sub>PP</sub>  |

| FMBW   | FM Demodulator Bandwidth                                                          | Gain at 12kHz versus 1kHz<br>180kΩ, 82kΩ 22pF on DET Pins                                     | 0    | 0.3  | 1    | dB               |

| DPCO   | Digital Phase Comparator Output Current (CPUMP Pins)                              | Average sink and source current to external capacitor                                         |      | 60   |      | μΑ               |

### **Table 7. Automatic Noise Reduction System**

| Symbol | Parameter                                                | Test Conditions                                                     | Min. | Тур. | Max. | Unit     |

|--------|----------------------------------------------------------|---------------------------------------------------------------------|------|------|------|----------|

| LRS    | Output Level (Pins LEVEL)                                | 1V <sub>PP</sub> on left and right channel                          | 0.9  | 1    | 1.1  | $V_{PP}$ |

| LDOR   | Level Detector Output Resistance<br>(Pins PK OUT)        |                                                                     | 4.0  | 5.4  | 6.8  | kΩ       |

| NDFT   | Level Detector Fall Time Constant (Pins PK OUT)          | External 22nF to GND and 1.2M $\Omega$ to $V_{REF}$                 |      | 26.4 |      | ms       |

| NDLL   | Bias Level (Pins PK OUT)                                 | No audio in                                                         |      | 2.40 |      | V        |

| LLCF   | Noise Reduction Cut-off<br>Frequency at Low Level Audio  | 100mV <sub>PP</sub> on DET Pins, External capacitor 330pF (FC Pins) |      | 0.85 |      | kHz      |

| HLCF   | Noise Reduction Cut-off<br>Frequency at High Level Audio | 1V <sub>PP</sub> on DET Pins, External capacitor 330pF (FC Pins)    |      | 7    |      | kHz      |

Table 8. Audio Output (Pins VOL OUT R, VOL OUT L)

| Symbol                                   | Parameter                                          | Test Conditions                                                                                                                                                                                                              | Min. | Тур.     | Max. | Unit            |

|------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|------|-----------------|

| DCOL                                     | DC Output Level                                    |                                                                                                                                                                                                                              |      | 4.8      |      | ٧               |

| AOLN                                     | Audio Output Level<br>with Reg 00 = 1A             | FM input as for APA50<br>No de-emphasis, No pre-emphasis<br>No noise reduction                                                                                                                                               | 1.5  | 1.9      | 2.34 | V <sub>PP</sub> |

| AOL50                                    | Audio Output Level<br>with Reg 00 = 1A             | FM input as for APA50<br>50µs de-emphasis, 27kW//2.7nF load<br>No pre-emphasis, No noise reduction                                                                                                                           | 2.0  | 3.3      | 4.0  | V <sub>PP</sub> |

| AOL75                                    | Audio Output Level<br>with Reg 00 = 1A             | FM input as for APA50<br>75μs de-emphasis, 27kΩ//2.7nF load<br>No pre-emphasis, No noise reduction                                                                                                                           | 2.0  | 3.3      | 4.0  | V <sub>PP</sub> |

| AOL17                                    | Audio Output Level<br>with Reg 00 = 1A             | FM input as for APA50 J17 de-emphasis, $36k\Omega$ 4.7k $\Omega$ 8.2nF load No pre-emphasis, No noise reduction                                                                                                              | 2.0  | 3.2      | 4.0  | V <sub>PP</sub> |

| AMA1                                     | Audio Output Attenuation with Mute-on. Reg 00 = 00 | 1V <sub>PP</sub> - 1kHz from S2 RTN Pins                                                                                                                                                                                     | 60   | 65       |      | dB              |

| MXAT                                     | Max Attenuation before Mute.<br>Reg 00 = 01        | 1kHz, from S2 RTN Pins                                                                                                                                                                                                       |      | 32.75    |      | dB              |

| MXAG                                     | Audio Gain. Reg 00 = 1F                            | 1kHz, from S2 RTN Pins                                                                                                                                                                                                       | 5    | 6        | 7    | dB              |

| ASTP                                     | Attenuation of each of the 31 steps                | 1kHz                                                                                                                                                                                                                         |      | 1.25     |      | dB              |

| THDA1                                    | THD with Reg 00 = 1A                               | 1V <sub>PP</sub> -1kHz from S2 RTN Pins                                                                                                                                                                                      |      | 0.15     |      | %               |

| THDA2                                    | THD with Reg 00 = 1A                               | 2V <sub>PP</sub> -1kHz from S2 RTN Pins                                                                                                                                                                                      |      | 0.3      | 1    | %               |

| THDFM                                    | THD with Reg 00 = 1A                               | FM input as for APA50<br>75µs de-emphasis, ANRS ON                                                                                                                                                                           |      | 0.3      | 1    | %               |

| ACS                                      | Audio Channel Separation                           | 1V <sub>PP</sub> -1kHz on S2 RTN Pins                                                                                                                                                                                        | 60   | 74       |      | dB              |

| ACSFM                                    | Audio Channel Separation at 1kHz                   | <ul> <li>0.5 V<sub>PP</sub> - 50kHz deviation FM input on one channel</li> <li>0.5V<sub>PP</sub> no deviation FM input on the other channel</li> <li>Reg 05 = 36<sub>HEX</sub></li> <li>75ms de-emphasis, no ANRS</li> </ul> |      | 60       |      | dB              |

| SNFM                                     | Signal to Noise Ratio                              | FM input as for APA50,<br>75µs de-emphasis,<br>no ANRS, Unweighted                                                                                                                                                           |      | 56       |      |                 |

| SNFMNR                                   | Signal to Noise Ratio                              | FM input as for APA50<br>75μs de-emphasis,<br>ANRS ON, Unweighted                                                                                                                                                            |      | 69       |      |                 |

| Z <sub>OUT L</sub><br>Z <sub>OUT H</sub> | Audio Output Impedance                             | Low impedance mode<br>High impedance mode                                                                                                                                                                                    | 30   | 18<br>44 | 55   | Ω<br>kΩ         |

Table 9. Auxiliary Audio Output (Pins S2 OUT R, S2 OUT L, S3 OUT R, S3 OUT L)

| Symbol                                   | Parameter                                      | Test Conditions                                                                                                        | Min. | Тур.     | Max.      | Unit                |

|------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------|----------|-----------|---------------------|

| DCOLAO                                   | DC output level                                | Aux. input pins open circuit                                                                                           |      | 4.8      |           | V                   |

| AOLNS                                    | Audio Output Level on S2 and S3                | FM input as for APA50<br>No de-emphasis, No pre-emphasis<br>No noise reduction                                         | 1.55 | 2        | 2.42      | V <sub>PP</sub>     |

| AOL50S                                   | Audio Output Level on S2 and S3                | FM input as for APA50 50ms deemphasis, $27k\Omega//2.7nF$ load No pre-emphasis, No noise reduction                     | 2.0  | 3.4      | 4.0       | V <sub>PP</sub>     |

| AOL75S                                   | Audio Output Level on S2 and S3                | FM input as for APA50 75ms deemphasis, $27k\Omega//2.7nF$ load No pre-emphasis, No noise reduction                     | 2.0  | 3.4      | 4.0       | V <sub>PP</sub>     |

| AOL17S                                   | Audio Output Level on S2 and S3                | FM input as for APA50 J17 deemphasis, $36 \text{k}\Omega$ 4.7k $\Omega$ 8.2nF load No pre-emphasis, No noise reduction | 2.0  | 3.3      | 4.0       | V <sub>PP</sub>     |

| AGAO                                     | S2 to S3 Audio Gain and S3 to S2<br>Audio Gain | 1kHz                                                                                                                   | -1   | 0        | +1        | dB                  |

| THDA02                                   | THD on S2, Input in S3                         | 2V <sub>PP</sub> - 1kHz from Aux input pins                                                                            |      | 0.04     | 0.2       | %                   |

| THDAOFM                                  | THD on S2 or S3                                | FM input as for APA50<br>75µs de-emphasis, no ANRS                                                                     |      | 0.3      | 1         | %                   |

| Z <sub>OUT L</sub><br>Z <sub>OUT H</sub> | Audio Output Impedance                         | Low impedance mode<br>High impedance mode                                                                              | 30   | 60<br>44 | 100<br>55 | $\Omega$ k $\Omega$ |

### Table 10. I/O

| Symbol                             | Parameter                             | Test Conditions                                      | Min. | Тур.       | Max. | Unit   |

|------------------------------------|---------------------------------------|------------------------------------------------------|------|------------|------|--------|

| V <sub>IL</sub><br>V <sub>IH</sub> | Low Level Input<br>High Level Input   |                                                      | 2.4  |            | 0.8  | V<br>V |

| V <sub>OL</sub><br>V <sub>OH</sub> | Low Level Output<br>High Level Output | I <sub>sink</sub> = 2mA<br>I <sub>source</sub> = 2mA | 3.2  | 0.2<br>4.6 | 0.4  | V<br>V |

| LNB <sub>T</sub>                   | Tone Frequency                        |                                                      | 22.2 | 22.2       | 22.2 | kHz    |

| LNB <sub>D</sub>                   | Tone Signal Duty Cycle                | No load connected on I/O                             | 49   | 50         | 51   | %      |

### Table 11. Reset

| Symbol | Parameter                                    | Test Conditions                                   | Min. | Тур. | Max. | Unit |

|--------|----------------------------------------------|---------------------------------------------------|------|------|------|------|

| RTCCU  | End of Reset Threshold for V <sub>CC</sub>   | V <sub>DD</sub> = 5V, V <sub>CC</sub> going up    |      | 8.7  |      | ٧    |

| RTCCD  | Start of Reset Threshold for V <sub>CC</sub> | V <sub>DD</sub> = 5V, V <sub>CC</sub> going down  |      | 7.9  |      | V    |

| RTDDU  | End of Reset Threshold for V <sub>DD</sub>   | V <sub>CC</sub> = 12V, V <sub>DD</sub> going up   |      | 3.8  |      | V    |

| RTDDD  | Start of Reset Threshold for V <sub>DD</sub> | V <sub>CC</sub> = 12V, V <sub>DD</sub> going down |      | 3.5  |      | V    |

**Table 12. Composite Signal Processing**

| Symbol | Parameter                                                       | Test Conditions                                                    | Min. | Тур. | Max. | Unit            |

|--------|-----------------------------------------------------------------|--------------------------------------------------------------------|------|------|------|-----------------|

| VIDC   | VID IN                                                          | External load current < 1µA                                        | 2.25 | 2.45 | 2.65 | V               |

| ZVI    | VID IN Input Impedance                                          |                                                                    | 7    | 11   | 14   | kW              |

| DEODC  | DC Output Level (Pins VIDEEM)                                   |                                                                    | 2.25 | 2.45 | 2.65 | V               |

| DEOMX  | Max AC Level before Clipping (Pins VIDEEM)                      | GV = 0dB, Reg 01 = 00                                              | 2    | 0    |      | V <sub>PP</sub> |

| DGV    | Gain error vs GV @100kHz                                        | GV = 0 to 12.7dB, Reg 01 = $00 \rightarrow 3F$                     | -0.5 | -1   | 0.5  | dB              |

| INVG   | Inverter Gain                                                   | De-emphasis amplifier mounted in unity gain, Normal video selected | -0.9 | 0    | -1.1 | dB              |

| VISOG  | Video Input to SCART Outputs<br>Gain                            | @ - 3dB with GV = 0dB, Reg 01 = 00                                 | -1   |      | 1    | MHz             |

| DEBW   | Bandwidth for 1V <sub>PP</sub> input<br>measured on Pins VIDEEM | GV = 0dB, 1V <sub>PP</sub> CVBS + 0.5V <sub>PP</sub>               | 10   |      |      | %               |

| DFG    | Differential Gain on Sync Pulses measured on Pins VIDEEM        | 25Hz sawtooth (input : VID IN)                                     |      |      | 1    | dB              |

| ITMOD  | Intermodulation of FM subcarriers with chroma subcarrier        | 7.02 and 7.2MHz sub-carriers,<br>12.2dB lower than chroma          |      | -60  |      | V               |

## Table 13. Clamp Stages (Pins CLAMP IN, S1, S2, S3 VID RTN)

| Symbol | Parameter                  | Parameter Test Conditions |     | Тур. | Max. | Unit |

|--------|----------------------------|---------------------------|-----|------|------|------|

| ISKC   | Clamp Input Sink Current   | V <sub>IN</sub> = 3V      | 0.5 | 1    | 1.5  | μΑ   |

| ISCC   | Clamp Input Source Current | V <sub>IN</sub> = 2V      | 40  | 50   | 60   | μA   |

### **Table 14. Video Matrix**

| Symbol              | Parameter                                                                                    | Test Conditions                             | Min. | Тур.                         | Max. | Unit  |

|---------------------|----------------------------------------------------------------------------------------------|---------------------------------------------|------|------------------------------|------|-------|

| XTK                 | Output Level on any Output when 1V <sub>PP</sub> CVBS input is selected for any other output | @ 5MHz                                      |      | -60                          |      | dB    |

| BFG                 | Output Buffer Gain (Pins S1 VID OUT, S2 VID OUT, S2 VID OUT)                                 | @ 100kHz                                    | 1.87 | 2                            | 2.13 |       |

| DCOLVH              | DC Output Level                                                                              | High impedance mode                         |      | 0                            | 0.2  | V     |

| Z <sub>OUT HV</sub> | Video Output Impedance                                                                       | High impedance mode                         | 16   | 23                           | 30   | kΩ    |

| VCL                 | Sync Tip Level on Selected Outputs (Pins S1 VID OUT, S2 VID OUT)                             | 1V <sub>PP</sub> CVBS through 10nF on input | 1.05 | 1.3                          | 1.55 | V     |

| VCL S3              | Sync Tip Level at S3 VID OUT with Black Level Adjust                                         | Register 4 b6 b7 0 0 0 1 1 0 1 1            |      | 1.36<br>1.52<br>1.67<br>1.84 |      | V V V |

### PIN INTERNAL CIRCUITRY S1 VID RTN, S2 VID RTN, S3 VID RTN, CLAMP IN

50mA source is active only when VIDIN < 2.7V.

Figure 9.

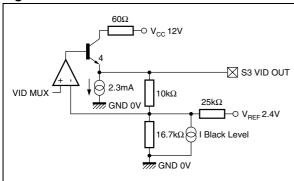

### S3 VID OUT

I black level is  $I^2C$  programmable from source 16mA to sink 33µA equivalent to an offset voltage of -150mV to +300mV.

The  $60\Omega$  collector resistor is for short cct. protection.

Figure 10.

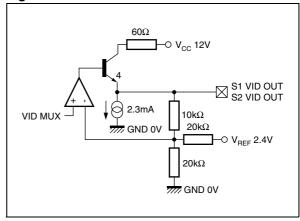

### S1 VID OUT, S2 VID OUT

Same as above but with no black level adjustment.

Figure 11.

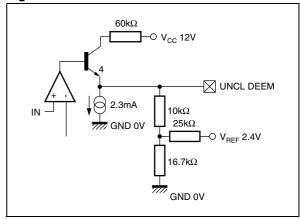

### **UNCL DEEM**

Same as above but with no black level adjustment and slightly different gain.

Figure 12.

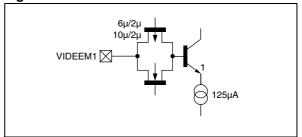

### VIDEEM1

Ron of the transistor gate is  $910k\Omega$ .

Figure 13.

### VIDEEM2 / 22kHz

Ron of the transistor gate is  $910k\Omega$ .

Figure 14.

### **VID IN**

Figure 15.

### PK OUTR, PK OUT L

Figure 16.

### FC L, FC R

Ivar is controlled by the peak det audio level max.  $\pm 15\mu A$  (1V<sub>PP</sub> audio).

Figure 17.

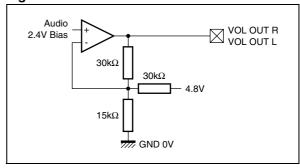

### **VOL OUT R, VOL OUT L**

Audio output with volume and scart driver with +12 dB of gain for up to  $2 V_{RMS}$ . The opamp has a push-pull output stage.

Figure 18.

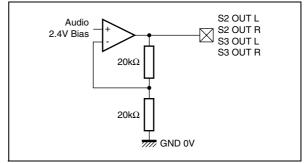

### S2 OUT L, S2 OUT R, S3 OUT L, S3 OUT R

Same as above but with gain fixed at +6dB.

Figure 19.

**477**

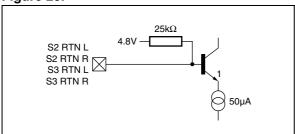

### S2 RTN L, S2 RTN R, S3 RTN L, S3 RTN R

4.8V bias voltage is the same as the bias level on the audio outputs.

Figure 20.

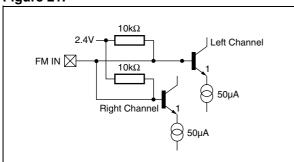

### FM IN

The other input for each channel is internally biased in the same way via  $10k\Omega$  to the 2.4V V<sub>REF</sub>.

Figure 21.

### **IREF**

The optimum value if I\_REF is 50mA ±2% so an external resistor of 47.5k $\Omega$  ±1% is required.

Figure 22.

### I/O/ 22kHz

The input is TTL compatible. The output is tri-stateable.

### Figure 23.

### SCL

This is the input to a Schmitt input buffer made with a CMOS amplifier.

### Figure 24.

### SDA

Input same as above.

Output pull down only: relies on external resistor for pull-up.

### Figure 25.

### J17 L, J17 R, U75 L, U75 R

$I1 - I2 = 2 x audio / 18k\Omega$ .

eg 1V<sub>PP</sub> audio: ±55µA.

The are internal switches to match the audio level of the different standards.

Figure 26.

### HA

Pull-down current for SDIP42. Input with CMOS levels.

Figure 27.

### XTL

Figure 28.

### **CPUMP L, CPUMP R**

An offset on the PLL loop filter will cause an offset in the two 1mA currents that will prevent the PLL from drifting-off frequency.

Figure 29.

### DET L, DET R

I2 - I1 = f (phase error).

### Figure 30.

### AMPLK L, AMPLK R, AGC L, AGC R

I2 and I1 from the amplitude detecting mixer.

Figure 31.

### **VREF**

The 400µA source is off during stand-by mode.

Figure 32.

### **LEVEL L, LEVEL R**

Figure 33.

### PK IN L, PK IN R

#### **V 12V**

Doubled bonded (two bond wires and two pads for one package pin):

- One pad is connected to all of the 12V ESD and video guard rings.

- The second pad is connected to power up the video block.

#### **V GND**

Doubled bonded:

- One pad is connected to power-up all of the video mux and I/O.

- The second pad is only as a low noise GND for the video input.

#### VDD 5V,GND 5V

Connected to XTL oscillator and the bulk of the CMOS logic and 5V ESD.

#### A GND

Doubled bonded:

- One pad connected to the left VCO, dividers, mixers and guard ring. the guard connection is star connected directly to the pad.

- The second pad is connected to both AGC amps and the deemphasis amplifiers, frequency synthesis and FM deviation selection circuit for both channels.

#### A 12V

Doubled bonded:e pad connected to the ESD and guard ring.

The second pad is connected to the main power for all of the audio parts.

#### A GND R

Doubled bonded:

- One pad connected to the right VCO, dividers, mixers and guard ring. The guard connection is star connected directly to the pad.

- The second pad is connected to the bias block, audio noise reduction, volume, mux and ESD.

A third bond wire on this pin is connected directly to the die pad (substrate).

Figure 34.

### I<sup>2</sup>C PROTOCOL

1) WRITING to the chip

S-Start Condition

P-Stop Condition

CHIP ADDR - 7 bits. Programmable 06H or 46H (STV0056A only) with Pin HA.

W-Write/Read bit is the 8th bit of the chip address.

**A-**ACKNOWLEDGE after receiving 8 bits of data/address.

**REG ADDR** Address of register to be written to, 8 bits of which bits 3, 4, 5, 6 & 7 are 'X'

or don't care ie only the first 3 bits are used.

**DATA** 8 bits of data being written to the register. All 8 bits must be written to at the

same time.

REG ADDR/A/DATA/A can be repeated, the write process can continue until terminated with a

STOP condition. If the **REG ADDR** is higher than 07 then IIC PROTOCOL

will still be met (ie an A generated).

### Table 15. Example

| S | 06 | W | Α | 00 | Α | 55 | Α | 01 | Α | 8F | <br>Α | Р |

|---|----|---|---|----|---|----|---|----|---|----|-------|---|

|   |    |   |   |    |   |    |   |    |   |    |       | i |

### 2) READING from the chip

When reading, there is an auto-increment feature. This means any read command always starts by reading Reg 8 and will continue to read the following registers in order after each acknowledge or until there is no acknowledge or a stop. This function is cyclic that is it will read the same set of registers without readdressing the chip. There are two modes of operation as set by writing to bit 7 of register 0. Read 3 registers in a cyclic fashion or all 5 registers in a cyclic fashion. Note only the last 5 of the 11 registers can be read.

Reg0 bit 7 = L -> Start / chip add / R / A/ Reg 8 / A / Reg 9 / A/ Reg 0A/ A/ Reg 8 / A/ Reg 9 / A / Reg 0A /... / P /

Reg0 bit 7 = H ⇒Start / chip add / R / A/ Reg 8 / A / Reg 9 / A/ Reg 0A / A / Reg 7 / A / Reg 6 / A / Reg 8 / A / Reg 9 / A / Reg 6 / A / Reg 6 / ... / P /

#### **CONTROL REGISTERS**

### Reg 0 write only

Bit (default 00<sub>HEX</sub>)

- 0 L Select 5 bits audio volume control 00H = MUTE

- 1 L Select 5 bits audio volume control 01H = -26.75dB

- 2 L Select 5 bits audio volume control ::: :

- 3 L Select 5 bits audio volume control 1.25dB steps up to

- 4 L Select 5 bits audio volume control 1FH = +12dB

- 5 L Audio mux switch K4 ANRS I/P select (L = PLL)

- 6 L Audio mux switch K3 ANRSselect (L = no ANRS, H = ANRS)

- 7 L L = read 3 registers, H = read 5 registers

### Reg 1 write only

Bit (default 00<sub>HEX</sub>)

- 0 L Select video gain bits

- 1 L Select video gain bits 00H = 0dB

- 2 L Select video gain bits 01H = +0.202dB

- 3 L Select video gain bits 02H = +0.404dB

- 4 L Select video gain bits n = + 0.202 dB \* n

- 5 L Select video gain bits 3FH = + 12.73 dB

- 6 L Selected video invert (H = inverted, L = non inverted)

- 7 L Video de-emphasis 1 / Video de-emphasis 2 (L: VID De-em 1)

### Reg 2 write only

Bit (default F7<sub>HEX</sub>)

- 0 H Select video source for scart 1 O/P

- 1 H Select video source for scart 1 O/P

- 2 H Select video source for scart 1 O/P

- 3 L Select 4.000MHz or 8.000MHz clock speed (L = 8MHz)

- 4 H Select audio source for volume output (Switch K1)

- 5 H Select audio source for volume output (Switch K1)

- 6 H Select Left/Right/Stereo for volume output

- 7 H Select Left/Right/Stereo for volume output

### Reg 3 write only

Bit (default F7<sub>HFX</sub>)

- 0 H Select video source for scart 2 O/P

- 1 H Select video source for scart 2 O/P

- 2 H Select video source for scart 2 O/P

- 3 L Video de-emphasis 2 / 22kHz (H: 22kHz)

- 4 H Select audio source for Scart 2 output (Switch K5)

- 5 H Select audio source for Scart 2 output (Switch K5)

- 6 H Audio de-emphasis select (Switch K2)

- 7 H Audio de-emphasis select (Switch K2)

### Reg 4 write only

Bit (default BF<sub>HEX</sub>)

- 0 H Select source for video decoder O/P

- 1 H Select source for video decoder O/P

- H Select source for video decoder O/P

H Stand-by or low power mode (H = low

- 3 H Stand-by or low power mode (H = low power)

4 H Select audio source for Scart 3 output (Switch K6)

- 5 H Select audio source for Scart 3 output (Switch K6)

- 6 L Black level adjust on Scart 3 video

- 7 H Black level adjust on Scart 3 video

```

write only

Reg 5

Bit (default B5<sub>HEX</sub>)

H FM deviation selection -- default value for 50kHz modulation

L FM deviation selection

H FM deviation selection

2

L FM deviation selection

H FM deviation selection

H FM deviation selection (L = double the FM deviation)

L Select 22kHz for I/O (Pin 29 / STV0056A)

H Select TP50a (H) or I/O (Pin 29 / STV0056A). TP50a for test only.

Reg 6

write/read

Bit (default 86<sub>HEX</sub>)

L Status of I/O

H Select data direction of I/O 1 (H = output)

H Select frequency synthesizer 1 OFF/ON (L = OFF)

3

Select frequency synthesizer 2 OFF/ON (L = OFF)

4

L Select RF source (L = OFF) to FM det 1

5

L Select RF source (L = OFF) to FM det 2

Select frequency for PLL synthesizer - LSB (bit 0) of 10-bit value

H Select frequency for PLL synthesizer - bit 1 of 10-bit value

Reg 7write/read

Bit (default AFHEX)

H Select frequency for PLL synthesizer - bit 2 of 10-bit value

H Select frequency for PLL synthesizer

1

Select frequency for PLL synthesizer

2

3

Select frequency for PLL synthesizer

Select frequency for PLL synthesizer

5

H Select frequency for PLL synthesizer

Select frequency for PLL synthesizer

H Select frequency for PLL synthesizer - bit 9, MSB (10th bit) of 10-bit value

Reg 8

read only

Bit

Subcarrier detection (DET 1) (L = No subcarrier)

0

1

Not used

2

Read frequency of watchdog 1 - LSB (bit 0) of 10-bit value

Read frequency of watchdog 1 - bit 1 of 10-bit value

3

Subcarrier detection (DET 2) (L = No subcarrier)

5

Not used

Read frequency of watchdog 2 - bit 0 of 10-bit value

Read frequency of watchdog 2 - bit 1 of 10-bit value

Reg 9

read only

Bit (default AFHEX)

Read frequency of watchdog 1 - bit 2 of 10-bit value

1

Read frequency of watchdog 1

2

Read frequency of watchdog 1

Read frequency of watchdog 1

3

4

Read frequency of watchdog 1

5

Read frequency of watchdog 1

6

Read frequency of watchdog 1

Read frequency of watchdog 1 - bit 9, MSB (10th bit) of 10-bit

```

# Reg 0A read only Bit

Read frequency of watchdog 2 - bit 2 of 10-bit value

Read frequency of watchdog 2

4 Read frequency of watchdog 2

5 Read frequency of watchdog 2

6 Read frequency of watchdog 2

Read frequency of watchdog 2 - bit 9, MSB (10th bit) of 10-bit

### **Video Mux Truth Tables**

Register 2 <0:2> ⇒ Scart 1 video output control

Register 3 <0:2> ⇒ Scart 2 video output control

Register 4 <0:2> ⇒ Scart 3 decoder output control

The truth table for the three scart outputs are the same.

| F      | Register 2/3 | /4     | Video Output                  |  |  |  |

|--------|--------------|--------|-------------------------------|--|--|--|

| Bit<2> | Bit<1>       | Bit<0> |                               |  |  |  |

| 0      | 0            | 0      | Baseband video                |  |  |  |

| 0      | 0            | 1      | De-emphasized video           |  |  |  |

| 0      | 1            | 0      | Normal video                  |  |  |  |

| 0      | 1            | 1      | Scart 3 return                |  |  |  |

| 1      | 0            | 0      | Scart 2 return                |  |  |  |

| 1      | 0            | 1      | Scart 1 return                |  |  |  |

| 1      | 1            | 0      | Nothing selected              |  |  |  |

| 1      | 1            | 1      | High Z or low power (default) |  |  |  |

| Regi   | Register 4 |             | Black Level Adjust on Scart 3 |  |

|--------|------------|-------------|-------------------------------|--|

| Bit<7> | Bit<6>     |             |                               |  |

| 0      | 0          | -150mV      |                               |  |

| 1      | 0          | 0 (default) |                               |  |

| 0      | 1          | +150mV      |                               |  |

| 1      | 1          | +300mV      |                               |  |

### **Table 16. Audio Mux Truth Tables**

| Register 2     |                            |             | Switch K1/Audio Source Selection for Volume Output                                                          |

|----------------|----------------------------|-------------|-------------------------------------------------------------------------------------------------------------|

| Bit<5> 0 1 0 1 | Bit<4><br>0<br>0<br>1<br>1 | A<br>C<br>B | Volume Output Audio de-emphasis (K2 switch O/P) Scart 2 return Scart 3 return High Z or low power (default) |

|                | Register 3                 |                  | Switch K2/Audio De-emphasis                              |

|----------------|----------------------------|------------------|----------------------------------------------------------|

| Bit<7> 0 1 0 1 | Bit<6><br>0<br>0<br>1<br>1 | A<br>C<br>B<br>B | Audio De-emphasis No de-emphasis J17 50μs 75μs (default) |

|                             | Register 0                  |                  | Switch K3 & K4                                                                                  |

|-----------------------------|-----------------------------|------------------|-------------------------------------------------------------------------------------------------|

| Bit <6><br>0<br>1<br>X<br>X | Bit <5><br>X<br>X<br>0<br>1 | A<br>B<br>A<br>B | ANRS I/O Select Noise reduction OFF Noise reduction ON (default) I/P = PLL I/P = Scart 3 return |

|                        | Register 3             |             | Switch K5/Audio Source Selection for Scart 2                                 |

|------------------------|------------------------|-------------|------------------------------------------------------------------------------|

| Bit <5><br>0<br>1<br>0 | Bit <4><br>0<br>0<br>1 | C<br>A<br>B | Aux Audio Output PLL output Scart 3 return Audio de-emphasis (K2 switch O/P) |

| 1                      | 1                      | -           | High Z or low power state (default)                                          |

|         | Register 4 |   | Switch K6/Audio Source Selection for Scart 3 |

|---------|------------|---|----------------------------------------------|

| Bit <5> | Bit <4>    |   | Audio Decoder Output                         |

| 0       | 0          | Α | PLL output                                   |

| 1       | 0          | С | Audio de-emphasis (K2 switch O/P)            |

| 0       | 1          | В | Scart 2 return                               |

| 1       | 1          | - | High Z or low power state (default)          |

| Regis         | ster 2                 | Left / Right / Stereo on Volume Output                                           |

|---------------|------------------------|----------------------------------------------------------------------------------|

| Bit <7> 0 1 1 | Bit <6><br>0<br>0<br>1 | Mono left / channel 1<br>Mono right / channel 2<br>Stereo left & right (default) |

**Table 17. Register 5: FM Deviation Selection**

| 4   | 3 | 2 | 1 | 0 | elected Nominal Carrier Modulation |                                         |

|-----|---|---|---|---|------------------------------------|-----------------------------------------|

| 4   | , | 2 | ı | O | Bit 5 = 0                          | Bit 5 = 1                               |

| 0   | 0 | 0 | 0 | 0 | Do not use                         | cal: do not use = 0.3373V offset on VCO |

| 0   | 0 | 0 | 0 | 1 | Do not use                         | cal: do not use = 0.3053V offset on VCO |

| 0   | 0 | 0 | 1 | 0 | Do not use                         | cal: do not use = 0.2763V offset on VCO |

| 0   | 0 | 0 | 1 | 1 | Cal. set. (2V)                     | calibration setting (1V offset on VCO)  |

| 0   | 0 | 1 | 0 | 0 | 592kHz                             | 296kHz modulation                       |

| 0   | 0 | 1 | 0 | 1 | 534kHz                             | 267kHz modulation                       |

| 0   | 0 | 1 | 1 | 0 | 484kHz                             | 242kHz                                  |

| 0   | 0 | 1 | 1 | 1 | 436kHz                             | 218kHz                                  |

| 0   | 1 | 0 | 0 | 0 | 396kHz                             | 198kHz                                  |

| 0   | 1 | 0 | 0 | 1 | 358kHz                             | 179kHz                                  |

| 0   | 1 | 0 | 1 | 0 | 322kHz                             | 161kHz                                  |

| 0   | 1 | 0 | 1 | 1 | 292kHz                             | 146kHz                                  |

| 0   | 1 | 1 | 0 | 0 | 266kHz                             | 133kHz                                  |

| 0   | 1 | 1 | 0 | 1 | 240kHz                             | 120kHz                                  |

| 0   | 1 | 1 | 1 | 0 | 218kHz                             | 109kHz                                  |

| 0   | 1 | 1 | 1 | 1 | 196kHz                             | 98.3kHz                                 |

| 1   | 0 | 0 | 0 | 0 | 179kHz                             | 89.7kHz                                 |

| 1   | 0 | 0 | 0 | 1 | 161kHz                             | 80.9kHz                                 |

| 1   | 0 | 0 | 1 | 0 | 146kHz                             | 73.1kHz                                 |

| 1   | 0 | 0 | 1 | 1 | 122kHz                             | 66.0kHz                                 |

| 1   | 0 | 1 | 0 | 0 | 120kHz                             | 60.0kHz                                 |

| 1   | 0 | 1 | 0 | 1 | 109kHz                             | 54.4kHz = default power up state        |

| 1   | 0 | 1 | 1 | 0 | 98kHz                              | 49.1kHz                                 |

| 1   | 0 | 1 | 1 | 1 | 89kHz                              | 44.3kHz                                 |

| 1   | 1 | 0 | 0 | 0 | 78kHz                              | 39.8kHz                                 |

| 1   | 1 | 0 | 0 | 1 | 71kHz                              | 35.9kHz                                 |

| 1 1 | 1 | 0 | 1 | 0 | 65kHz                              | 32.4kHz                                 |

| 1   | 1 | 0 | 1 | 1 | 58kHz                              | 29.1kHz                                 |

| 1   | 1 | 1 | 0 | 0 | 53kHz                              | 26.7kHz                                 |

| 1   | 1 | 1 | 0 | 1 | 48.6kHz                            | 24.3kHz                                 |

| 1   | 1 | 1 | 1 | 0 | 43.8kHz                            | 21.9kHz                                 |

| 1   | 1 | 1 | 1 | 1 | 39.6kHz                            | 19.7kHz                                 |

| Register 1<br>Bit <7> | Register 3<br>Bit <3> | Video De-emphasis/22kHz |  |  |

|-----------------------|-----------------------|-------------------------|--|--|

| 0                     | 0                     | De-emphasis 1 (default) |  |  |

| 0                     | 1                     | De-emphasis 1 + 22kHz   |  |  |

| 1                     | 0                     | De-emphasis 2           |  |  |

| 1                     | 1                     | De-emphasis 2           |  |  |

| Regis         | ster 5                      | Digital I/O (STV0056A pin 29)                                                              |

|---------------|-----------------------------|--------------------------------------------------------------------------------------------|

| Bit <7> 0 0 1 | Bit <6><br>0<br>1<br>0<br>1 | I/O (refer to Register 6 Bit <0> Bit <1>) 22kHz Do not use (for test only) (default) 22kHz |

#### **FM DEMODULATION SOFTWARE ROUTINE**

With the STV0056A circuit, for each channel, three steps are required to achieve a FM demodulation:

- 1st step: To set the demodulation parameters:

- FM deviation selection,

- Subcarrier frequency selection.

- 2nd step: To implement a waiting loop to check the actual VCO frequency.

- 3rd step: To close the demodulation phase locked loop (PLL).

Referring to the FM demodulation block diagram, the frequency synthesis block is common to both

channels (left and right); consequently two complete sequence shave to be done one after the other when demodulating stereo pairs.

### **Detailed Description**

Conventions:

- R = Stands for Register

- B = Stands for Bit

Example: R05 B2 = Register 05, Bit 2

For clarity, the explanations are based on the following example: stereo pair 7.02MHz/L 7.20MHz/R, deviation ±50kHz max.

### 1ST STEP (LEFT): SETTING THE DEMODULATION PARAMETERS

**A.** The FM deviation is selected by loading R5 with the appropriate value (see R5 truth table).

NB: Very wide deviations (up to  $\pm 592 \text{kHz}$ ) can be accommodated when R5 B5 is low.

Corresponding bandwidth can be calculated as follows:

Bw ≈ 2 (FM deviation + audio bandwidth)

Bw  $\approx$  2 (value given in table + audio bandwidth) In the example:

- **B.** The subcarrier frequency is selected by launching a frequency synthesis (the VCO is driven to the wanted frequency). This operation requires two actions:

- To connect the VCO to the frequency synthesis loop. Refering to the FMblock diagram:

- SW4 closed ⇒ R6 B2 = H

- SW3 to bias ⇒ R6 B4 = L

- SW2 to bias ⇒ R6 B3 = L

- SW1 opened ⇒ R6 B5 = L

- To load R7 and R6 B6 B7 with the value corresponding to the left channel frequency. This 10 bits value is calculated as follows: Subcarrier frequency = coded value x 10kHz (10kHz is the minimum step of the frequency synthesis function) Considering that the tunning range is comprised between5 to 10MHz, the coded valueis a number between 500 and 1000 (2<sup>10</sup> = 1024) then 10 bits are required.

Example:

$7.02MHz = 702 \times 10kHz$   $702 \implies 1010 \ 1111 \ 10 \implies AF + 10$ R7 is loaded with AF and R6 B6: L, R6 B7: H.

Table 18 gives the setting for the most common subcarrier frequencies.

Table 18. Frequency Synthesis Register Setting for the Most Common Subcarrier Frequencies

| Subcarrier Frequency | Register 7 | Register 6 |       |

|----------------------|------------|------------|-------|

| (MHz)                | (HEX)      | Bit 7      | Bit 6 |

| 5.58                 | 8B         | 1          | 0     |

| 5.76                 | 90         | 0          | 0     |

| 5.8                  | 91         | 0          | 0     |

| 5.94                 | 94         | 1          | 0     |

| 6.2                  | 9B         | 0          | 0     |

| 6.3                  | 9D         | 1          | 0     |

| 6.4                  | A0         | 0          | 0     |

| 6.48                 | A2         | 0          | 0     |

| 6.5                  | A2         | 1          | 0     |

| 6.6                  | A5         | 0          | 0     |

| 6.65                 | A6         | 0          | 1     |

| 6.8                  | AA         | 0          | 0     |

| 6.85                 | AB         | 0          | 1     |

| 7.02                 | AF         | 1          | 0     |

| 7.20                 | B4         | 0          | 0     |

| 7.25                 | B5         | 0          | 1     |

| 7.38                 | B8         | 1          | 0     |

| 7.56                 | BD         | 0          | 0     |

| 7.74                 | C1         | 1          | 0     |

| 7.85                 | C4         | 0          | 1     |

| 7.92                 | C6         | 0          | 0     |

| 8.2                  | CD         | 0          | 0     |

| 8.65                 | D8         | 0          | 1     |

### 2ND STEP (LEFT): VCO FREQUENCYCHECKING (VCO)

This second step is actually a waiting loop in which the actual running frequency of the VCO is measured.

To exit of this loop is allowed when: Subcarrier Frequency -  $10kHz \le Measured$  Frequency  $\le Subcarrier$  Frequency + 10kHz ( $\pm$  10kHz is the maximum dispersion of the frequency synthesis function).

In practice, R8 B2 B3 and R9 are read and compared to the value loaded in R6 B6 B7 and R7  $\pm 1$  bit.

#### Note:

The duration of this step depends on how large is frequency difference between the start frequency and the targeted frequency. Typically:

- the rate of change of the VCO frequency is about 3.75 MHz/s ( $C_{pump} = 10 \mu F$ )

- In addition to this settling time, 100ms must be added to take into account the sampling period of the watchdog.

### **3RD STEP (LEFT)**

The FMdemodulationcan bestarted byconnecting the VCO to the phase locked loop (PLL).

In practice:

- SW3 closed ⇒ R6 B4 = H

- SW4 opened ⇒ R6 B2 = L

After this sequence of 3 steps for left channel, a similar sequence is needed for the right channel.

#### Note

In the sequence for the right, there is no need to again select the FM deviation (once is enough for the pair).

#### General Remark

Before to enable the demodulated signal to the audio output, it is recommanded to keep the muting

and to check whether a subcarrier is present at the wanted frequency. Such an information is available in R8 B0 and R8 B4 which can be read.

Two different strategies can be adopted when enabling the output:

- Either both left and right demodulated signals are simultaneously authorized when both channel are ready.

- Or while the right channel sequence running, the already ready left signal is sent to the left and right outputs and the real stereo sound L/R is output when both channels are ready. This second option gives sound a few hundreds of ms before the first one.

Figure 35. TYPICAL APPLICATION (3 SCARTS, PAL/SECAM Europe Application)

### **TWIN TUNER APPLICATION**

Easy parallel connection of the outputs to the carts without any additional switching hardware.

This configuration is possible due to the high impedance mode that can be selected for each audio and video outputs.

Figure 36. Twin Tuner Application

### **PART NUMBERING**

### **Table 19. Order Codes**

| Part Number | Package  | Temperature Range |

|-------------|----------|-------------------|

| STV0056A    | SHRINK56 | 0 to 70°C         |

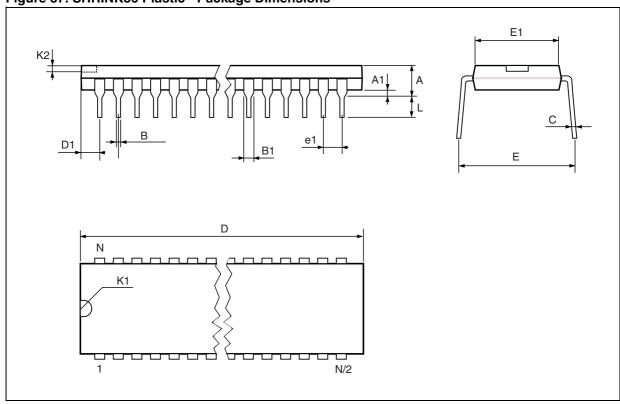

### **PACKAGE MECHANICAL**

Table 20. SHRINK56 Plastic - Mechanical Data

| Symbol |      | millimeters |       | inches    |       |       |  |

|--------|------|-------------|-------|-----------|-------|-------|--|

|        | Min  | Тур         | Max   | Min       | Тур   | Max   |  |

| Α      |      |             | 5.08  |           |       | 0.200 |  |

| A1     | 0.51 |             |       | 0.020     |       |       |  |

| В      | 0.35 |             | 0.59  | 0.014     |       | 0.023 |  |

| B1     | 0.75 |             | 1.42  | 0.030     |       | 0.056 |  |

| С      | 0.20 |             | 0.36  | 0.008     |       | 0.014 |  |

| D      |      | 52.12       |       |           | 2.052 |       |  |

| D1     | _    | _           | _     | -         | _     | _     |  |

| Е      |      |             | 18.54 |           |       | 0.730 |  |

| E1     |      | 13.72       |       |           | 0.540 |       |  |

| K1     | _    | _           | _     | -         | _     | _     |  |

| K2     | _    | _           | _     | -         | _     | _     |  |

| L      | 2.54 |             | 3.81  | 0.100     |       | 0.150 |  |

| e1     |      | 1.78        |       |           | 0.070 |       |  |

|        |      | •           | Numbe | r of Pins |       |       |  |

| N      | 56   |             |       |           |       |       |  |

Figure 37. SHRINK56 Plastic - Package Dimensions

Note: Drawing is not to scale

### **REVISION HISTORY**

**Table 21. Revision History**

| Date           | Revision | Description of Changes                |

|----------------|----------|---------------------------------------|

| September-1996 | 1        | First Issue                           |

| 9-June-2004 2  |          | Stylesheet update. No content change. |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners

© 2004 STMicroelectronics - All rights reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States

www.st.com