# Video Processor for CRT Monitors with PictureBooST™

### **Main Features**

#### ■ General

- I2C-Bus Controlled

- Supports AC- and DC-coupled applications

- 5V to 8V Power Supply

- Matches to virtually any video amplifier

### **■** PictureBooST<sup>™</sup>

- PictureBooST™ insertion input

- Full-screen PictureBooST™ via I²C-bus

- Context-sensitive Picture Enhancement

## ■ Video Clamping

- Input and Output Video Clamp

- Sync Pulse Polarity Auto-rectification

- Clamp Pulse Generation timed either by sync or video blanking pulse

## **■** Video Processing

- Contrast Adjustment with excellent channel matching

- Gain stages for control of white

- Two DC-mode cut-off ranges

- Output DC offset control

- Automatic Beam Limiter (ABL)

- Video Insertion Pulse (VIP), 2 levels

- Amplifier Control (Blanking and Stand-by)

#### ■ OSD Insertion with Contrast Control

### **■** Control Output

- Amplifier Standby and Blanking Control

- 3 DAC for control of DC Restore Amplifier or Brightness in DC-coupled system

## **General Description**

The STV9212 is an I²C-bus controlled color video processor designed for standard CRT monitor applications. It can drive systems where cathodes are either AC- or DC-coupled to the amplifier outputs. The three video channels provide contrast and white balance separate gain adjustments as well as one-per-channel DC cut-off control and common DC offset control functions. On top of these usual controls, it features context-sensitive picture enhancement circuitry to support the PictureBooST™ function that enhances the appearance of still pictures and moving video.

In AC coupling applications, the device can pilot three cathode DC restore channels dedicated to set CRT cut-off bias voltages and to control brightness through cathodes.

The RGB video outputs have a class A architecture and directly drive the amplifier channels without unnecessarily consuming current. Bandwidth limitation I<sup>2</sup>C-bus adjustments can contribute to keeping the application EMI under control.

OSD (On-Screen Display) graphics are inserted by means of a Fast Blanking signal. Independent OSD contrast control facilitates adaptation to various OSD generators and provides system flexibility.

The STV9212 is perfectly compatible with other ST components for CRT video boards, such as video amplifiers and OSD generators.

October 2003 1/34

# **Table of Contents**

| Chapter 1 | STV9212 Pin Allocation and Description             |    |

|-----------|----------------------------------------------------|----|

| 1.1       | Pinout                                             | 4  |

| 1.2       | Pin Descriptions                                   | 4  |

| Chapter 2 | Functional Description                             |    |

| 2.1       | Video RGB Input Clamp                              | 6  |

| 2.2       | Video Blanking                                     | 8  |

| 2.3       | Contrast Control Stage and Automatic Beam Limiter  | 9  |

| 2.4       | PictureBooST                                       | 10 |

| 2.5       | OSD Insertion                                      | 11 |

| 2.6       | Drive Stage                                        | 11 |

| 2.7       | Video Insertion Pulse                              | 12 |

| 2.8       | Output Stage                                       | 12 |

| 2.9       | Output Infra-black Level, Cut-off and Brightness   | 15 |

| 2.10      | Signal Waveforms                                   | 18 |

| 2.11      | Miscellaneous                                      | 18 |

| Chapter 3 | I <sup>2</sup> C-Bus Interface Specifications      |    |

| 3.1       | I <sup>2</sup> C-bus Register Descriptions         | 21 |

| Chapter 4 | Electrical Specifications                          | 24 |

| 4.1       | Absolute Maximum Ratings                           | 24 |

| 4.2       | Thermal Data                                       | 24 |

| 4.3       | Static Electrical Characteristics                  | 24 |

| 4.4       | Dynamic Electrical Characteristics                 | 25 |

| 4.5       | I <sup>2</sup> C-Bus Electrical Characteristics    | 27 |

| 4.6       | I <sup>2</sup> C-Bus Interface Timing Requirements | 27 |

| Chapter 5 | Soldering Information                              |    |

| Chapter 6 | Package Mechanical Data                            |    |

| Chapter 7 | Input/Output Diagrams                              |    |

| S٦ | Г١ | /( | 31 | 1 | 2 |

|----|----|----|----|---|---|

| J  | ١, |    | 74 | _ | _ |

| Chapter 8 | Revision History | <br> |  |

|-----------|------------------|------|--|

# 1 STV9212 Pin Allocation and Description

# 1.1 Pinout

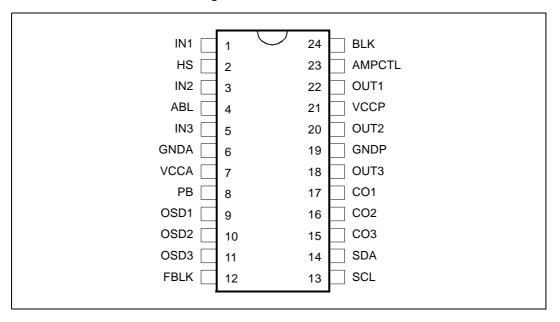

Figure 1: STV9212 Pinout

# 1.2 Pin Descriptions

**Table 1: STV9212 Pin Descriptions**

| Pin | Name | Function                     | Pin | Name   | Function                               |

|-----|------|------------------------------|-----|--------|----------------------------------------|

| 1   | IN1  | Video Input, Channel 1       | 13  | SCL    | I <sup>2</sup> C-bus Clock Input       |

| 2   | HS   | Video Clamp Sync Input       | 14  | SDA    | I <sup>2</sup> C-bus Data Input/Output |

| 3   | IN2  | Video Input, Channel 2       | 15  | CO3    | Cut-off / Brightness DAC 3 Output      |

| 4   | ABL  | Automatic Beam Limiter Input | 16  | CO2    | Cut-off DAC 2 Output                   |

| 5   | IN3  | Video Input, Channel 3       | 17  | CO1    | Cut-off DAC 1 Output                   |

| 6   | GNDA | Analog Ground                | 18  | OUT3   | Video Output, Channel 3                |

| 7   | VCCA | Analog Supply                | 19  | GNDP   | Output Stage Ground                    |

| 8   | PB   | Picture Boost Input          | 20  | OUT2   | Video Output, Channel 2                |

| 9   | OSD1 | OSD Input, Channel 1         | 21  | VCCP   | Output Stage Supply                    |

| 10  | OSD2 | OSD Input, Channel 2         | 22  | OUT1   | Video Output, Channel 1                |

| 11  | OSD3 | OSD Input, Channel 3         | 23  | AMPCTL | Output for Amplifier Control           |

| 12  | FBLK | OSD Insertion Control Input  | 24  | BLK    | Blanking and Video Clamp Sync Input    |

# 2 Functional Description

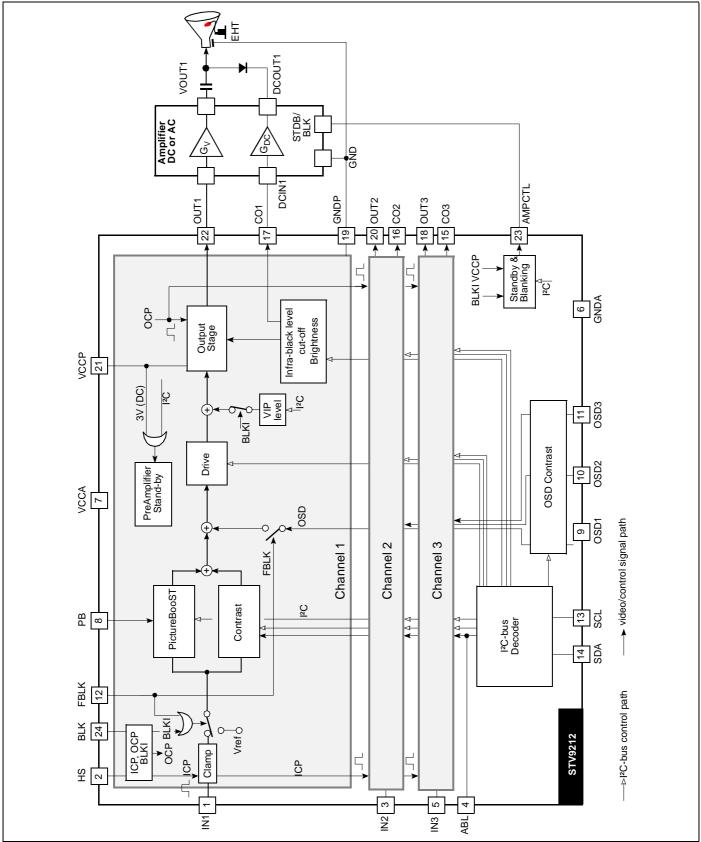

The functional blocks are described in the order they act on the signal.

Figure 2: STV9212 Block Diagram

# 2.1 Video RGB Input Clamp

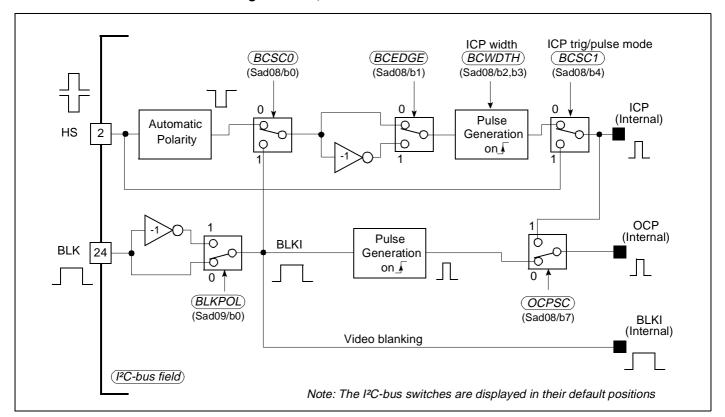

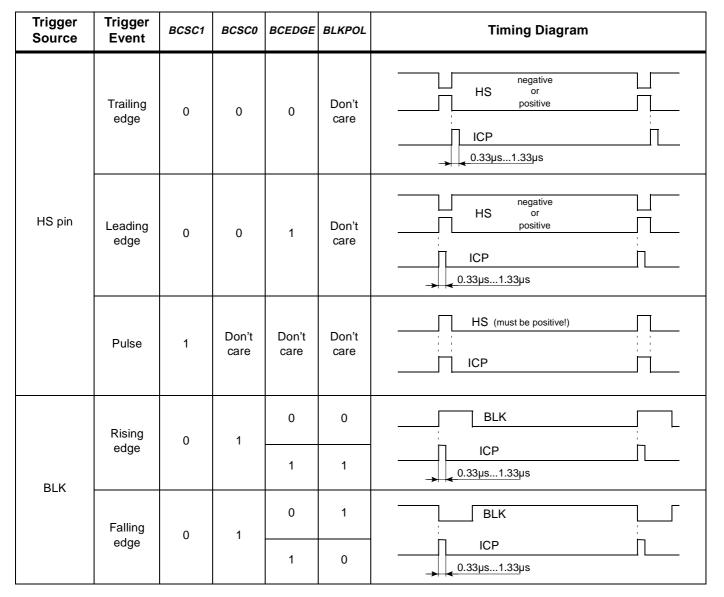

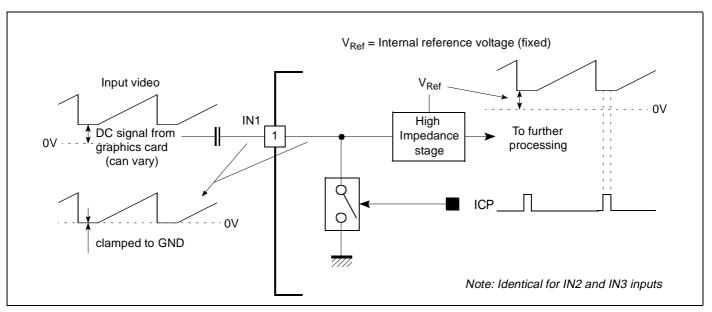

The three RGB inputs have to be supplied with a video signal through coupling capacitors playing the role of analog memories for internal video clamps. The input clamping level is approximately 0V. The clamp is gated by the Input Clamp Pulse (ICP) that is internally generated from a signal on either the HS or BLK pin. The selection is done via register 8 of the I<sup>2</sup>C-bus. For more information, refer to Figure 3: ICP, OCP and BLKI Generation and Table 2: ICP Timing.

Provided with an automatic polarity rectification function, the HS input accepts horizontal synchronization signals of either polarity. The device can select either the leading or trailing edge of this signal to trigger the ICP generator.

The BLK input is followed by an inverter stage that can be enabled or by-passed via the I²C-bus. This allows the use of a signal of either polarity, the control software taking care of the inverter position according to the signal applied. The BLKI signal found behind this inverter stage also drives the video blanking circuitry which requires a positive BLKI polarity for correct operation. Once bit *BLKPOL* has correctly been uploaded to ensure a positive BLKI polarity, the ICP triggering edge can be selected via control bit *BCEDGE*. A horizontal flyback pulse is generally expected to be applied on the BLK input. As the edges of horizontal flyback pulse can fall into the active video content (outside the video signal line blanking portion), the application must ensure that such an edge is never selected for triggering the ICP.

The width of the internally generated ICP is controlled via the I<sup>2</sup>C-bus. The HS input can be used to pass a clamping pulse, if available in the application, directly to clamping stages, without any additional processing. In this case, the appropriate polarity (positive) is required. See Table 2: ICP Timing. The ICP timings triggered by the trailing edge of the BLK signal are not presented.

The Output Clamp Pulse (OCP) is described in Section 2.8: Output Stage.

Figure 3: ICP, OCP and BLKI Generation

**Table 2: ICP Timing**

Figure 4: Video Input Clamp

# 2.2 Video Blanking

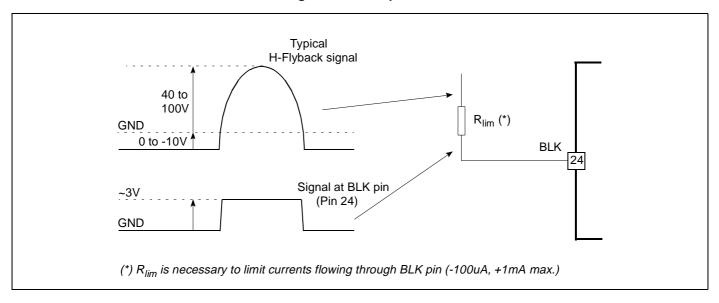

The three video channels are simultaneously blanked with the high level of either BLKI or FBLK signals. BLKI is an internal signal drawn from the signal applied on the BLK pin (H-flyback) as shown in Figure 3. The blanking consists in forcing a "black" level to the internal clamped video signal.

## **BLK Input**

The BLK input receives an H-flyback pulse that drives:

- the video blanking circuitry during scan line retrace,

- the output clamping stage.

A clipping circuit at the input allows the direct use of a high-voltage H-flyback pulse applied through a serial resistor as shown in Figure 5. A logic-level signal is also accepted but the serial resistor remains mandatory. In all cases, the value of this resistor must be such that the sinking and sourcing currents are limited to 1mA and 100µA, respectively.

Figure 5: BLK Input Pin

## **Permanent Blanking**

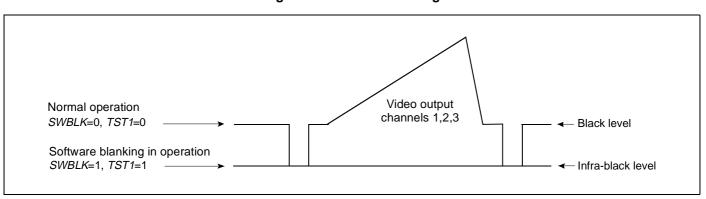

The entire TV screen can be blanked for an unlimited amount of time using the software blanking feature. Both bits *SWBLK* and *TST1* must be set to 1. The three video outputs are forced to their infra-black levels as shown in Figure 6. Infra-black levels are defined in Section 2.9.

Figure 6: Software Blanking

The screen can also be blanked by permanently keeping the On-Screen Display FBLK input signal at high level. In this case, only the video contents of the three video channels are replaced by "black level" OSD content insertion (signals on pins OSD1 through OSD3 permanently at low level). Refer to Section 2.5: OSD Insertion on page 11.

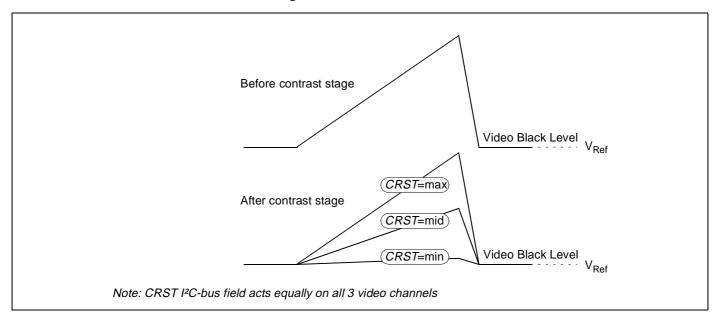

# 2.3 Contrast Control Stage and Automatic Beam Limiter

The contrast stages are simultaneously controlled on all three RGB channels with high attenuation matching precision. Refer to electrical specifications for values. See Figure 7: Contrast Control and Table 4: I<sup>2</sup>C-Bus Register Map.

**Figure 7: Contrast Control**

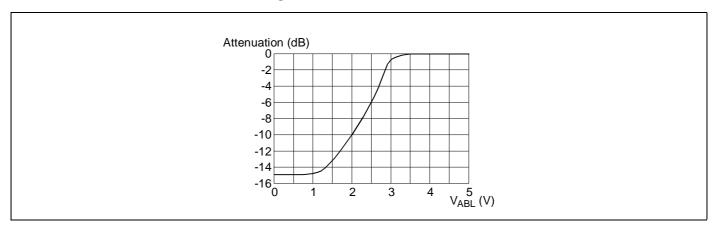

The Automatic Beam Limiter (ABL) is an attenuator controlled through the ABL input, independent of contrast stage attenuation. The operating range is about 2 V (from 3 V to 1 V). A typical characteristic is shown in Figure 8. Refer to Section 4: Electrical Specifications for specific values. When not used, the ABL pin is to be connected to VCCA.

Figure 8: ABL Characteristics

## 2.4 PictureBooST

The PictureBooST™ function provides a picture enhancement effect for images with photographic or moving video contents.

The function is activated whenever the level on pin PB is high (TTL) or the bit *PBINS* is at 1, if the general PictureBooST™ enable bit *PBGEN* is at 1. By means of PB input signal toggling, the function can take effect in a part of the screen, e.g. a window, or on the whole screen.

The picture enhancement is achieved through combination of three actions, as shown in Figure 9:

- a content-sensitive peaking with slow restore (vivacity),

- a contrast addition.

- a brightness addition.

The vivacity amplitude depends on the slope height and steepness and on the status of bits PBVIVAM[1:0]. The return to stabilized state is exponential with a time constant adjustable via bits PBVIVTC[2:0]. Any undershoot below the video black level is clipped to a level close to black.

The PictureBooST™ brightness is a DC offset superimposed on the video signal in the boosted zone. Its value is selected by bits *PBBRIG*[1:0]. The vivacity and PictureBooST™ brightness are both enabled by bit *PBVIVEN*.

The PictureBooST™ contrast component evenly increases the video amplitude in the boosted zone. Its value is controlled by bits *PBCRST[1:0]*.

Refer to Section 4: Electrical Specifications for values.

Video before PictureBooST™ stage

PB input

Video after PictureBooST™ stage

PB brightness

clipping

Figure 9: PictureBooST Action

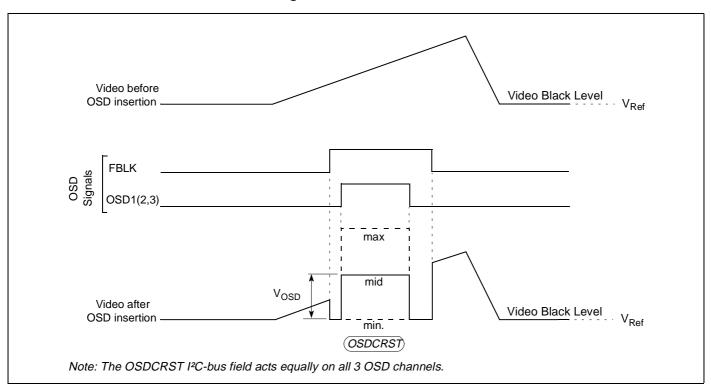

### 2.5 OSD Insertion

The On-Screen Display (OSD) is inserted with a high level on the FBLK input (TTL). The device acts as follows:

- The three RGB video input signals (IN1, IN2, IN3) are internally blanked, i.e. put at the black level.

- Binary levels (TTL) on inputs OSD1, OSD2 and OSD3, after processing in the OSD contrast stage, are added to the corresponding blanked video channels.

In this way, the OSD contents replace the video contents where the FBLK input is high. See Figure 2 and Figure 10.

The OSD is inserted after the PictureBooST™ block and before the Drive block. As a consequence, OSD insertion overlaps all video contents, including the PictureBooST™-ed zones. Color temperature adjustments by means of the I²C-bus Drive registers act in the OSD insets.

The OSD contrast stage allows the adjustment of the level of OSD insets simultaneously on the three OSD channels and independently of the video contrast adjustment. Refer to Section 4: Electrical Specifications for values.

Figure 10: OSD Insertion

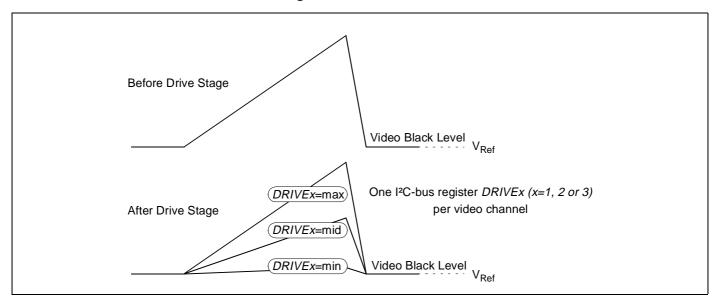

# 2.6 Drive Stage

The Drive stage is a set of three attenuators separately controlled via three I²C-bus registers, DRIVE1, DRIVE2 and DRIVE3. It affects all signals, ordinary video, PictureBooST™ processed video and OSD insets. It is designed to compensate for differences in gain of the three CRT cathodes. See Figure 11 and for values, refer to Section 4: Electrical Specifications.

Figure 11: Drive Control

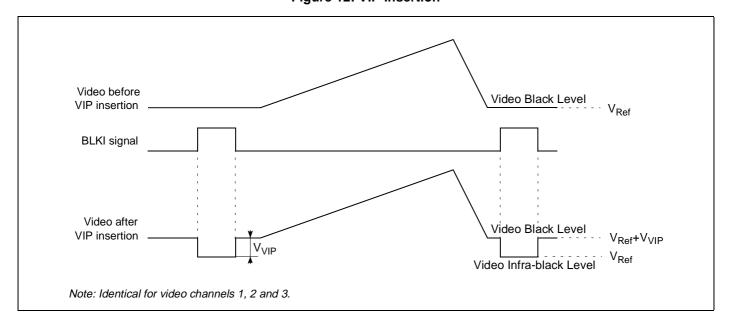

## 2.7 Video Insertion Pulse

The Video Insertion Pulse (VIP) creates an indent on the three video signals, timed with the positive part of the BLKI signal. (See Section 2.2: Video Blanking on page 8). As its level is below the video black level, it introduces a video "infra-black" level. The video infra-black level position versus ground is then controlled in subsequent stages. In the absence of the blanking pulse on pin BLK, the VIP is not inserted and the subsequent stages control the position of video black level. Figure 12 shows the signal before and after insertion of the VIP. Two different VIP values are programmable by bit *VIP*. Refer to Section 4: Electrical Specifications for values.

Figure 12: VIP Insertion

# 2.8 Output Stage

The output stage consists of an output clamp and a buffer. If a reduced output video amplitude and/ or a reduced infra-black level range is sufficient in the application, the  $V_{CCP}$  can be lowered to 5V.

Even at 8V of V<sub>CCP</sub>, care must be taken at device application level to ensure operation without signal top limitation.

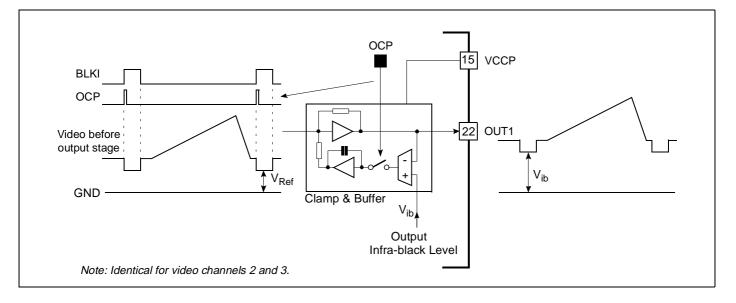

## 2.8.1 Output Clamp

The DC position of video infra-black and video black levels at the video outputs must be fixed regardless of video or OSD inset contents, especially in applications where the device's output infra-black level determines directly the infra-black level on the CRT cathodes (DC-coupled applications). This fixing is achieved by means of a fully-integrated output clamp that brings the output video infra-black level (video black level, in absence of the BLK pulse) to the level of a variable reference (V<sub>ib</sub>) as shown in Figure 13. The V<sub>ib</sub> is described in detail in Section 2.9 on page 15. The clamp circuit is driven by the Output Clamp Pulse (OCP). For correct operation, this pulse must entirely fall into the VIP pulse if this is present (clamp of infra-black level) or onto the video black part (clamp of black level). In the former case, the OCP generator is to be triggered with the leading edge of the BLK pulse, in the latter case it must copy the ICP pulse. Refer to Figure 3 for the OCP generation block diagram. Table 3 shows possible OCP timings. Although possible, the OCP timings, triggered by the BLK trailing edge, are not shown as they have no practical use.

#### 2.8.2 Bandwidth Control

Controlled via bits *BW[3:0]*, the output stage can limit the rise and fall time of the output signal. The optimum choice for this adjustment is highly application dependent. Refer to Section 4: Electrical Specifications for values and to Section 6: Application Hints for practical advice.

## 2.8.3 Output Buffer

The output buffer provides enough current so that external buffers are not required and the power amplifier can interface directly to the device's outputs.

Figure 13: Output Stage

**Table 3: OCP Timing**

| Source | Trigger<br>Event | OCPSC | BLKPOL     | Timing Diagram |

|--------|------------------|-------|------------|----------------|

| ICP    | Pulse            | 1     | Don't care | ICP            |

| BLK    | Rising<br>edge   | 0     | 0          | BLK OCP        |

| BEIX   | Falling<br>edge  |       | 1          | BLK            |

# 2.9 Output Infra-black Level, Cut-off and Brightness

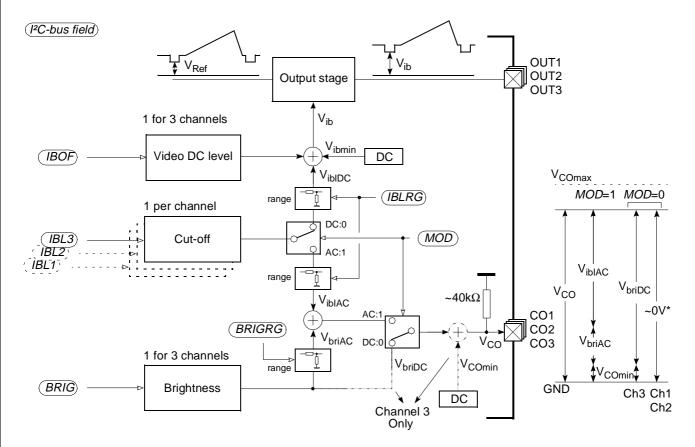

The schematic diagram of these functions is shown in Figure 14.

Figure 14: Cut-off and Brightness Control Block Diagram

Note: Identical for CO1, CO2 and CO3 outputs except for "brightness" ( $V_{briDC}$ ) that is only output at CO3 while MOD=0. The switches are drawn in their default positions.

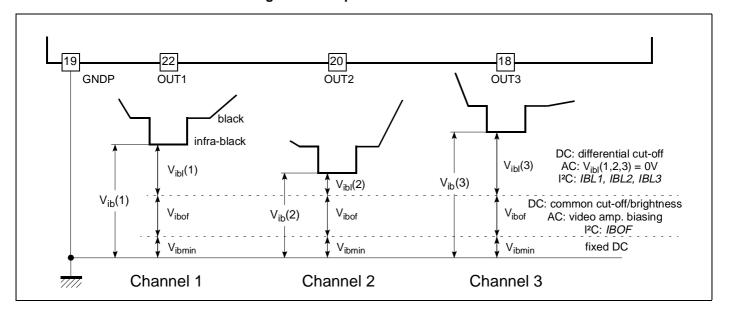

### 2.9.1 Output Infra-black Level

The infra-black level of the video signal at the video outputs OUT1, OUT2 and OUT3 is positioned to the  $V_{ib}$  reference by the output clamp circuit, thus defining the Output infra-black level. If the output clamp circuit is furnished with a correctly timed OCP (see corresponding sections), the output infra-black level equals  $V_{ib}$ .  $V_{ib}$  is composed of a fixed DC voltage ( $V_{ibmin}$ ), a variable DC voltage ( $V_{ibof}$ ) applied on all three channels and a per-channel variable DC voltage ( $V_{ibl}$  (1,2,3)) as shown in Figure 15. In AC-coupling mode (bit MOD = 1), the  $V_{ibl}$  part is suppressed and the  $V_{ib}$  is therefore equal on all three channels, only varying with bits IBOF[5:0] acting on  $V_{ibof}$ . This can be used to match the device's outputs to the input of the video amplifier used (biasing). In DC-coupling mode (bit MOD = 0),  $V_{ibl}$  (1,2,3) are separately set via bits IBL1[7:0], IBL2[7:0] and IBL3[7:0], respectively. This serves to adjust the cut-off points of the three CRT cathodes. In this case,  $V_{ibof}$  can serve to pre-position the cut-off ranges in the factory adjustment procedure or/and to provide a rough brightness control.

<sup>\* ~0</sup>V when the output is left open

Figure 15: Output Infra-black Level

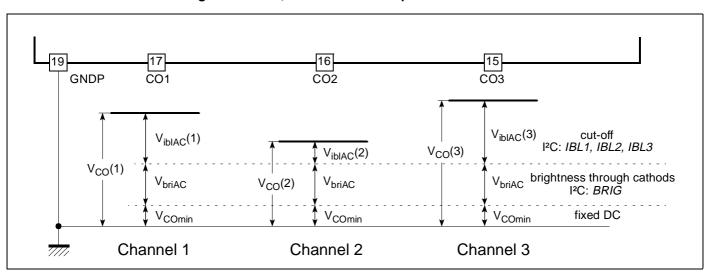

## 2.9.2 Cut-off and Brightness Control Outputs

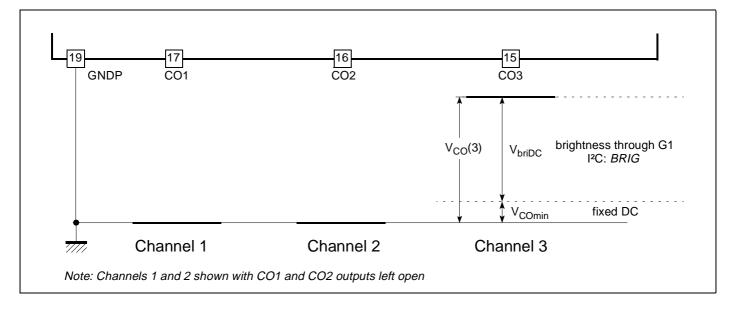

Outputs CO1, CO2 and CO3 provide a DC voltage controlled via bits BRIG[7:0], IBLx[7:0], IBLRG[7:0], BRIGRG[1:0] and MOD[7:0]. The principal of operation is shown in Figure 14.

When bit MOD is in position AC (= 1), the output voltage is a sum of the "brightness"  $V_{briAC}$ , "cut-off"  $V_{iblAC}$  and a fixed  $V_{COmin}$  providing a bottom limitation. The brightness adjustment is equally applied to all three CO1, CO2 and CO3 outputs. It varies depending on bits BRIG[7:0] and BRIGRG[1:0], with bits BRIGRG[1:0] controlling the range of BRIG adjustment. The cut-off adjustment is separate for each channel, having one I<sup>2</sup>C-bus field per channel: IBL1, IBL2 and IBL3. The ratio between the brightness and cut-off ranges depends on the brightness range selection. See Figure 16.

Figure 16: CO1, CO2 and CO3 Outputs while MOD = 1

When bit MOD is in position DC (= 0), the output voltage on CO3 output is a sum of the "brightness"  $V_{briDC}$  and a fixed  $V_{COmin}$  providing a pedestal. Outputs CO1 and CO2 are floating with internal

resistors of approximately 40 k $\Omega$  to ground. The V<sub>briDC</sub> varies with bits *BRIG[7:0]* and does not depend on bits *BRIGRG[1:0]*. See Figure 17.

Figure 17: CO1, CO2 and CO3 Outputs while MOD = 0

# 2.10 Signal Waveforms

Figure 18 gives a summary of main signals waveforms.

Services of the services of th

Figure 18: Signal Waveforms

## 2.11 Miscellaneous

### 2.11.1 Stand-by Mode

The device is set in Stand-by mode either by means of bit PASTBY or by lowering the  $V_{CCP}$  supply voltage below the  $V_{CCPS}$  threshold. Once in Stand-by mode, the device does not process the video signal and its power consumption is significantly reduced. The  $I^2C$ -bus interface remains operational. A low level is forced on the AMPCTL output. Refer to Section 4: Electrical Specifications for values.

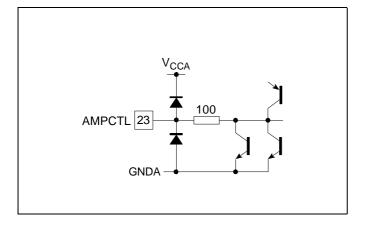

### 2.11.2 AMPCTL Output

The AMPCTL is designed to control a video power amplifier. It provides a three-level logical signal that depends on bits *ASTBY* and *ABLEN*, as well as on the operating mode (stand-by / normal) of the device. Figure 19 gives all possible states of the AMPCTL output. Refer to Section 4: Electrical Specifications for electrical parameter values. Pin AMPCTL is of push-pull type. It must not directly

be grounded in the application and it can be left floating. Only video amplifiers provided with an appropriate control input can take advantage of the signal on the AMPCTL output.

Figure 19: AMPCTL Output States

# 3 I<sup>2</sup>C-Bus Interface Specifications

The device is compatible to general I<sup>2</sup>C-bus specification. Its slave write address is DCh. Subaddress (Sad) auto-incrementing is not available. Only Write mode is supported. The control register map is given in Table 4.

**Bold** weight denotes default values assumed at power-on reset. The power-on reset is effected every time that the supply voltage on VCCA pin drops below V<sub>PORTH</sub> threshold (Refer to electrical specifications).

In order to ensure compatibility with future devices, all "Reserved" bits are to be set to 0 once uploaded by the control software.

Table 4: I<sup>2</sup>C-Bus Register Map

| Sad | b7                       | b6                                 | b5                 | b4                        | b3       | b2                   | b1                    | b0                       |

|-----|--------------------------|------------------------------------|--------------------|---------------------------|----------|----------------------|-----------------------|--------------------------|

| 04  |                          |                                    |                    | CRST                      |          | <u> </u>             |                       | Reserved                 |

| 01  | 1                        | 0                                  | 0                  | 0                         | 0        | 0                    | 0                     | 0                        |

| 02  |                          |                                    |                    | BR                        | RIG      | l                    |                       |                          |

| UZ  | 1                        | 0                                  | 0                  | 0                         | 0        | 0                    | 0                     | 0                        |

| 03  |                          |                                    |                    | DRIVE1                    |          |                      |                       | Reserved                 |

| 03  | 1                        | 0                                  | 0                  | 0                         | 0        | 0                    | 0                     | 0                        |

| 04  |                          |                                    |                    | DRIVE2                    |          |                      |                       | Reserved                 |

| 04  | 1                        | 0                                  | 0                  | 0                         | 0        | 0                    | 0                     | 0                        |

| 05  |                          |                                    |                    | DRIVE3                    |          |                      |                       | Reserved                 |

| 00  | 1                        | 0                                  | 0                  | 0                         | 0        | 0                    | 0                     | 0                        |

| 06  |                          |                                    |                    | erved                     |          |                      | BRI                   | GRG                      |

|     | 0                        | 0                                  | 0                  | 0                         | 0        | 0                    | 0                     | 1                        |

| 07  |                          | Rese                               |                    |                           |          |                      | CRST                  |                          |

|     | 0                        | 0                                  | 0                  | 0                         | 1        | 0                    | 0                     | 1                        |

|     | OCPTG                    | TST1                               | TST0               | BCSC1                     | ВСИ      | /DTH                 | BCEDGE                | BCSC0                    |

| 08  | 0:BLK<br>1:ICP           | 0:Normal<br>1:Test                 | 0:Normal<br>1:Test | 0:Trig mode<br>1:HS pulse | 0        | 1                    | 0:Rising<br>1:Falling | 0:HS trig<br>1:BLK trig  |

|     | ASTBY                    | ABLEN                              | Reserved           | TST2                      | Reserved | MOD                  | SWBLK                 | BLKPOL                   |

| 09  | 0:Normal<br>1:Standby    | <b>0</b> :Bl. disable 1:Bl. enable | 0                  | 0:Test<br>1:Normal        | 0        | <b>0</b> :DC<br>1:AC | 0:Disable<br>1:Enable | 0:Non-inv.<br>1:Inverted |

| 0A  |                          |                                    |                    | IB                        | L1       |                      |                       |                          |

| UA  | 1                        | 0                                  | 0                  | 0                         | 0        | 0                    | 0                     | 0                        |

| 0B  |                          |                                    |                    | IB                        | L2       |                      |                       |                          |

| VD. | 1                        | 0                                  | 0                  | 0                         | 0        | 0                    | 0                     | 0                        |

| 0C  |                          |                                    |                    | IB                        | L3       |                      |                       |                          |

| 00  | 1                        | 0                                  | 0                  | 0                         | 0        | 0                    | 0                     | 0                        |

|     | PASTBY                   | Reserved                           | TST4               | TST3                      |          | В                    | W                     |                          |

| 0D  | 0:Normal                 | 0                                  | 0:Normal           | <b>0</b> :Normal          | 1        | 0                    | 0                     | 0                        |

|     | 1:Standby                |                                    | 1:Test             | 1:Test                    | -        |                      |                       |                          |

|     | VIP                      |                                    |                    | IB                        | OF       | ı                    |                       | IBLRG                    |

| 0E  | 0:0.2V<br><b>1</b> :0.4V | 1                                  | 0                  | 0                         | 0        | 0                    | 0                     | 0:Wide<br>1:Narrow       |

|     | PBGEN                    | PBINS                              |                    |                           |          |                      | BRIG                  |                          |

| 0F  | 0:Disable<br>1:Enable    | 0:PB Pin<br>1:Perman.              | 0                  | 0                         | 1        | 0                    | 0                     | 1                        |

|     | PBVIVEN                  | PBV                                | IVAM               | Reserved                  |          | PBVIVTC              |                       | Reserved                 |

| 10  | 0:Disable<br>1:Enable    | 0                                  | 1                  | 0                         | 1        | 0                    | 0                     | 0                        |

# 3.1 I<sup>2</sup>C-bus Register Descriptions

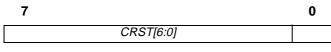

Sad01

Read/Write

Reset Value: 1000 0000 (80h)

Values 00 and 7Fh in field *CRST[6:0]* are prohibited.

Bits[7:1] = Contrast Adjustment (CRST)

Bit 0 = Reserved

### Sad02

Read/Write

Reset Value: 1000 0000 (80h)

7 **0**BRIG[7:0]

Bits[7:0] = Brightness Adjustment (BRIG)

In AC mode, this value is added to infrablack levels and output on pins CO1, CO2 and CO3.

In DC mode, it is output all alone on pin CO3.

## Sad03

Read/Write

Reset Value: 1000 0000 (80h)

| 7           | 0 |

|-------------|---|

| DRIVE1[6:0] |   |

Values 00 and 7Fh in field *DRIVE1[6:0]* are prohibited.

Bits[7:1] = Gain Adjustment on Channel 1 (DRIVE1)

Bit 0 = Reserved

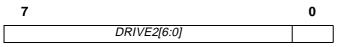

#### Sad04

Read/Write

Reset Value: 1000 0000 (80h)

Values 00 and 7Fh in field *DRIVE2[6:0]* are prohibited.

Bits[7:1] = Gain Adjustment on Channel 2 (DRIVE2)

Bit 0 = Reserved

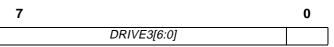

### Sad05

Read/Write

Reset Value: 1000 0000 (80h)

Values 00 and 7Fh in field *DRIVE3[6:0]* are prohibited.

Bits[7:1] = Gain Adjustment on Channel 3 (DRIVE3)

Bit 0 = Reserved.

### Sad06

Read/Write

Reset Value: 0000 0001 (01h)

| 7 |  |  | 0      |

|---|--|--|--------|

|   |  |  | BRIGRG |

|   |  |  | [1:0]  |

Bits[7:2] = Reserved.

Bits[1:0]= Brightness Adjustment Range (BRIGRG)

Four positions. See Section 4.4: Dynamic

Electrical Characteristics.

#### Sad07

Read/Write

Reset Value: 0000 1001 (09h)

| 7 |  |              | 0 |

|---|--|--------------|---|

|   |  | OSDCRST[3:0] |   |

Bits[7:4] = Reserved.

Bits[3:0]= OSD Contrast Adjustment

#### Sad08

Read/Write

Reset Value: 0000 0100 (04h)

| 7    |          |      |             |      | 0    |

|------|----------|------|-------------|------|------|

| OCPT | TST[1:0] | BCSC | BCWDTH[1:0] | BCED | BCSC |

| G    | 131[1.0] | 1    |             | GE   | 0    |

Bit 7 = Output clamping pulse selection

0: Pulse triggered by BLK input (default)

1: Internal ICP pulse

- Bits[6:5] = Test mode activation for device testing in fabrication. When performing software blanking through *SWBLK* bit, *TST1* bit must be set to 1.

- 0: Normal operation mode (Default)

- 1: Test mode

Bits[4,0] = Blanking and clamping pulse source.

| BCSC1 | BCSC0      | Selected Source          |

|-------|------------|--------------------------|

| 0     | 0          | HS pin trigger (Default) |

| 0     | 1          | BLK pin trigger          |

| 1     | Don't care | HS pin pulse             |

Bits[3:2] = Width of ICP pulse when bit BCSC1 is 0.

| ВСИ | /DTH | BCPC Width        |

|-----|------|-------------------|

| 0   | 0    | 0.33 µs           |

| 0   | 1    | 0.66 µs (Default) |

| 1   | 0    | 1 µs              |

| 1   | 1    | 1.33 µs           |

- Bit 1 = When HS pin is selected to trigger the ICP pulse generator.

- 0: Trailing edge of HS pulse (Default)

- 1: Leading edge of HS pulse

When BLK pin is selected to trigger the ICP pulse generator:

| BCEDGE BLKPOL |   | Trigger on BLK        |

|---------------|---|-----------------------|

| 0             | 0 | Rising edge (default) |

| 0             | 1 | Falling edge          |

| 1             | 0 | Falling edge          |

| 1             | 1 | Rising edge           |

Refer to BLKPOL bit description.

### Sad09

Read/Write

Reset Value: 0001 0000 (10h)

| 7    |      |      |     |      | 0    |

|------|------|------|-----|------|------|

| ASTB | ABLE | TST2 | MOD | SWBL | BLKP |

| Y    | N    | 1312 | WOD | K    | OL   |

- Bit 7 = Amplifier standby selection.

- 0: Normal (default)

- 1: Standby

- Bit 6 = Amplifier blanking enable. The bit is "don't care" whenever bit *ASTBY* is in Standby position.

- 0: Blanking pulse not generated (default)

- 1: Blanking pulse generated

- Bit 5 = Reserved.

- Bit 4 = Test mode activation for device testing in fabrication.

- 0: Test mode

- 1: Normal operation mode (Default)

- Bit 3 = Reserved.

- Bit 2 = Application mode selection.

- 0: Application with DC-coupled cathodes. (Default)

- 1: Application with AC-coupled cathodes.

- Bit 1 = Permanent blanking of video channels through software.

- 0: Disable, blanking gated with signal on BLK pin. (Default)

- 1: Permanent blanking. Bit *TST1* must also be set to 1.

- Bit 0 = Blanking signal (H-fly back) polarity inversion. For correct operation, the internal BLKI pulse after this controlled inversion must be positive.

- 0: Non Inverted, good for positive blanking pulse (Default)

- 1: Inverted, good for negative blanking pulse

## Sad0A, Sad0B and Sad0C

Read/Write

Reset Value: 1000 0000 (80h)

| 1         | U |

|-----------|---|

| IBL1[7:0] |   |

| IBL2[7:0] |   |

| IBL3[7:0] |   |

Bits[7:0] = Infra-black (Cut-off) Level Control, Channels 1 to 3 (IBLx)

> In DC-coupling mode, the register controls the pedestal of corresponding video channel signal.

> In AC-coupling mode, the register controls the level on outputs CO1, CO2 or CO3, respectively.

### Sad0D

Read/Write

Reset Value: 0000 1000 (08h)

| 7          |          |         | 0 |

|------------|----------|---------|---|

| PAST<br>BY | TST[4:3] | BW[3:0] |   |

- Bit 7 = Preamplifier and Amplifier STandBY selection

- 0: Normal (default)

- 1: Standby

Bit 6 = Reserved.

Bits[5:4] = Test mode activation bits for device testing in fabrication.

0: Normal operation mode (Default)

1: Test mode

Bits[3:0] = Internal band width limitation control. Refer to electrical characteristics.

#### Sad0E

Read/Write

Reset Value: 1100 0001 (C1h)

7 0 **IBLR** VIP IBOF[5:0] G

Bit 7 = Video Insertion Pulse depth.

0: 0.2V

1: 0.4V (default)

Bits[6:1] = Infra-black level offset control simultaneously on all three video channels.

Bit 0 = Control range of infra-black level adjustments via IBL1, IBL2 and IBL3 registers. Acts either on video signal channels or CO1, CO2, CO3 outputs. Refer to electrical characteristics.

0: Wide

1: Narrow (default)

### Sad0F

Ν

S

Read/Write

Reset Value: 0000 1001 (09h)

7 0 PBGE PBIN PBCRST[1:0] PBBRIG[1:0] Bit 7 = PictureBooST General Enable. (PBGEN)

0: Disable, function inhibited (Default)

1: Enable, function active

Bit 6 = PictureBooST Insertion Control. (PBINS)

0: PB pin insertion (Default)

1: Permanent insertion regardless of signal on PB pin

Bit 5 = Reserved.

Bits[4:3] = PictureBooST Contrast Control (PBCRST)

Bit 2 = Reserved.

Bits[1:0] = PictureBooST Brightness Control (PBBRIG)

### Sad10

Read/Write

Reset Value: 0010 1000 (28h)

7 0 PBVIV PBVIVAM[1:0] PBVIVTC[2:0] ΕN

Bit 7 = PictureBooST vivacity and brightness enable.

0: Disable (default)

1: Enable

Bits[6:5] = PictureBooST Vivacity Amplitude Control.

Bit 4 = Reserved.

Bits[3:1] = PictureBooST Vivacity Time Constant Control.

Bit 0 = Reserved.

# 4 Electrical Specifications

# 4.1 Absolute Maximum Ratings

All voltages refer to the GNDA pin.

| Symbol            | Parameter                                                                              | Min. | Max. | Units |

|-------------------|----------------------------------------------------------------------------------------|------|------|-------|

| $V_{CCA}$         | Supply voltage on VCCA (Pin 7)                                                         |      | 5.5  | V     |

| V <sub>CCP</sub>  | Supply voltage on VCCP (Pin 21)                                                        | TBD  | 8.8  | V     |

| V <sub>IN</sub>   | V <sub>IN</sub> Voltage at any pin except video inputs and supply pins                 |      | 5.5  | V     |

| VI                | Voltage at video inputs (Pins 1,3 and 5)                                               | TBD  | 1.4  | V     |

| V <sub>ESD</sub>  | V <sub>ESD</sub> ESD susceptibility Human Body Model (100 pF discharge through 1.5 kΩ) |      | ±2   | kV    |

| T <sub>STG</sub>  | Storage Temperature                                                                    | -40  | +150 | °C    |

| T <sub>OPER</sub> | Operating Junction Temperature                                                         | -40  | +150 | °C    |

# 4.2 Thermal Data

| Symbol            | Parameter                              | Min. | Тур. | Max. | Units |

|-------------------|----------------------------------------|------|------|------|-------|

| R <sub>thJA</sub> | Junction-to-Ambient Thermal Resistance |      | 60   |      | °C/W  |

| T <sub>AMB</sub>  | Operating Ambient Temperature          | 0    |      | 70   | °C/W  |

## 4.3 Static Electrical Characteristics

$T_{AMB}$  = 25°C,  $V_{CCA}$  = 5V, and  $V_{CCP}$  = 8V, unless otherwise specified. All voltages refer to the GNDA pin.

| Symbol            | Parameter                                  | Test Conditions                                                 | Min.               | Тур.     | Max.                      | Units    |

|-------------------|--------------------------------------------|-----------------------------------------------------------------|--------------------|----------|---------------------------|----------|

| Supply            |                                            | 1                                                               |                    | I        | 1                         |          |

| V <sub>CCA</sub>  | Supply Voltage                             | Pin 7                                                           | 4.5                | 5        | 5.5                       | V        |

| V <sub>CCP</sub>  | Power Stage Supply Voltage                 | Pin 21                                                          | 4.5                | 8        | 8.8                       | V        |

| V <sub>CCPS</sub> | Power Supply Voltage Stand-by<br>Threshold | Pin 21                                                          | 2.5                | 3.0      | 3.5                       | V        |

| I <sub>CCA</sub>  | VCCA Supply Current                        | $V_{CCA} = 5V (PBGEN Disable)$<br>$V_{CCA} = 5V (PBGEN Enable)$ |                    | 65<br>85 |                           | mA<br>mA |

| I <sub>CCP</sub>  | VCCP Supply Current                        | V <sub>CCP</sub> = 8V                                           |                    | 50       |                           | mA       |

| I <sub>S</sub>    | Total Supply Current in Stand-by Mode      | Pin 21 and pin 7                                                |                    |          | 6                         | mA       |

| Inputs and C      | Outputs                                    |                                                                 | 1                  | l.       | JI.                       |          |

| V <sub>I</sub>    | Video Input voltage amplitude              |                                                                 |                    | 0.7      | 1                         | V        |

| V <sub>O</sub>    | Output voltage swing                       |                                                                 | 0.5 <sup>(1)</sup> |          | V <sub>CCP</sub><br>-0.5V | V        |

| $V_{IL}$          | Low level input voltage (TTL)              | OSD, FBLK, PB, HS,BLK                                           |                    |          | 0.8                       | V        |

| $V_{IH}$          | High level input voltage (TTL)             | OSD, FBLK, PB, HS,BLK                                           | 2.4                |          |                           | V        |

| I <sub>IL</sub>   | BLK input current                          | BLK                                                             | -0.1               |          | +1.0                      | mA       |

| I <sub>IN</sub>   | Input current                              | OSD, FBLK, PB                                                   | -1                 |          | 1                         | μΑ       |

| Symbol             | Parameter                                                         | Test Conditions                                                                                                         | Min. | Тур. | Max. | Units |

|--------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| $R_{HS}$           | Input resistance                                                  | HS                                                                                                                      |      | 40   |      | kΩ    |

| V <sub>AMPSB</sub> | Output voltage at AMPCTL pin, standby (Figure 18)                 | I <sup>2</sup> C-bus bit <i>ASTBY</i> = 1 or/and<br>V <sub>CCP</sub> < V <sub>CCPS</sub><br>Sink current 200μA          |      | 80   | 200  | mV    |

| V <sub>AMPBL</sub> | Output voltage at AMPCTL pin, blanking (Figure 18)                | I <sup>2</sup> C-bus bit <i>ASTBY</i> = 1 I <sup>2</sup> C-bus bit <i>ABLEN</i> = 1 Sink current 0μA BLKI at high level | TBD  | 1.6  | TBD  | V     |

| V <sub>AMPHI</sub> | Output voltage at AMPCTL pin, no standby, no blanking (Figure 18) | I <sup>2</sup> C-bus bit <i>ASTBY</i> = 0 and V <sub>CCP</sub> > V <sub>CCPS</sub> Sink current 0μA                     |      | 3.1  |      | V     |

# 4.4 Dynamic Electrical Characteristics

$\rm T_{AMB}$  = 25°C, V\_{CCA} = 5 V, V\_{CCP} = 8 V, V<sub>i</sub> = 0.7 V<sub>PP</sub>, C<sub>LOAD</sub> = 5 pF, R<sub>S</sub> = 100  $\Omega$  serial resistor between output pin and C<sub>LOAD</sub>, unless otherwise specified. "x" denotes channel number and can assume values of 1, 2 and/or 3. All voltages refer to the GNDA pin.

| Symbol               | Parameter                                               | Test Conditions                                                                                               | Min. | Тур.            | Max. | Units       |

|----------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------|-----------------|------|-------------|

| Video Outp           | ut Signal (Pins 18, 20 and 22) - Contr                  | ast and Drive                                                                                                 |      |                 |      |             |

| G                    | Maximum total gain for video path with PictureBooST off | I <sup>2</sup> C-bus fields <i>CRST</i> = 7Eh,<br><i>DRIVEx</i> = 7Eh<br><i>PBGEN</i> = 0                     |      | 12              |      | dB          |

| V <sub>OM</sub>      | Maximum video output voltage <sup>(2)</sup>             | I <sup>2</sup> C-bus fields <i>CRST</i> = 7Eh,<br><i>DRIVEx</i> = 7Eh<br><i>PBGEN</i> = 0<br><i>PBGEN</i> = 1 |      | 2.8<br>4.0      |      | V<br>V      |

| V <sub>ON</sub>      | Nominal video output voltage                            | l <sup>2</sup> C-bus fields <i>CRST</i> = 40h,<br><i>DRIVEx</i> = 40h (POR state)                             |      | TBD             |      | V           |

| CAR                  | Contrast control range                                  | Max. to min. contrast (CRST = 7Eh to CRST = 01h)                                                              |      | 28              |      | dB          |

| DAR                  | Drive control range                                     | Max. to min. drive (DRIVEx = 7Eh to DRIVEx = 01h)                                                             |      | 13              |      | dB          |

| GM                   | Gain matching <sup>(3)</sup>                            | I <sup>2</sup> C-bus fields <i>CRST</i> = 40h,<br><i>DRIVEx</i> = 40h (POR state)                             |      | ±0.1            |      | dB          |

| Video Outp           | ut Signal - OSD                                         | •                                                                                                             |      |                 |      |             |

| V <sub>OSD</sub>     | OSD insertion output level                              | referenced to output black level  DRIVEx = 7Eh  OSDCRST = 0Fh  OSDCRST = 0h                                   |      | 4.9<br>0        |      | V<br>V      |

| Video Outp           | ut Signal - VIP                                         |                                                                                                               | •    | •               |      |             |

| V <sub>VIP</sub>     | Video Insertion Pulse level                             | From Infrablack level to black level $VIP = 1$<br>VIP = 0 <sup>(4)</sup>                                      |      | 0.4<br>0.2      |      | Vpp<br>Vpp  |

| Video Outp           | ut Signal - Infra Black Level (Figure 1                 | 5)                                                                                                            |      |                 |      |             |

| V <sub>ibmin</sub>   | Infra black level pedestal                              |                                                                                                               |      | 0.4             |      | V           |

| V <sub>ibof</sub>    | Infra black offset component                            | IBOF = 3Fh<br>IBOF = 0h                                                                                       |      | 2.1<br>0        |      | V<br>V      |

| V <sub>ibl</sub> [x] | Infra black level component                             | IBLx = 0h or MOD = 1 (AC mode) IBLx = FFh, MOD = 0 (DC mode) IBLRG = 1 IBLRG = 0                              |      | 0<br>1.3<br>1.8 |      | V<br>V<br>V |

**477**

| Symbol                          | Parameter                                                                                            | Test Conditions                                                                                   | Min. | Тур.                           | Max.     | Units                |

|---------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------|--------------------------------|----------|----------------------|

| Cut-off Out                     | put (Pins CO1, CO2 and CO3)                                                                          |                                                                                                   |      | ı                              |          |                      |

| V <sub>COmin</sub>              | Pedestal level on COx outputs                                                                        |                                                                                                   |      | 0.5                            |          | V                    |

| V <sub>COmax</sub>              | Upper limitation on COx outputs                                                                      | Sum of V <sub>briAC</sub> +V <sub>ibIAC</sub> or V <sub>briDC</sub> exceeding the limit           |      | V <sub>CCA</sub><br>-0.5V      |          | V                    |

| $V_{briAC}$                     | Brightness component in AC mode (Figure 16)                                                          | MOD = 1 (AC mode)  BRIG = 0h  BRIG = FFh:  BRIGRG = 00b  BRIGRG = 01b  BRIGRG = 10b  BRIGRG = 11b |      | 0<br>0.4<br>0.8<br>1.25<br>1.9 |          | V<br>V<br>V<br>V     |

| V <sub>briDC</sub>              | Brightness component in DC mode on CO3 pin <sup>(6)</sup> (Figure 17)                                | MOD = 0 (DC mode)<br>BRIG = 0h<br>BRIG = FFh                                                      |      | 0<br>4                         |          | V<br>V               |

| V <sub>iblAC</sub> (x)          | Cut-off component                                                                                    | MOD = 0 (DC mode)<br>MOD = 1 (AC mode)<br>IBLx = 0h<br>IBLx = FFh:<br>IBLRG = 0<br>IBLRG = 1      |      | 0<br>0<br>3.7<br>1.85          |          | V<br>V<br>V          |

| PictureBoo                      | ST™ Block (Figure 9)                                                                                 |                                                                                                   |      | •                              |          |                      |

| G <sub>PB</sub>                 | Maximum gain                                                                                         | PBGEN = 1 PBCRST = 00b PBCRST = 01b PBCRST = 10b PBCRST = 11b                                     |      | 0.8<br>1.6<br>2.3<br>3         |          | dB<br>dB<br>dB<br>dB |

| $V_{BriPB}$                     | PictureBooST brightness expressed in equivalent input level                                          | PBGEN = 1 and PBVIVEN = 1 PBBRIG = 00b PBBRIG = 01b PBBRIG = 10b PBBRIG = 11b                     |      | 64<br>48<br>32<br>16           |          | mV<br>mV<br>mV       |

| V <sub>viv</sub> /A             | Vivacity amplitude as percentage of its host square pulse level before PictureBooST("A" in Figure 9) | PBGEN = 1 and PBVIVEN = 1 PBVIVAM = 00b PBVIVAM = 01b PBVIVAM = 10b PBVIVAM = 11b                 |      | 12.5<br>25<br>37.5<br>50       |          | %<br>%<br>%<br>%     |

| $	au_{viv}$                     | Vivacity time constant                                                                               | PBGEN = 1 and PBVIVEN = 1 PBVIVTC = 000b PBVIVTC = 001b PBVIVTC = 111b                            |      | 0<br>35<br>245                 |          | ns<br>ns<br>ns       |

| ABL (Figure                     | 9)                                                                                                   |                                                                                                   | •    |                                |          |                      |

| G <sub>ABL</sub>                | ABL gain                                                                                             | V <sub>ABL</sub> >3.2 V<br>V <sub>ABL</sub> = 1 V                                                 |      | 0<br>-15                       |          | dB<br>dB             |

| V <sub>ThABL</sub>              | ABL threshold voltage                                                                                |                                                                                                   |      | 3                              |          | V                    |

| I <sub>ABL</sub>                | ABL input current                                                                                    | V <sub>ABL</sub> = 3.2V<br>V <sub>ABL</sub> = 1V                                                  |      | 0<br>-2                        |          | μA<br>μA             |

| Video Outp                      | ut Signal - Dynamic Performances (F                                                                  |                                                                                                   | 1    | 1                              | <u>I</u> | <u> </u>             |

| t <sub>r</sub> , t <sub>f</sub> | Rise Time, Fall Time <sup>(5)</sup>                                                                  | $V_{OUT} = 2V_{PP}$ (VIP exclusive)<br>BW = 0Fh<br>BW = 00h                                       |      | 3.5<br>7                       |          | ns<br>ns             |

| BW                              | Large signal bandwidth                                                                               | $V_{OUT} = 2V_{PP}$ , sinus wave, -3dB<br>BW = 0Fh<br>BW = 00h                                    |      | TBD<br>TBD                     |          | MHz<br>MHz           |

| Symbol | Parameter                       | Test Conditions                                                 | Min. | Тур.       | Max. | Units    |

|--------|---------------------------------|-----------------------------------------------------------------|------|------------|------|----------|

| СТ     | Crosstalk between Video Outputs | V <sub>OUT</sub> = 2V <sub>PP</sub><br>f = 10 MHz<br>f = 50 MHz |      | TBD<br>TBD |      | dB<br>dB |

# 4.5 I<sup>2</sup>C-Bus Electrical Characteristics

$$T_{amb} = 25^{\circ} \text{ C}, V_{CCA} = 5 \text{ V}, V_{CCP} = 8 \text{ V}, V_{i} = 0.7 \text{ V}_{PP}, C_{LOAD} = 5 \text{ pF}$$

| Symbol                 | Parameter                     | Test Conditions                      | Min. | Тур. | Max. | Unit<br>s |

|------------------------|-------------------------------|--------------------------------------|------|------|------|-----------|

| V <sub>IL</sub>        | Low Level Input Voltage       | On Pins SDA, SCL                     |      |      | 1.5  | V         |

| V <sub>IH</sub>        | High Level Input Voltage      |                                      | 3    |      |      | V         |

| I <sub>IN</sub>        | Input Current (Pins SDA, SCL) | 0.4 V < V <sub>IN</sub> < 4.5 V      | -10  |      | +10  | μΑ        |

| f <sub>SCL(Max.)</sub> | SCL Maximum Clock Frequency   |                                      |      | 200  |      | kHz       |

| V <sub>OL</sub>        | Low Level Output Voltage      | SDA pin when ACK Sink Current = 6 mA |      |      | 0.6  | V         |

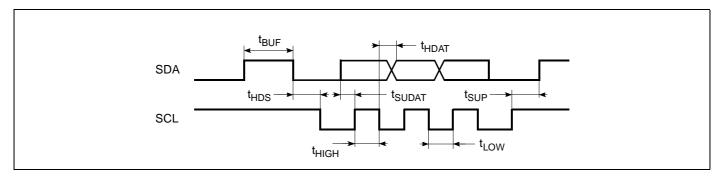

# 4.6 I<sup>2</sup>C-Bus Interface Timing Requirements

| Symbol             | Parameter                                      | Min. | Тур. | Max. | Units |

|--------------------|------------------------------------------------|------|------|------|-------|

| t <sub>BUF</sub>   | Time the bus must be free between two accesses | 1300 |      |      | ns    |

| t <sub>HDS</sub>   | Hold Time for Start Condition                  |      |      |      | ns    |

| t <sub>SUP</sub>   | Set-up Time for Stop Condition                 | 600  |      |      | ns    |

| t <sub>LOW</sub>   | The Low Period of Clock                        | 1300 |      |      | ns    |

| t <sub>HIGH</sub>  | The High Period of Clock                       | 600  |      |      | ns    |

| t <sub>HDAT</sub>  | Hold Time Data                                 | 300  |      |      | ns    |

| t <sub>SUDAT</sub> | Set-up Time Data                               | 250  |      |      | ns    |

| t <sub>r</sub>     | Rise Time of both SDA and SCL                  |      |      | 1    | μs    |

| t <sub>f</sub>     | t <sub>f</sub> Fall Time of both SDA and SCL   |      |      | 300  | ns    |

Figure 20: I<sup>2</sup>C-Bus Timing Diagram

## **Notes on Electrical Characteristics**

- Note 1. The video on the preamplifier output must remain above 0.5V even for high frequency signals.

- 2. Assuming that the video output signal remains inside the linear area of the preamplifier output (between 0.5V and  $V_{CCP}$  0.5V).

**57**

- 3. Matching measured between the different outputs.

- 4. When the Blanking signal is present on the BLK input, the VIP insertion pulse is always generated. Only its amplitude changes (see Figure 12).

- 5.  $t_R$ ,  $t_F$  are simulated values, assuming an ideal input signal with rise/fall time = 0.1 ns. Measured between 10% and 90% of the pulse height.

- 6. When MOD = 0, the CO1 and CO2 are internally grounded through resistors.

# 5 Soldering Information

The device can be soldered by wave, dipping or manually. Wave soldering is the preferred method for mounting through-hole mount IC packages on a printed-circuit board.

## Soldering by dipping or by solder wave

The maximum permissible temperature of the solder is 260 °C; solder at this temperature must not be in contact with the joints for more than 5 seconds. The total contact time of successive solder waves must not exceed 5 seconds. The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified maximum storage temperature  $(T_{STG}[max])$ . If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit.

## Manual soldering

Apply the soldering iron (24 V or less) to the lead(s) of the package, either below the seating plane or not more than 2 mm above it. If the temperature of the soldering iron bit is less than 300 °C it may remain in contact for up to 10 seconds. If the bit temperature is between 300 and 400 °C, contact may last up to 5 seconds.

# 6 Package Mechanical Data

A1 A2 A

A1 A2 A

B1

C Stand-off

D 0.015 in.

O.33 mm.

Gage Plane

eB

Figure 21: 24-Pin Plastic Dual In-Line Package, Shrink 300-mil Width

**Table 5: Package Dimensions**

| Dim. | Millimeters |       |       | Inches    |       |       |  |

|------|-------------|-------|-------|-----------|-------|-------|--|

|      | Min.        | Тур.  | Max.  | Min.      | Тур.  | Max.  |  |

| А    |             |       | 5.08  |           |       | 0.200 |  |

| A1   | 0.51        |       |       | 0.020     |       |       |  |

| A2   | 3.05        | 3.30  | 4.57  | 0.120     | 0.130 | 0.180 |  |

| b    | 0.38        | 0.46  | 0.56  | 0.015     | 0.018 | 0.022 |  |

| b2   | 0.89        | 1.02  | 1.14  | 0.035     | 0.040 | 0.045 |  |

| С    | 0.23        | 0.25  | 0.38  | 0.009     | 0.010 | 0.015 |  |

| D    | 22.35       | 22.61 | 22.86 | 0.880     | 0.890 | 0.900 |  |

| Е    | 7.62        |       | 8.64  | 0.300     |       | 0.340 |  |

| E1   | 6.10        | 6.40  | 6.86  | 0.240     | 0.252 | 0.270 |  |

| е    |             | 1.78  |       |           | 0.070 |       |  |

| eA   |             | 7.62  |       |           | 0.300 |       |  |

| eВ   |             |       | 10.92 |           |       | 0.430 |  |

| еC   | 0.00        |       | 1.52  | 0.000     |       | 0.060 |  |

| L    | 2.54        | 3.30  | 3.81  | 0.100     | 0.130 | 0.150 |  |

|      |             | •     | Numbe | r of Pins |       |       |  |

| N    |             | 24    |       |           |       |       |  |

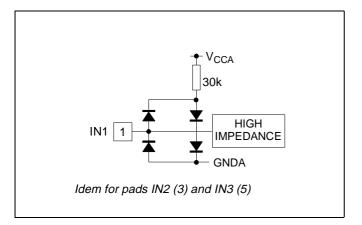

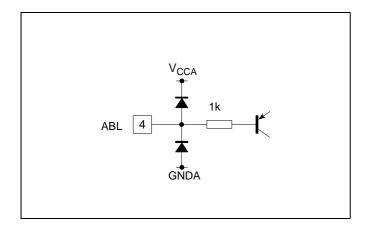

# 7 Input/Output Diagrams

Figure 22: Video Inputs

Figure 23: ABL Input

Figure 24: Amplifier Control Output

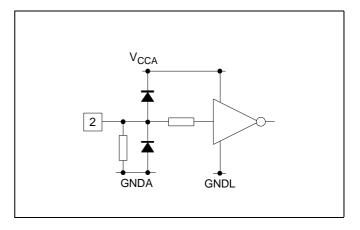

Figure 25: Hsync Input

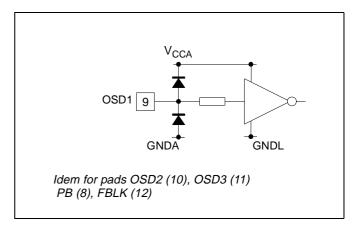

Figure 26: PictureBooST and OSD Inputs

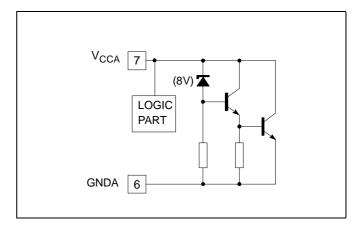

Figure 27: Analog Supplies

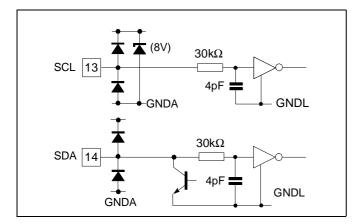

Figure 28: I<sup>2</sup>C-Bus

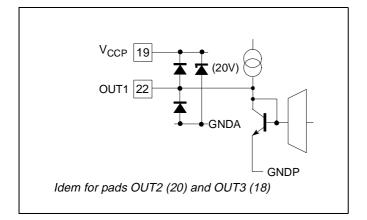

Figure 29: Output Stage Supply and Video Outputs

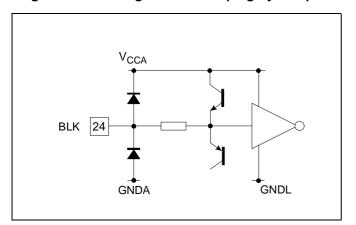

Figure 30: Blanking / Video Clamping Sync Inputs

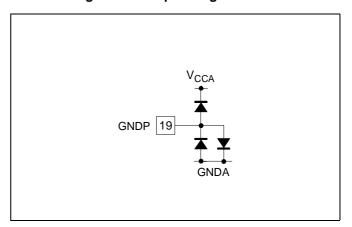

Figure 31: Output Stage Ground

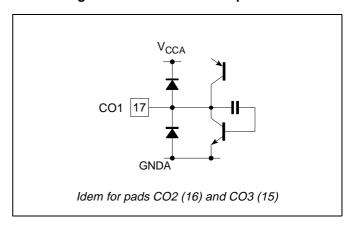

Figure 32: Cut-off DAC Output Pins

STV9212 Revision History

# **8 Revision History**

**Table 6: Summary of Modifications**

| Version | Date        | Description          |

|---------|-------------|----------------------|

| 1.0     | 14 Nov 2002 | First Issue          |

| 1.1     | 03 Jul 2003 | Minor modifications. |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

© 2003 STMicroelectronics - All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

www.st.com