# 1.0 A Adjustable Linear Regulator

The CS5201–1 linear regulator provides 1.0 A with an output voltage accuracy of  $\pm 1.0$  %. The device uses two external resistors to set the output voltage within a 1.25 V to 5.5 V range.

This regulator is intended for use as a post regulator and microprocessor supply. The fast loop response and low dropout voltage make this regulator ideal for applications where low voltage operation and good transient response are important.

The circuit is designed to operate with dropout voltages less than 1.2 V at 1.0 A output current. Device protection includes overcurrent and thermal shutdown.

The CS5201 is pin compatible with the LT1086 family of linear regulators.

The regulator is available in TO-220, surface mount D<sup>2</sup>, and SOT-223 packages.

### **Features**

- Output Current to 1.0 A

- Output Accuracy to ±1.0% Over Temperature

- Dropout Voltage (typical) 1.0 V @ 1.0 A

- Fast Transient Response

- Fault Protection

- Current Limit

- Thermal Shutdown

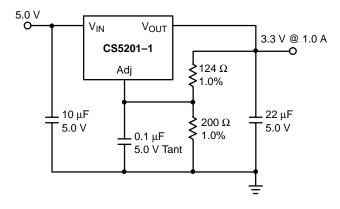

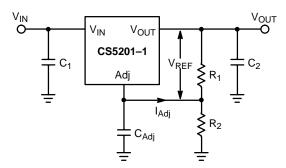

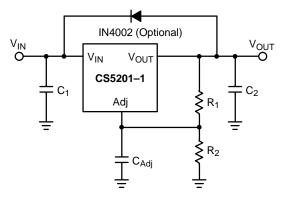

Figure 1. Applications Diagram

### ON Semiconductor®

http://onsemi.com

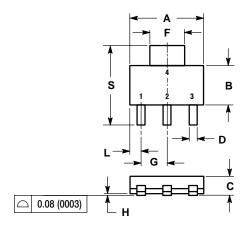

D<sup>2</sup>PAK 3-PIN DP SUFFIX CASE 418E

Tab = V<sub>OUT</sub> Pin 1. Adj 2. V<sub>OUT</sub> 3. V<sub>IN</sub>

SOT-223 ST SUFFIX

### **ORDERING INFORMATION\*†**

**CASE 318E**

| Device        | Package             | Shipping         |

|---------------|---------------------|------------------|

| CS5201-1GT3   | TO-220‡             | 50 Units/Rail    |

| CS5201-1GDP3  | D <sup>2</sup> PAK‡ | 50 Units/Rail    |

| CS5201-1GDPR3 | D <sup>2</sup> PAK‡ | 750 Tape & Reel  |

| CS5201-1GST3  | SOT-223‡            | 80 Units/Rail    |

| CS5201-1GSTR3 | SOT-223‡            | 2500 Tape & Reel |

- \*Additional ordering information can be found on page 7 of this data sheet.

- †Consult your local sales representative for fixed output voltage versions.

- ‡TO-220 are all 3-pin, straight leaded. D<sup>2</sup>PAK and SOT-223 are all 3-pin.

### **DEVICE MARKING INFORMATION**

See general marking information in the device marking section on page 7 of this data sheet.

### CS5201-1

### **MAXIMUM RATINGS\***

| Parameter                               |                                                                                  |                      | Unit     |

|-----------------------------------------|----------------------------------------------------------------------------------|----------------------|----------|

| Supply Voltage, V <sub>CC</sub>         |                                                                                  | 7.0                  | V        |

| Operating Temperature Range             |                                                                                  | -40 to +70           | °C       |

| Junction Temperature                    |                                                                                  | 150                  | °C       |

| Storage Temperature Range               |                                                                                  | -60 to +150          | °C       |

| Lead Temperature Soldering:             | Wave Solder (through hole styles only) Note 1<br>Reflow (SMD styles only) Note 2 | 260 Peak<br>230 Peak | °C<br>°C |

| ESD Damage Threshold (Human Body Model) |                                                                                  | 2.0                  | kV       |

- 1. 10 second maximum.

- 2. 60 second maximum above 183°C

### $\textbf{ELECTRICAL CHARACTERISTICS} \ (C_{IN} = 10 \ \mu\text{F}, \ C_{OUT} = 22 \ \mu\text{F} \ \text{Tantalum}, \ V_{OUT} + V_{DROPOUT} < V_{IN} < 7.0 \ \text{V}, \ 0^{\circ}\text{C} \leq T_{A} \leq 70^{\circ}\text{C}, \ \text{C} = 10 \ \text{C} = 10$ $T_J \le +150$ °C, unless otherwise specified, $I_{full\ load} = 1.0 \text{ A}$ )

| Characteristic                       | Test Conditions                                                                                                                | Min              | Тур   | Max              | Unit |  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------|-------|------------------|------|--|

| Adjustable Output Voltage            |                                                                                                                                |                  |       |                  |      |  |

| Reference Voltage (Notes 3 and 4)    | $V_{IN} - V_{OUT} = 1.5 \text{ V}; V_{Adj} = 0 \text{ V}$<br>10 mA $\leq I_{OUT} \leq 1.0 \text{ A}$                           | 1.241<br>(-1.0%) | 1.254 | 1.266<br>(+1.0%) | V    |  |

| Line Regulation                      | $1.5 \text{ V} \le \text{V}_{\text{IN}} - \text{V}_{\text{OUT}} \le 5.75 \text{ V}; \text{I}_{\text{OUT}} = 10 \text{ mA}$     | -                | 0.02  | 0.20             | %    |  |

| Load Regulation (Notes 3 and 4)      | $V_{IN} - V_{OUT} = 1.5 \text{ V}; 10 \text{ mA} \le I_{OUT} \le 1.0 \text{ A}$                                                | _                | 0.04  | 0.40             | %    |  |

| Dropout Voltage (Note 5)             | I <sub>OUT</sub> = 1.0 A                                                                                                       | -                | 1.0   | 1.2              | V    |  |

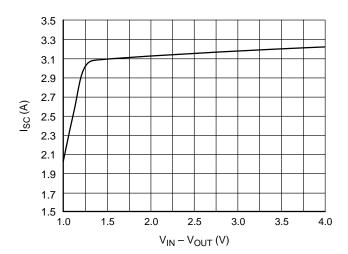

| Current Limit                        | $V_{IN} - V_{OUT} = 3.0 \text{ V}; T_J \ge 25^{\circ}\text{C}$                                                                 | 1.1              | 3.1   | -                | Α    |  |

| Minimum Load Current (Note 6)        | V <sub>IN</sub> = 7.0 V, V <sub>Adj</sub> = 0 V                                                                                | -                | 0.6   | 2.0              | mA   |  |

| Adjust Pin Current                   | $V_{IN} - V_{OUT} = 3.0 \text{ V}; I_{OUT} = 10 \text{ mA}$                                                                    | _                | 50    | 100              | μА   |  |

| Thermal Regulation (Note 7)          | 30 ms Pulse, T <sub>A</sub> = 25°C                                                                                             | -                | 0.002 | 0.020            | %/W  |  |

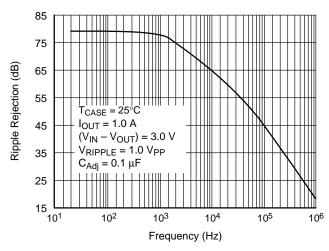

| Ripple Rejection (Note 7)            | f = 120 Hz; I <sub>OUT</sub> = 1.0 A; V <sub>IN</sub> – V <sub>OUT</sub> = 3.0 V;<br>V <sub>RIPPLE</sub> = 1.0 V <sub>PP</sub> | _                | 80    | _                | dB   |  |

| Thermal Shutdown (Note 8)            | -                                                                                                                              | 150              | 180   | 210              | °C   |  |

| Thermal Shutdown Hysteresis (Note 8) | -                                                                                                                              | _                | 25    | _                | °C   |  |

- 3. Load regulation and output voltage are measured at a constant junction temperature by low duty cycle pulse testing. Changes in output voltage due to temperature changes must be taken into account seperately.

- 4. Specifications apply for an external Kelvin sense connection at a point on the output pin 1/4" from the bottom of the package.

- Dropout voltage is a measurement of the minimum input/output differential at full load.

The minimum load current is the minimum current required to maintain regulation. Normally the current in the resistor divider used to set the output voltage is selected to meet the minimum load requirement.

- Guaranteed by design, not 100% tested in production.

- 8. Thermal shutdown is 100% functionally tested in production.

### **PACKAGE PIN DESCRIPTION**

| Pack   | age Pin Nu         | mber    |                  |                                                  |  |

|--------|--------------------|---------|------------------|--------------------------------------------------|--|

| TO-220 | D <sup>2</sup> PAK | SOT-223 | Pin Symbol       | Function                                         |  |

| 1      | 1                  | 1       | Adj              | Adjust pin (low side of the internal reference). |  |

| 2      | 2                  | 2       | V <sub>OUT</sub> | Regulated output voltage (case).                 |  |

| 3      | 3                  | 3       | V <sub>IN</sub>  | Input voltage.                                   |  |

<sup>\*</sup>The maximum package power dissipation must be observed.

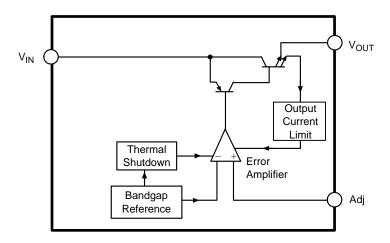

Figure 2. Block Diagram

### TYPICAL PERFORMANCE CHARACTERISTICS

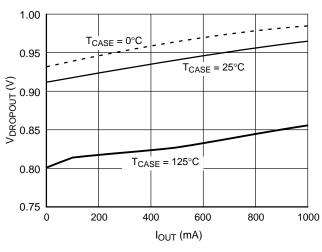

Figure 3. Dropout Voltage vs. Output Current

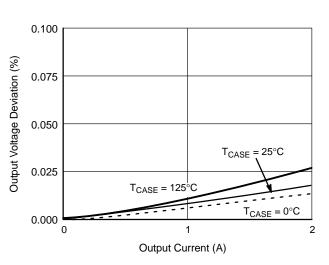

Figure 5. Load Regulation vs. Output Current

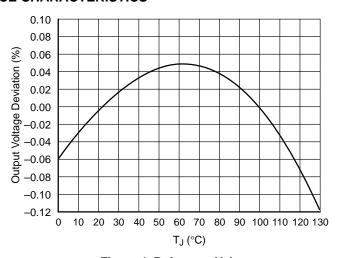

Figure 4. Reference Voltage vs. Temperature

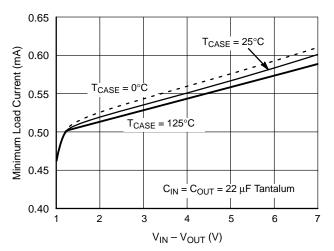

Figure 6. Minimum Load Current vs.  $V_{\text{IN}} - V_{\text{OUT}}$

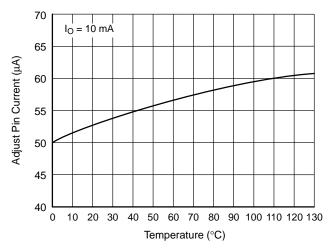

Figure 7. Adjust Pin Current vs. Temperature

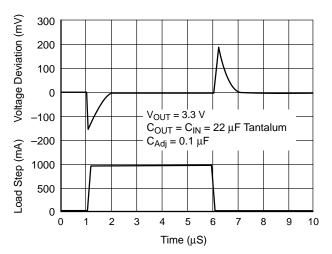

Figure 9. Transient Response

Figure 8. Ripple Rejection vs. Frequency

Figure 10. Short Circuit Current vs.  $V_{IN} - V_{OUT}$

### **APPLICATIONS INFORMATION**

The CS5201–1 linear regulator provides adjustable voltages at currents up to 1.0 A. The regulator is protected against overcurrent conditions and includes thermal shutdown.

The CS5201–1 has a composite PNP–NPN output transistor and requires an output capacitor for stability. A detailed procedure for selecting this capacitor is included in the Stability Considerations section.

### **Adjustable Operation**

The CS5201–1 has an output voltage range of 1.25 V to 5.5 V. An external resistor divider sets the output voltage as shown in Figure 11. The regulator maintains a fixed 1.25V (typical) reference between the output pin and the adjust pin.

A resistor divider network R1 and R2 causes a fixed current to flow to ground. This current creates a voltage across R2 that adds to the 1.25 V across R1 and sets the overall output voltage. The adjust pin current (typically 50  $\mu$ A) also flows through R2 and adds a small error that should be taken into account if precise adjustment of  $V_{OUT}$  is necessary.

The output voltage is set according to the formula:

$$V_{OUT} = V_{REF} \times \left(\frac{R1 + R2}{R1}\right) + I_{Adj} \times R2$$

The term  $I_{Adj} \times R2$  represents the error added by the adjust pin current.

R1 is chosen so that the minimum load current is at least 2.0 mA. R1 and R2 should be the same type, e.g. metal film for best tracking over temperature. While not required, a bypass capacitor from the adjust pin to ground will improve ripple rejection and transient response. A 0.1  $\mu$ F tantalum capacitor is recommended for "first cut" design. Type and value may be varied to obtain optimum performance vs. price.

Figure 11. Resistor Divider Scheme

### **Short Circuit Protection**

The CS5201–1 linear regulator has an absolute maximum specification of 7.0 V for the voltage difference between  $V_{IN}$  and  $V_{OUT}$ . However, the IC may be used to regulate voltages in excess of 7.0 V. The main considerations in such a design are power–up and short circuit capability.

In most applications, ramp-up of the power supply to V<sub>IN</sub> is fairly slow, typically on the order of several tens of milliseconds, while the regulator responds in less than one microsecond. In this case, the linear regulator begins charging the load as soon as the V<sub>IN</sub> to V<sub>OUT</sub> differential is large enough that the pass transistor conducts current. The load at this point is essentially at ground, and the supply voltage is on the order of several hundred millivolts, with the result that the pass transistor is in dropout. As the supply to V<sub>IN</sub> increases, the pass transistor will remain in dropout, and current is passed to the load until V<sub>OUT</sub> reaches the point at which the IC is in regulation. Further increase in the supply voltage brings the pass transistor out of dropout. The result is that the output voltage follows the power supply ramp-up, staying in dropout until the regulation point is reached. In this manner, any output voltage may be regulated. There is no theoretical limit to the regulated voltage as long as the V<sub>IN</sub> to V<sub>OUT</sub> differential of 7.0 V is not exceeded.

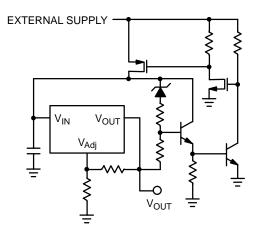

However, the possibility of destroying the IC in a short circuit condition is very real for this type of design. Short circuit conditions will result in the immediate operation of the pass transistor outside of its safe operating area. Over–voltage stresses will then cause destruction of the pass transistor before overcurrent or thermal shutdown circuitry can become active. Additional circuitry may be required to clamp the  $V_{\rm IN}$  to  $V_{\rm OUT}$  differential to less than 7.0 V if failsafe operation is required. One possible clamp circuit is

illustrated in Figure 12; however, the design of clamp circuitry must be done on an application by application basis. Care must be taken to ensure the clamp actually protects the design. Components used in the clamp design must be able to withstand the short circuit condition indefinitely while protecting the IC.

Figure 12. Short Circuit Protection Circuit for High Voltage Application.

### **Stability Considerations**

The output compensation capacitor helps determine three main characteristics of a linear regulator: start—up delay, load transient response, and loop stability.

The capacitor value and type is based on cost, availability, size and temperature constraints. A tantalum or aluminum electrolytic capacitor is best, since a film or ceramic capacitor with almost zero ESR can cause instability. The aluminum electrolytic capacitor is the least expensive solution. However, when the circuit operates at low temperatures, both the value and ESR of the capacitor will vary considerably. The capacitor manufacturer's data sheet provides this information.

A 22  $\mu F$  tantalum capacitor will work for most applications, but with high current regulators such as the CS5201–1 the transient response and stability improve with higher values of capacitance. The majority of applications for this regulator involve large changes in load current so the output capacitor must supply the instantaneous load current. The ESR of the output capacitor causes an immediate drop in output voltage given by:

$$\Delta V = \Delta I \times ESR$$

For microprocessor applications it is customary to use an output capacitor network consisting of several tantalum and ceramic capacitors in parallel. This reduces the overall ESR and reduces the instantaneous output voltage drop under transient load conditions. The output capacitor network should be as close to the load as possible for the best results.

### **Protection Diodes**

When large external capacitors are used with a linear regulator it is sometimes necessary to add protection diodes. If the input voltage of the regulator gets shorted, the output capacitor will discharge into the output of the regulator. The discharge current depends on the value of the capacitor, the output voltage and the rate at which  $V_{\rm IN}$  drops. In the CS5201–1 linear regulator, the discharge path is through a large junction and protection diodes are not usually needed. If the regulator is used with large values of output capacitance and the input voltage is instantaneously shorted to ground, damage can occur. In this case, a diode connected as shown in Figure 13 is recommended.

Figure 13. Protection Diode for Large Output Capacitors

### **Output Voltage Sensing**

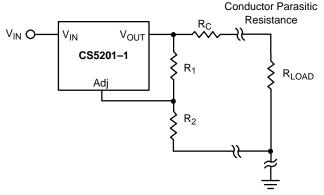

Since the CS5201-1 is a three terminal regulator, it is not possible to provide true remote load sensing. Load regulation is limited by the resistance of the conductors connecting the regulator to the load.

For the adjustable regulator, the best load regulation occurs when R1 is connected directly to the output pin of the regulator as shown in Figure 14. If R1 is connected to the load, RC is multiplied by the divider ratio and the effective resistance between the regulator and the load becomes.

$$R_C imes \left( \frac{R1 + R2}{R1} \right)$$

where  $R_C$  = conductor parasitic resistance.

Figure 14. Grounding Scheme for Adjustable Output Regulator to Minimize Parasitic Resistance Effects

## Calculating Power Dissipation and Heat Sink Requirements

The CS5201–1 linear regulator includes thermal shutdown and current limit circuitry to protect the device. High power regulators such as these usually operate at high junction temperatures so it is important to calculate the power dissipation and junction temperatures accurately to ensure that an adequate heat sink is used.

The case is connected to  $V_{OUT}$  on the CS5201–1, electrical isolation may be required for some applications. Thermal compound should always be used with high current regulators such as these.

The thermal characteristics of an IC depend on the following four factors:

- 1. Maximum Ambient Temperature T<sub>A</sub> (°C)

- 2. Power dissipation P<sub>D</sub> (Watts)

- 3. Maximum junction temperature T<sub>J</sub> (°C)

- 4. Thermal resistance junction to ambient R<sub>ΘJA</sub> (°C/W)

These four are related by the equation

$$T_{J} = T_{A} + P_{D} \times R_{\Theta JA} \tag{1}$$

The maximum ambient temperature and the power dissipation are determined by the design while the maximum junction temperature and the thermal resistance depend on the manufacturer and the package type.

The maximum power dissipation for a regulator is:

$$PD(max) = \{VIN(max) - VOUT(min)\}IOUT(max) + VIN(max)IQ$$

(2)

where:

V<sub>IN(max)</sub> is the maximum input voltage,

V<sub>OUT(min)</sub> is the minimum output voltage,

$I_{OUT(max)}$  is the maximum output current, for the application

I<sub>Q</sub> is the maximum quiescent current at I<sub>OUT(max)</sub>.

A heat sink effectively increases the surface area of the package to improve the flow of heat away from the IC and into the surrounding air.

Each material in the heat flow path between the IC and the outside environment has a thermal resistance. Like series electrical resistances, these resistances are summed to determine  $R_{\Theta JA}$ , the total thermal resistance between the junction and the surrounding air.

- 1. Thermal Resistance of the junction to case,  $R_{\Theta JC}$  (°C/W)

- 2. Thermal Resistance of the case to Heat Sink,  $R_{\Theta CS}$  (°C/W)

- 3. Thermal Resistance of the Heat Sink to the ambient air,  $R_{\Theta SA}$  (°C/W)

These are connected by the equation:

$$R_{\Theta}JA = R_{\Theta}JC + R_{\Theta}CS + R_{\Theta}SA \tag{3}$$

The value for  $R_{\Theta JA}$  is calculated using equation (3) and the result can be substituted in equation (1).

The value for  $R_{\Theta JC}$  is 3.5°C/W for a given package type based on an average die size. For a high current regulator such as the CS5201–1 the majority of the heat is generated in the power transistor section. The value for  $R_{\Theta SA}$  depends on the heat sink type, while  $R_{\Theta CS}$  depends on factors such as package type, heat sink interface (is an insulator and

thermal grease used?), and the contact area between the heat sink and the package. Once these calculations are complete, the maximum permissible value of  $R_{\Theta JA}$  can be calculated and the proper heat sink selected. For further discussion on heat sink selection, see application note "Thermal Management," document number AND8036/D, available through the Literature Distribution Center or via our website at http://onsemi.com.

### ADDITIONAL ORDERING INFORMATION

| Orderable Part<br>Number | Туре               | Description                            |

|--------------------------|--------------------|----------------------------------------|

| CS5201-1GT3              | 1.0 A, Adj. Output | TO-220 THREE LEAD, STRAIGHT            |

| CS5201-1GDP3             | 1.0 A, Adj. Output | D <sup>2</sup> PAK 3–PIN               |

| CS5201-1GDPR3            | 1.0 A, Adj. Output | D <sup>2</sup> PAK 3-PIN (Tape & Reel) |

| CS5201-1GST3             | 1.0 A, Adj. Output | SOT-223                                |

| CS5201-1GSTR3            | 1.0 A, Adj. Output | SOT-223 (Tape & Reel)                  |

### **MARKING DIAGRAMS**

A = Assembly Location

WL, L = Wafer Lot

YY, Y = Year

WW, W = Work Week

### CS5201-1

### **PACKAGE DIMENSIONS**

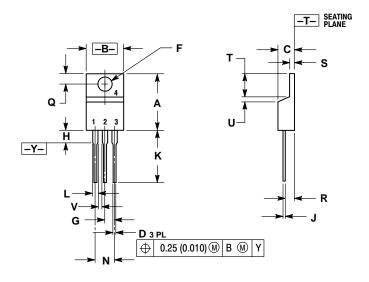

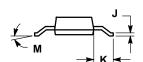

TO-220 **THREE LEAD** T SUFFIX CASE 221A-08 **ISSUE AA**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

|     | INCHES  |       | MILLIN   | IETERS |

|-----|---------|-------|----------|--------|

| DIM | MIN MAX |       | MIN      | MAX    |

| Α   | 0.560   | 0.625 | 14.23    | 15.87  |

| В   | 0.380   | 0.420 | 9.66     | 10.66  |

| С   | 0.140   | 0.190 | 3.56     | 4.82   |

| D   | 0.025   | 0.035 | 0.64     | 0.89   |

| F   | 0.139   | 0.155 | 3.53     | 3.93   |

| G   | 0.100   | BSC   | 2.54 BSC |        |

| Н   |         | 0.280 |          | 7.11   |

| J   | 0.012   | 0.045 | 0.31     | 1.14   |

| K   | 0.500   | 0.580 | 12.70    | 14.73  |

| L   | 0.045   | 0.060 | 1.15     | 1.52   |

| N   | 0.200   | BSC   | 5.08 BSC |        |

| Q   | 0.100   | 0.135 | 2.54     | 3.42   |

| R   | 0.080   | 0.115 | 2.04     | 2.92   |

| S   | 0.020   | 0.055 | 0.51     | 1.39   |

| T   | 0.235   | 0.255 | 5.97     | 6.47   |

| U   | 0.000   | 0.050 | 0.00     | 1.27   |

| ٧   | 0.045   |       | 1.15     |        |

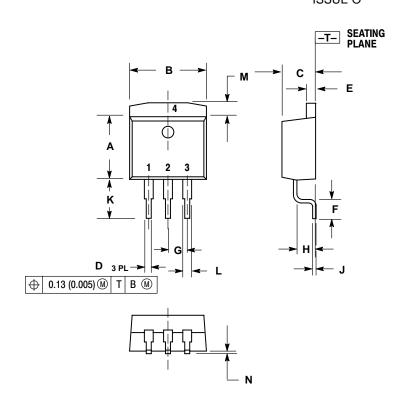

D<sup>2</sup>PAK 3-PIN **DP SUFFIX** CASE 418E-01 ISSUE O

- NOTES:

1. DIMENSIONS AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

|     | INC   | HES   | MILLIN   | IETERS |

|-----|-------|-------|----------|--------|

| DIM | MIN   | MAX   | MIN      | MAX    |

| Α   | 0.326 | 0.336 | 8.28     | 8.53   |

| В   | 0.396 | 0.406 | 10.05    | 10.31  |

| С   | 0.170 | 0.180 | 4.31     | 4.57   |

| D   | 0.026 | 0.036 | 0.66     | 0.91   |

| Е   | 0.045 | 0.055 | 1.14     | 1.40   |

| F   | 0.090 | 0.110 | 2.29     | 2.79   |

| G   | 0.10  | 0 BSC | 2.54 BSC |        |

| Н   | 0.098 | 0.108 | 2.49     | 2.74   |

| _   | 0.018 | 0.025 | 0.46     | 0.64   |

| K   | 0.204 | 0.214 | 5.18     | 5.44   |

| L   | 0.045 | 0.055 | 1.14     | 1.40   |

| M   | 0.055 | 0.066 | 1.40     | 1.68   |

| N   | 0.000 | 0.004 | 0.00     | 0.10   |

### SOT-223 ST SUFFIX CASE 318E-04 ISSUE K

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

|     | INCHES |        | MILLIMETERS |       |

|-----|--------|--------|-------------|-------|

| DIM | MIN    | MAX    | MIN         | MAX   |

| Α   | 0.249  | 0.263  | 6.30        | 6.70  |

| В   | 0.130  | 0.145  | 3.30        | 3.70  |

| С   | 0.060  | 0.068  | 1.50        | 1.75  |

| D   | 0.024  | 0.035  | 0.60        | 0.89  |

| F   | 0.115  | 0.126  | 2.90        | 3.20  |

| G   | 0.087  | 0.094  | 2.20        | 2.40  |

| Н   | 0.0008 | 0.0040 | 0.020       | 0.100 |

| J   | 0.009  | 0.014  | 0.24        | 0.35  |

| K   | 0.060  | 0.078  | 1.50        | 2.00  |

| L   | 0.033  | 0.041  | 0.85        | 1.05  |

| M   | 0°     | 10 °   | 0 °         | 10 °  |

| S   | 0.264  | 0.287  | 6.70        | 7.30  |

### **PACKAGE THERMAL DATA**

| Parameter       |         | TO-220<br>THREE LEAD | D <sup>2</sup> PAK<br>3–PIN | SOT-223 | Unit |

|-----------------|---------|----------------------|-----------------------------|---------|------|

| $R_{\Theta JC}$ | Typical | 3.5                  | 3.5                         | 15      | °C/W |

| $R_{\Theta JA}$ | Typical | 50                   | 10–50*                      | 156     | °C/W |

<sup>\*</sup> Depending on thermal properties of substrate.  $R_{\Theta JA}$  =  $R_{\Theta JC}$  +  $R_{\Theta CA}$

## **Notes**

## **Notes**

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

### PUBLICATION ORDERING INFORMATION

### Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

**Phone:** 303–675–2175 or 800–344–3860 Toll Free USA/Canada **Fax:** 303–675–2176 or 800–344–3867 Toll Free USA/Canada

Email: ONlit@hibbertco.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

**JAPAN**: ON Semiconductor, Japan Customer Focus Center 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–0031

Phone: 81–3–5740–2700 Email: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local

Sales Representative.