# 8-Input Universal Shift/Storage Register with Synchronous Reset and Common I/O Pins1

The MC74ACT323 is an 8-bit universal shift/storage register with3-state outputs. Its function is similar to the MC74ACT299 with the exception of Synchronous Reset. Parallel load inputs and flip-flop outputs are multiplexed to minimize pin count. Separate serial inputs and outputs are provided for  $Q_0$  and  $Q_7$  to allow easy cascading. Four operation modes are possible: hold (store), shift left, shift right and parallel load.

- Common Parallel I/O for Reduced Pin Count

- Additional Serial Inputs and Outputs for Expansion

- Four Operating Modes: Shift Left, Shift Right, Load and Store

- 3-State Outputs for Bus-Oriented Applications

- Outputs Source/Sink 24 mA

- TTL Compatible Inputs

## ON Semiconductor™

http://onsemi.com

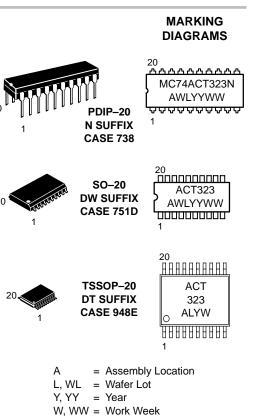

### ORDERING INFORMATION

| Device         | Package  | Shipping         |  |  |  |  |  |  |

|----------------|----------|------------------|--|--|--|--|--|--|

| MC74ACT323N    | PDIP-20  | 18 Units/Rail    |  |  |  |  |  |  |

| MC74ACT323DW   | SOIC-20  | 38 Units/Rail    |  |  |  |  |  |  |

| MC74ACT323DWR2 | SOIC-20  | 1000 Tape & Reel |  |  |  |  |  |  |

| MC74ACT323DT   | TSSOP-20 | 75 Units/Rail    |  |  |  |  |  |  |

| MC74ACT323DTR2 | TSSOP-20 | 2500 Tape & Reel |  |  |  |  |  |  |

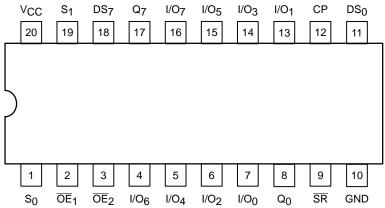

Figure 1. Pinout: 20-Lead Packages Conductors (Top View)

#### **PIN ASSIGNMENT**

| PIN                                    | FUNCTION                                                           |

|----------------------------------------|--------------------------------------------------------------------|

| CP                                     | Clock Pulse Input                                                  |

| DS <sub>0</sub>                        | Serial Data Input for Right Shift                                  |

| DS7                                    | Serial Data Input for Left Shift                                   |

| S <sub>0</sub> , S <sub>1</sub>        | Mode Select Inputs                                                 |

| SR                                     | Synchronous Master Reset                                           |

| $\overline{OE}_{1}, \overline{OE}_{2}$ | 3-State Output Enable Inputs                                       |

| 1/0 <sub>0</sub> –1/0 <sub>7</sub>     | Multipled Parallel Data Inputs or<br>3-State Parallel Data Outputs |

| Q <sub>0</sub> , Q <sub>7</sub>        | Serial Outputs                                                     |

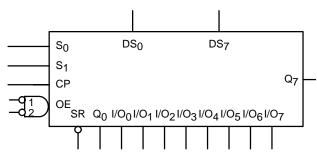

Figure 3. Logic Symbol

### **TRUTH TABLE**

| Inputs |                |                |    |                                                                                                                                                                                |

|--------|----------------|----------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SR     | S <sub>1</sub> | S <sub>0</sub> | СР | Response                                                                                                                                                                       |

| L      | Х              | Х              | 7  | Synchronous Reset; Q <sub>0</sub> – Q <sub>7</sub> =<br>LOW                                                                                                                    |

| н      | н              | н              | Т  | Parallel Load; I/O_n $\rightarrow$ Q_n                                                                                                                                         |

| н      | L              | Н              |    | Parallel Load; I/O <sub>n</sub> $\rightarrow$ Q <sub>n</sub><br>Shift Right; DS <sub>0</sub> $\rightarrow$ Q <sub>0</sub> , Q <sub>0</sub> $\rightarrow$ Q <sub>1</sub> , etc. |

| н      | н              | L              | Ъ  | Shift Left; $\text{DS}_7 \rightarrow \text{Q}_7,  \text{Q}_7 \rightarrow \text{Q}_6,  \text{etc.}$                                                                             |

| н      | L              | L              | Х  | Hold                                                                                                                                                                           |

H = HIGH Voltage Level X = Immaterial

L = LOW Voltage Level J = LOW-to-HIGH Clock Transition

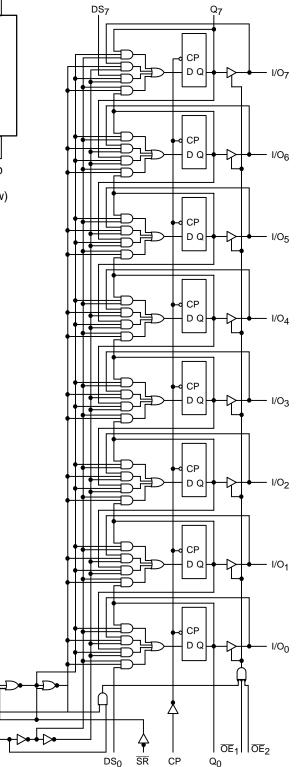

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

#### Figure 2. LOGIC DIAGRAM

S<sub>0</sub>

S

### FUNCTIONAL DESCRIPTION

The MC74ACT323 contains eight edge- triggered D-type flip-flops and the interstage logic necessary to perform synchronous reset, shift left, shift right, parallel load and hold operations. The type of operation is determined by S<sub>0</sub> and S<sub>1</sub> as shown in the Mode Select Table. All flip-flop outputs are brought out through 3 state buffers to separate I/O pins that also serve as data inputs in the parallel load mode. Q<sub>0</sub> and Q<sub>7</sub> are also brought out on other pins for expansion in serial shifting of longer words.

A LOW signal on  $\overline{SR}$  overrides the Select inputs and allows the flip-flops to be reset by the next rising edge of CP.

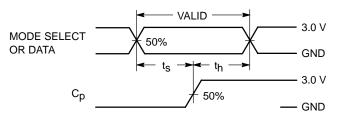

All other state changes are also initiated by the LOW-to-HIGH CP transition. Inputs can change when the clock is in either state provided only that the recommended setup and hold times, relative to the rising edge of CP, are observed.

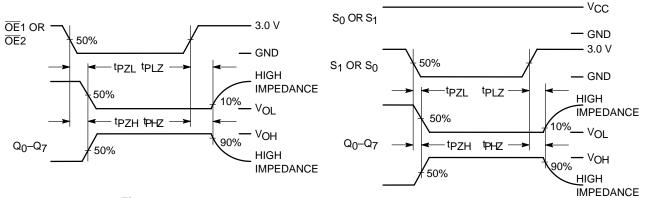

A HIGH signal on either  $\overline{\text{OE}}_1$  or  $\overline{\text{OE}}_2$  disables the 3-state buffers and puts the I/O pins in the high impedance state. In this condition the shift, hold, load and reset operations can still occur. The 3-state buffers are also disabled by HIGH signals on both S<sub>0</sub> and S<sub>1</sub> in preparation for a parallel load operation.

| Symbol           | F                                      | Parameter                                                                            | Value                             | Unit |

|------------------|----------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------|------|

| VCC              | DC Supply Voltage                      |                                                                                      | -0.5 to +7.0                      | V    |

| VI               | DC Input Voltage                       |                                                                                      | $-0.5 \le V_{I} \le V_{CC} + 0.5$ | V    |

| VO               | DC Output Voltage                      | (Note 2)                                                                             | $-0.5 \le V_{O} \le V_{CC} + 0.5$ | V    |

| Iк               | DC Input Diode Current                 |                                                                                      | ±20                               | mA   |

| ЮК               | DC Output Diode Current                |                                                                                      | ±50                               | mA   |

| IO               | DC Output Sink/Source Current          |                                                                                      | ±50                               | mA   |

| ICC              | DC Supply Current per Output Pin       |                                                                                      | ±50                               | mA   |

| IGND             | DC Ground Current per Output Pin       |                                                                                      | ±50                               | mA   |

| TSTG             | Storage Temperature Range              |                                                                                      | -65 to +150                       | °C   |

| тL               | Lead temperature, 1 mm from Case for   | or 10 Seconds                                                                        | 260                               | °C   |

| ТJ               | Junction temperature under Bias        |                                                                                      | + 150                             | °C   |

| θJA              | Thermal resistance                     | PDIP<br>SOIC<br>TSSOP                                                                | 67<br>96<br>128                   | °C/W |

| PD               | Power Dissipation in Still Air at 85°C | PDIP<br>SOIC<br>TSSOP                                                                | 750<br>500<br>450                 | mW   |

| MSL              | Moisture Sensitivity                   |                                                                                      | Level 1                           |      |

| F <sub>R</sub>   | Flammability Rating                    | Oxygen Index: 30% – 35%                                                              | UL 94 V–0 @ 0.125 in              |      |

| V <sub>ESD</sub> | ESD Withstand Voltage                  | Human Body Model (Note 3)<br>Machine Model (Note 4)<br>Charged Device Model (Note 5) | > 2000<br>> 200<br>>1000          | V    |

| ILatch-Up        | Latch–Up Performance                   | Above V_CC and Below GND at $85^\circ\text{C}$ (Note 6)                              | ±100                              | mA   |

MAXIMUM RATINGS (Note 1)

Absolute maximum continuous ratings are those values beyond which damage to the device may occur. Extended exposure to these

conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation under absolute maximum

–rated

conditions is not implied.

2. IO absolute maximum rating must be observed.

3. Tested to EIA/JESD22-A114-A.

4. Tested to EIA/JESD22-A115-A.

5. Tested to JESD22–C101–A.

6. Tested to EIA/JESD78.

### **RECOMMENDED OPERATING CONDITIONS**

| Symbol                             | Parameter                                            |                                                    | Min    | Тур       | Мах       | Unit |

|------------------------------------|------------------------------------------------------|----------------------------------------------------|--------|-----------|-----------|------|

| VCC                                | DC Input Voltage (Referenced to GND)                 |                                                    | 4.5    |           | 5.5       | V    |

| V <sub>in</sub> , V <sub>out</sub> | DC Input Voltage, Output Voltage (Referenced to GND) |                                                    |        |           | VCC       | V    |

| TA                                 | Operating Temperature, All Package Types             |                                                    | -40    | 25        | +85       | °C   |

| t <sub>r</sub> , t <sub>f</sub>    | Input Rise and Fall Time (Note 8)                    | V <sub>CC</sub> = 4.5 V<br>V <sub>CC</sub> = 5.5 V | 0<br>0 | 10<br>8.0 | 10<br>8.0 | ns/V |

| ТJ                                 | Junction Temperature (PDIP)                          |                                                    |        |           | 140       | °C   |

| IOH                                | Output Current – High                                |                                                    |        |           | -24       | mA   |

| I <sub>OL</sub>                    | Output Current – Low                                 |                                                    |        |           | 24        | mA   |

7. Unused Inputs may not be left open. All inputs must be tied to a high voltage level or low logic voltage level.

8. V<sub>in</sub> from 0.8 V to 2.0 V; refer to individual Data Sheets for devices that differ from the typical input rise and fall times.

### **DC CHARACTERISTICS**

|                                      | Parameter                                 |                     | T <sub>A</sub> = - | +25°C        | T <sub>A</sub> = −40°C to<br>+85°C |          |                                                                   |

|--------------------------------------|-------------------------------------------|---------------------|--------------------|--------------|------------------------------------|----------|-------------------------------------------------------------------|

| Symbol                               |                                           | V <sub>CC</sub> (V) | ) Typ Guar         |              | anteed Limits                      | Unit     | Conditions                                                        |

| VIH                                  | Minimum High Level Input Voltage          | 4.5<br>5.5          | 1.5<br>1.5         | 2.0<br>2.0   | 2.0<br>2.0                         | V<br>V   | V <sub>OUT</sub> = 0.1 V<br>or<br>V <sub>CC</sub> - 0.1 V         |

| VIL                                  | Maximum Low Level Input Voltage           | 4.5<br>5.5          | 1.5<br>1.5         | 0.8<br>0.8   | 0.8<br>0.8                         | V<br>V   | V <sub>OUT</sub> = 0.1 V<br>or<br>V <sub>CC</sub> - 0.1 V         |

| VOH                                  | Minimum High Level Output Voltage         | 4.5<br>5.5          | 4.49<br>5.49       | 4.4<br>5.4   | 4.4<br>5.4                         | V<br>V   | I <sub>OUT</sub> = -50 μA                                         |

|                                      |                                           | 4.5<br>5.5          |                    | 3.86<br>4.86 | 3.76<br>4.76                       | V<br>V   | $V_{IN} = V_{IL} \text{ or } V_{IH} -24 \text{ mA}$<br>IOH -24 mA |

| V <sub>OL</sub>                      | Maximum Low Level Output Voltage          | 4.5<br>5.5          | 0.001<br>0.001     | 0.1<br>0.1   | 0.1<br>0.1                         | V<br>V   | I <sub>OUT</sub> = 50 μA                                          |

|                                      |                                           | 4.5<br>5.5          |                    | 0.36<br>0.36 | 0.44<br>0.44                       | V<br>V   | $V_{IN} = V_{IL} \text{ or } V_{IH} -24 \text{ mA}$<br>IOH -24 mA |

| I <sub>IN</sub>                      | Maximum Input Leakage Current             | 5.5                 |                    | ±0.1         | ±1.0                               | μΑ       | $V_{I} = V_{CC}, GND$                                             |

| ΔICCT                                | Additional Maximum I <sub>CC</sub> /Input | 5.5                 | 0.6                |              | 1.5                                | mA       | $V_{I} = V_{CC} - 2.1 V$                                          |

| I <sub>OZ</sub>                      | Maximum 3–State Current                   | 5.5                 |                    | ±0.5         | ±5.0                               | μA       |                                                                   |

| I <sub>OLD</sub><br>I <sub>OHD</sub> | †Minimum Dynamic Output Current           | 5.5<br>5.5          |                    |              | 75<br>–75                          | mA<br>mA | V <sub>OLD</sub> = 1.65 V Max<br>V <sub>OHD</sub> = 3.85 V Min    |

| ICC                                  | Maximum Quiescent Supply Current          | 5.5                 |                    | 8.0          | 80                                 | μA       | $V_{IN} = V_{CC}$ or GND                                          |

\*All outputs loaded; thresholds on input associated with output under test. †Maximum test duration 2.0 ms, one output loaded at a time.

3.5

3.5

4.0

3.0

7.5

7.5

8.5

8.0

11

11.5

12.5

11.5

3.0

3.0

3.0

2.5

12.5

13

13.5

12.5

Unit MHz ns ns ns

ns

ns

ns

ns

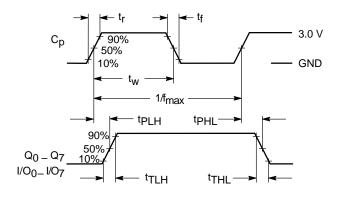

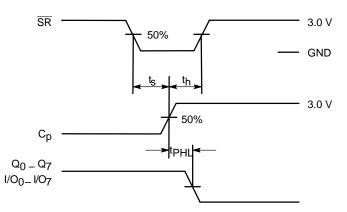

| AC CHAP          | <b>TACTERISTICS</b> $i_r = i_f$ | = 3.0 lis (FOI Figure                  | s and wave           | ionns, see | Figures 4 ai                                     | iu 5.)                                                    |     |      |

|------------------|---------------------------------|----------------------------------------|----------------------|------------|--------------------------------------------------|-----------------------------------------------------------|-----|------|

|                  |                                 |                                        |                      |            | T <sub>A</sub> = +25°C<br>C <sub>L</sub> = 50 pF | T <sub>A</sub> = -40°C to +85°C<br>C <sub>L</sub> = 50 pF |     |      |

| Symbol           | Param                           | eter                                   | V <sub>CC*</sub> (V) | Min        | Тур                                              | Max                                                       | Min | Max  |

| f <sub>max</sub> | Maximum Input Freque            | ency                                   | 5.0                  | 120        | 125                                              |                                                           | 110 |      |

| <sup>t</sup> PLH | Propagation Delay               | CP to Q <sub>0 or</sub> Q <sub>7</sub> | 5.0                  | 5.0        | 9.0                                              | 12.5                                                      | 4.0 | 14   |

| <sup>t</sup> PHL | Propagation Delay               | CP to Q <sub>0 or</sub> Q <sub>7</sub> | 5.0                  | 5.0        | 9.0                                              | 13.5                                                      | 4.5 | 15   |

| <sup>t</sup> PLH | Propagation Delay               | CP to I/O <sub>n</sub>                 | 5.0                  | 5.0        | 8.5                                              | 12.5                                                      | 4.5 | 14.5 |

5.0

5.0

5.0

5.0

### **AC CHARACTERISTICS** $t_r = t_f = 3.0$ ns (For Figures and Waveforms, See Figures 4 and 5.)

\*Voltage Range 5.0 V is 5.0 V  $\pm$ 0.5 V

<sup>t</sup>PZH

<sup>t</sup>PZL

<sup>t</sup>PHZ

<sup>t</sup>PLZ

### AC OPERATING REQUIREMENTS

Output Enable Time

Output Enable Time

Output Disable Time

Output Disable Time

| Symbol         | I Parameter             |                                                          | V <sub>CC</sub> * (V) | T <sub>A</sub> = +25°C<br>C <sub>L</sub> = 50 pF |         | T <sub>A</sub> = -40°C to +85°C<br>C <sub>L</sub> = 50 pF | Unit |

|----------------|-------------------------|----------------------------------------------------------|-----------------------|--------------------------------------------------|---------|-----------------------------------------------------------|------|

| -              |                         |                                                          |                       | Тур                                              | Guarant |                                                           |      |

| t <sub>s</sub> | Setup Time, HIGH or LOW | S <sub>0</sub> or S <sub>1</sub> to CP                   | 5.0                   | 2.0                                              | 5.0     | 5.0                                                       | ns   |

| t <sub>h</sub> | Hold Time, HIGH or LOW  | S <sub>0</sub> or S <sub>1</sub> to CP                   | 5.0                   | 0                                                | 1.5     | 1.5                                                       | ns   |

| t <sub>s</sub> | Setup Time, HIGH or LOW | I/O <sub>n,</sub> DS <sub>0,</sub> DS <sub>7</sub> to CP | 5.0                   | 1.0                                              | 4.0     | 4.5                                                       | ns   |

| t <sub>h</sub> | Hold Time, HIGH or LOW  | I/O <sub>n,</sub> DS <sub>0,</sub> DS <sub>7</sub> to CP | 5.0                   | 0                                                | 1.0     | 1.0                                                       | ns   |

| t <sub>s</sub> | Setup Time, HIGH or LOW | SR to CP                                                 | 5.0                   | 1.0                                              | 2.5     | 2.5                                                       | ns   |

| t <sub>h</sub> | Hold Time, HIGH or LOW  | SR to CP                                                 | 5.0                   | 0                                                | 1.0     | 1.0                                                       | ns   |

| tw             | CP Pulse Width          | HIGH or LOW                                              | 5.0                   | 2.0                                              | 4.0     | 4.5                                                       | ns   |

\*Voltage Range 5.0 V is 5.0 V  $\pm$ 0.5 V

### CAPACITANCE

| Symbol          | Parameter                     | Value<br>Typ | Unit | Test Conditions         |

|-----------------|-------------------------------|--------------|------|-------------------------|

| C <sub>IN</sub> | Input Capacitance             | 4.5          | pF   | V <sub>CC</sub> = 5.0 V |

| C <sub>PD</sub> | Power Dissipation Capacitance | 170          | pF   | V <sub>CC</sub> = 5.0 V |

### SWITCHING WAVEFORMS

Figure 6.

Figure 7.

\*Includes all probe and jig capacitance

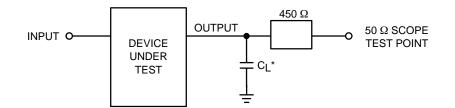

Figure 9. Test Circuit

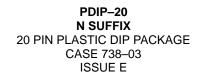

### PACKAGE DIMENSIONS

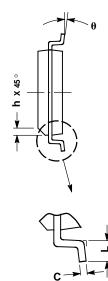

NOTES: 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. DIMENSION L TO CENTER OF LEAD WHEN

FORMER DIMENSION.

FORMED PARALLEL. 4. DIMENSION B DOES NOT INCLUDE MOLD FLASH.

|     | INCHES |       | MILLIN   | ETERS |  |

|-----|--------|-------|----------|-------|--|

| DIM | MIN    | MAX   | MIN      | MAX   |  |

| Α   | 1.010  | 1.070 | 25.66    | 27.17 |  |

| В   | 0.240  | 0.260 | 6.10     | 6.60  |  |

| С   | 0.150  | 0.180 | 3.81     | 4.57  |  |

| D   | 0.015  | 0.022 | 0.39     | 0.55  |  |

| Е   | 0.050  | BSC   | 1.27     | BSC   |  |

| F   | 0.050  | 0.070 | 1.27     | 1.77  |  |

| G   | 0.100  | BSC   | 2.54 BSC |       |  |

| J   | 0.008  | 0.015 | 0.21     | 0.38  |  |

| K   | 0.110  | 0.140 | 2.80     | 3.55  |  |

| L   | 0.300  | BSC   | 7.62     | BSC   |  |

| М   | 0 °    | 15°   | 0°       | 15°   |  |

| Ν   | 0.020  | 0.040 | 0.51     | 1.01  |  |

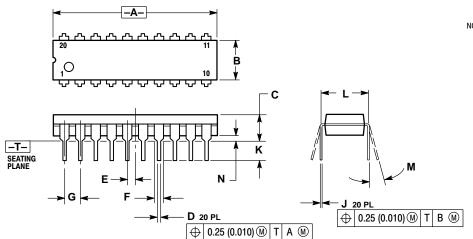

SO-20 **DW SUFFIX** 20 PIN PLASTIC SOIC PACKAGE CASE 751D-05 **ISSUE F**

NOTES:

DIMENSIONS ARE IN MILLIMETERS.

INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994.

DIMENSIONS D AND E DO NOT INCLUDE MOLD PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

DIMENSION B DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF B DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |       |  |  |  |

|-----|-------------|-------|--|--|--|

| DIM | MIN         | MAX   |  |  |  |

| Α   | 2.35        | 2.65  |  |  |  |

| A1  | 0.10        | 0.25  |  |  |  |

| В   | 0.35        | 0.49  |  |  |  |

| С   | 0.23        | 0.32  |  |  |  |

| D   | 12.65       | 12.95 |  |  |  |

| Е   | 7.40        | 7.60  |  |  |  |

| е   | 1.27        | BSC   |  |  |  |

| Н   | 10.05       | 10.55 |  |  |  |

| h   | 0.25        | 0.75  |  |  |  |

| L   | 0.50        | 0.90  |  |  |  |

| θ   | 0 °         | 7 °   |  |  |  |

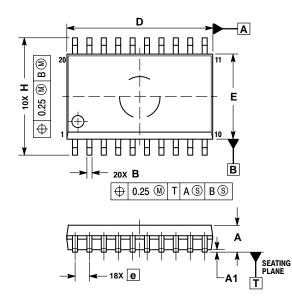

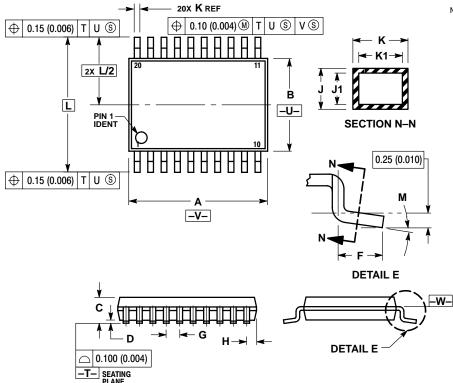

#### PACKAGE DIMENSIONS TSSOP-20 DT SUFFIX 20 PIN PLASTIC TSSOP PACKAGE CASE 948E-02 ISSUE A

NOTES: 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. 2. CONTROLLING DIMENSION: MILLIMETER.

- CONTROLLING DIMENSION: MILLIMETER.

DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH

- PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE. 4. DIMENSION B DOES NOT INCLUDE INTERLEAD

- DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.

- CINCLUSION K DOES NOT INCLUDE DAMBAR PROTRUSION K DOES NOT INCLUDE DAMBAR PROTRUSION SHALL BE 0.08 (0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 6. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

- DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE -W-.

|     | MILLIN   | IETERS | INCHES    |       |  |

|-----|----------|--------|-----------|-------|--|

| DIM | MIN      | MAX    | MIN       | MAX   |  |

| Α   | 6.40     | 6.60   | 0.252     | 0.260 |  |

| В   | 4.30     | 4.50   | 0.169     | 0.177 |  |

| С   |          | 1.20   |           | 0.047 |  |

| D   | 0.05     | 0.15   | 0.002     | 0.006 |  |

| F   | 0.50     | 0.75   | 0.020     | 0.030 |  |

| G   | 0.65     | BSC    | 0.026 BSC |       |  |

| н   | 0.27     | 0.37   | 0.011     | 0.015 |  |

| J   | 0.09     | 0.20   | 0.004     | 0.008 |  |

| J1  | 0.09     | 0.16   | 0.004     | 0.006 |  |

| K   | 0.19     | 0.30   | 0.007     | 0.012 |  |

| K1  | 0.19     | 0.25   | 0.007     | 0.010 |  |

| L   | 6.40 BSC |        | 0.252 BSC |       |  |

| М   | 0°       | 8°     | 0°        | 8°    |  |

**ON Semiconductor** and without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### PUBLICATION ORDERING INFORMATION

#### Literature Fulfillment:

Literature Distribution Center for ON Semiconductor

P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: ONlit@hibbertco.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

JAPAN: ON Semiconductor, Japan Customer Focus Center 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–0031 Phone: 81–3–5740–2700 Email: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local Sales Representative.