# 3 A Dual High-Speed MOSFET Drivers

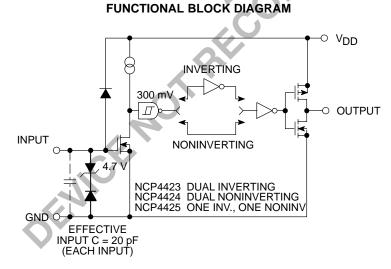

The NCP4423/4424/4425 are MOSFET drivers that are capable of giving reliable service in demanding electrical environments.

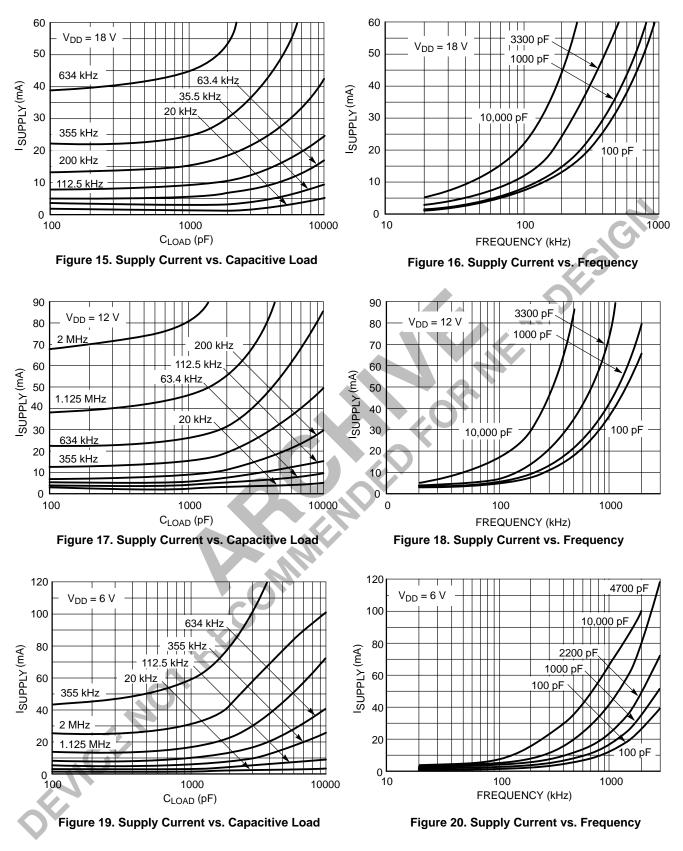

Although primarily intended for driving power MOSFETs, these drivers are well–suited for driving other loads (capacitive, resistive, or inductive) which require a low impedance driver capable of high peak currents and fast switching times. Applications such as heavily loaded clock lines, coaxial cables, or piezoelectric transducers can all be driven with the NCP4423/4424/4425. The only known limitation on loading is that the total power dissipated of the driver must be kept within the maximum power dissipation limits of the package.

#### Features

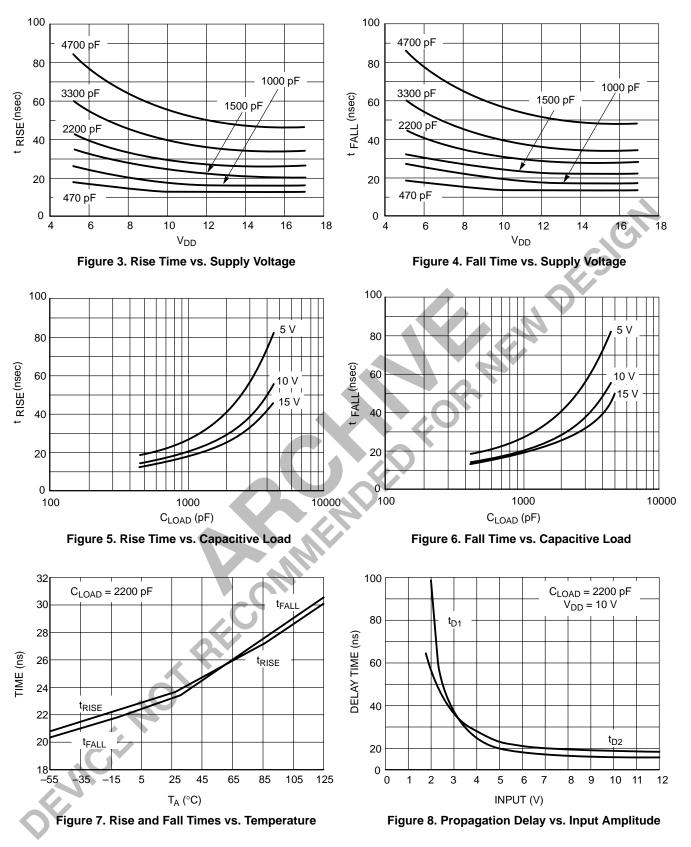

- High Peak Output Current (3 A)

- Wide Operating Range (4.5 V to 18 V)

- High Capacitive Load Drive Capability (1800 pF in 25 nsec)

- Short Delay Times (<40 nsec Typ)

- Matched Rise/Fall Times

- Low Supply Current With Logic "1" Input (3.5 mA) With Logic "0" Input (350 μA)

- Low Output Impedance  $(3.5 \Omega \text{ Typ})$

- Latch-Up Protected: Will Withstand 1.5 A Reverse Current

- Logic Input Will Withstand Negative Swing Up to 5 V

- ESD Protected (4 kV)

#### NOTES:

1. NCP4425 has one inverting and one noninverting driver.

2. Ground any unused driver input.

### **ON Semiconductor®**

http://onsemi.com

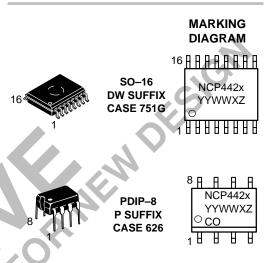

- = Device Number (3, 4, or 5)

- YY = Year

- WW = Work Week

- X = Assembly ID Code

- Z = Subcontractor ID Code

- CO = Country of Origin

#### **ORDERING INFORMATION**

| Device      | Package | Shipping         |

|-------------|---------|------------------|

| NCP4423DWR2 | SO–16   | 1000 Tape & Reel |

| NCP4424DWR2 | SO-16   | 1000 Tape & Reel |

| NCP4425DWR2 | SO-16   | 1000 Tape & Reel |

| NCP4423P    | PDIP-8  | 50 Units/Rail    |

| NCP4424P    | PDIP-8  | 50 Units/Rail    |

| NCP4425P    | PDIP-8  | 50 Units/Rail    |

#### **PIN CONNECTIONS**

|            | 16–Pin SO Wide                                       | 4423            | 4424            | 4425<br>I   | 8–Pin DIP    |

|------------|------------------------------------------------------|-----------------|-----------------|-------------|--------------|

| NC         |                                                      | ♥<br>NC         | ♦<br>NC         | ¥<br>NC     |              |

| IN A       | 2 15                                                 | OUT A           | OUT A           | OUT A       | 2 NCP4423 7  |

| NC         | 2 14                                                 | OUTA            | OUTA            | OUTA        | 3 NCP4424 6  |

| GND        | S      NCP4423      14        4      NCP4424      13 | V <sub>DD</sub> | V <sub>DD</sub> | $V_{DD}$    | 4 5          |

| GND        | 5 NCP4425 12                                         | $V_{DD}$        | $V_{DD}$        | $V_{DD}$    |              |

| NC         | 6 11                                                 | OUT B           | OUT B           | OUT B       |              |

| IN B<br>NC | 7 <u>10</u><br>8 9                                   | OUT B<br>NC     | OUT B<br>NC     | OUT B<br>NC |              |

|            | (Top View)                                           | NO              | NO              | NO          |              |

| NC -       |                                                      |                 |                 |             | 4            |

| NOT        | E: Duplicate pins must<br>operation.                 | both be co      | onnected fo     | r proper    | A NEW DESIGN |

|            |                                                      |                 |                 |             |              |

|            |                                                      |                 |                 |             |              |

|            |                                                      |                 |                 |             |              |

|            |                                                      |                 |                 |             |              |

|            |                                                      |                 |                 |             |              |

|            |                                                      |                 |                 |             |              |

|            |                                                      |                 |                 |             |              |

|            |                                                      |                 |                 |             |              |

|            |                                                      |                 |                 |             |              |

|            |                                                      |                 |                 |             |              |

|            |                                                      |                 |                 |             |              |

|            |                                                      | 0               |                 |             |              |

|            |                                                      | )               |                 |             |              |

|            |                                                      |                 |                 |             |              |

|            |                                                      |                 |                 |             |              |

|            |                                                      |                 |                 |             |              |

|            | <b>)</b>                                             |                 |                 |             |              |

| 2          |                                                      |                 |                 |             |              |

|            |                                                      |                 |                 |             |              |

|            |                                                      |                 |                 |             |              |

|            |                                                      |                 |                 |             |              |

|            |                                                      |                 |                 |             |              |

| DENICEN    |                                                      |                 |                 |             |              |

|            |                                                      |                 |                 |             |              |

|            |                                                      |                 |                 |             |              |

|            |                                                      |                 |                 |             |              |

|            |                                                      |                 |                 |             |              |

| 8–Pin DIP |                    |   |  |  |

|-----------|--------------------|---|--|--|

| 1         |                    | 8 |  |  |

| 2         | NCP4423<br>NCP4424 | 7 |  |  |

| 3         | NCP4424<br>NCP4425 | 6 |  |  |

| 4         |                    | 5 |  |  |

#### **ABSOLUTE MAXIMUM RATINGS**

| Rating                                                                                                                                | Value              | Unit     |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------|--|--|--|

| Supply Voltage                                                                                                                        | +22                | V        |  |  |  |

| Input Voltage, IN A or IN B (V <sub>DD</sub> + 0.3 V to GND – 5.0 V)                                                                  | -5                 | V        |  |  |  |

| Maximum Chip Temperature                                                                                                              | +150               | °C       |  |  |  |

| Storage Temperature Range, T <sub>stg</sub>                                                                                           | -65 to +150        | °C       |  |  |  |

| Lead Temperature (Soldering, 10 sec)                                                                                                  | +300               | °C       |  |  |  |

| Package Thermal Resistance SOIC, $R_{\theta JA}$<br>PDIP, $R_{\theta JA}$<br>PDIP, $R_{\theta JC}$                                    | 155<br>–125<br>–45 | °C/W     |  |  |  |

| Operating Temperature Range                                                                                                           | -40 to +85         | °C       |  |  |  |

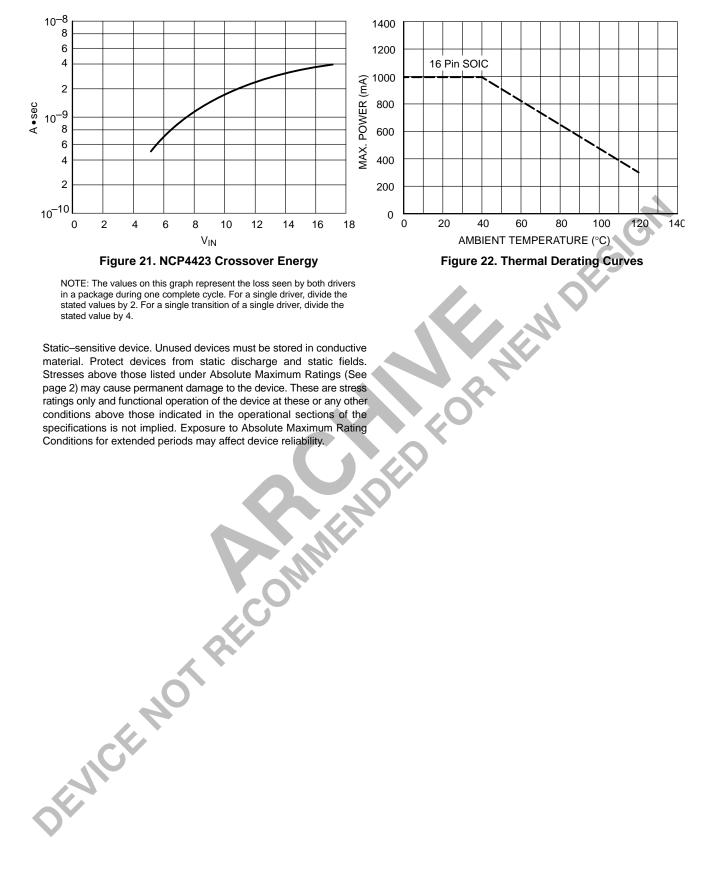

| Package Power Dissipation ( $T_A \le 70^{\circ}C$ )<br>SOIC<br>PDIP                                                                   | 470<br>730         | mW<br>mc |  |  |  |

| <b>ELECTRICAL CHARACTERISTICS</b> (T <sub>A</sub> = +25°C with 4.5 V $\leq$ V <sub>DD</sub> $\leq$ 18 V, unless otherwise specified.) |                    |          |  |  |  |

|                                                                                                                                       |                    |          |  |  |  |

|                                                  |                 |                                                                                                |                        |             |             | 1        |

|--------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------|------------------------|-------------|-------------|----------|

| Characteristic                                   | Symbol          | Test Conditions                                                                                | Min                    | Тур         | Max         | Unit     |

| Input                                            |                 |                                                                                                |                        |             |             |          |

| Logic 1 High Input Voltage                       | V <sub>OH</sub> | -                                                                                              | 2.4                    |             | -           | V        |

| Logic 0 Low Input Voltage                        | VIL             | -                                                                                              | -                      | <b>-</b>    | 0.8         | V        |

| Input Current                                    | I <sub>IN</sub> | $0 V \le V_{IN} \le V_{DD}$                                                                    | -1.0                   | _           | 1.0         | μA       |

| Output                                           | ·               |                                                                                                |                        |             |             |          |

| High Output Voltage                              | V <sub>OH</sub> |                                                                                                | V <sub>DD</sub> -0.025 | -           | -           | V        |

| Low Output Voltage                               | V <sub>OL</sub> |                                                                                                | -                      | -           | 0.025       | V        |

| Output Resistance, High                          | R <sub>OH</sub> | I <sub>OUT</sub> = 10 mA,<br>V <sub>DD</sub> = 18 V                                            | -                      | 2.8         | 5.0         | Ω        |

| Output Resistance, Low                           | R <sub>OL</sub> | I <sub>OUT</sub> = 10 mA,<br>V <sub>DD</sub> = 18 V                                            | -                      | 3.5         | 5.0         | Ω        |

| Peak Output Current                              | I <sub>PK</sub> |                                                                                                | -                      | 3.0         | -           | А        |

| Latch–Up Protection<br>Withstand Reverse Current | IREV            | Duty Cycle ≤ 2%<br>t ≤ 300 μs                                                                  | 1.5                    | -           | -           | A        |

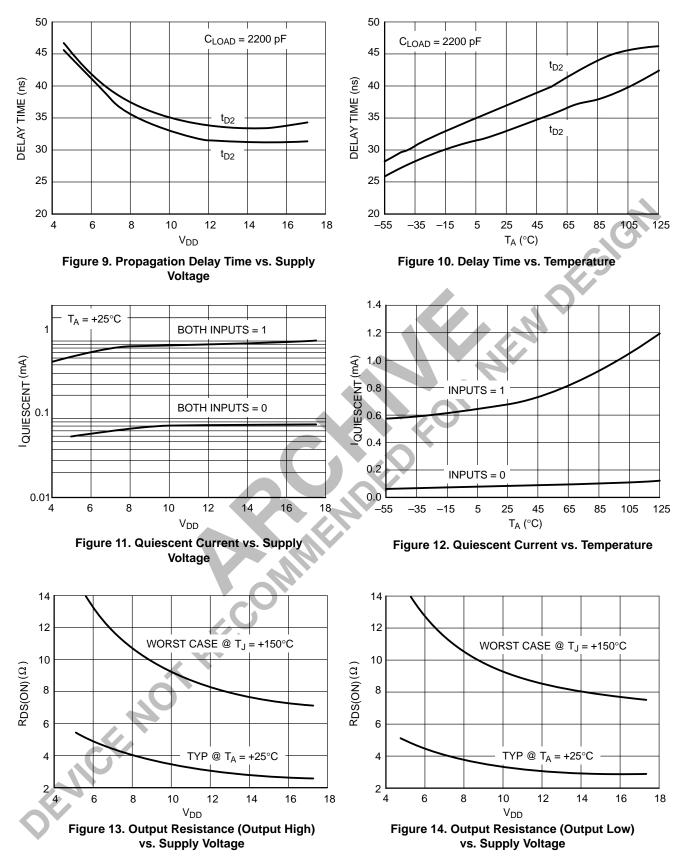

| Switching Time (Note 1)                          |                 |                                                                                                |                        |             |             |          |

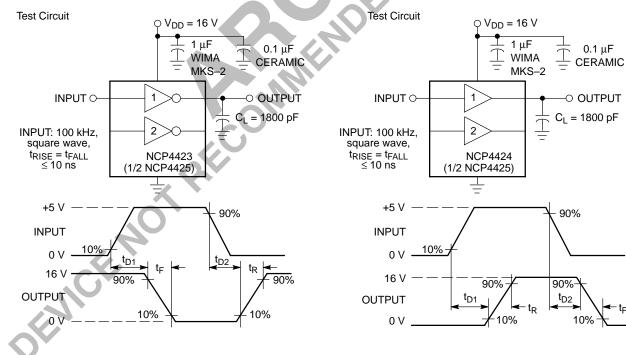

| Rise Time                                        | t <sub>R</sub>  | Figure 1, C <sub>L</sub> = 1800 pF                                                             | -                      | 23          | 35          | nsec     |

| Fall Time                                        | t⊭              | Figure 1, C <sub>L</sub> = 1800 pF                                                             | -                      | 25          | 35          | nsec     |

| Delay Time 1                                     | t <sub>D1</sub> | Figure 1, C <sub>L</sub> = 1800 pF                                                             | -                      | 33          | 75          | nsec     |

| Delay Time 2                                     | t <sub>D2</sub> | Figure 1, C <sub>L</sub> = 1800 pF                                                             | -                      | 38          | 75          | nsec     |

| Power Supply                                     | ·               |                                                                                                |                        | <u> </u>    | •           | <u> </u> |

| Power Supply Current                             | I <sub>S</sub>  | $V_{IN} = 3.0 \text{ V} \text{ (Both Inputs)}$<br>$V_{IN} = 0 \text{ V} \text{ (Both Inputs)}$ |                        | 1.5<br>0.15 | 2.5<br>0.25 | mA       |

1. Switching times guaranteed by design.

| Characteristic                                   | Symbol           | Test Conditions                                                   | Min                    | Тур        | Max        | Unit |

|--------------------------------------------------|------------------|-------------------------------------------------------------------|------------------------|------------|------------|------|

| Input                                            |                  |                                                                   |                        |            |            |      |

| Logic 1 High Input Voltage                       | V <sub>IH</sub>  | -                                                                 | 2.4                    | -          | -          | V    |

| Logic 0 Low Input Voltage                        | V <sub>IL</sub>  | -                                                                 | -                      | -          | 0.8        | V    |

| Input Current                                    | l <sub>IN</sub>  | $0 \text{ V} \leq \text{V}_{\text{IN}} \leq \text{V}_{\text{DD}}$ | -10                    | -          | 10         | μA   |

| Output                                           |                  |                                                                   |                        |            |            |      |

| High Output Voltage                              | V <sub>OH</sub>  | -                                                                 | V <sub>DD</sub> -0.025 | -          | -          | V    |

| Low Output Voltage                               | V <sub>OL</sub>  | -                                                                 | -                      | -          | 0.025      | V    |

| Output Resistance, High                          | R <sub>O</sub>   | I <sub>OUT</sub> = 10 mA,<br>V <sub>DD</sub> = 18 V               | -                      | 3.7        | 8.0        | Ω    |

| Output Resistance, Low                           | R <sub>O</sub>   | I <sub>OUT</sub> = 10 mA,<br>V <sub>DD</sub> = 18 V               | -                      | 4.3        | 8.0        | Ω    |

| Peak Output Current                              | I <sub>PK</sub>  | -                                                                 | -                      | 3.0        | -          | A    |

| Latch–Up Protection<br>Withstand Reverse Current | I <sub>REV</sub> | Duty Cycle ≤ 2%<br>t ≤ 300 μsec                                   | 1.5                    | -          |            | A    |

| Switching Time (Note 1)                          | ·                |                                                                   |                        |            |            | •    |

| Rise Time                                        | t <sub>R</sub>   | Figure 1, C <sub>L</sub> = 1800 pF                                |                        | 28         | 60         | nsec |

| Fall Time                                        | t <sub>F</sub>   | Figure 1, C <sub>L</sub> = 1800 pF                                |                        | 32         | 60         | nsec |

| Delay Time 1                                     | t <sub>D1</sub>  | Figure 1, C <sub>L</sub> = 1800 pF                                |                        | 32         | 100        | nsec |

| Delay Time 2                                     | t <sub>D2</sub>  | Figure 1, C <sub>L</sub> = 1800 pF                                |                        | 38         | 100        | nsec |

| Power Supply                                     |                  |                                                                   |                        |            | •          | •    |

| Power Supply Current                             | ۱ <sub>S</sub>   | $V_{IN} = 3.0 V$ (Both Inputs)<br>$V_{IN} = 0 V$ (Both Inputs)    | -                      | 2.0<br>0.2 | 3.5<br>0.3 | mA   |

Figure 1. Inverting Driver Switching Time

Figure 2. Noninverting Driver Switching Time

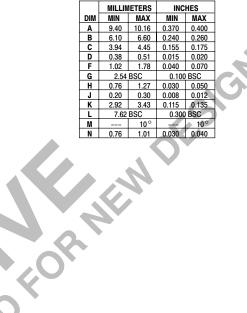

#### PACKAGE DIMENSIONS

PDIP-8 **P SUFFIX** CASE 626-05 ISSUE K Д ДД -B-<u>)</u>1 J ٩F -A-L С N SEATING PLANE М

κ

Ø 0.13 (0.005) M T A M

NOTE 2

-T-

H

FORMED PARALLEL. 2. PACKAGE CONTOUR OPTIONAL (ROUND OR SQUARE CORNERS). 3. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. INCHES

NOTES: 1. DIMENSION L TO CENTER OF LEAD WHEN

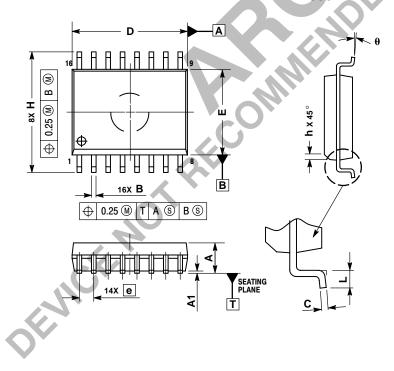

SO-16 DW SUFFIX CASE 751G-03 ISSUE B

В 🕅

D

G

$\oplus$

NOTES:

- DIMENSIONS ARE IN MILLIMETERS.

INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994.

- DIMENSIONS D AND E DO NOT INLCUDE MOLD PROTRUSION. 3.

MAXIMUM MOLD PROTRUSION 0.15 PER SIDE. DIMENSION B DOES NOT INCLUDE DAMBAR 5. PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF THE B DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |       |  |  |  |

|-----|-------------|-------|--|--|--|

| DIM | MIN         | MAX   |  |  |  |

| Α   | 2.35        | 2.65  |  |  |  |

| A1  | 0.10        | 0.25  |  |  |  |

| В   | 0.35        | 0.49  |  |  |  |

| С   | 0.23        | 0.32  |  |  |  |

| D   | 10.15       | 10.45 |  |  |  |

| Е   | 7.40        | 7.60  |  |  |  |

| е   | 1.27 BSC    |       |  |  |  |

| Н   | 10.05       | 10.55 |  |  |  |

| h   | 0.25        | 0.75  |  |  |  |

| L   | 0.50        | 0.90  |  |  |  |

| θ   | 0 °         | 7 °   |  |  |  |

# <u>Notes</u>

DEWCE NOT RECOMMENDED FOR MENDESIGN

# <u>Notes</u>

DEWCE NOT RECOMMENDED FOR MENDESIGN

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any product binetime. SCILLC makes no warrarty, representation or guarantee regarding the subability of its products for any product or circuit, and specification or use and and the subability of the specification or use and an experimentation of the subability of the specification or use of any product or circuit, and specification or use and an experimentation of the subability of the specification or use of any product or circuit, and specification or use and an experimentation or use and an experimentation or use and and the subability of the specification or use of any product or circuit, and specification or use and an experimentation or use of any product or circuit, and specification or use of any product or circuit, and specification or use and an experimentation or use of any product or circuit, and specification or use of any product or circuit, and specification or use of any product or circuit.

**ON Semiconductor** and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and to softicers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### PUBLICATION ORDERING INFORMATION

#### Literature Fulfillment:

Literature Distribution Center for ON Semiconductor

P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: ONlit@hibbertco.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

JAPAN: ON Semiconductor, Japan Customer Focus Center 2–9–1 Kamimeguro, Meguro–ku, Tokyo, Japan 153–0051 Phone: 81–3–5773–3850 Email: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local Sales Representative.