## High Slew Rate, Wide Bandwidth, JFET Input Operational Amplifiers

These devices are a new generation of high speed JFET input monolithic operational amplifiers. Innovative design concepts along with JFET technology provide wide gain bandwidth product and high slew rate. Well-matched JFET input devices and advanced trim techniques ensure low input offset errors and bias currents. The all NPN output stage features large output voltage swing, no deadband crossover distortion, high capacitive drive capability, excellent phase and gain margins, low open loop output impedance, and symmetrical source/sink AC frequency response.

This series of devices is available in fully compensated or decompensated (A<sub>VCL</sub> $\leq$ 2) and is specified over a commercial temperature range. They are pin compatible with existing Industry standard operational amplifiers, and allow the designer to easily upgrade the performance of existing designs.

- Wide Gain Bandwidth: 8.0 MHz for Fully Compensated Devices 16 MHz for Decompensated Devices

- High Slew Rate: 25 V/µs for Fully Compensated Devices 50 V/µs for Decompensated Devices

- High Input Impedance:  $10^{12}\Omega$

- Input Offset Voltage: 0.5 mV Maximum (Single Amplifier)

- Large Output Voltage Swing: -14.7 V to +14 V for V<sub>CC</sub>/V<sub>EE</sub> =  $\pm 15 \text{ V}$

- Low THD Distortion: 0.01%

- Excellent Phase/Gain Margins: 55°/7.6 dB for Fully Compensated Devices

## ORDERING INFORMATION

| Op Amp<br>Function | Fully<br>Compen-<br>sated | A <sub>VCL</sub> ≥2<br>Compensated | Operating<br>Temperature<br>Range | Package     |

|--------------------|---------------------------|------------------------------------|-----------------------------------|-------------|

| Cinalo             | MC34081BD                 | MC34080BD                          |                                   | SO–8        |

| Single             | MC34081BP                 | MC34080BP                          | $T_A = 0^\circ$ to +70°C          | Plastic DIP |

| Dual               | MC34082P                  | MC34083BP                          |                                   | Plastic DIP |

| Qued               | MC34084DW                 | MC34085BDW                         |                                   | SO-16L      |

| Quad               | MC34084P                  | MC34085BP                          | $T_A = 0^\circ$ to +70°C          | Plastic DIP |

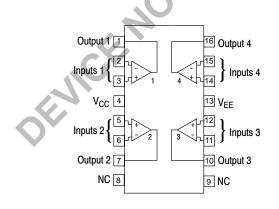

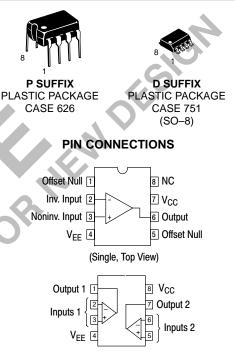

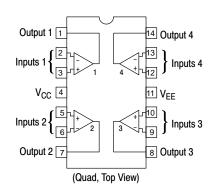

#### PIN CONNECTIONS

(Dual, Top View)

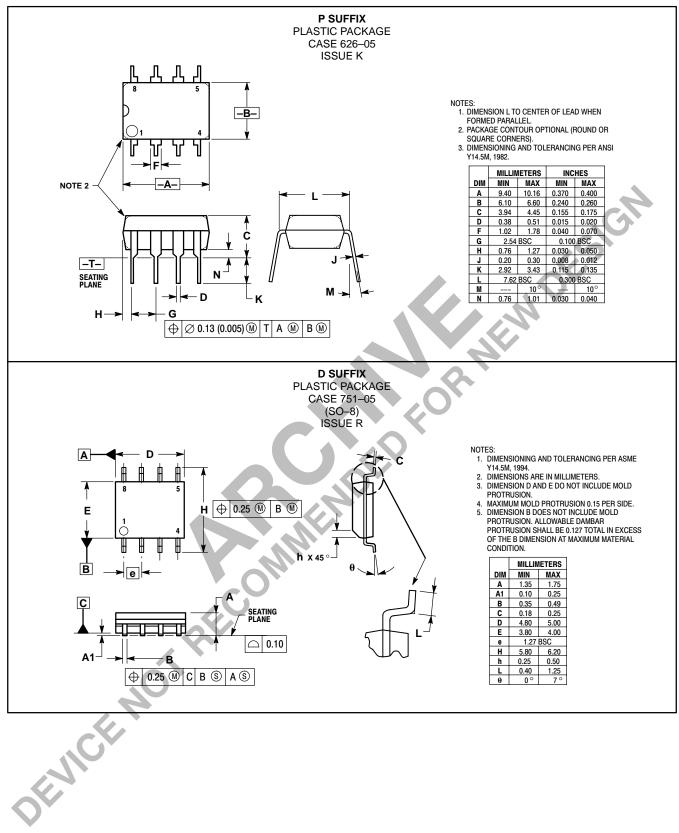

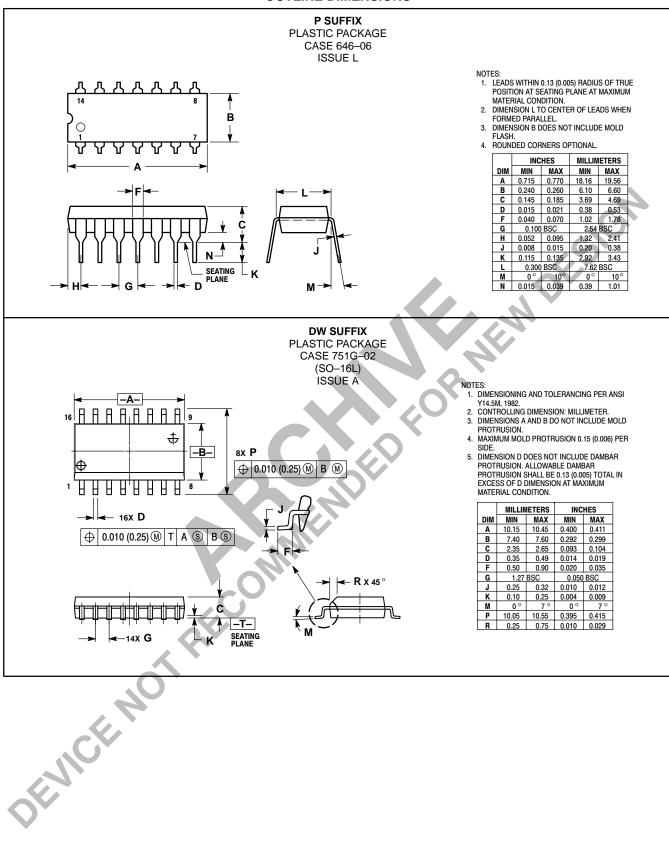

P SUFFIX PLASTIC PACKAGE CASE 646 DW SUFFIX PLASTIC PACKAGE CASE 751G (SO–16L)

# MC34080 thru MC34085

**HIGH PERFORMANCE**

JFET INPUT

**OPERATIONAL AMPLIFIERS**

1

#### **MAXIMUM RATINGS**

| Rating                                      | Symbol           | Value        | Unit |

|---------------------------------------------|------------------|--------------|------|

| Supply Voltage (from $V_{CC}$ to $V_{EE}$ ) | VS               | +44          | V    |

| Input Differential Voltage Range            | V <sub>IDR</sub> | (Note 1)     | V    |

| Input Voltage Range                         | V <sub>IR</sub>  | (Note 1)     | V    |

| Output Short Circuit Duration (Note 2)      | t <sub>SC</sub>  | Indefinite   | sec  |

| Operating Ambient Temperature Range         | T <sub>A</sub>   | 0 to +70     | °C   |

| Operating Junction Temperature              | TJ               | +125         | °C   |

| Storage Temperature Range                   | T <sub>stg</sub> | - 65 to +165 | °C   |

NOTES: 1. Either or both input voltages must not exceed the magnitude of V<sub>CC</sub> or V<sub>EE</sub>. 2. Power dissipation must be considered to ensure maximum junction temperature

(T<sub>J</sub>) is not exceeded.

F

| DC ELECTRICAL CHARACTERISTICS ( $V_{CC}$ = +15 V, $V_{EE}$ = - | -15 V, T <sub>A</sub> = T <sub>low</sub> to T <sub>high</sub> [Note 3], unless otherwise noted.) |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Characteristics                                                                                                                                                                            | Symbol                     | Min                                                  | Тур            | Мах            | Uni              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------|----------------|----------------|------------------|

| nput Offset Voltage (Note 4)                                                                                                                                                               | V <sub>IO</sub>            |                                                      |                |                | mV               |

| Single<br>$T_A = +25^{\circ}C$                                                                                                                                                             |                            |                                                      | 0.5            | 2.0            |                  |

| $T_A = +25$ C<br>$T_A = 0^\circ$ to +70°C (MC34080B, MC34081B)                                                                                                                             |                            | _                                                    | 0.5            | 4.0            |                  |

| Dual                                                                                                                                                                                       |                            |                                                      |                | _              |                  |

| $T_{A} = +25^{\circ}C$                                                                                                                                                                     |                            | —                                                    | 1.0            | 3.0            |                  |

| T <sub>A</sub> = 0° to +70°C (MC34082, MC34083)<br>Quad                                                                                                                                    |                            |                                                      |                | 5.0            |                  |

| $T_A = +25^{\circ}C$                                                                                                                                                                       |                            | _                                                    | 6.0            | 12             |                  |

| $T_A = 0^\circ$ to +70°C (MC34084, MC34085)                                                                                                                                                |                            | —                                                    | —              | 14             |                  |

| werage Temperature Coefficient of Offset Voltage                                                                                                                                           | $\Delta V_{IO} / \Delta T$ | —                                                    | 10             | _              | μV/ <sup>c</sup> |

| nput Bias Current (V <sub>CM</sub> = 0 Note 5)                                                                                                                                             | I <sub>IB</sub>            |                                                      |                |                |                  |

| $T_A = +25^{\circ}C$                                                                                                                                                                       |                            | —                                                    | 0.06           | 0.2            | nA               |

| $T_A = 0^\circ$ to $+70^\circ$ C                                                                                                                                                           |                            | _                                                    | _              | 4.0            | Þ                |

| nput Offset Current ( $V_{CM} = 0$ Note 5)                                                                                                                                                 | Ι <sub>ΙΟ</sub>            |                                                      |                |                |                  |

| $T_{A} = +25^{\circ}C$ $T_{A} = 0^{\circ} \text{ to } +70^{\circ}C$                                                                                                                        |                            | _                                                    | 0.02           | 0.1<br>2.0     | nA               |

|                                                                                                                                                                                            |                            |                                                      |                | 2.0            | 11               |

| arge Signal Voltage Gain (V <sub>O</sub> = $\pm$ 10 V, R <sub>L</sub> = 2.0 k)<br>T <sub>A</sub> = +25°C                                                                                   | A <sub>VOL</sub>           | 25                                                   | 80             | _              | V/m              |

| $T_A = T_{low}$ to $T_{high}$                                                                                                                                                              |                            | 15                                                   | _              | —              |                  |

| Dutput Voltage Swing                                                                                                                                                                       | V <sub>OH</sub>            |                                                      |                |                | V                |

| $R_{L} = 2.0 \text{ k}, T_{A} = +25^{\circ}\text{C}$                                                                                                                                       |                            | 13.2                                                 | 13.7           | —              |                  |

| $R_{L} = 10 \text{ k}, T_{A} = +25^{\circ}\text{C}$                                                                                                                                        |                            | 13.4<br>13.4                                         | 13.9<br>—      | _              |                  |

| $R_L = 10 \text{ k}, T_A = T_{\text{low to}} T_{\text{high}}$                                                                                                                              |                            | 13.4                                                 |                |                |                  |

| $R_L = 2.0 \text{ k}, T_A = +25^{\circ}\text{C}$<br>$R_L = 10 \text{ k}, T_A = +25^{\circ}\text{C}$                                                                                        | V <sub>OL</sub>            |                                                      | -14.1<br>-14.7 | -13.5<br>-14.1 |                  |

| $R_L = 10 \text{ k}, T_A = \pm 23 \text{ C}$<br>$R_L = 10 \text{ k}, T_A = T_{low to} T_{high}$                                                                                            |                            | _                                                    | -14.7          | -14.1          |                  |

| Dutput Short Circuit Current ( $T_A = +25^{\circ}C$ )                                                                                                                                      | I <sub>SC</sub>            |                                                      |                |                | mA               |

| Input Overdrive = 1.0 V, Output to Ground                                                                                                                                                  | -50                        |                                                      |                |                |                  |

| Source                                                                                                                                                                                     |                            | 20                                                   | 31             | —              |                  |

| Sink                                                                                                                                                                                       |                            | 20                                                   | 28             |                |                  |

| nput Common Mode Voltage Range<br>$T_A = +25^{\circ}C$                                                                                                                                     | V <sub>ICR</sub>           | (V <sub>EE</sub> +4.0) to<br>(V <sub>CC</sub> - 2.0) |                |                | V                |

|                                                                                                                                                                                            | CMRR                       | 70                                                   |                | 5)             | 40               |

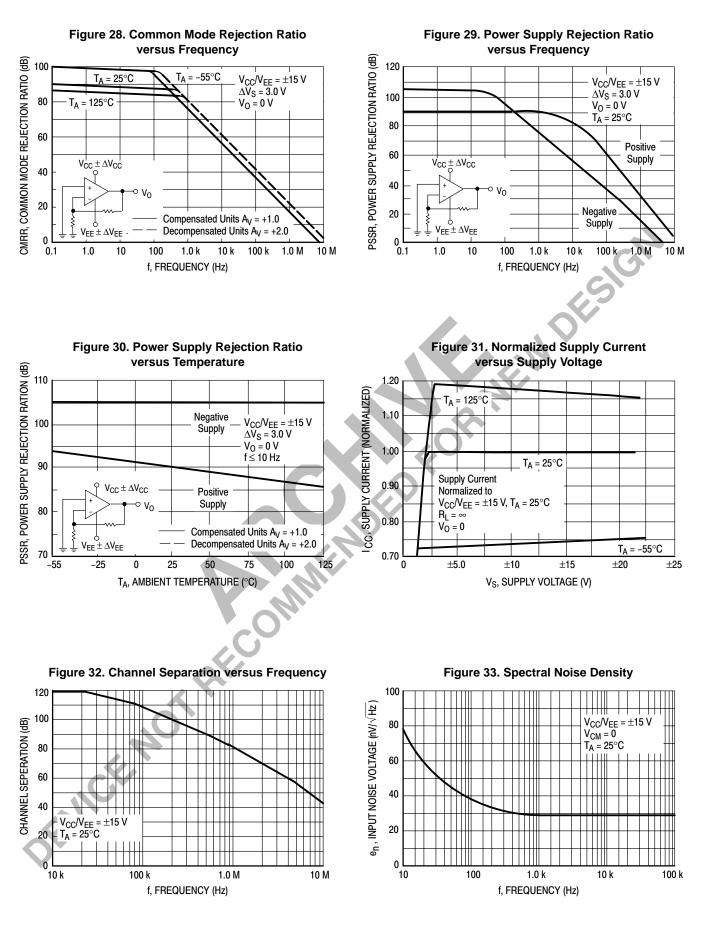

| Common Mode Rejection Ratio ( $R_S \le 10 \text{ k}, T_A = +25^{\circ}\text{C}$ )                                                                                                          | PSRR                       |                                                      | 90             |                | dB               |

| Power Supply Rejection Ratio ( $R_S = 100 \Omega$ , $T_A = 25^{\circ}C$ )                                                                                                                  |                            | 70                                                   | 86             |                | dB               |

| Power Supply Current<br>Single                                                                                                                                                             | Ι <sub>D</sub>             |                                                      |                |                | m/               |

| $T_A = +25^{\circ}C$                                                                                                                                                                       |                            |                                                      | 2.5            | 3.4            |                  |

| $T_A = T_{low}$ to $T_{high}$                                                                                                                                                              |                            |                                                      |                | 4.2            |                  |

| Single<br>$T_A = +25^{\circ}C$<br>$T_A = T_{low}$ to $T_{high}$<br>Dual<br>$T_A = +25^{\circ}C$<br>$T_A = +25^{\circ}C$<br>$T_A = -25^{\circ}C$                                            |                            | _                                                    | 4.9            | 6.0            |                  |

| $T_A = +25 \text{ G}$<br>$T_A = T_{low}$ to $T_{high}$                                                                                                                                     |                            |                                                      |                | 0.0<br>7.5     |                  |

| Quad                                                                                                                                                                                       |                            |                                                      |                |                |                  |

| $T_A = +25^{\circ}C$<br>T = T = to T                                                                                                                                                       |                            | -                                                    | 9.7            | 11             |                  |

| $T_A = T_{low}$ to $T_{high}$                                                                                                                                                              |                            | —                                                    | _              | 13             |                  |

| <b>TES:</b> (continued)<br>$3. T_{low} = 0^{\circ}C$ for MC34080B<br>$T_{high} = +70^{\circ}C$ for MC34080B                                                                                |                            |                                                      |                |                |                  |

| MC34081B MC34081B                                                                                                                                                                          |                            |                                                      |                |                |                  |

| MC34084 MC34084<br>MC34085 MC34085                                                                                                                                                         |                            |                                                      |                |                |                  |

| 4. See application information for typical changes in input offset voltage due to solderabili 5, Limits at $T_A = +25^{\circ}C$ are guaranteed by high temperature ( $T_{high}$ ) testing. | ity and temperature cycli  | ng.                                                  |                |                |                  |

| s anno at r <sub>A</sub> = 120 0 at guaranteed by high temperature (T <sub>high</sub> ) testing.                                                                                           |                            |                                                      |                |                |                  |

|                                                                                                                                                                                            |                            |                                                      |                |                |                  |

| Characteristics                                                                                                                                                          | Symbol         | Min                | Тур                  | Max | Unit         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------|----------------------|-----|--------------|

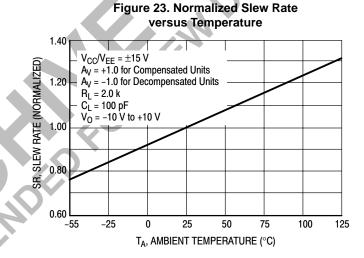

| $ \begin{array}{l} \mbox{Slew Rate } (V_{in} = -10 \ V \ to \ +10 \ V, \ R_L = 2.0 \ k\Omega, \ C_L = 100 \ pF) \\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $                 | SR             | 20<br>—<br>35<br>— | 25<br>30<br>50<br>50 |     | V/µs         |

| Settling Time (10 V Step, $A_V = -1.0$ )<br>To 0.10% ( $\pm^{1}/_2$ LSB of 9–Bits)<br>To 0.01% ( $\pm^{1}/_2$ LSB of 12–Bits)                                            | t <sub>s</sub> |                    | 0.72<br>1.6          |     | μs           |

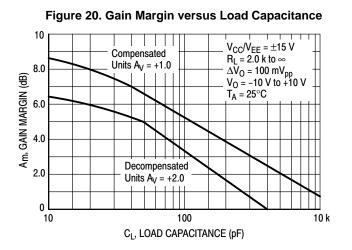

| Gain Bandwidth Product (f = 200 kHz)<br>Compensated<br>Decompensated                                                                                                     | GBW            | 6.0<br>12          | 8.0<br>16            |     | MHz          |

| Power Bandwidth (R <sub>L</sub> = 2.0 k, V <sub>O</sub> = 20 V <sub>pp</sub> , THD = 5.0%)<br>Compensated A <sub>V</sub> = +1.0<br>Decompensated A <sub>V</sub> = $-1.0$ | BWp            |                    | 400<br>800           | Ð   | kHz          |

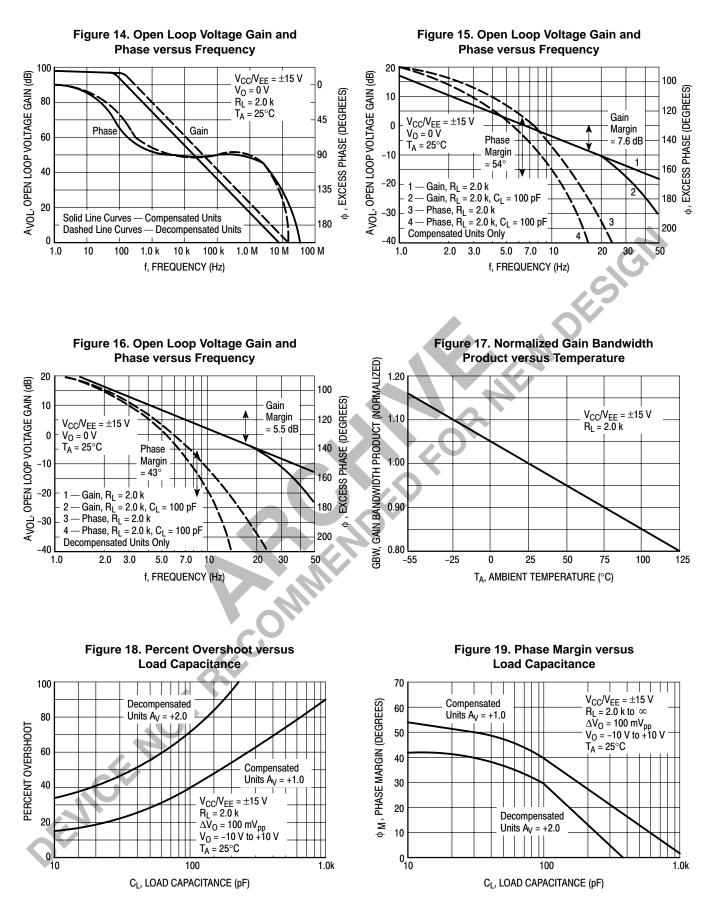

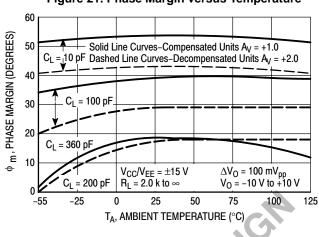

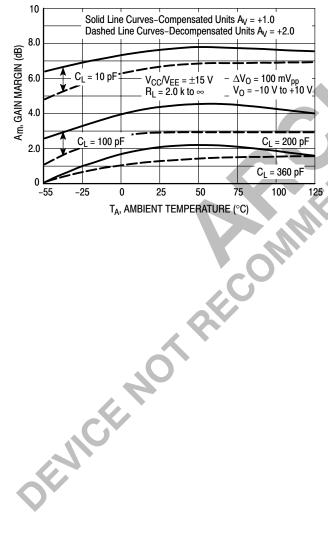

| Phase Margin (Compensated)<br>$R_L = 2.0 \text{ k}$<br>$R_L = 2.0 \text{ k}$ , $C_L = 100 \text{ pF}$                                                                    | φm             | _                  | 55<br>39             |     | De-<br>grees |

| Gain Margin (Compensated)<br>$R_L = 2.0 \text{ k}$<br>$R_L = 2.0 \text{ k}$ , $C_L = 100 \text{ pF}$                                                                     | A <sub>m</sub> | 4                  | 7.6<br>4.5           |     | dB           |

| Equivalent Input Noise Voltage<br>$R_S = 100 \Omega$ , f = 1.0 kHz                                                                                                       | e <sub>n</sub> | _                  | 30                   |     | nV/√Hz       |

| Equivalent Input Noise Current (f = 1.0 kHz)                                                                                                                             | l <sub>n</sub> | —                  | 0.01                 | _   | pA/√Hz       |

| Input Capacitance                                                                                                                                                        | C <sub>i</sub> | —                  | 5.0                  | _   | pF           |

| Input Resistance                                                                                                                                                         | r <sub>i</sub> | —                  | 10 <sup>12</sup>     | _   | Ω            |

| Total Harmonic Distortion $A_V = +10$ , $R_L = 2.0$ k, $2.0 \le V_O \le 20$ V <sub>pp</sub> , f = 10 kHz                                                                 | THD            | _                  | 0.05                 |     | %            |

| Channel Separation (f = 10 kHz)                                                                                                                                          | _              | —                  | 120                  |     | dB           |

| Open Loop Output Impedance (f = 1.0 MHz)                                                                                                                                 | Z <sub>o</sub> | _                  | 35                   | _   | Ω            |

#### AC ELECTRICAL CHARACTERISTICS (V<sub>CC</sub> = +15 V, V<sub>EE</sub> = - 15 V, T<sub>A</sub> = +25°C, unless otherwise noted.)

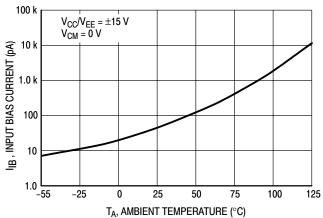

# Figure 2. Input Bias Current versus Temperature

Figure 22. Gain Margin versus Temperature

Figure 21. Phase Margin versus Temperature

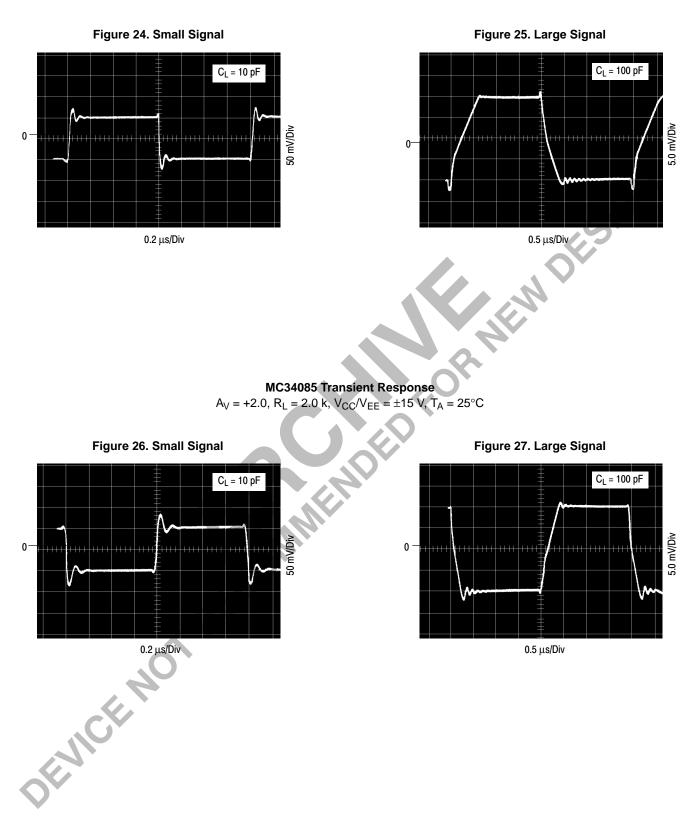

#### MC34084 Transient Response

A<sub>V</sub> = +1.0, R<sub>L</sub> = 2.0 k, V<sub>CC</sub>/V<sub>EE</sub> =  $\pm 15$  V, T<sub>A</sub> =  $25^{\circ}C$

#### **APPLICATIONS INFORMATION**

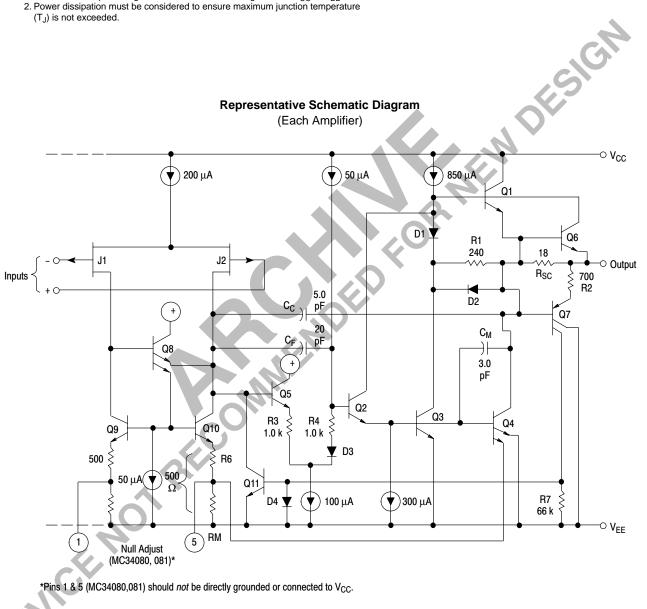

The bandwidth and slew rate of the MC34080 series is nearly double that of currently available general purpose JFET op-amps. This improvement in AC performance is due to the P-channel JFET differential input stage driving a compensated miller integration amplifier in conjunction with an all NPN output stage.

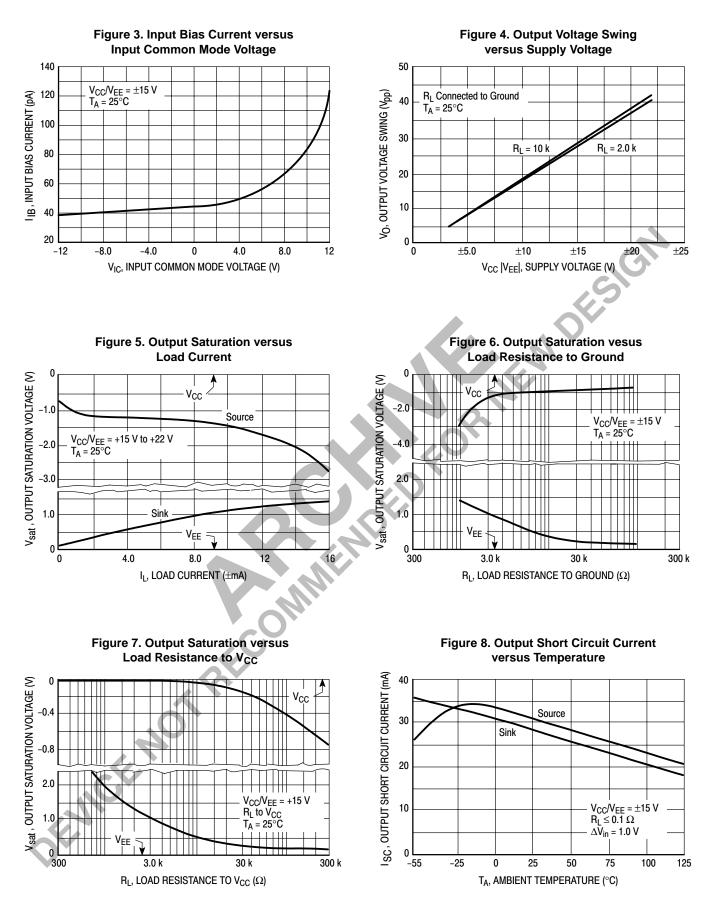

The all NPN output stage offers unique advantages over the more conventional NPN/PNP transistor Class AB output stage. With a 10 k load resistance, the op amp can typically swing within 1.0 V of the positive rail (V<sub>CC</sub>), and within 0.3 V of the negative rail (V<sub>EE</sub>), providing a 28.7 p–p swing from ±15 V supplies. This large output swing becomes most noticeable at lower supply voltages. If the load resistance is referenced to V<sub>CC</sub> instead of ground, the maximum possible output swing can be achieved for a given supply voltage. For light load currents, the load resistance will pull the output to V<sub>CC</sub> during the positive swing and the NPN output transistor will pull the output very near V<sub>EE</sub> during the negative swing. The load resistance value should be much less than that of the feedback resistance to maximize pull–up capability.

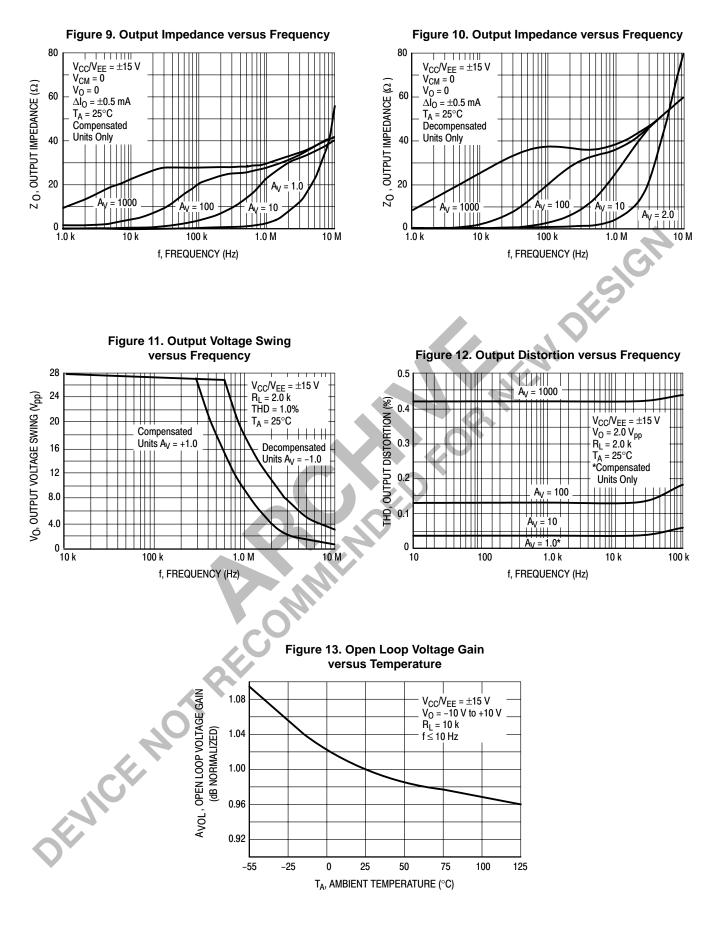

The all NPN transistor output stage is also inherently fast, contributing to the operation amplifier's high gain-bandwidth product and fast settling time. The associated high frequency output impedance is 50  $\Omega$  (typical) at 8.0 MHz. This allows driving capacitive loads from 0 pF to 300 pF without oscillations over the military temperature range, and over the full range of output swing. The 55°C phase margin and 7.6 dB gain margin as well as the general gain and phase characteristics are virtually independent of the sink/source output swing conditions. The high frequency characteristics of the MC34080 series is especially useful for active filter applications.

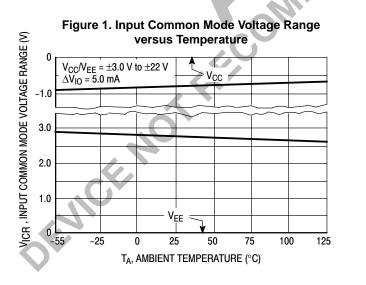

The common mode input range is from 2.0 V below the positive rail ( $V_{CC}$ ) to 4.0 V above the negative rail ( $V_{EE}$ ). The amplifier remains active if the inputs are biased at the positive rail. This may be useful for some applications in that single supply operation is possible with a single negative supply. However, a degradation of offset voltage and voltage gain may result.

Phase reversal does not occur if either the inverting or noninverting input (or both) exceeds the positive common mode limit. If either input (or both) exceeds the negative common mode limit, the output will be in the high state. The input stage also allows a differential up to  $\pm 44$  V, provided the maximum input voltage range is not exceeded. The supply voltage operating range is from  $\pm 5.0$  V to  $\pm 22$  V.

For optimum frequency performance and stability, careful component placement and printed circuit board layout should be exercised. For example, long unshielded input or output leads may result in unwanted input–output coupling. In order to reduce the input capacitance, resistors connected to the input pins should be physically close to these pins. This not only minimizes the input pole for optimum frequency response, but also minimizes extraneous "pickup" at this node.

Supply decoupling with adequate capacitance close to the supply pin is also important, particularly over temperature, since many types of decoupling capacitors exhibit large impedance changes over temperature.

Primarily due to the JFET inputs of the op amp, the input offset voltage may change due to temperature cycling and board soldering. After 20 temperature cycles (– 55° to 165°C), the typical standard deviation for input offset voltage is 559  $\mu$ V in the plastic packages. With respect to board soldering (260°C, 10 seconds), the typical standard deviation for input offset voltage is 525  $\mu$ V in the plastic package. Socketed devices should be used over a minimal temperature range for optimum input offset voltage performance.

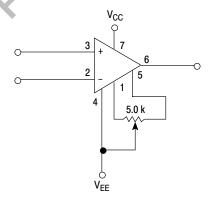

#### Figure 34. Offset Nulling Circuit

#### **OUTLINE DIMENSIONS**

#### OUTLINE DIMENSIONS

## MC34080 thru MC34085 NOTES

DEWICE NOT RECOMMENDED FOR MENDESIGN

## MC34080 thru MC34085 NOTES

DEWICE NOT RECOMMENDED FOR MENDESIGN

Committee Commit

**ON Semiconductor** is a trademark and is a registered trademark of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### PUBLICATION ORDERING INFORMATION

#### Literature Fulfillment:

Literature Distribution Center for ON Semiconductor

P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: ONlit@hibbertco.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

JAPAN: ON Semiconductor, Japan Customer Focus Center 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–0031 Phone: 81–3–5740–2700 Email: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local Sales Representative.