# Radiation Hardened, Ultra High Speed Current Feedback Amplifier with Offset Adjust

August 1996

#### Features

- Electrically Screened to SMD 5962F9675601VPA

- MIL-PRF-38535 Class V Compliant

- Low Distortion (HD3, 30MHz) ..... -84dBc (Typ)

- Wide -3dB Bandwidth ..... 850MHz (Typ)

- Very High Slew Rate ...... 2300V/µs (Typ)

- Fast Settling (0.1%) ..... 11ns (Typ)

- Excellent Gain Flatness (to 50MHz) ..... 0.05dB (Typ)

- High Output Current ..... 65mA (Typ)

- Latch Up ..... None (DI Technology)

#### Applications

- Video Switching and Routing

- Pulse and Video Amplifiers

- Wideband Amplifiers

- RF/IF Signal Processing

- Flash A/D Driver

- Imaging Systems

#### Description

The HS-1120RH is a radiation hardened, high speed, wideband, fast settling current feedback amplifier. These devices are QML approved and are processed and screened in full compliance with MIL-PRF-38535. Built with Intersil' proprietary, complementary bipolar UHF-1 (DI bonded wafer) process, it is the fastest monolithic amplifier available from any semiconductor manufacturer.

The HS-1120RH's wide bandwidth, fast settling characteristic, and low output impedance, make this amplifier ideal for driving fast A/D converters. Additionally, it offers offset voltage nulling capabilities as described in the "Offset Adjustment" section of this datasheet.

Component and composite video systems will also benefit from this amplifier's performance, as indicated by the excellent gain flatness, and 0.03%/0.05 Degree Differential Gain/Phase specifications (R<sub>1</sub> = 75 $\Omega$ ).

# Detailed electrical specifications are contained in SMD 5962F9675601VPA, available on the Intersil Website or AnswerFAX systems (document #967560)

A Cross Reference Table is available on the Intersil Website for conversion of Intersil Part Numbers to SMDs. The address is (http://www.intersil.com/datasheets/smd/smd\_xref. html)\_SMD numbers must be used to order Padiation Hard-

$\ensuremath{\textbf{html}}\xspace).$  SMD numbers must be used to order Radiation Hardened Products.

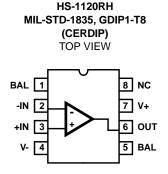

#### Ordering Information

| PART NUMBER           | TEMP.<br>RANGE ( <sup>o</sup> C) | PACKAGE     | PKG. NO. |

|-----------------------|----------------------------------|-------------|----------|

| 5962F9675601VPA       | -55 to 125                       | 8 Ld CERDIP | GDIP1-T8 |

| HFA1100IJ<br>(Sample) | -40 to 85                        | 8 Ld CERDIP | F8.3A    |

| HFA11XXEVAL           | Evaluation Boa                   | ard         |          |

#### Pinout

#### Application Information

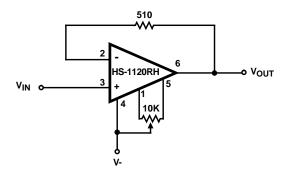

#### **Optimum Feedback Resistor**

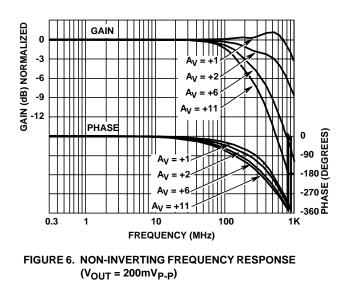

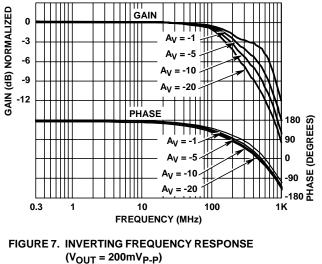

The enclosed plots of inverting and non-inverting frequency response illustrate the performance of the HS-1120RH in various gains. Although the bandwidth dependency on closed loop gain isn't as severe as that of a voltage feedback amplifier, there can be an appreciable decrease in bandwidth at higher gains. This decrease may be minimized by taking advantage of the current feedback amplifier's unique relationship between bandwidth and R<sub>F</sub>. All current feedback amplifiers require a feedback resistor, even for unity gain applications, and R<sub>F</sub>, in conjunction with the internal compensation capacitor, sets the dominant pole of the frequency response. Thus, the amplifier's bandwidth is inversely proportional to R<sub>F</sub>. The HS-1120RH design is optimized for a 510 $\Omega$  R<sub>F</sub> at a gain of +1. Decreasing R<sub>F</sub> in a unity gain application decreases stability, resulting in excessive peaking and overshoot. At higher gains the amplifier is more stable, so RF can be decreased in a tradeoff of stability for bandwidth.

The table below lists recommended  $\mathsf{R}_\mathsf{F}$  values for various gains, and the expected bandwidth.

| GAIN<br>(A <sub>CL</sub> ) | R <sub>F</sub> (Ω) | BANDWIDTH<br>(MHz) |

|----------------------------|--------------------|--------------------|

| -1                         | 430                | 580                |

| +1                         | 510                | 850                |

| +2                         | 360                | 670                |

| +5                         | 150                | 520                |

| +10                        | 180                | 240                |

| +19                        | 270                | 125                |

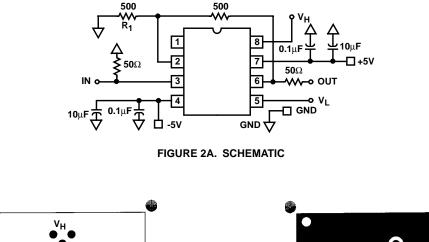

# PC Board Layout

The frequency response of this amplifier depends greatly on the amount of care taken in designing the PC board. The use of low inductance components such as chip resistors and chip capacitors is strongly recommended, while a solid ground plane is a must!

Attention should be given to decoupling the power supplies. A large value ( $10\mu$ F) tantalum in parallel with a small value ( $0.1\mu$ F) chip capacitor works well in most cases.

Terminated microstrip signal lines are recommended at the input and output of the device. Capacitance directly on the output must be minimized, or isolated as discussed in the next section.

Care must also be taken to minimize the capacitance to ground seen by the amplifier's inverting input (-IN). The larger this capacitance, the worse the gain peaking, resulting in pulse overshoot and possible instability. To this end, it is recommended that the ground plane be removed under traces connected to -IN, and connections to -IN should be kept as short as possible.

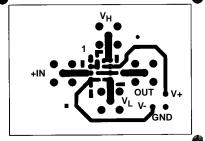

An example of a good high frequency layout is the Evaluation Board shown in Figure 2.

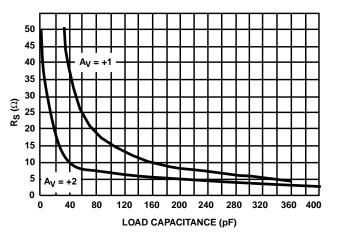

#### **Driving Capacitive Loads**

Capacitive loads, such as an A/D input, or an improperly terminated transmission line will degrade the amplifier's phase margin resulting in frequency response peaking and possible oscillations. In most cases, the oscillation can be avoided by placing a resistor ( $R_S$ ) in series with the output prior to the capacitance.

Figure 1 details starting points for the selection of this resistor. The points on the curve indicate the  $R_S$  and  $C_L$  combinations for the optimum bandwidth, stability, and settling time, but experimental fine tuning is recommended. Picking a point above or to the right of the curve yields an overdamped response, while points below or left of the curve indicate areas of underdamped performance.

$R_S$  and  $C_L$  form a low pass network at the output, thus limiting system bandwidth well below the amplifier bandwidth of 850MHz. By decreasing  $R_S$  as  $C_L$  increases (as illustrated in the curves), the maximum bandwidth is obtained without sacrificing stability. Even so, bandwidth does decrease as you move to the right along the curve. For example, at  $A_V = +1$ ,  $R_S = 50\Omega$ ,  $C_L = 30pF$ , the overall bandwidth is limited to 300MHz, and bandwidth drops to 100MHz at  $A_V = +1$ ,  $R_S = 5\Omega$ ,  $C_L = 340pF$ .

FIGURE 1. RECOMMENDED SERIES OUTPUT RESISTOR vs LOAD CAPACITANCE

# **Evaluation Board**

The performance of the HS-1120RH may be evaluated using the HFA11XXEVAL Evaluation Board.

The layout and schematic of the board are shown in Figure 2. To order evaluation boards, please contact your local sales office.

# Offset Adjustment

The output offset voltage of the HS-1120RH may be nulled via connections to the BAL pins. Unlike a voltage feedback amplifier, offset adjustment is accomplished by varying the sign and/or magnitude of the inverting input bias current ( $-I_{BIAS}$ ). With voltage feedback amplifiers, bias currents are matched and bias current induced offset errors are nulled by matching the impedances seen at the positive and negative inputs. Bias

currents are uncorrelated on current feedback amplifiers, so this technique is inappropriate.

-I<sub>BIAS</sub> flows through R<sub>F</sub> causing an output offset error. Likewise, any change in -I<sub>BIAS</sub> forces a corresponding change in output voltage, providing the capability for output offset adjustment. By nulling -I<sub>BIAS</sub> to zero, the offset error due to this current is eliminated. In addition, an adjustment limit greater than the -I<sub>BIAS</sub> limit allows the user to null the contributions from other error sources, such as V<sub>IO</sub>, or +IN

source impedance. For example, the excess adjust current of  $50\mu A [I_{BN}ADJ (Min) - I_{BSN} (Max)]$  allows for the nulling of an additional 26mV of output offset error (with  $R_F = 510\Omega$ ) at room temperature. The amount of adjustment is a function of  $R_F$ , so adjust range increases with increased  $R_F$ . If allowed by other considerations, such as bandwidth and noise,  $R_F$  can be increased to provide more adjustment range.

The recommended offset adjustment circuit is shown in Figure 3.

FIGURE 2C. BOTTOM LAYOUT

FIGURE 2B. TOP LAYOUT

FIGURE 2. EVALUATION BOARD SCHEMATIC AND LAYOUT

# Typical Performance Characteristics

Device Characterized at:  $V_{SUPPLY} = \pm 5V$ ,  $R_F = 360\Omega$ ,  $A_V = +2V/V$ ,  $R_L = 100\Omega$ , Unless Otherwise Specified

| PARAMETERS                           | CONDITIONS                                                                                                     | TEMPERATURE                 | TYPICAL         | UNITS              |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------|--------------------|

| Input Offset Voltage (Note 1)        | V <sub>CM</sub> = 0V                                                                                           | +25 <sup>0</sup> C          | 2               | mV                 |

| Average Offset Voltage Drift         | Versus Temperature                                                                                             | Full                        | 10              | μV/ <sup>o</sup> C |

| V <sub>IO</sub> CMRR                 | $\Delta V_{CM} = \pm 2V$                                                                                       | +25 <sup>0</sup> C          | 46              | dB                 |

| V <sub>IO</sub> PSRR                 | $\Delta V_{S} = \pm 1.25 V$                                                                                    | +25 <sup>0</sup> C          | 50              | dB                 |

| +Input Current (Note 1)              | $V_{CM} = 0V$                                                                                                  | +25°C                       | 25              | μA                 |

| Average +Input Current Drift         | Versus Temperature                                                                                             | Full                        | 40              | nA/ <sup>o</sup> C |

| -Input Current (Note 1)              | $V_{CM} = 0V$                                                                                                  | +25 <sup>0</sup> C          | 12              | μA                 |

| Average -Input Current Drift         | Versus Temperature                                                                                             | Full                        | 40              | nA/ <sup>o</sup> C |

| -Input Current Adjust Range          | V <sub>CM</sub> = 0V                                                                                           | +25 <sup>0</sup> C          | ±200            | μA                 |

| +Input Resistance                    | $\Delta V_{CM} = \pm 2V$                                                                                       | +25 <sup>0</sup> C          | 50              | kΩ                 |

| -Input Resistance                    |                                                                                                                | +25 <sup>0</sup> C          | 16              | Ω                  |

| Input Capacitance                    |                                                                                                                | +25 <sup>0</sup> C          | 2.2             | pF                 |

| Input Noise Voltage (Note 1)         | f = 100kHz                                                                                                     | +25°C                       | 4               | nV/√Hz             |

| +Input Noise Current (Note 1)        | f = 100kHz                                                                                                     | +25°C                       | 18              | pA/√Hz             |

| -Input Noise Current (Note 1)        | f = 100  kHz                                                                                                   | +25°C                       | 21              | pA/√Hz             |

| Input Common Mode Range              |                                                                                                                | Full                        | ±3.0            | V                  |

| Open Loop Transimpedance             | A <sub>V</sub> = -1                                                                                            | +25 <sup>o</sup> C          | 500             | kΩ                 |

| Output Voltage                       | $A_V = -1, R_L = 100\Omega$                                                                                    | +25°C                       | ±3.3            | V                  |

| output voltage                       | $A_V = -1, R_L = 100\Omega$                                                                                    | Full                        | ±3.0            | V                  |

| Output Current (Note 1)              | $A_V = -1, R_L = 50\Omega$                                                                                     | +25°C to +125°C             | ±65             | mA                 |

|                                      | $A_V = -1, R_L = 50\Omega$                                                                                     | -55°C to 0°C                | ±50             | mA                 |

| DC Closed Loop Output Resistance     | AV = 1, NL = 3022                                                                                              | +25°C                       | 0.1             | Ω                  |

| Quiescent Supply Current (Note 1)    | R <sub>I</sub> = Open                                                                                          | Full                        | 24              | mA                 |

| -3dB Bandwidth (Note 1)              | $A_V = -1, R_F = 430\Omega, V_{OUT} = 200 \text{mV}_{P-P}$                                                     | +25°C                       | 580             | MHz                |

|                                      | $A_V = +1, R_F = 510\Omega, V_{OUT} = 200 \text{mV}_{P-P}$                                                     | +25°C                       | 850             | MHz                |

|                                      | $A_V = +2, R_F = 360\Omega, V_{OUT} = 200 \text{mV}_{P-P}$                                                     | +25°C                       | 670             | MHz                |

| Slew Rate                            | $A_V = +2$ , $R_F = 30022$ , $V_{OUT} = 20011V_{P-P}$<br>$A_V = +1$ , $R_F = 510\Omega$ , $V_{OUT} = 5V_{P-P}$ | +25 C<br>+25 <sup>o</sup> C | 1500            | V/µs               |

|                                      | $A_V = +1$ , $K_F = 51022$ , $V_{OUT} = 5V_{P-P}$                                                              | +25°C                       | 2300            | V/μs<br>V/μs       |

| Full Power Bandwidth                 |                                                                                                                | +25°C                       | 2300            | ν/μs<br>MHz        |

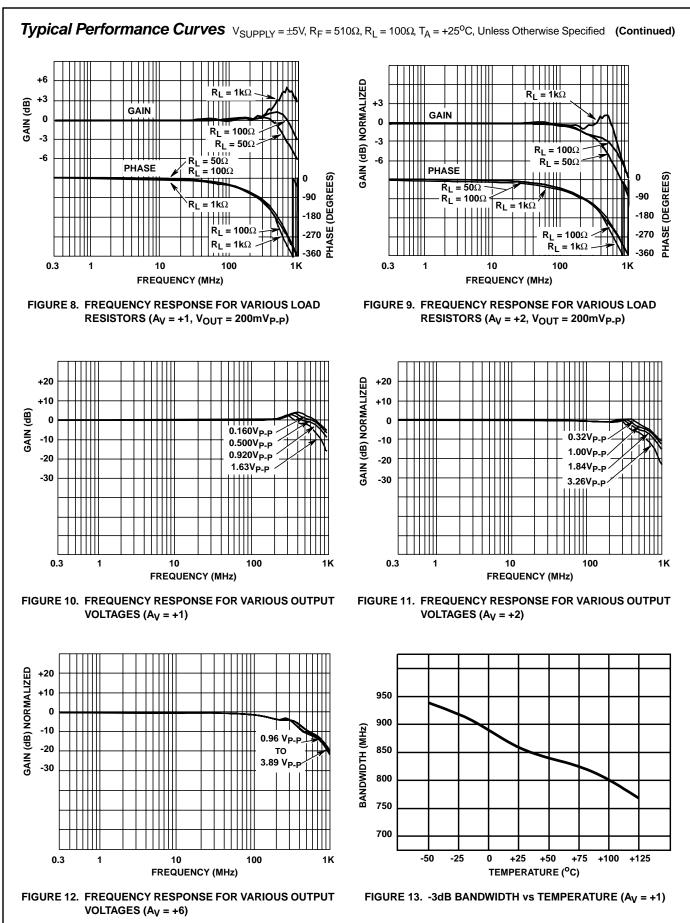

| Gain Flatness (Note 1)               | $V_{OUT} = 5V_{P-P}$<br>To 30MHz, R <sub>F</sub> = 510 $\Omega$                                                | +25 C<br>+25 <sup>0</sup> C |                 | dB                 |

| Gain Flatness (Note 1)               | To 50MHz, $R_F = 510\Omega$                                                                                    | +25°C<br>+25°C              | ±0.014<br>±0.05 | dB                 |

|                                      |                                                                                                                | +25°C<br>+25°C              |                 | dB                 |

| Linear Dhase Deviation (Note 1)      | To 100MHz, $R_F = 510\Omega$                                                                                   | +25°C<br>+25°C              | ±0.14           |                    |

| Linear Phase Deviation (Note 1)      | To 100MHz, $R_F = 510\Omega$                                                                                   | +25°C<br>+25°C              | ±0.6            | Degrees            |

| 2nd Harmonic Distortion (Note 1)     | $30MHz, V_{OUT} = 2V_{P-P}$                                                                                    | +25°C<br>+25°C              | -55             | dBc                |

|                                      | 50MHz, $V_{OUT} = 2V_{P-P}$                                                                                    | +25°C<br>+25°C              | -49             | dBc                |

|                                      | 100MHz, $V_{OUT} = 2V_{P-P}$                                                                                   |                             | -44             | dBc                |

| 3rd Harmonic Distortion (Note 1)     | $30MHz$ , $V_{OUT} = 2V_{P-P}$                                                                                 | +25 <sup>0</sup> C          | -84             | dBc                |

|                                      | 50MHz, $V_{OUT} = 2V_{P-P}$                                                                                    | +25°C                       | -70             | dBc                |

|                                      | 100MHz, $V_{OUT} = 2V_{P-P}$                                                                                   | +25°C                       | -57             | dBc                |

| 3rd Order Intercept (Note 1)         | $100MHz, R_{F} = 510\Omega$                                                                                    | +25 <sup>0</sup> C          | 30              | dBm                |

| 1dB Compression                      | $100MHz$ , $R_F = 510\Omega$                                                                                   | +25 <sup>o</sup> C          | 20              | dBm                |

| Reverse Isolation (S <sub>12</sub> ) | 40MHz, R <sub>F</sub> = 510Ω                                                                                   | +25 <sup>o</sup> C          | -70             | dB                 |

|                                      | 100MHz, R <sub>F</sub> = 510Ω                                                                                  | +25 <sup>0</sup> C          | -60             | dB                 |

|                                      | 600MHz, R <sub>F</sub> = 510Ω                                                                                  | +25 <sup>0</sup> C          | -32             | dB                 |

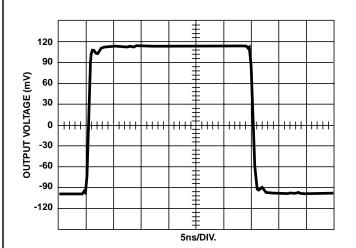

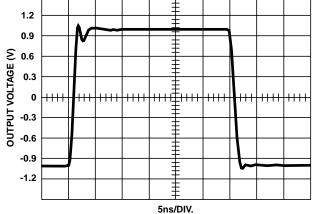

#### Typical Performance Characteristics (Continued)

Device Characterized at:  $V_{SUPPLY} = \pm 5V$ ,  $R_F = 360\Omega$ ,  $A_V = +2V/V$ ,  $R_L = 100\Omega$ , Unless Otherwise Specified (Continued)

| PARAMETERS              | CONDITIONS                                                           | TEMPERATURE        | TYPICAL | UNITS   |

|-------------------------|----------------------------------------------------------------------|--------------------|---------|---------|

| Rise and Fall Time      | $V_{OUT} = 0.5 V_{P-P}$                                              | +25 <sup>o</sup> C | 500     | ps      |

|                         | $V_{OUT} = 2V_{P-P}$                                                 | +25 <sup>0</sup> C | 800     | ps      |

| Overshoot (Note 1)      | $V_{OUT} = 0.5 V_{P-P}$ , Input $t_R/t_F = 550 ps$                   | +25 <sup>0</sup> C | 11      | %       |

| Settling Time (Note 1)  | To 0.1%, V <sub>OUT</sub> = 2V to 0V, R <sub>F</sub> = 510 $\Omega$  | +25 <sup>o</sup> C | 11      | ns      |

|                         | To 0.05%, V <sub>OUT</sub> = 2V to 0V, R <sub>F</sub> = 510 $\Omega$ | +25 <sup>o</sup> C | 19      | ns      |

|                         | To 0.02%, V <sub>OUT</sub> = 2V to 0V, $R_F$ = 510 $\Omega$          | +25 <sup>0</sup> C | 34      | ns      |

| Differential Gain       | $A_V = +2$ , $R_L = 75\Omega$ , NTSC                                 | +25 <sup>o</sup> C | 0.03    | %       |

| Differential Phase      | $A_V = +2$ , $R_L = 75\Omega$ , NTSC                                 | +25°C              | 0.05    | Degrees |

| Overdrive Recovery Time | $R_F = 510\Omega$ , $V_{IN} = 5V_{P-P}$                              | +25 <sup>o</sup> C | 7.5     | ns      |

NOTE:

1. See Typical Performance Curve for more information.

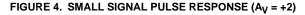

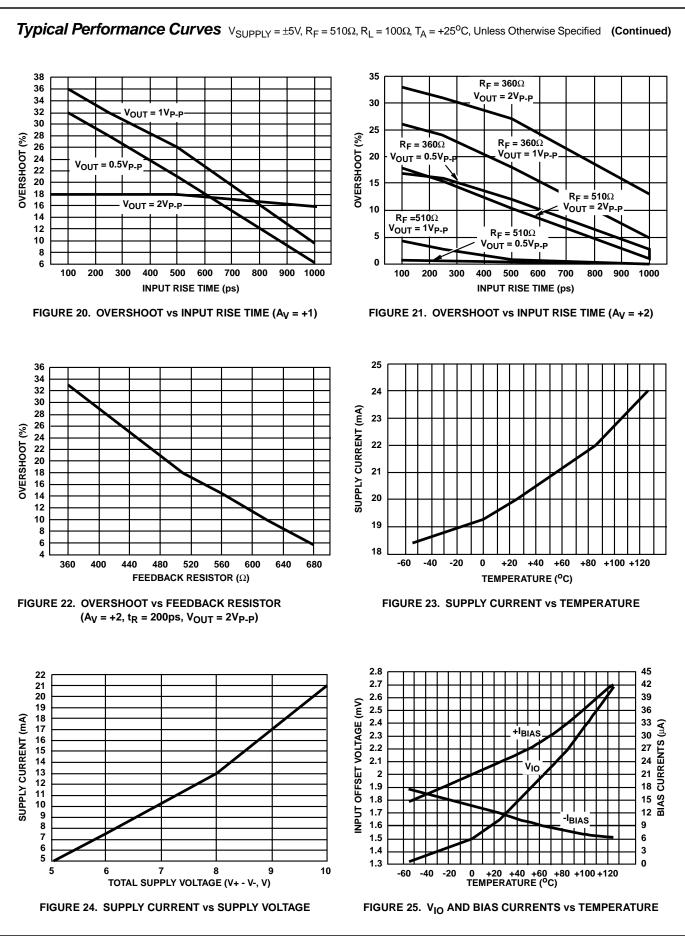

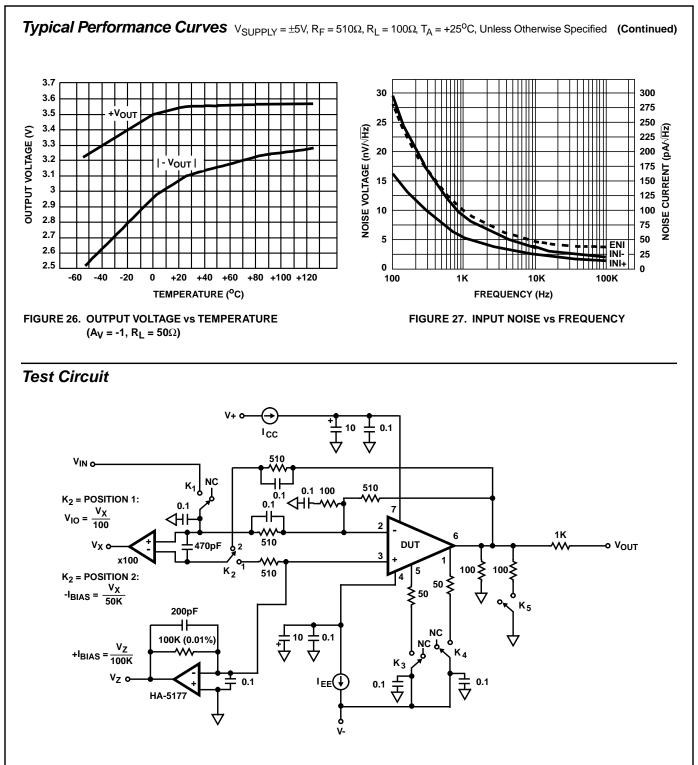

**Typical Performance Curves**  $V_{SUPPLY} = \pm 5V$ ,  $R_F = 510\Omega$ ,  $R_L = 100\Omega$ ,  $T_A = +25^{\circ}C$ , Unless Otherwise Specified

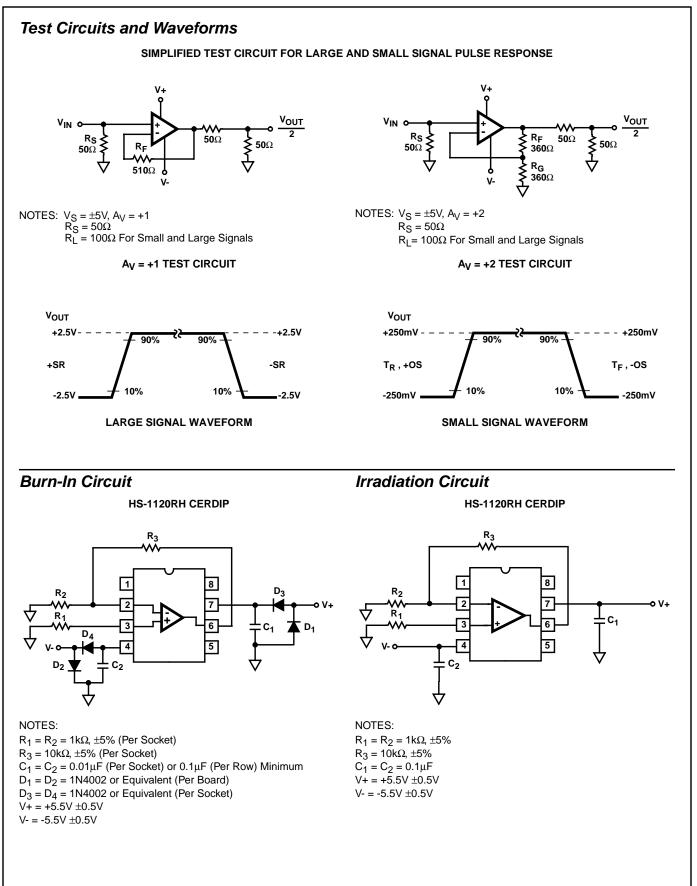

FIGURE 5. LARGE SIGNAL PULSE RESPONSE (A<sub>V</sub> = +2)

#### NOTES:

All resistors =  $\pm 1\%$  (Ω), unless otherwise noted All capacitors =  $\pm 10\%$  (µF), unless otherwise noted Chip Components Recommended

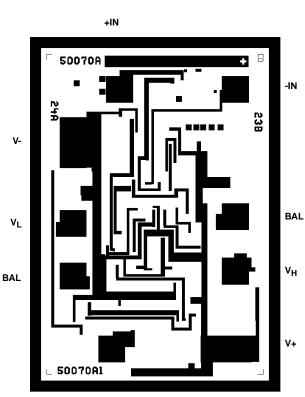

#### **Die Characteristics**

#### DIE DIMENSIONS:

63 mils x 44 mils x 19 mils ±1 mil 1600μm x 1130μm x 483μm ±25.4μm

#### **METALLIZATION:**

Type: Metal 1: AICu(2%)/TiW Thickness: Metal 1: 8kÅ ±0.4kÅ

Type: Metal 2: AICu(2%) Thickness: Metal 2: 16kÅ ±0.8kÅ

#### Metallization Mask Layout

GLASSIVATION: Type: Nitride Thickness: 4kÅ ±0.5kÅ

WORST CASE CURRENT DENSITY:  $1.6 \times 10^5 \text{ A/cm}^2$

TRANSISTOR COUNT: 52

SUBSTRATE POTENTIAL (Powered Up): Floating

HS-1120RH

OUT

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com