Data Sheet August 2001 File Number 3544.3

# Radiation Hardened Single 16/Differential 8 Channel CMOS Analog Multiplexers with Active Overvoltage Protection

The HS-0546RH and HS-0547RH are radiation hardened analog multiplexers with Active Overvoltage Protection and guaranteed ron matching. Analog input levels may greatly exceed either power supply without damaging the device or disturbing the signal path of other channels. Active protection circuitry assures that signal fidelity is maintained even under fault conditions that would destroy other multiplexers. Analog inputs can withstand constant 70V peak-to-peak levels with ±15V supplies and digital inputs will sustain continuous faults up to 4V greater than either supply. In addition, signal sources are protected from short circuiting should multiplexer supply loss occur: each input presents  $1k\Omega$  of resistance under this condition. These features make the HS-0546RH and HS-0547RH ideal for use in systems where the analog inputs originate from external equipment or separately powered circuitry. Both devices are fabricated with 44V dielectrically isolated CMOS technology. The HS-0546 is a 16 channel device and the HS-0547 is an 8 channel differential version. If input overvoltage protection is not needed, the HS-0506 and HS-0507 multiplexers are recommended.

Specifications for Rad Hard QML devices are controlled by the Defense Supply Center in Columbus (DSCC). The SMD numbers listed here must be used when ordering.

Detailed Electrical Specifications for these devices are contained in SMD 5962-95693. A "hot-link" is provided on our homepage for downloading. http://www.intersil.com

#### **Features**

- Electrically Screened to SMD # 5962-95693

- · QML Qualified per MIL-PRF-38535 Requirements

- Gamma Dose . . . . . . . . . . . . . . . . 1 x 10<sup>4</sup>RAD(Si)

- No Latch-Up

- · No Channel Interaction During Overvoltage

- Guaranteed r<sub>ON</sub> Matching

- · Break-Before-Make Switch

- Analog Signal Range.....±15V

- Access Time...... 1.0μs

# **Applications**

- · Data Acquisition Systems

- · Control Systems

- Telemetry

# Ordering Information

| ORDERING NUMBER | INTERNAL<br>MKT. NUMBER | TEMP. RANGE<br>(°C) |

|-----------------|-------------------------|---------------------|

| 5962D9569301V9A | HS0-0546RH-Q            | 25                  |

| 5962D9569301VXA | HS1-0546RH-Q            | -55 to 125          |

| 5962D9569301VXC | HS1B-0546RH-Q           | -55 to 125          |

| 5962D9569302V9A | HS0-0547RH-Q            | 25                  |

| 5962D9569302VXA | HS1-0547RH-Q            | -55 to 125          |

| 5962D9569302VXC | HS1B-0547RH-Q           | -55 to 125          |

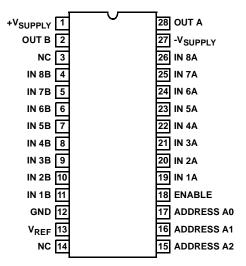

## **Pinouts**

Α

HS-0546RH GDIP1-T28 (CERDIP) OR CDIP2-T28 (SBDIP)

TOP VIEW

| V <sub>SUPPLY</sub> 1 | 5 | 28 OUT                  |

|-----------------------|---|-------------------------|

| NC 2                  |   | 27 -V <sub>SUPPLY</sub> |

| NC 3                  |   | 26 IN 8                 |

| IN 16 4               |   | 25 IN 7                 |

| IN 15 5               |   | 24 IN 6                 |

| IN 14 6               |   | 23 IN 5                 |

| IN 13 7               |   | 22 IN 4                 |

| IN 12 8               |   | 21 IN 3                 |

| IN 11 9               |   | 20 IN 2                 |

| IN 10 10              |   | 19 IN 1                 |

| IN 9 11               |   | 18 ENABLE               |

| GND 12                |   | 17 ADDRESS A0           |

| V <sub>REF</sub> 13   |   | 16 ADDRESS A1           |

| ADDRESS A3 14         |   | 15 ADDRESS A0           |

| -                     |   |                         |

# HS-0547RH GDIP1-T28 (CERDIP) OR CDIP2-T28 (SBDIP) TOP VIEW

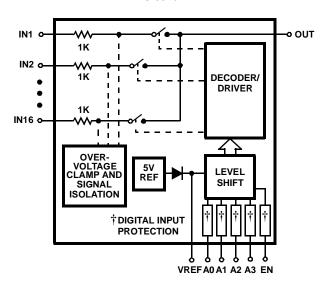

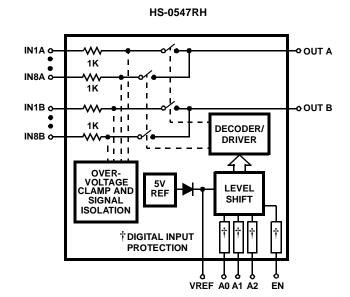

# **Functional Diagrams**

#### HS-0546RH

#### **HS-0546RH TRUTH TABLE**

| А3 | A2 | <b>A</b> 1 | A0 | EN | "ON"<br>CHANNEL |

|----|----|------------|----|----|-----------------|

| Х  | Х  | Х          | Х  | L  | NONE            |

| L  | L  | L          | L  | Н  | 1               |

| L  | L  | L          | Н  | Н  | 2               |

| L  | L  | Н          | L  | Н  | 3               |

| L  | L  | Н          | Н  | Н  | 4               |

| L  | Н  | L          | L  | Н  | 5               |

| L  | Н  | L          | Н  | Н  | 6               |

| L  | Н  | Н          | L  | Н  | 7               |

| L  | Н  | Н          | Н  | Н  | 8               |

| Н  | L  | L          | L  | Н  | 9               |

| Н  | L  | L          | Н  | Н  | 10              |

| Н  | L  | Н          | L  | Н  | 11              |

| Н  | L  | Н          | Н  | Н  | 12              |

| Н  | Н  | L          | L  | Н  | 13              |

| Н  | Н  | L          | Н  | Н  | 14              |

| Н  | Н  | Н          | L  | Н  | 15              |

| Н  | Н  | Н          | Н  | Н  | 16              |

#### **HS-0547RH TRUTH TABLE**

| A2 | <b>A</b> 1 | Α0 | EN | "ON" CHANNEL<br>PAIR |

|----|------------|----|----|----------------------|

| Х  | Х          | Х  | L  | NONE                 |

| L  | L          | L  | Н  | 1                    |

| L  | L          | Н  | Н  | 2                    |

| L  | Н          | L  | Н  | 3                    |

| L  | Н          | Н  | Н  | 4                    |

| Н  | L          | L  | Н  | 5                    |

| Н  | L          | Н  | Н  | 6                    |

| Н  | Н          | L  | Н  | 7                    |

| Н  | Н          | Н  | Н  | 8                    |

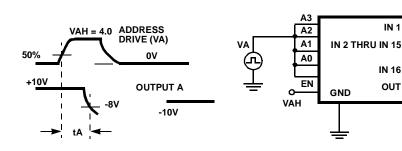

±10V

**∓10V**

VOUT

10K

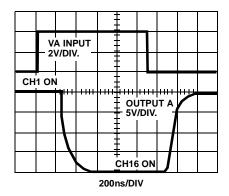

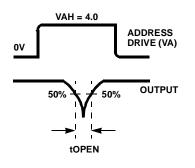

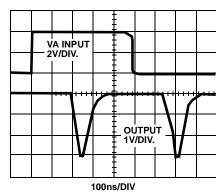

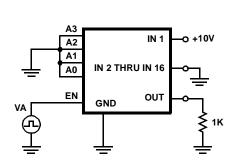

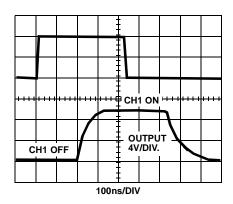

# Switching Waveforms

FIGURE 1. ACCESS TIME

FIGURE 2. BREAK-BEFORE-MAKE DELAY (tOPEN)

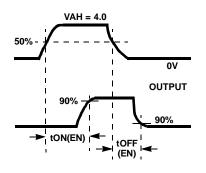

FIGURE 3. ENABLE DELAY tON(EN), tOFF(EN)

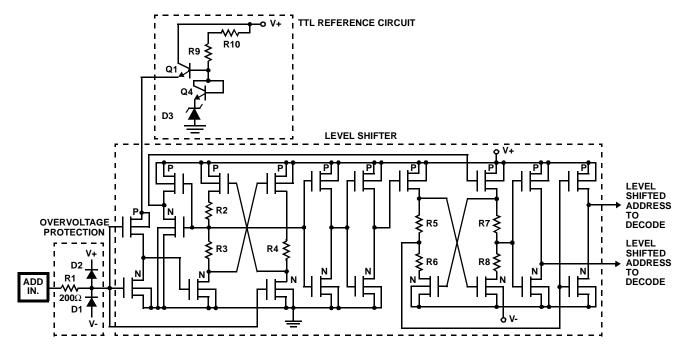

# Schematic Diagrams

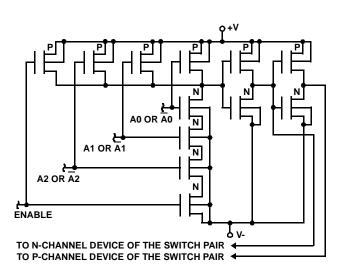

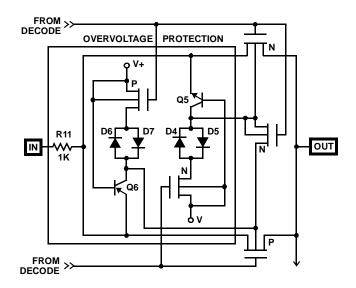

FIGURE 4. ADDRESS INPUT BUFFER AND LEVEL SHIFTER

FIGURE 5. ADDRESS DECODER

FIGURE 6. MULTIPLEX SWITCH

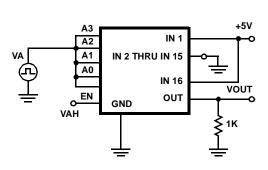

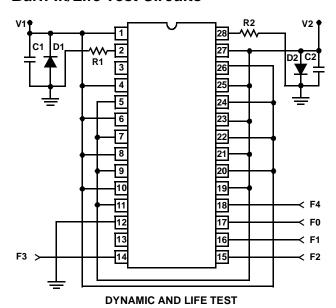

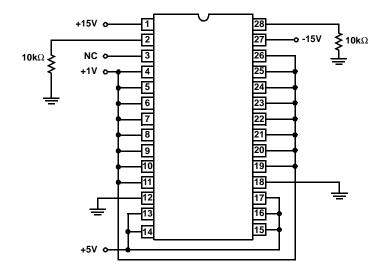

## **Burn-In/Life Test Circuits**

#### NOTES:

- 1. The Dynamic Test Circuit is utilized for all life testing.

- 2. V1 = +15V minimum, +16V maximum.

- 3. V2 = -15V maximum, -16V minimum.

- 4. R1, R2 =  $10k\Omega$ ,  $\pm 5\%$ , 1/4 or 1/2W (per socket).

- 5. C1, C2 =  $0.01 \mu F$  minimum (per socket) or  $0.1 \mu F$  minimum (per row).

- 6. D1, D2 = 1N4002 or equivalent (per board).

- 7. F0 = 100kHz, 10%; F1 = F0/2; F2 = F1/2; F3 = F2/2; F4 = F3/2 40% 60% duty cycle; VIL = 0.8V maximum; VIH = 4.0V minimum.

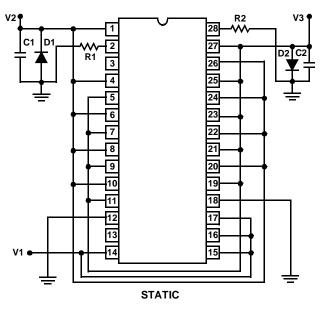

#### NOTES:

- 8. V1 = +5V minimum, +6V maximum.

- 9. V2 = +15V minimum, +16V maximum.

- 10. V3 = -15V maximum, -16V minimum.

- 11. R1, R2 =  $10k\Omega$ ,  $\pm 5\%$ , 1/4 or 1/2W (per socket).

- 12. C1, C2 =  $0.01\mu F$  minimum (per socket) or  $0.1\mu F$  minimum (per row).

- 13. D1, D2 = 1N4002 or equivalent (per board).

## Irradiation Circuit

5

#### Die Characteristics

**DIE DIMENSIONS:**

83.9 mils x 159 mils x 19 mils

**INTERFACE MATERIALS:**

Glassivation:

Type: Nitride

Thickness: 7kÅ ±0.7kÅ

**Top Metallization:**

Type: Al

Thickness: 16kÅ ±2kÅ

Substrate: CMOS, DI

# Metallization Mask Layout

ASSEMBLY RELATED INFORMATION:

**Substrate Potential:**

Unbiased (DI)

ADDITIONAL INFORMATION:

**Worst Case Current Density:**

$1.4 \times 10^5 \text{ A/cm}^2$

**Transistor Count:**

HS-0546 - 485 HS-0547 - 485

| HS-0546RH                           | HS-0547RH                           |

|-------------------------------------|-------------------------------------|

| EN A0 A1 A2 A3 V <sub>REF</sub> GND | EN A0 A1 A2 NC V <sub>REF</sub> GND |

| 18 17 16 15 14 13 12                | 18, 17, 16 15, 14 13 12             |

|                                     |                                     |

|                                     |                                     |

|                                     |                                     |

|                                     |                                     |

|                                     |                                     |

|                                     |                                     |

| IN 1 19 11 IN 9                     | IN 1A 19 11 IN 1B                   |

| IN 2 20 10 IN 10                    | IN 2A 20 10 IN 2B                   |

|                                     |                                     |

|                                     |                                     |

| IN 3 21 9 IN 11                     | IN 3A 21 9 IN 3B                    |

| IN 4 22 8 IN 12                     | IN 4A 22 8 IN 4B                    |

|                                     |                                     |

| IN 5 23 7 IN 13                     | IN 5A 23 7 IN 5B                    |

| IN 5 23 7 IN 13 IN 6 24 6 IN 14     | IN 5A 23 7 IN 5B IN 6A 24 6 IN 6B   |

|                                     |                                     |

|                                     |                                     |

| IN 7 25 5 IN 15                     | IN 7A 25 5 IN 7B                    |

| IN 8 26 4 IN 16                     | IN 8A 26 4 IN 8B                    |

|                                     |                                     |

| 27 28 690 1 1 28 8 2                | 27 28 690 2 (1)                     |

| -V OUT +V NC                        | -V OUT A +V OUT B                   |

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com