CA3273

April 1994 High-Side Driver

### **Features**

| • | <b>Equivalent High Pass P-N-P Transistor</b> |

|---|----------------------------------------------|

| • | Current Limiting0.6A to 1.2A                 |

| • | Over-Voltage Shutdown+25V to +40V            |

| • | Junction Temperature Thermal Limit+150°C     |

# **Applications**

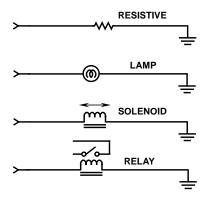

- Fuel Pump Driver

- Relay Driver

- Solenoid Driver

- Stepper Motor Driver

- · Remote Power Switch

- · Logic Control Switch

## Description

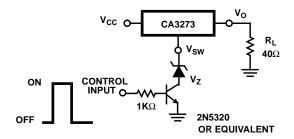

The CA3273 is a power IC equivalent of a P-N-P pass transistor operated as a high-side-driver current switch in either the saturated (ON) or cutoff (OFF) modes. The CA3273 incorporates circuitry to protect the pass currents, excessive input voltage, and thermal overstress. The high-side driver is intended for general purpose, automotive and potentially high-stress applications. If high-stress conditions exist, the use of an external zener diode of 35V or less between supply and load terminals may be required to prevent damage due to severe conditions (such as load dump, reverse battery and positive or negative transients). The CA3273 is designed to withstand a nominal reverse-battery (VBAT = 13V) condition without permanent damage to the IC. The CA3273 is supplied in a modified 3-lead TO-202 plastic power package.

## **Ordering Information**

| PART<br>NUMBER | TEMPERATURE<br>RANGE | PACKAGE             |  |  |

|----------------|----------------------|---------------------|--|--|

| CA3273         | -40°C to +85°C       | TO-202 Modified SIP |  |  |

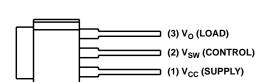

#### Pinout

CA3273 (SIP) TOP VIEW

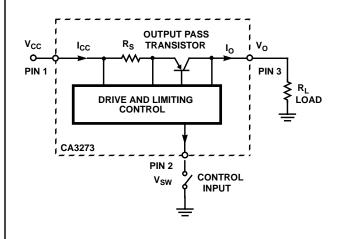

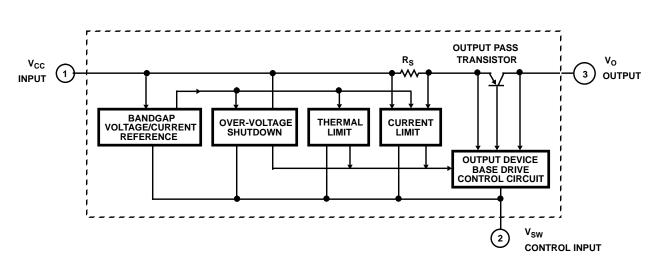

# **Block Diagram**

# Specifications CA3273

# Absolute Maximum Ratings Thermal Information

| Fault Max, Supply Voltage, V <sub>CC</sub>                                                 |

|--------------------------------------------------------------------------------------------|

| Maximum Operating V <sub>CC</sub> :                                                        |

| At $I_O = 400 \text{mA} (-40^{\circ} \text{C to} + 85^{\circ} \text{C Ambient}) \dots 16V$ |

| At $I_0 = 600 \text{mA} (-40^{\circ} \text{C to } +25^{\circ} \text{C Ambient}) \dots 24V$ |

| Max. Positive Output Peak Pulse, V <sub>SW</sub> OpenV <sub>CC</sub> +12V                  |

| Max. Operating Output Load Current600mA                                                    |

| Short Circuit Load Current, I <sub>SC</sub> Internal Limiting                              |

| Reverse Battery                                                                            |

| Thermal Resistance $\theta$ Plastic SIP Package | ,, ,                         |

|-------------------------------------------------|------------------------------|

| At +25°C Ambient, T <sub>A</sub> (Note 1)       | N/°C<br>50°C<br>85°C<br>50°C |

|                                                 |                              |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

### **Electrical Specifications** $T_A = -40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ , Unless Otherwise Noted, See Block Diagram for Test Pin Reference

| PARAMETERS                                            | SYMBOL               | TEST CONDITIONS                                                            | MIN  | TYP | MAX  | UNITS |

|-------------------------------------------------------|----------------------|----------------------------------------------------------------------------|------|-----|------|-------|

| Operating Voltage Range                               | V <sub>CC</sub>      | V <sub>CC</sub> Reference to V <sub>SW</sub>                               | 4    | -   | 24   | V     |

| Saturation Voltage(V <sub>CC</sub> - V <sub>O</sub> ) | V <sub>SAT</sub>     | $I_{O} = -400 \text{mA}, V_{SW} = 0 \text{V}, V_{CC} = 16 \text{V}$        | -    | -   | 0.5  | V     |

| Operating Load                                        | $R_{L}$              | V <sub>SW</sub> = 0V (Switch ON)                                           |      |     |      |       |

|                                                       |                      | $T_A = +85^{\circ}C, V_{CC} = 16V$                                         | 40   | -   | -    | Ω     |

|                                                       |                      | $T_A = +25^{\circ}C, V_{CC} = 24V$                                         | 40   |     |      | Ω     |

| Over-Voltage Shutdown Threshold                       | V <sub>CC(THD)</sub> | $V_{SW}$ = 0V, $R_L$ = 1k $\Omega$ , Increase $V_{CC}$ , ( $V_O$ goes low) | 25   | 33  | 40   | V     |

| Over-Current Limiting                                 | I <sub>O(LIM)</sub>  | V <sub>CC</sub> =16V, V <sub>SW</sub> = 1V (Switch ON)                     | -    | -   | 1.2  | А     |

| Over-Temperature Limiting                             | T <sub>LIM</sub>     |                                                                            | -    | 150 | -    | °C    |

| Control Current, Switch ON                            | I <sub>SW</sub>      | V <sub>CC</sub> =16V, V <sub>SW</sub> = 0V                                 |      |     |      |       |

|                                                       |                      | $I_O = 0mA$                                                                | -    | -15 | -    | mA    |

|                                                       |                      | I <sub>O</sub> = -400mA                                                    | -    | -22 | -    | mA    |

| Control Current, Max. Load,<br>Switch ON              |                      | V <sub>CC</sub> = 24V, V <sub>SW</sub> = 0V,<br>I <sub>O</sub> = -600mA    | -    | -33 | -    | mA    |

| Max. Control Current, High and                        | I <sub>SW(MAX)</sub> | $R_L = 40\Omega$ , $V_{SW} = 1V$                                           |      |     |      |       |

| ow V <sub>CC</sub>                                    |                      | V <sub>CC</sub> = 24V                                                      | -50  | -   | -    | mA    |

|                                                       |                      | V <sub>CC</sub> = 7V                                                       | -50  | -   | -    | mA    |

| Min. Control Current, No Load,                        | I <sub>SW(NL)</sub>  | V <sub>O</sub> = Open, (Switch OFF)                                        |      |     |      |       |

| Switch OFF                                            |                      | $V_{CC} = 24V, V_{SW} = 23V$                                               | -200 | -   | +50  | μΑ    |

|                                                       |                      | V <sub>CC</sub> = 7V, V <sub>SW</sub> = 6V                                 | -200 | -   | +50  | μΑ    |

| Output Current Leakage                                | I <sub>O(LEAK)</sub> | $V_O = 0V$ , $V_{CC} = 16V$ , (Switch OFF)                                 |      |     |      |       |

|                                                       |                      | V <sub>SW</sub> =16V                                                       | -100 | -   | +100 | μΑ    |

|                                                       |                      | V <sub>SW</sub> =15V                                                       | -100 | -   | +100 | μА    |

#### NOTES:

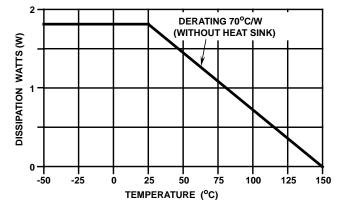

- 1. The calculation for dissipation and junction temperature rise due to dissipation is:  $P_D = (V_{CC} V_O) \times I_O + V_{CC} \times I_{SW}$  and  $T_J = T_A + P_D \times \theta_{JA}$  where  $T_J$  is device junction temperature,  $T_A$  is ambient temperature and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.

- 2. Thermal limiting occurs at +150°C on the chip.

FIGURE 1. FUNCTIONAL BLOCK DIAGRAM OF CA3273

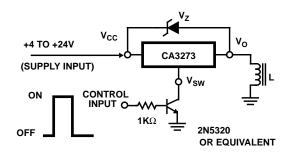

FIGURE 2. TYPICAL APPLICATION WITH ZENER DIODE FOR OVER-VOLTAGE PROTECTION WITH INDUCTIVE LOAD SWITCHING.  $V_Z$  SHOULD BE LESS THAN 35V. WHEN CURRENT IS SWITCHED OFF IN THE OUTPUT LOAD (L), THE INDUCTIVE KICK PULSE GOES NEGATIVE. THE CLAMPED CLAMP LEVEL OF THE NEGATIVE GOING PULSE IS  $V_{CC}$  -  $V_Z$ .

FIGURE 4. DISSIPATION DERATING CURVES

FIGURE 3. OPTIONAL RANGE SHIFTING OF THE  $V_{CC}$  INPUT VOLTAGE USING A ZENER DIODE TO OFFSET THE  $V_{SW}$  CONTROL PIN. (I.E.,THE OVER-VOLTAGE SHUTDOWN THRESHOLD WILL BE INCREASED TO  $V_{CC}$  OPERATING VOLTAGE IS  $V_Z + 4V$ ).

FIGURE 5. TYPICAL LOADS

| 1             |                                                                                                                                                                                                                                                                                                                           |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |                                                                                                                                                                                                                                                                                                                           |

|               |                                                                                                                                                                                                                                                                                                                           |

|               |                                                                                                                                                                                                                                                                                                                           |

|               |                                                                                                                                                                                                                                                                                                                           |

|               |                                                                                                                                                                                                                                                                                                                           |

| 1             |                                                                                                                                                                                                                                                                                                                           |

| 1             |                                                                                                                                                                                                                                                                                                                           |

|               |                                                                                                                                                                                                                                                                                                                           |

|               |                                                                                                                                                                                                                                                                                                                           |

| All Inter     | il semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.                                                                                                                                                                                                             |

| l             |                                                                                                                                                                                                                                                                                                                           |

| intersil prod | cts are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without                                                                                                                                                                     |

| and reliable  | dingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which |

| mav result fi | om its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.                                                                                                                                                                                          |

|               |                                                                                                                                                                                                                                                                                                                           |

|               | For information regarding Intersil Corporation and its products, see web site http://www.intersil.com                                                                                                                                                                                                                     |

|               |                                                                                                                                                                                                                                                                                                                           |

| I             |                                                                                                                                                                                                                                                                                                                           |