# Regarding the change of names mentioned in the document, such as Hitachi Electric and Hitachi XX, to Renesas Technology Corp.

The semiconductor operations of Mitsubishi Electric and Hitachi were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Renesas Technology Home Page: http://www.renesas.com

Renesas Technology Corp. Customer Support Dept. April 1, 2003

#### **Cautions**

Keep safety first in your circuit designs!

Renesas Technology Corporation puts the maximum effort into making semiconductor products better

and more reliable, but there is always the possibility that trouble may occur with them. Trouble with

semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate

measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or

(iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- 1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corporation or a third party.

- 2. Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

$4 \text{ M SRAM} (256\text{-kword} \times 16\text{-bit})$

ADE-203-975B (Z) Rev. 2.0 Oct. 14, 1999

#### **Description**

The Hitachi HM62V16258B Series is 4-Mbit static RAM organized 262,144-word × 16-bit. HM62V16258B Series has realized higher density, higher performance and low power consumption by employing Hi-CMOS process technology. It offers low power standby power dissipation; therefore, it is suitable for battery backup systems. It is packaged in standard 44-pin plastic TSOPII.

#### **Features**

Single 3.0 V supply: 2.7 V to 3.6 V

Fast access time: 70 ns/85 ns (max)

• Power dissipation:

— Active: 9 mW (typ)— Standby: 3 μW (typ)

- Completely static memory.

- No clock or timing strobe required

- Equal access and cycle times

- Common data input and output.

- Three state output

- Battery backup operation.

## **Ordering Information**

| Type No.                                 | Access time    | Package                                                     |

|------------------------------------------|----------------|-------------------------------------------------------------|

| HM62V16258BLTT-7<br>HM62V16258BLTT-8     | 70 ns<br>85 ns | 400-mil 44-pin plastic TSOPII (normal-bend type) (TTP-44DB) |

| HM62V16258BLTT-7SL<br>HM62V16258BLTT-8SL | 70 ns<br>85 ns |                                                             |

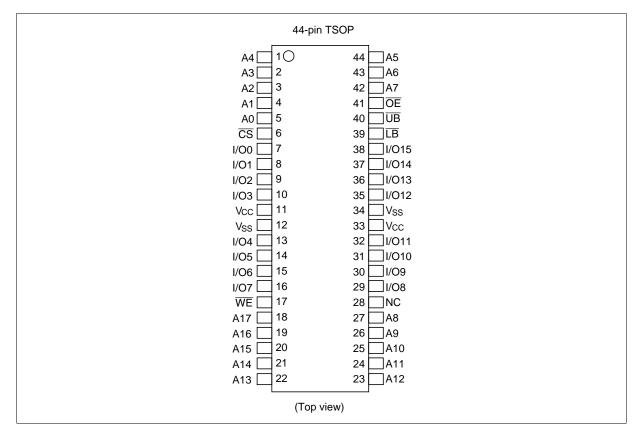

#### **Pin Arrangement**

#### **Pin Description**

| Pin name        | Function          |

|-----------------|-------------------|

| A0 to A17       | Address input     |

| I/O0 to I/O15   | Data input/output |

| CS              | Chip select       |

| WE              | Write enable      |

| ŌĒ              | Output enable     |

| LB              | Lower byte select |

| ŪB              | Upper byte select |

| V <sub>cc</sub> | Power supply      |

| V <sub>ss</sub> | Ground            |

| NC              | No connection     |

3

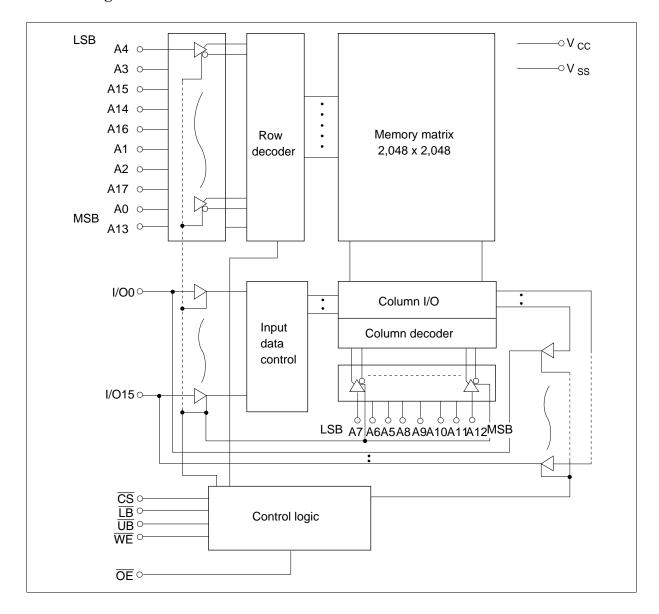

#### **Block Diagram**

#### **Operation Table**

| CS | WE | OE | UB | LB | I/O0 to I/O7 | I/O8 to I/O15 | Operation        |

|----|----|----|----|----|--------------|---------------|------------------|

| Н  | ×  | ×  | ×  | ×  | High-Z       | High-Z        | Standby          |

| ×  | ×  | ×  | Н  | Н  | High-Z       | High-Z        | Standby          |

| L  | Н  | L  | L  | L  | Dout         | Dout          | Read             |

| L  | Н  | L  | Н  | L  | Dout         | High-Z        | Lower byte read  |

| L  | Н  | L  | L  | Н  | High-Z       | Dout          | Upper byte read  |

| L  | L  | ×  | L  | L  | Din          | Din           | Write            |

| L  | L  | ×  | Н  | L  | Din          | High-Z        | Lower byte write |

| L  | L  | ×  | L  | Н  | High-Z       | Din           | Upper byte write |

| L  | Н  | Н  | ×  | ×  | High-Z       | High-Z        | Output disable   |

Note:  $H: V_{IH}, L: V_{IL}, \times: V_{IH} \text{ or } V_{IL}$

#### **Absolute Maximum Ratings**

| Parameter                                               | Symbol          | Value                              | Unit |

|---------------------------------------------------------|-----------------|------------------------------------|------|

| Power supply voltage relative to $V_{\rm SS}$           | V <sub>cc</sub> | -0.5 to + 4.6                      | V    |

| Terminal voltage on any pin relative to V <sub>ss</sub> | V <sub>T</sub>  | $-0.5^{*1}$ to $V_{CC} + 0.3^{*2}$ | V    |

| Power dissipation                                       | P <sub>T</sub>  | 1.0                                | W    |

| Storage temperature range                               | Tstg            | -55 to +125                        | °C   |

| Storage temperature range under bias                    | Tbias           | -10 to +85                         | °C   |

Notes: 1.  $V_T$  min: -3.0 V for pulse half-width  $\leq 30$  ns.

2. Maximum voltage is +4.6 V.

#### **DC Operating Conditions**

| Parameter                 | Symbol          | Min  | Тур | Max                   | Unit | Note |

|---------------------------|-----------------|------|-----|-----------------------|------|------|

| Supply voltage            | V <sub>cc</sub> | 2.7  | 3.0 | 3.6                   | V    |      |

|                           | V <sub>SS</sub> | 0    | 0   | 0                     | V    |      |

| Input high voltage        | V <sub>IH</sub> | 2.0  | _   | V <sub>cc</sub> + 0.3 | V    |      |

| Input low voltage         | V <sub>IL</sub> | -0.3 | _   | 0.6                   | V    | 1    |

| Ambient temperature range | Та              | 0    | _   | 70                    | °C   |      |

Note: 1.  $V_{IL}$  min: -3.0 V for pulse half-width  $\leq 30$  ns.

#### **DC** Characteristics

| Parameter                 |               | Symbol              | Min        | Typ*1 | Max | Unit | Test conditions                                                                                                                                                                                                                                                       |

|---------------------------|---------------|---------------------|------------|-------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input leaka               | age current   | I <sub>LI</sub>     | _          | _     | 1   | μΑ   | $Vin = V_{SS}$ to $V_{CC}$                                                                                                                                                                                                                                            |

| Output leakage current    |               | I <sub>LO</sub>     | _          | _     | 1   | μΑ   | $\frac{\overline{CS}}{\overline{LB}} = \frac{V_{IH}}{\overline{UB}} \text{ or } \overline{\overline{OE}} = V_{IH} \text{ or } \overline{\overline{WE}} = V_{IL} \text{ or,}$ $\overline{LB} = \overline{\overline{UB}} = V_{IH}, V_{I/O} = V_{SS} \text{ to } V_{CC}$ |

| Operating                 | current       | $I_{cc}$            | _          | _     | 20  | mA   | $\overline{\text{CS}} = \text{V}_{\text{IL}}, \text{ Others} = \text{V}_{\text{IH}}/\text{V}_{\text{IL}}, \text{ I}_{\text{I/O}} = \text{0 mA}$                                                                                                                       |

| Average operating current | operating     |                     | _          | _     | 70  | mA   | Min. cycle, duty = 100%, $I_{I/O} = 0$ mA, $\overline{CS} = V_{IL}$ , Others = $V_{IH}/V_{IL}$                                                                                                                                                                        |

|                           | HM62V16258B-8 | I <sub>CC1</sub>    | _          | _     | 65  | mΑ   | <del>-</del>                                                                                                                                                                                                                                                          |

|                           |               | I <sub>CC2</sub>    | _          | 3     | 15  | mA   | $\begin{split} &\text{Cycle time} = 1  \mu\text{s, duty} = 100\%, \\ &I_{\text{I/O}} = 0 \text{ mA, } \overline{\text{CS}} \leq 0.2 \text{ V,} \\ &V_{\text{IH}} \geq V_{\text{CC}} - 0.2 \text{ V, } V_{\text{IL}} \leq 0.2 \text{ V} \end{split}$                   |

| Standby c                 | urrent        | $I_{\text{SB}}$     | _          | _     | 0.3 | mA   | $\overline{\text{CS}} = V_{IH}$                                                                                                                                                                                                                                       |

| Standby c                 | urrent        | *2<br>  SB1         | _          | 1     | 40  | μΑ   | $ \begin{array}{c} 0 \text{ V} \leq \text{Vin} \\ \overline{\text{CS}} \geq \text{V}_{\text{CC}} - 0.2 \text{ V} \end{array} $                                                                                                                                        |

|                           |               | I <sub>SB1</sub> *3 | _          | 1     | 20  | μΑ   |                                                                                                                                                                                                                                                                       |

| Output hig                | jh voltage    | $V_{OH}$            | 2.4        | _     | _   | V    | $I_{OH} = -1 \text{ mA}$                                                                                                                                                                                                                                              |

|                           |               |                     | $V_{cc}$ – | 0.2—  | _   | V    | $I_{OH} = -100 \mu A$                                                                                                                                                                                                                                                 |

| Output low                | v voltage     | $V_{OL}$            | _          | _     | 0.4 | V    | I <sub>OL</sub> = 2 mA                                                                                                                                                                                                                                                |

|                           |               |                     | _          | _     | 0.2 | V    | $I_{OL} = 100 \mu A$                                                                                                                                                                                                                                                  |

Notes: 1. Typical values are at  $V_{CC} = 3.0 \text{ V}$ ,  $Ta = +25^{\circ}\text{C}$  and not guaranteed.

- 2. This characteristic is guaranteed only for L version.

- 3. This characteristic is guaranteed only for L-SL version.

#### **Capacitance** (Ta = +25°C, f = 1.0 MHz)

| Parameter                | Symbol           | Min | Тур | Max | Unit | Test conditions | Note |

|--------------------------|------------------|-----|-----|-----|------|-----------------|------|

| Input capacitance        | Cin              | _   | _   | 8   | pF   | Vin = 0 V       | 1    |

| Input/output capacitance | C <sub>I/O</sub> | _   | _   | 10  | pF   | $V_{I/O} = 0 V$ | 1    |

Note: 1. This parameter is sampled and not 100% tested.

AC Characteristics (Ta = 0 to +70°C,  $V_{CC} = 2.7$  V to 3.6 V, unless otherwise noted.)

#### **Test Conditions**

• Input pulse levels:  $V_{IL} = 0.4 \text{ V}$ ,  $V_{IH} = 2.2 \text{ V}$

• Input rise and fall time: 5 ns

• Input timing reference levels: 1.4 V

• Output timing reference levels: 1.4 V

• Output load: 1 TTL + 30 pF (HM62V16258B-7) (Including scope and jig)

1 TTL + 100 pF (HM62V16258B-8) (Including scope and jig)

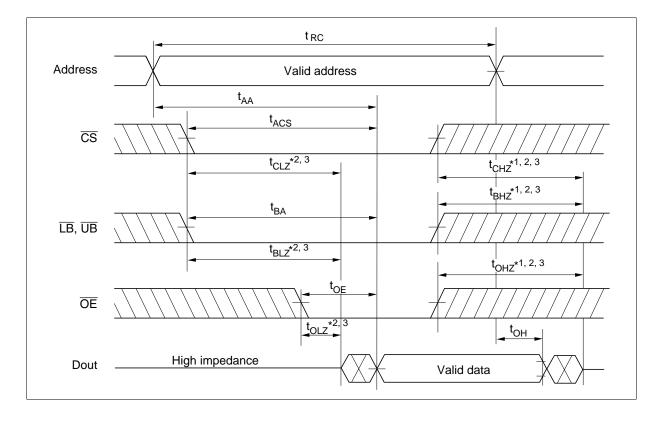

#### **Read Cycle**

|                                    |                  | HM62\ | /16258B |     |     |      |         |

|------------------------------------|------------------|-------|---------|-----|-----|------|---------|

|                                    |                  | -7    |         | -8  |     |      |         |

| Parameter                          | Symbol           | Min   | Max     | Min | Max | Unit | Notes   |

| Read cycle time                    | t <sub>RC</sub>  | 70    | _       | 85  | _   | ns   |         |

| Address access time                | t <sub>AA</sub>  | _     | 70      | _   | 85  | ns   |         |

| Chip select access time            | t <sub>ACS</sub> | _     | 70      | _   | 85  | ns   |         |

| Output enable to output valid      | t <sub>OE</sub>  | _     | 40      | _   | 45  | ns   |         |

| Output hold from address change    | t <sub>oh</sub>  | 10    | _       | 10  | _   | ns   |         |

| LB, UB access time                 | t <sub>BA</sub>  | _     | 70      | _   | 85  | ns   |         |

| Chip select to output in low-Z     | t <sub>CLZ</sub> | 10    | _       | 10  | _   | ns   | 2, 3    |

| LB, UB enable to low-z             | t <sub>BLZ</sub> | 5     | _       | 5   | _   | ns   | 2, 3    |

| Output enable to output in low-Z   | t <sub>oLZ</sub> | 5     | _       | 5   | _   | ns   | 2, 3    |

| Chip deselect to output in high-Z  | t <sub>CHZ</sub> | 0     | 25      | 0   | 25  | ns   | 1, 2, 3 |

| LB, UB disable to high-Z           | t <sub>BHZ</sub> | 0     | 25      | 0   | 25  | ns   | 1, 2, 3 |

| Output disable to output in high-Z | t <sub>OHZ</sub> | 0     | 25      | 0   | 25  | ns   | 1, 2, 3 |

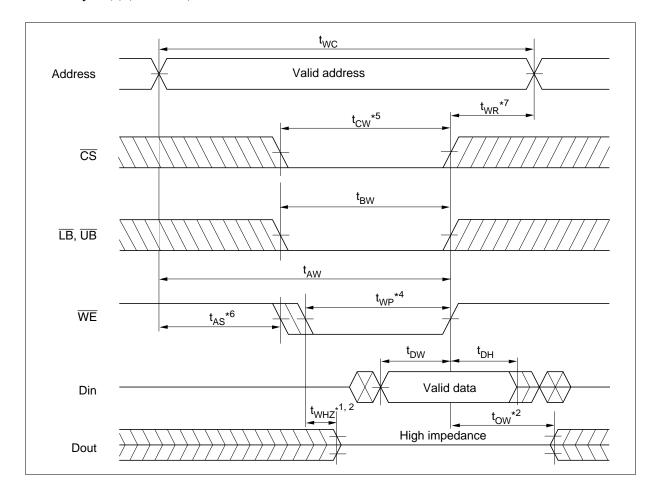

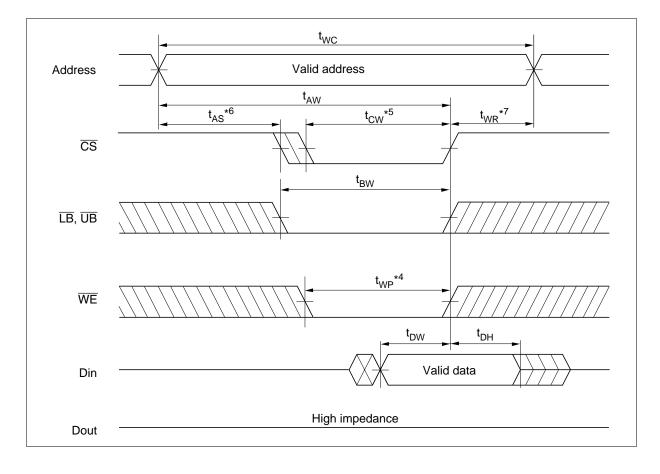

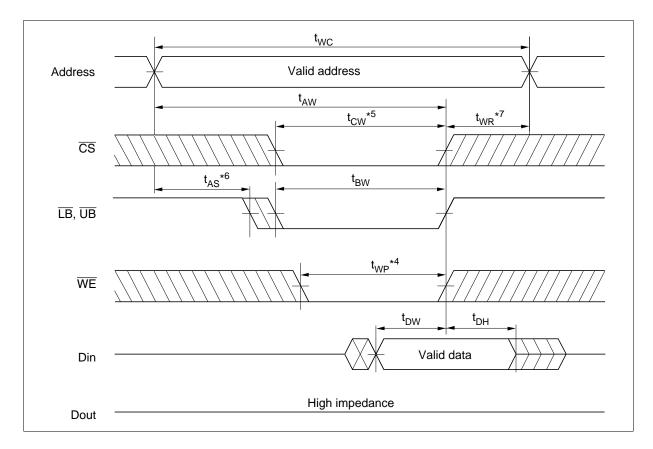

#### Write Cycle

|                                    |                             | -7  |     | -8  |     |      |       |

|------------------------------------|-----------------------------|-----|-----|-----|-----|------|-------|

| Parameter                          | Symbol                      | Min | Max | Min | Max | Unit | Notes |

| Write cycle time                   | t <sub>wc</sub>             | 70  | _   | 85  | _   | ns   |       |

| Address valid to end of write      | $\mathbf{t}_{AW}$           | 60  |     | 70  | _   | ns   |       |

| Chip selection to end of write     | t <sub>cw</sub>             | 60  | _   | 70  | _   | ns   | 5     |

| Write pulse width                  | t <sub>WP</sub>             | 50  | _   | 55  | _   | ns   | 4     |

| LB, UB valid to end of write       | $t_{\scriptscriptstyle BW}$ | 55  | _   | 70  | _   | ns   |       |

| Address setup time                 | t <sub>AS</sub>             | 0   | _   | 0   | _   | ns   | 6     |

| Write recovery time                | t <sub>wR</sub>             | 0   | _   | 0   | _   | ns   | 7     |

| Data to write time overlap         | $t_{\scriptscriptstyle DW}$ | 30  | _   | 35  | _   | ns   |       |

| Data hold from write time          | $t_{DH}$                    | 0   | _   | 0   | _   | ns   |       |

| Output active from end of write    | t <sub>ow</sub>             | 5   | _   | 5   | _   | ns   | 2     |

| Output disable to output in High-Z | t <sub>OHZ</sub>            | 0   | 25  | 0   | 25  | ns   | 1, 2  |

| Write to output in high-Z          | t <sub>WHZ</sub>            | 0   | 25  | 0   | 25  | ns   | 1, 2  |

Notes: 1.  $t_{CHZ}$ ,  $t_{OHZ}$ ,  $t_{WHZ}$  and  $t_{BHZ}$  are defined as the time at which the outputs achieve the open circuit conditions and are not referred to output voltage levels.

- 2. This parameter is sampled and not 100% tested.

- 3. At any given temperature and voltage condition,  $t_{HZ}$  max is less than  $t_{LZ}$  min both for a given device and from device to device.

- 4. A write occures during the overlap of a low  $\overline{CS}$ , a low  $\overline{WE}$  and a low  $\overline{LB}$  or a low  $\overline{UB}$ . A write begins at the latest transition among  $\overline{CS}$  going low,  $\overline{WE}$  going low and  $\overline{LB}$  going low or  $\overline{UB}$  going low. A write ends at the earliest transition among  $\overline{CS}$  going high,  $\overline{WE}$  going high and  $\overline{LB}$  going high or  $\overline{UB}$  going high.  $t_{WP}$  is measured from the beginning of write to the end of write.

- 5.  $t_{CW}$  is measured from the later of  $\overline{CS}$  going low to the end of write.

- 6.  $t_{AS}$  is measured from the address valid to the beginning of write.

- 7.  $t_{WR}$  is measured from the earliest of  $\overline{CS}$  or  $\overline{WE}$  going high to the end of write cycle.

#### **Timing Waveform**

#### Read Cycle

#### Write Cycle (1) ( $\overline{\text{WE}}$ Clock)

#### Write Cycle (2) ( $\overline{CS}$ Clock, $\overline{OE} = V_{IH}$ )

Write Cycle (3) ( $\overline{LB}$ ,  $\overline{UB}$  Clock,  $\overline{OE} = V_{IH}$ )

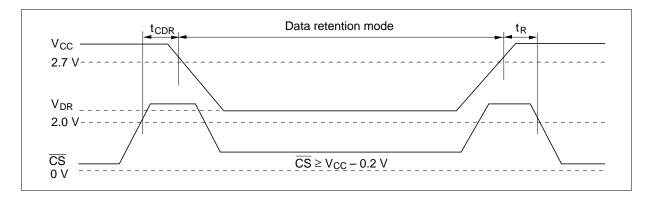

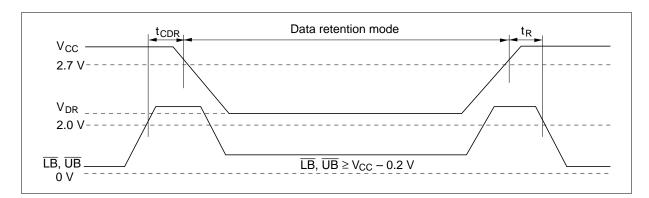

#### **Low V**<sub>CC</sub> **Data Retention Characteristics** (Ta = 0 to +70°C)

| Parameter                            | Symbol               | Min              | Typ* | ⁴ Max | Unit | Test conditions <sup>'3</sup>                                                                                                                                                                                                                                                                         |

|--------------------------------------|----------------------|------------------|------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>cc</sub> for data retention   | $V_{DR}$             | 2.0              | _    | _     | V    | $\begin{array}{c} \text{Vin} \geq 0\text{V} \\ \text{(1)} \ \overline{\text{CS}} \geq \text{V}_{\text{CC}} - 0.2\text{V or} \\ \text{(2)} \ \overline{\text{LB}} = \overline{\text{UB}} \geq \text{V}_{\text{CC}} - 0.2\text{V} \\ \overline{\text{CS}} \leq 0.2\text{V} \end{array}$                 |

| Data retention current               | I <sub>CCDR</sub> *1 | _                | 8.0  | 20    | μΑ   | $\begin{array}{c} V_{\text{CC}} = 3.0 \text{ V, Vin} \ge 0\text{V} \\ \text{(1)} \ \ \overline{\text{CS}} \ge V_{\text{CC}} - 0.2 \text{ V or} \\ \text{(2)} \ \ \overline{\text{LB}} = \overline{\text{UB}} \ge V_{\text{CC}} - 0.2 \text{ V} \\ \overline{\text{CS}} \le 0.2 \text{ V} \end{array}$ |

|                                      | I <sub>CCDR</sub> *2 | _                | 0.8  | 10    | μΑ   |                                                                                                                                                                                                                                                                                                       |

| Chip deselect to data retention time | $t_{\mathtt{CDR}}$   | 0                | _    | _     | ns   | See retention waveform                                                                                                                                                                                                                                                                                |

| Operation recovery time              | t <sub>R</sub>       | $t_{RC}^{^{*5}}$ | _    | _     | ns   |                                                                                                                                                                                                                                                                                                       |

Notes: 1. This characteristic is guaranteed only for L-version, 10  $\mu$ A max. at Ta = 0 to +40°C.

- 2. This characteristic is guaranteed only for L-SL version, 5  $\mu$ A max. at Ta = 0 to +40°C.

- 3.  $\overline{CS}$  controls address buffer,  $\overline{WE}$  buffer,  $\overline{OE}$  buffer,  $\overline{LB}$ ,  $\overline{UB}$  buffer and Din buffer. If  $\overline{CS}$  controls data retention mode, Vin levels (address,  $\overline{WE}$ ,  $\overline{OE}$ ,  $\overline{LB}$ ,  $\overline{UB}$ ,  $\overline{I/O}$ ) can be in the high impedance state. If  $\overline{LB}$ ,  $\overline{UB}$  controls data retention mode,  $\overline{LB}$ ,  $\overline{UB}$  must be  $\overline{LB} = \overline{UB} \ge V_{cc} 0.2 \text{ V}$ ,  $\overline{CS}$  must be  $\overline{CS} \le 0.2 \text{ V}$ . The other input levels (address,  $\overline{WE}$ ,  $\overline{OE}$ ,  $\overline{I/O}$ ) can be in the high impedance state.

- 4. Typical values are at  $V_{cc} = 3.0 \text{ V}$ ,  $Ta = +25^{\circ}\text{C}$  and not guaranteed.

- 5.  $t_{RC}$  = read cycle time.

#### Low $V_{CC}$ Data Retention Timing Waveform (1) ( $\overline{CS}$ Controlled)

Low  $V_{CC}$  Data Retention Timing Waveform (2) ( $\overline{LB}$ ,  $\overline{UB}$  Controlled)

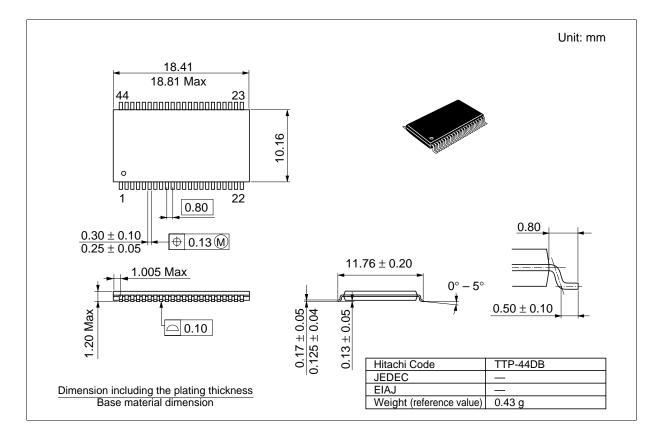

#### **Package Dimensions**

#### HM62V16258BLTT Series (TTP-44DB)

#### Cautions

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

## IITACE

Semiconductor & Integrated Circuits.

Nippon Bldg., 2-6-2, Onte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109

**URL NorthAmerica** http:semiconductor.hitachi.com/ Europe http://www.hitachi-eu.com/hel/ecg

http://www.has.hitachi.com.sg/grp3/sicd/index.htm http://www.hitachi.com.tw/E/Product/SICD\_Frame.htm Asia (Singapore) Asia (Taiwan) Asia (HongKóng) http://www.hitachi.com.hk/eng/bo/grp3/index.htm

http://www.hitachi.co.jp/Sicd/indx.htm Japan

#### For further information write to:

Hitachi Semiconductor (America) Inc. 179 East Tasman Drive, San Jose, CA 95134 Tel: <1> (408) 433-1990 Fax: <1>(408) 433-0223

Hitachi Europe GmbH Electronic components Group Dornacher Straße 3 D-85622 Feldkirchen, Munich Germany Tel: <49> (89) 9 9180-0

Fax: <49> (89) 9 29 30 00 Hitachi Europe Ltd. Electronic Components Group. Whitebrook Park Lower Cookham Road Maidenhead

Berkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000 Fax: <44> (1628) 778322

Hitachi Asia Pte. Ltd. 16 Collyer Quay #20-00 Hitachi Tower Singapore 049318 Tel: 535-2100 Fax: 535-1533

Hitachi Asia Ltd. Taipei Branch Office 3F, Hung Kuo Building. No.167 Tun-Hwa North Road, Taipei (105) Tel: <886> (2) 2718-3666 Fax: <886> (2) 2718-8180

Hitachi Asia (Hong Kong) Ltd. Group III (Electronic Components) 7/F., North Tower, World Finance Centre, Harbour City, Canton Road, Tsim Sha Tsui,

Kowloon, Hong Kong Tel: <852> (2) 735 9218 Fax: <852> (2) 730 0281 Telex: 40815 HITEC HX

Copyright © Hitachi, Ltd., 1998. All rights reserved. Printed in Japan.