# HVL396C

# Variable Capacitance Diode for VCO

REJ03G0024-0100Z (Previous: ADE-208-1504)

> Rev.1.00 Apr.17.2003

#### **Features**

- High capacitance ratio. (n = 2.30 min)

- Low series resistance. (rs =  $0.4 \Omega \text{ max}$ )

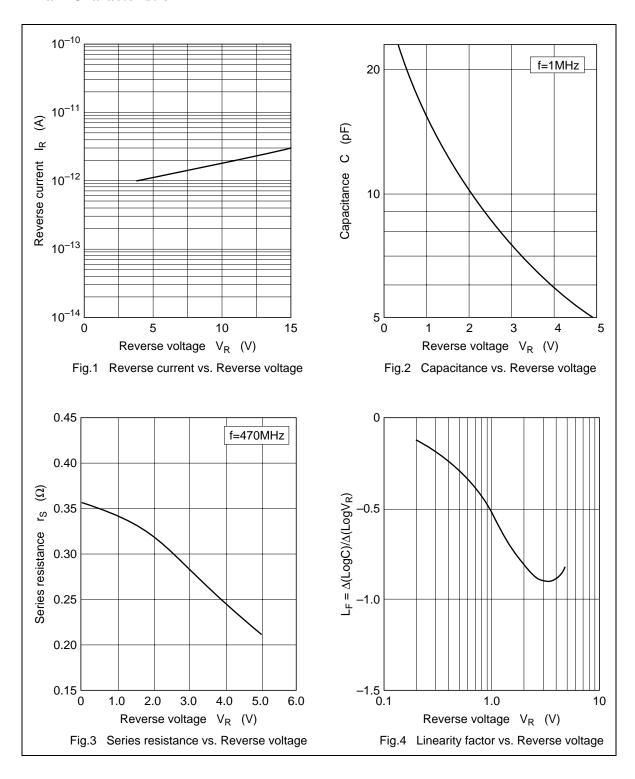

- Extremely small Flat Package (EFP) is suitable for surface mount design.

# **Ordering Information**

| Type No. | Laser Mark | Package Code |  |  |

|----------|------------|--------------|--|--|

| HVL396C  | 7          | EFP          |  |  |

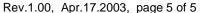

#### **Pin Arrangement**

### **Absolute Maximum Ratings**

$(Ta = 25^{\circ}C)$

| Item                 | Symbol | Value       | Unit |

|----------------------|--------|-------------|------|

| Reverse voltage      | $V_R$  | 10          | V    |

| Junction temperature | Tj     | 125         | °C   |

| Storage temperature  | Tstg   | –55 to +125 | °C   |

#### **Electrical Characteristics**

$(Ta = 25^{\circ}C)$

| Item              | Symbol          | Min  | Тур | Max  | Unit | Test Condition                    |

|-------------------|-----------------|------|-----|------|------|-----------------------------------|

| Reverse current   | I <sub>R1</sub> | _    | _   | 10   | nA   | V <sub>R</sub> = 10 V             |

|                   | I <sub>R2</sub> | _    | _   | 50   |      | V <sub>R</sub> = 10 V, Ta = 60°C  |

| Capacitance       | C <sub>1</sub>  | 14.5 | _   | 17.5 | pF   | V <sub>R</sub> = 1 V, f = 1 MHz   |

|                   | C <sub>4</sub>  | 5.2  | _   | 6.5  |      | V <sub>R</sub> = 4 V, f = 1 MHz   |

| Capacitance ratio | n               | 2.3  | _   | _    | _    | C <sub>1</sub> /C <sub>4</sub>    |

| Series resistance | r <sub>s</sub>  | _    | _   | 0.4  | Ω    | V <sub>R</sub> = 1 V, f = 470 MHz |

Notes: 1. Please do not use the soldering iron due to avoid high stress to the EFP package.

2. The material of lead is exposed for cutting plane. Therefore, soldering nature of lead tip part is considered as unquestioned. Please kindly consider soldering nature.

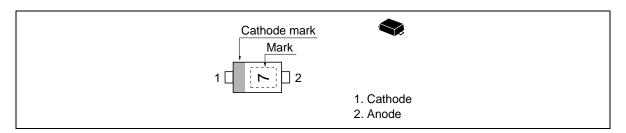

#### **Main Characteristic**

## **Package Dimensions**

#### Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Keep safety first in your circuit designs!

1. Renessa Technology Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

Notes regarding these materials

Notes regarding these materials

1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corporation or a third party.

2. Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors.

Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

5. Renesas Technology Corporation semiconductors

- 5. Refriesa February Composition Serificultural Ser

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited. 8. Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

Copyright © 2003. Renesas Technology Corporation, All rights reserved. Printed in Japan.