# Regarding the change of names mentioned in the document, such as Hitachi Electric and Hitachi XX, to Renesas Technology Corp.

The semiconductor operations of Mitsubishi Electric and Hitachi were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Renesas Technology Home Page: http://www.renesas.com

Renesas Technology Corp. Customer Support Dept. April 1, 2003

#### **Cautions**

Keep safety first in your circuit designs!

Renesas Technology Corporation puts the maximum effort into making semiconductor products better

and more reliable, but there is always the possibility that trouble may occur with them. Trouble with

semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate

measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or

(iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- 1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corporation or a third party.

- 2. Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

# HB28B2000A8H/HB28B1000A8H HB28B640A8H/HB28B512A8H HB28B448A8H/HB28B320A8H HB28B256A8H/HB28B192A8H HB28B128A8H/HB28B064A8H

FLASH ATA Card 2 GByte/1 GByte/640 MByte/512 MByte/448 MByte 320 MByte/256 MByte/192 MByte/128 MByte 64 MByte

ADE-203-1345B (Z) Rev. 2.0 Sep. 2, 2002

#### **Description**

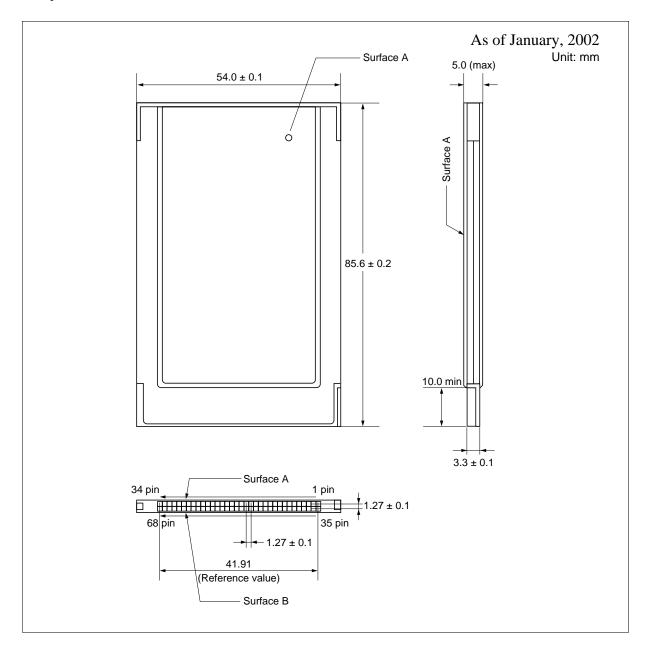

HB28B2000A8H, HB28B1000A8H, HB28B640A8H, HB28B512A8H, HB28B448A8H, HB28B320A8H, HB28B256A8H, HB28B192A8H, HB28B128A8H, HB28B064A8H are Flash ATA card. This card complies with PC card ATA standard and is suitable for the usage of data storage memory medium for PC or any other electric equipment. This card is equipped with 0.18  $\mu$ m CMOS 512 Mega bit Flash memory. This card is suitable for ISA (Industry Standard Architecture) bus interface standard, and read/write unit is 1 sector (512 bytes) sequential access. By using this card it is possible to operate good performance for the system which have PC card slots.

#### **Features**

- PC card ATA standard specification

- 68 pin two pieces connector and Type II (5 mm)

- 3.3 V/5 V single power supply operation

- ISA standard and Read/Write unit is 512 bytes (sector) sequential access

- Sector Read/Write transfer rate: 8MB/sec burst

- Card density is 2 Giga bytes maximum

- This card is equipped 0.18 μm CMOS 512 Mega bit Flash memory

- 3 variations of mode access

- Memory card mode

- I/O card mode

- True IDE mode

- High reliability based on internal ECC (Error Correcting Code) function

- Auto Sleep Function

- Data write is 300,000 cycles/block.\*1

Note: 1. One block consists of four sectors (512 byte  $\times$  4).

### Card Line Up\*1

| Type No.     | Card density | Capacity*4         | Total sectors/<br>card*3 | Sectors/<br>track*2 | Number of<br>head | Number of cylinder |

|--------------|--------------|--------------------|--------------------------|---------------------|-------------------|--------------------|

| HB28B2000A8H | 2 GB         | 2,050,965,504 byte | 4,005,792                | 63                  | 16                | 3974               |

| HB28B1000A8H | 1 GB         | 1,025,482,752 byte | 2,002,896                | 63                  | 16                | 1987               |

| HB28B640A8H  | 640 MB       | 640,475,136 byte   | 1,250,928                | 63                  | 16                | 1241               |

| HB28B512A8H  | 512 MB       | 512,483,328 byte   | 1,000,944                | 63                  | 16                | 993                |

| HB28B448A8H  | 448 MB       | 448,519,680 byte   | 876,015                  | 63                  | 15                | 927                |

| HB28B320A8H  | 320 MB       | 320,409,600 byte   | 625,800                  | 56                  | 15                | 745                |

| HB28B256A8H  | 256 MB       | 256,204,800 byte   | 500,400                  | 48                  | 15                | 695                |

| HB28B192A8H  | 192 MB       | 192,184,320 byte   | 375,360                  | 32                  | 15                | 782                |

| HB28B128A8H  | 128 MB       | 128,188,416 byte   | 250,368                  | 32                  | 8                 | 978                |

| HB28B064A8H  | 64 MB        | 64,094,208 byte    | 125,184                  | 32                  | 4                 | 978                |

Notes: 1. These data are written in ID.

- 2. Total tracks = number of head  $\times$  number of cylinder.

- 3. Total sectors/card = sectors/track × number of head × number of cylinder.

- 4. It is the logical address capacity including the area which is used for file system.

### **Card Pin Assignment**

|         | Memory card n | node | I/O card mode | I/O card mode |             |     |

|---------|---------------|------|---------------|---------------|-------------|-----|

| Pin No. | Signal name   | I/O  | Signal name   | I/O           | Signal name | I/O |

| 1       | GND           | _    | GND           | _             | GND         | _   |

| 2       | D3            | I/O  | D3            | I/O           | D3          | I/O |

| 3       | D4            | I/O  | D4            | I/O           | D4          | I/O |

| 4       | D5            | I/O  | D5            | I/O           | D5          | I/O |

| 5       | D6            | I/O  | D6            | I/O           | D6          | I/O |

| 6       | D7            | I/O  | D7            | I/O           | D7          | I/O |

| 7       | -CE1          | ı    | -CE1          | ı             | -CE1        | I   |

| 8       | A10           | I    | A10           | I             | A10         | I   |

| 9       | -OE           | I    | -OE           | I             | -ATASEL     | I   |

| 10      | _             | _    | <del>_</del>  | _             | <del></del> | _   |

| 11      | A9            | ļ    | A9            | I             | A9          | ļ   |

| 12      | A8            | I    | A8            | I             | A8          | I   |

| 13      | _             | _    | <del>_</del>  | _             | <del></del> | _   |

| 14      | _             | _    | _             | _             | _           | _   |

| 15      | -WE           | I    | -WE           | I             | -WE         | I   |

| 16      | RDY/-BSY      | 0    | -IREQ         | 0             | INTRQ       | 0   |

| 17      | VCC           | _    | VCC           | _             | VCC         | _   |

| 18      | _             | _    | _             | _             | _           | _   |

| 19      | _             | _    | _             | _             | _           | _   |

| 20      | _             | _    | _             | _             | _           | _   |

| 21      | _             | _    | _             | _             | _           | _   |

| 22      | A7            | I    | A7            | I             | A7          | 1   |

| 23      | A6            | I    | A6            | I             | A6          | 1   |

| 24      | A5            | I    | A5            | I             | A5          | I   |

| 25      | A4            | 1    | A4            | I             | A4          | 1   |

| 26      | A3            | I    | A3            | I             | A3          | 1   |

| 27      | A2            | I    | A2            | I             | A2          | I   |

| 28      | A1            | I    | A1            | I             | A1          | I   |

| 29      | A0            | I    | A0            | I             | A0          | I   |

| 30      | D0            | I/O  | D0            | I/O           | D0          | I/O |

| 31      | D1            | I/O  | D1            | I/O           | D1          | I/O |

| 32      | D2            | I/O  | D2            | I/O           | D2          | I/O |

| 33      | WP            | 0    | -IOIS16       | 0             | -IOIS16     | 0   |

|         | Memory card n | node | I/O card mode | I/O card mode |              | True IDE mode |  |  |

|---------|---------------|------|---------------|---------------|--------------|---------------|--|--|

| Pin No. | Signal name   | I/O  | Signal name   | I/O           | Signal name  | I/O           |  |  |

| 34      | GND           | _    | GND           | _             | GND          | _             |  |  |

| 35      | GND           | _    | GND           | _             | GND          | _             |  |  |

| 36      | -CD1          | 0    | -CD1          | 0             | -CD1         | 0             |  |  |

| 37      | D11           | I/O  | D11           | I/O           | D11          | I/O           |  |  |

| 38      | D12           | I/O  | D12           | I/O           | D12          | I/O           |  |  |

| 39      | D13           | I/O  | D13           | I/O           | D13          | I/O           |  |  |

| 40      | D14           | I/O  | D14           | I/O           | D14          | I/O           |  |  |

| 41      | D15           | I/O  | D15           | I/O           | D15          | I/O           |  |  |

| 42      | -CE2          | I    | -CE2          | I             | -CE2         | 1             |  |  |

| 43      | -VS1          | 0    | -VS1          | 0             | -VS1         | 0             |  |  |

| 44      | -IORD         | I    | -IORD         | I             | -IORD        | I             |  |  |

| 45      | -IOWR         | I    | -IOWR         | I             | -IOWR        | I             |  |  |

| 46      | _             | _    | _             | _             | _            | _             |  |  |

| 47      | _             | _    | _             | _             | _            | _             |  |  |

| 48      | _             | _    | _             | _             | _            | _             |  |  |

| 49      | _             | _    | _             | _             | _            | _             |  |  |

| 50      | _             | _    | _             | _             | _            | _             |  |  |

| 51      | VCC           | _    | VCC           | _             | VCC          | _             |  |  |

| 52      | _             | _    | <del>_</del>  | _             | <del>_</del> | _             |  |  |

| 53      | _             | _    | <del></del>   | _             | <del></del>  | _             |  |  |

| 54      | _             | _    | _             | _             | _            | _             |  |  |

| 55      | _             | _    | <del>_</del>  | _             | <del>_</del> | _             |  |  |

| 56      | -CSEL         | I    | -CSEL         | I             | -CSEL        | ı             |  |  |

| 57      | -VS2          | 0    | -VS2          | 0             | -VS2         | 0             |  |  |

| 58      | RESET         | I    | RESET         | I             | -RESET       | I             |  |  |

| 59      | -WAIT         | 0    | -WAIT         | 0             | IORDY        | 0             |  |  |

| 60      | -INPACK       | 0    | -INPACK       | 0             | -INPACK      | 0             |  |  |

| 61      | -REG          | I    | -REG          | I             | -REG         | I             |  |  |

| 62      | BVD2          | I/O  | -SPKR         | I/O           | -DASP        | I/O           |  |  |

| 63      | BVD1          | I/O  | -STSCHG       | I/O           | -PDIAG       | I/O           |  |  |

| 64      | D8            | I/O  | D8            | I/O           | D8           | I/O           |  |  |

| 65      | D9            | I/O  | D9            | I/O           | D9           | I/O           |  |  |

| 66      | D10           | I/O  | D10           | I/O           | D10          | I/O           |  |  |

| 67      | -CD2          | 0    | -CD2          | 0             | -CD2         | 0             |  |  |

| 68      | GND           | _    | GND           | _             | GND          | _             |  |  |

### **Card Pin Explanation**

| Signal name                                        | Direction | Pin No.                                         | Description                                                                                                                                                  |

|----------------------------------------------------|-----------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A10 to A0<br>(PC Card Memory mode)                 | I         | 8, 11, 12, 22, 23,<br>24, 25, 26, 27,<br>28, 29 | Address bus is A10 to A0. A10 is MSB and A0 is LSB.                                                                                                          |

| A10 to A0<br>(PC Card I/O mode)                    |           |                                                 |                                                                                                                                                              |

| A2 to A0<br>(True IDE mode)                        |           | 27, 28, 29                                      | Address bus is A10 to A0. Only A2 to A0 are used, A10 to A3 should be grounded by the host.                                                                  |

| BVD1<br>(PC Card Memory mode)                      | I/O       | 63                                              | BVD1 outputs the battery voltage status in the card. This output line is constantly driven to a high state since a battery is not required for this product. |

| -STSCHG<br>(PC Card I/O mode)                      | -         |                                                 | -STSCHG is used for changing the status of Configuration and status register in attribute area.                                                              |

| -PDIAG<br>(True IDE mode)                          |           |                                                 | -PDIAG is the Pass Diagnostic signal in Master/Slave handshake protocol.                                                                                     |

| BVD2<br>(PC Card Memory mode)                      | I/O       | 62                                              | BVD2 outputs the battery voltage status in the card. This output line is constantly driven to a high state since a battery is not required for this product. |

| -SPKR<br>(PC Card I/O mode)                        | -         |                                                 | -SPKR outputs speaker signals. This output line is constantly driven to a high state since this product does not support the audio function.                 |

| -DASP<br>(True IDE mode)                           | -         |                                                 | -DASP is the Disk Active/Slave Present signal in the Master/Slave handshake protocol.                                                                        |

| -CD1, -CD2<br>(PC Card Memory mode)                | 0         | 36, 67                                          | -CD1 and -CD2 are the card detection signalsCD1 and -CD2 are connected to ground in this card, so host can detect that the card is inserted or not.          |

| -CD1, -CD2<br>(PC Card I/O mode)                   | =         |                                                 |                                                                                                                                                              |

| -CD1, -CD2<br>(True IDE mode)                      | -         |                                                 |                                                                                                                                                              |

| -CE1, -CE2<br>(PC Card Memory mode)<br>Card Enable | I         | 7, 42                                           | -CE1 and -CE2 are low active card select signals.<br>Byte/Word/Odd byte mode are defined by combination<br>of -CE1, -CE2 and A0.                             |

| -CE1, -CE2<br>(PC Card I/O mode)<br>Card Enable    | -         |                                                 |                                                                                                                                                              |

| -CE1, -CE2<br>(True IDE mode)                      | -         |                                                 | -CE2 is used for select the Alternate Status Register and the Device Control Register while -CE1 is the chip select for the other task file registers.       |

| Signal name                                        | Direction | Pin No.                                                            | Description                                                                                                                                                                                                                             |

|----------------------------------------------------|-----------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -CSEL<br>(PC Card Memory mode)                     | I         | 56                                                                 | This signal is not used.                                                                                                                                                                                                                |

| -CSEL<br>(PC Card I/O mode)                        | _         |                                                                    |                                                                                                                                                                                                                                         |

| -CSEL<br>(True IDE mode)                           |           |                                                                    | This signal is used to configure this device as a Master or a Slave when configured in the True IDE mode. When this pin is grounded, this device is configured as a Master. When the pin is open, this device is configured as a Slave. |

| D15 to D0<br>(PC Card Memory mode)                 | I/O       | 41, 40, 39, 38,<br>37, 66, 65, 64, 6,<br>5, 4, 3, 2, 32, 31,<br>30 | Data bus is D15 to D0. D0 is the LSB of the even byte of the word. D8 is the LSB of the odd byte of the word.                                                                                                                           |

| D15 to D0<br>(PC Card I/O mode)                    | -         |                                                                    |                                                                                                                                                                                                                                         |

| D15 to D0<br>(True IDE mode)                       |           |                                                                    |                                                                                                                                                                                                                                         |

| GND<br>(PC Card Memory mode)                       | _         | 1, 34, 35, 68                                                      | Ground                                                                                                                                                                                                                                  |

| GND<br>(PC Card I/O mode)                          |           |                                                                    |                                                                                                                                                                                                                                         |

| GND<br>(True IDE mode)                             | -         |                                                                    |                                                                                                                                                                                                                                         |

| -INPACK<br>(PC Card Memory mode)                   | 0         | 60                                                                 | This signal is not used and should not be connected at the host.                                                                                                                                                                        |

| -INPACK<br>(PC Card I/O mode)<br>Input Acknowledge | -         |                                                                    | This signal is asserted low by this card when the card is selected and responding to an I/O read cycle at the address that is on the address bus during -CE and -IORD are low. This signal is used for the input data buffer control.   |

| -INPACK<br>(True IDE mode)                         | =         |                                                                    | This signal is not used and should not be connected at the host.                                                                                                                                                                        |

| -IORD<br>(PC Card Memory mode)                     | I         | 44                                                                 | This signal is not used.                                                                                                                                                                                                                |

| -IORD<br>(PC Card I/O mode)                        | -         |                                                                    | -IORD is used for control of read data in I/O task file area. This card does not respond to -IORD until I/O card interface setting up.                                                                                                  |

| -IORD<br>(True IDE mode)                           | -         |                                                                    | -IORD is used for control of read data in I/O task file area. This card does not respond to -IORD until True IDE interface setting up.                                                                                                  |

| Signal name                                              | Direction | Pin No. | Description                                                                                                                                                                                                          |

|----------------------------------------------------------|-----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -IOWR<br>(PC Card Memory mode)                           | I         | 45      | This signal is not used.                                                                                                                                                                                             |

| -IOWR<br>(PC Card I/O mode)                              | -         |         | -IOWR is used for control of data write in I/O task file area. This card does not respond to -IOWR until I/O card interface setting up.                                                                              |

| -IOWR<br>(True IDE mode)                                 | -         |         | -IOWR is used for control of data write in I/O task file area. This card does not respond to -IOWR until True IDE interface setting up.                                                                              |

| -OE<br>(PC Card Memory mode)                             | I         | 9       | -OE is used for the control of reading register's data in attribute area or task file area.                                                                                                                          |

| -OE<br>(PC Card I/O mode)                                |           |         | -OE is used for the control of reading register's data in attribute area.                                                                                                                                            |

| -ATASEL<br>(True IDE mode)                               | -         |         | To enable True IDE mode this input should be grounded by the host.                                                                                                                                                   |

| RDY/-BSY<br>(PC Card Memory mode)                        | 0         | 16      | The signal is RDY/-BSY pin. RDY/-BSY pin turns low level during the card internal initialization operation at VCC applied or reset applied, so next access to the card should be after the signal turned high level. |

| -IREQ<br>(PC Card I/O mode)                              | -         |         | This signal is active low -IREQ pin. The signal of low level indicates that the card is requesting software service to host, and high level indicates that the card is not requesting.                               |

| INTRQ<br>(True IDE mode)                                 | -         |         | This signal is the active high Interrupt Request to the host.                                                                                                                                                        |

| -REG<br>(PC Card Memory mode)<br>Attribute memory select | I         | 61      | -REG is used during memory cycles to distinguish between task file and attribute memory accesses. High for task file, Low for attribute memory is accessed.                                                          |

| -REG<br>(PC Card I/O mode)                               | -         |         | -REG is constantly low when task file or attribute memory is accessed.                                                                                                                                               |

| -REG<br>(True IDE mode)                                  | -         |         | This input signal is not used and should be connected to VCC.                                                                                                                                                        |

| Signal name                         | Direction | Pin No. | Description                                                                                                                                                                                                                                  |

|-------------------------------------|-----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

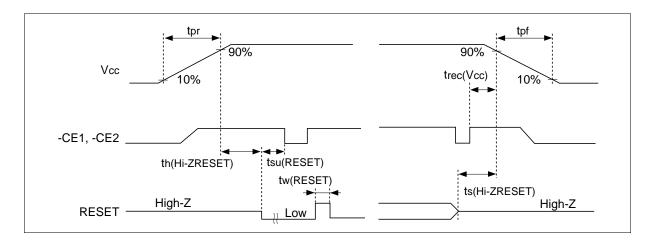

| RESET<br>(PC Card Memory mode)      | I         | 58      | This signal is active high RESET pin. If this signal is asserted high, the card internal initialization begins to operate. During the card internal initialization RDY/-BSY is low. After the card internal initialization RDY/-BSY is high. |

| RESET<br>(PC Card I/O mode)         |           |         | This signal is active high RESET pin. If this signal is asserted high, the card internal initialization begins to operate. In this mode, RDY/-BSY signal can not be used, so using Status Register the Ready/Busy status can be confirmed.   |

| -RESET<br>(True IDE mode)           | -         |         | This signal is active low -RESET pin. If this signal is asserted low, all the register's in this card are reset. In this mode, RDY/-BSY signal can not be used, so using status register the Ready/Busy status can be confirmed.             |

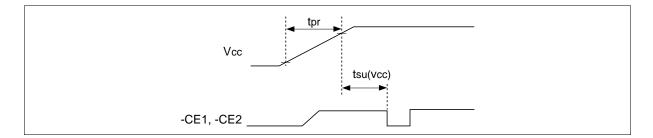

| VCC<br>(PC Card Memory mode)        | _         | 17, 51  | +5 V, +3.3 V power.                                                                                                                                                                                                                          |

| VCC<br>(PC Card I/O mode)           | _         |         |                                                                                                                                                                                                                                              |

| VCC<br>(True IDE mode)              |           |         |                                                                                                                                                                                                                                              |

| -VS1, -VS2<br>(PC Card Memory mode) | 0         | 43, 57  | These signals are intended to notify VCC requirement to hostVS1 is held grounded and -VS2 is nonconnected in this card.                                                                                                                      |

| -VS1, -VS2<br>(PC Card I/O mode)    |           |         |                                                                                                                                                                                                                                              |

| -VS1, -VS2<br>(True IDE mode)       |           |         |                                                                                                                                                                                                                                              |

| -WAIT<br>(PC Card Memory mode)      | 0         | 59      | This signal is active low -WAIT pin. In this card this signal is constantly high level.                                                                                                                                                      |

| -WAIT<br>(PC Card I/O mode)         | -         |         |                                                                                                                                                                                                                                              |

| IORDY<br>(True IDE mode)            | -         |         | This output signal may be used as IORDY. In this card this signal is constantly high impedance.                                                                                                                                              |

| -WE<br>(PC Card Memory mode)        | 1         | 15      | -WE is used for the control of writing register's data in attribute memory area or task file area.                                                                                                                                           |

| -WE<br>(PC Card I/O mode)           | -         |         | -WE is used for the control of writing register's data in attribute memory area.                                                                                                                                                             |

| -WE<br>(True IDE mode)              | -         |         | This input signal is not used and should be connected to VCC by the host.                                                                                                                                                                    |

| Signal name                                  | Direction | Pin No. | Description                                                                                                                                                                                                                           |

|----------------------------------------------|-----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WP<br>(PC Card Memory mode)<br>Write Protect | 0         | 33      | WP is held low because this card does not have write protect switch.                                                                                                                                                                  |

| -IOIS16<br>(PC Card I/O mode)                | _         |         | -IOIS16 is asserted when task file registers are accessed in 16-bit mode.                                                                                                                                                             |

| -IOIS16<br>(True IDE mode)                   | -         |         | This output signal is asserted low when this device is expecting a word data transfer cycle. Initial mode is 16-bit. If the user issues a Set Feature Command to put the device in Byte access mode, the card permits 8-bit accesses. |

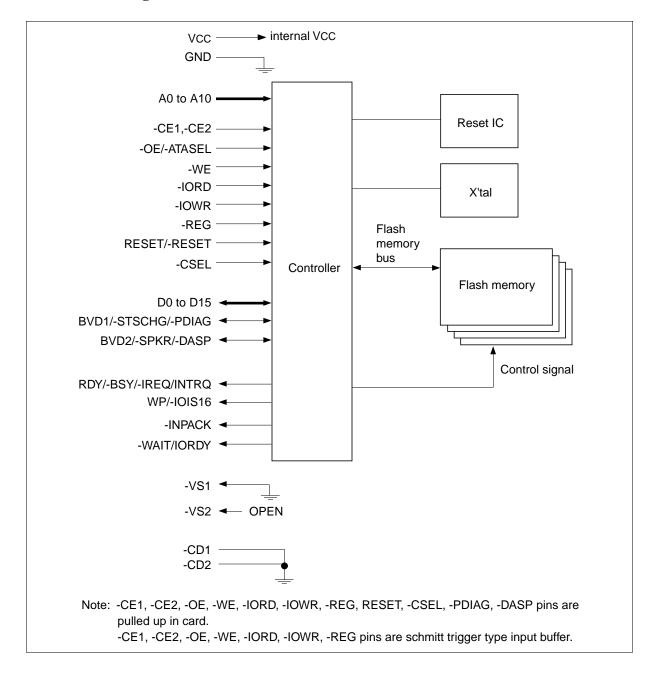

### **Card Block Diagram**

### **Card Function Explanation**

#### **Register construction**

- Attribute region

- Configuration register

- Configuration Option register

- Configuration and Status register

- Pin Replacement register

- Socket and Copy register

- CIS (<u>C</u>ard <u>Information S</u>tructure)

- Task File region

- Data register

- Error register

- Feature register

- Sector Count register

- Sector Number register

- Cylinder Low register

- Cylinder High register

- Drive Head register

- Status register

- Alternate Status register

- Command register

- Device Control register

- Drive Address register

#### Host access specifications

#### 1. Attribute access specifications

When CIS-ROM region or Configuration register region is accessed, read and write operations are executed under the condition of -REG = "L" as follows. That region can be accessed by Byte/Word/Odd-byte modes which are defined by PC card standard specifications.

#### **Attribute Read Access Mode**

| Mode                    | -REG | -CE2 | -CE1 | A0 | -OE | -WE | D8 to D15 | D0 to D7  |

|-------------------------|------|------|------|----|-----|-----|-----------|-----------|

| Standby mode            | ×    | Н    | Н    | ×  | ×   | ×   | High-Z    | High-Z    |

| Byte access (8-bit)     | L    | Н    | L    | L  | L   | Н   | High-Z    | even byte |

|                         | L    | Н    | L    | Н  | L   | Н   | High-Z    | invalid   |

| Word access (16-bit)    | L    | L    | L    | ×  | L   | Н   | invalid   | even byte |

| Odd byte access (8-bit) | L    | L    | Н    | ×  | L   | Н   | invalid   | High-Z    |

Note: x: L or H

#### **Attribute Write Access Mode**

| Mode                    | -REG | -CE2 | -CE1 | A0 | -OE | -WE | D8 to D15  | D0 to D7   |

|-------------------------|------|------|------|----|-----|-----|------------|------------|

| Standby mode            | ×    | Н    | Н    | ×  | ×   | ×   | Don't care | Don't care |

| Byte access (8-bit)     | L    | Н    | L    | L  | Н   | L   | Don't care | even byte  |

|                         | L    | Н    | L    | Н  | Н   | L   | Don't care | Don't care |

| Word access (16-bit)    | L    | L    | L    | ×  | Н   | L   | Don't care | even byte  |

| Odd byte access (8-bit) | L    | L    | Н    | ×  | Н   | L   | Don't care | Don't care |

Note: x: L or H

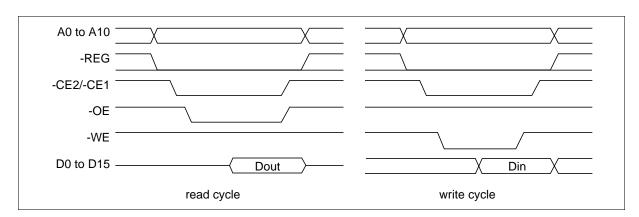

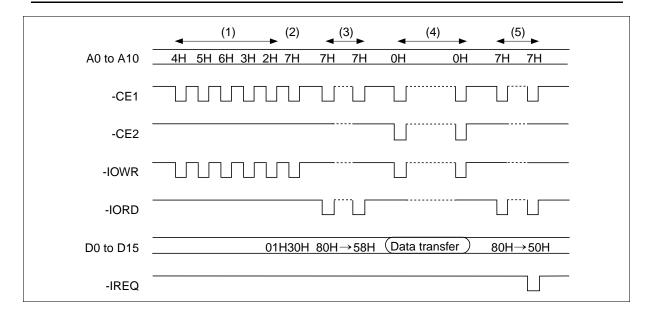

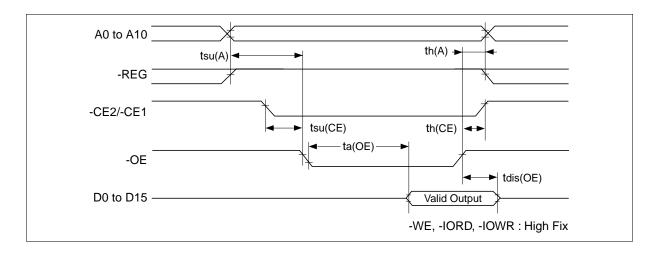

#### **Attribute Access Timing Example**

#### 2. Task File register access specifications

There are two cases of Task File register mapping, one is mapped I/O address area, the other is mapped Memory address area. Each case of Task File register read and write operations are executed under the condition as follows. That area can be accessed by Byte/Word/Odd Byte mode which are defined by PC card standard specifications.

#### (1) I/O address map

#### Task File Register Read Access Mode (1)

| Mode                    | -REG | -CE2 | -CE1 | A0 | -IORD | -IOWR | -OE | -WE | D8 to D15 | D0 to D7  |

|-------------------------|------|------|------|----|-------|-------|-----|-----|-----------|-----------|

| Standby mode            | ×    | Н    | Н    | ×  | ×     | ×     | ×   | ×   | High-Z    | High-Z    |

| Byte access (8-bit)     | L    | Н    | L    | L  | L     | Н     | Н   | Н   | High-Z    | even byte |

|                         | L    | Н    | L    | Н  | L     | Н     | Н   | Н   | High-Z    | odd byte  |

| Word access (16-bit)    | L    | L    | L    | ×  | L     | Н     | Н   | Н   | odd byte  | even byte |

| Odd byte access (8-bit) | L    | L    | Н    | ×  | L     | Н     | Н   | Н   | odd byte  | High-Z    |

Note: x: L or H

#### Task File Register Write Access Mode (1)

| Mode                    | -REG | -CE2 | -CE1 | A0 | -IORD | -IOWR | -OE | -WE | D8 to D15  | D0 to D7   |

|-------------------------|------|------|------|----|-------|-------|-----|-----|------------|------------|

| Standby mode            | ×    | Н    | Н    | ×  | ×     | ×     | ×   | ×   | Don't care | Don't care |

| Byte access (8-bit)     | L    | Н    | L    | L  | Н     | L     | Н   | Н   | Don't care | even byte  |

|                         | L    | Н    | L    | Н  | Н     | L     | Н   | Н   | Don't care | odd byte   |

| Word access (16-bit)    | L    | L    | L    | ×  | Н     | L     | Н   | Н   | odd byte   | even byte  |

| Odd byte access (8-bit) | L    | L    | Н    | ×  | Н     | L     | Н   | Н   | odd byte   | Don't care |

Note: x: L or H

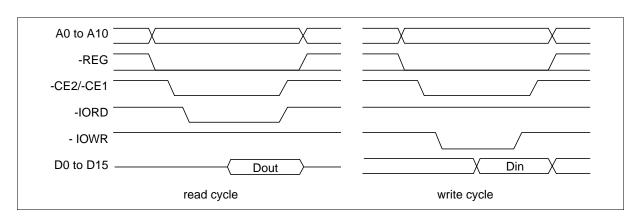

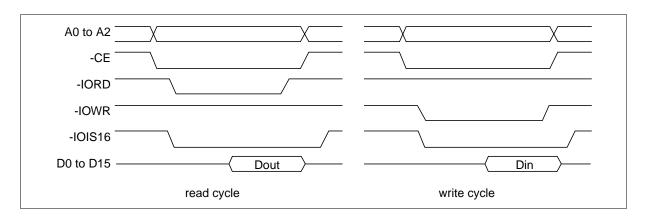

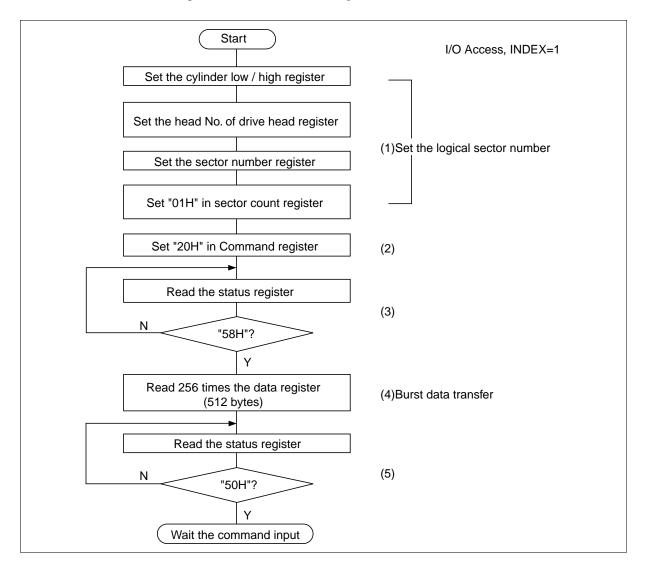

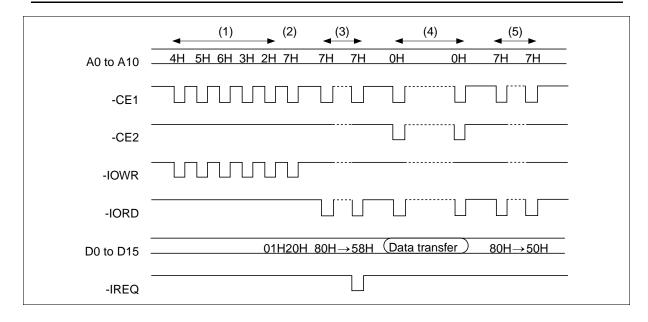

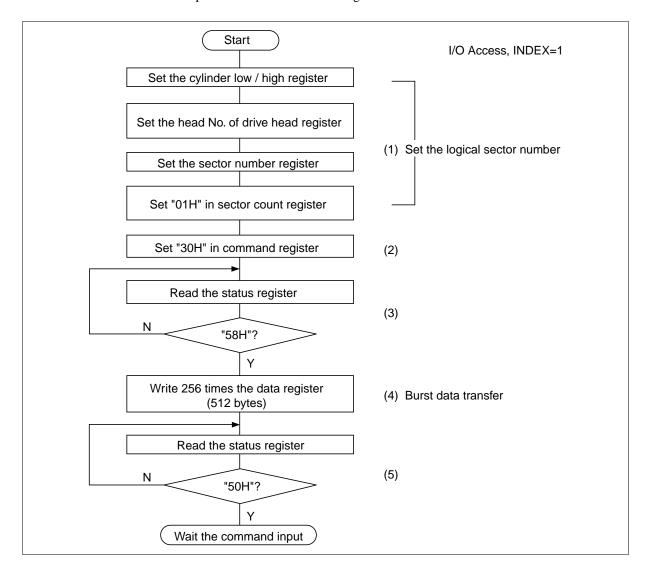

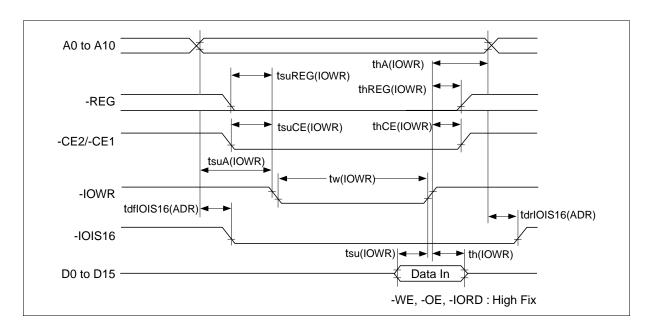

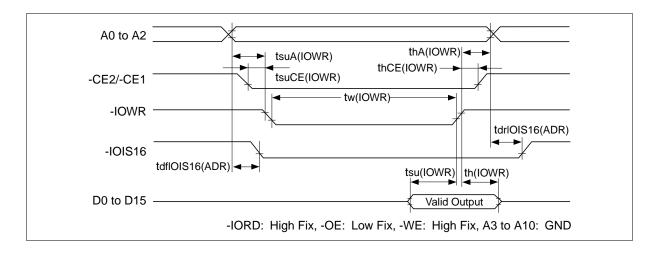

#### Task File Register Access Timing Example (1)

### (2) Memory address map

### Task File Register Read Access Mode (2)

| Mode                    | -REG | -CE2 | -CE1 | A0 | -OE | -WE | -IORD | -IOWR | D8 to D15 | D0 to D7  |

|-------------------------|------|------|------|----|-----|-----|-------|-------|-----------|-----------|

| Standby mode            | ×    | Н    | Н    | ×  | ×   | ×   | ×     | ×     | High-Z    | High-Z    |

| Byte access (8-bit)     | Н    | Н    | L    | L  | L   | Н   | Н     | Н     | High-Z    | even byte |

|                         | Н    | Н    | L    | Н  | L   | Н   | Н     | Н     | High-Z    | odd byte  |

| Word access (16-bit)    | Н    | L    | L    | ×  | L   | Н   | Н     | Н     | odd byte  | even byte |

| Odd byte access (8-bit) | Н    | L    | Н    | ×  | L   | Н   | Н     | Н     | odd byte  | High-Z    |

Note: x: L or H

### Task File Register Write Access Mode (2)

| Mode                    | -REG | -CE2 | -CE1 | Α0 | -OE | -WE | -IORD | -IOWR | D8 to D15  | D0 to D7   |

|-------------------------|------|------|------|----|-----|-----|-------|-------|------------|------------|

| Standby mode            | ×    | Н    | Н    | ×  | ×   | ×   | ×     | ×     | Don't care | Don't care |

| Byte access (8-bit)     | Н    | Н    | L    | L  | Н   | L   | Н     | Н     | Don't care | even byte  |

|                         | Н    | Н    | L    | Н  | Н   | L   | Н     | Н     | Don't care | odd byte   |

| Word access (16-bit)    | Н    | L    | L    | ×  | Н   | L   | Н     | Н     | odd byte   | even byte  |

| Odd byte access (8-bit) | Н    | L    | Н    | ×  | Н   | L   | Н     | Н     | odd byte   | Don't care |

Note: x: L or H

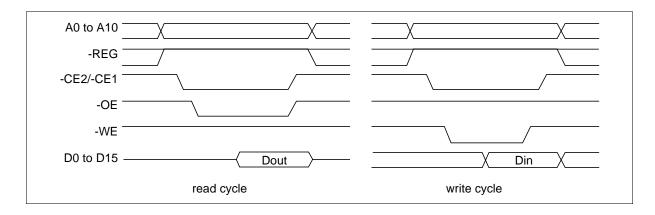

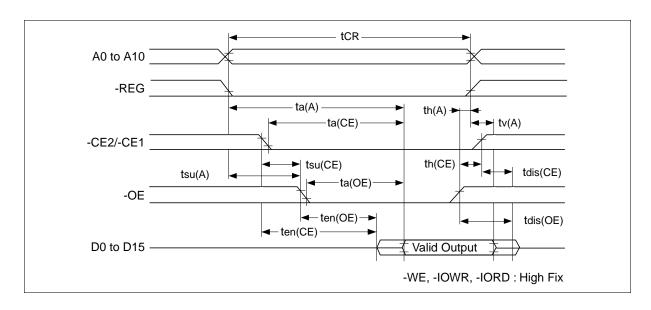

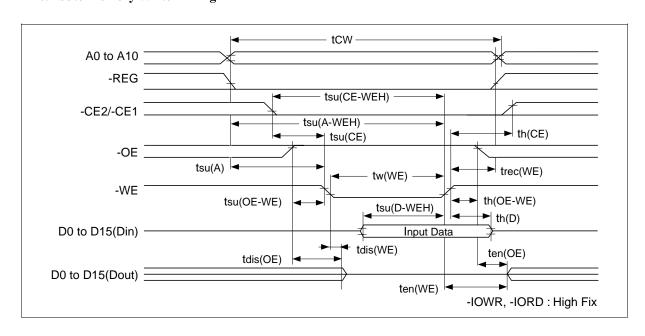

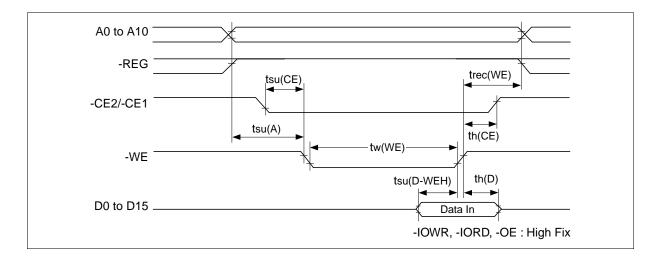

### Task File Register Access Timing Example (2)

#### 3. True IDE Mode

The card can be configured in a True IDE mode of operation. This card is configured in this mode only when the -OE input signal is asserted GND by the host. In this True IDE mode Attribute Registers are not accessible from the host. Only I/O operation to the task file and data register are allowed. If this card is configured during power on sequence, data register are accessed in word (16-bit). The card permits 8-bit accesses if the user issues a Set Feature Command to put the device in 8-bit mode.

True IDE Mode Read I/O Function

| Mode                    | -CE2 | -CE1 | A0 to A | 2 -IORD | -IOWR | D8 to D15 | D0 to D7   |

|-------------------------|------|------|---------|---------|-------|-----------|------------|

| Invalid mode            | L    | L    | ×       | ×       | ×     | High-Z    | High-Z     |

| Standby mode            | Н    | Н    | ×       | ×       | ×     | High-Z    | High-Z     |

| Data register access    | Н    | L    | 0       | L       | Н     | odd byte  | even byte  |

| Alternate status access | L    | Н    | 6H      | L       | Н     | High-Z    | status out |

| Other task file access  | Н    | L    | 1-7H    | L       | Н     | High-Z    | data       |

Note: x: L or H

True IDE Mode Write I/O Function

| Mode                    | -CE2 | -CE1 | A0 to A | 2 -IORD | -IOWR | D8 to D15  | D0 to D7   |

|-------------------------|------|------|---------|---------|-------|------------|------------|

| Invalid mode            | L    | L    | ×       | ×       | ×     | don't care | don't care |

| Standby mode            | Н    | Н    | ×       | ×       | ×     | don't care | don't care |

| Data register access    | Н    | L    | 0       | Н       | L     | odd byte   | even byte  |

| Control register access | L    | Н    | 6H      | Н       | L     | don't care | control in |

| Other task file access  | Н    | L    | 1-7H    | Н       | L     | don't care | data       |

Note: x: L or H

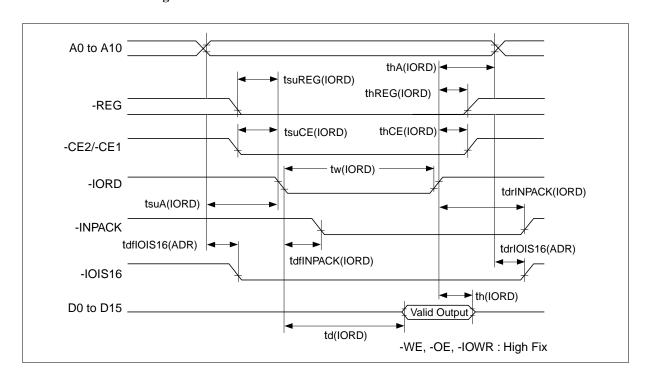

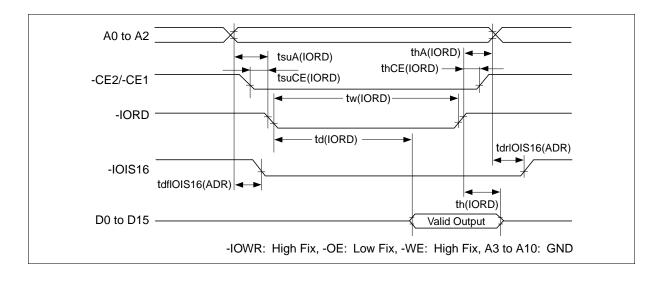

True IDE Mode I/O Access Timing Example

#### Configuration register specifications

This card supports four Configuration registers for the purpose of the configuration and observation of this card. These registers can be used in memory card mode and I/O card mode. In True IDE mode, these registers can not be used.

#### 1. Configuration Option register (Address 200H)

This register is used for the configuration of the card configuration status and for the issuing soft reset to the card.

| bit7   | bit6    | bit5  | bit4 | bit3 | bit2 | bit1 | bit0 |

|--------|---------|-------|------|------|------|------|------|

| SRESET | LevIREQ | INDEX |      |      |      |      |      |

Note: initial value: 00H

| Name                | R/W | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRESET<br>(HOST->)  | R/W | Setting this bit to "1", places the card in the reset state (Card Hard Reset). This operation is equal to Hard Reset, except this bit is not cleared. Then this bit set to "0", places the card in the reset state of Hard Reset (This bit is set to "0" by Hard Reset). Card configuration status is reset and the card internal initialized operation starts when Card Hard Reset is executed, so next access to the card should be the same sequence as the power on sequence. |

| LevIREQ<br>(HOST->) | R/W | This bit sets to "0" when pulse mode interrupt is selected, and "1" when level mode interrupt is selected.                                                                                                                                                                                                                                                                                                                                                                        |

| INDEX<br>(HOST->)   | R/W | This bits is used for select operation mode of the card as follows.  When Power on, Card Hard Reset and Soft Reset, this data is "000000" for the purpose of Memory card interface recognition.                                                                                                                                                                                                                                                                                   |

#### **INDEX** bit assignment

#### **INDEX** bit

| 5 | 4 | 3 | 2 | 1 | 0 | Card mode   | Task File register address | Mapping mode          |

|---|---|---|---|---|---|-------------|----------------------------|-----------------------|

| 0 | 0 | 0 | 0 | 0 | 0 | Memory card | 0H to FH, 400H to 7FFH     | memory mapped         |

| 0 | 0 | 0 | 0 | 0 | 1 | I/O card    | xx0H to xxFH               | contiguous I/O mapped |

| 0 | 0 | 0 | 0 | 1 | 0 | I/O card    | 1F0H to 1F7H, 3F6H to 3F7H | primary I/O mapped    |

| 0 | 0 | 0 | 0 | 1 | 1 | I/O card    | 170H to 177H, 376H to 377H | secondary I/O mapped  |

### 2. Configuration and Status register (Address 202H)

This register is used for observing the card state.

| bit7  | bit6   | bit5  | bit4 | bit3 | bit2 | bit1 | bit0 |

|-------|--------|-------|------|------|------|------|------|

| CHGED | SIGCHG | IOIS8 | 0    | 0    | PWD  | INTR | 0    |

Note: initial value: 00H

| Name               | R/W | Function                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHGED<br>(CARD->)  | R   | This bit indicates that CRDY/-BSY bit on Pin Replacement register is set to "1". When CHGED bit is set to "1", -STSCHG pin is held "L" at the condition of SIGCHG bit set to "1" and the card configured for the I/O interface.                                                                                                                                                                                                   |

| SIGCHG<br>(HOST->) | R/W | This bit is set or reset by the host for enabling and disabling the status-change signal (-STSCHG pin). When the card is configured I/O card interface and this bit is set to "1", -STSCHG pin is controlled by CHGED bit. If this bit is set to "0", -STSCHG pin is kept "H".                                                                                                                                                    |

| IOIS8<br>(HOST->)  | R/W | The host sets this field to "1" when it can provide I/O cycles only with on 8 bit data bus (D7 to D0).                                                                                                                                                                                                                                                                                                                            |

| PWD<br>(HOST->)    | R/W | When this bit is set to "1", the card enters sleep state (Power Down mode). When this bit is reset to "0", the card transfers to idle state (active mode). RRDY/-BSY bit on Pin Replacement Register becomes BUSY when this bit is changed. RRDY/-BSY will not become Ready until the power state requested has been entered. This card automatically powers down when it is idle, and powers back up when it receives a command. |

| INTR<br>(CARD->)   | R   | This bit indicates the internal state of the interrupt request. This bit state is available whether I/O card interface has been configured or not. This signal remains true until the condition which caused the interrupt request has been serviced. If interrupts are disabled by the -IEN bit in the Device Control Register, this bit is a zero.                                                                              |

#### 3. Pin Replacement register (Address 204H)

This register is used for providing the signal state of -IREQ signal when the card configured I/O card interface.

| bit7 | bit6 | bit5      | bit4 | bit3 | bit2 | bit1      | bit0 |

|------|------|-----------|------|------|------|-----------|------|

| 0    | 0    | CRDY/-BSY | 0    | 1    | 1    | RRDY/-BSY | 0    |

Note: initial value: 0CH

| Name                  | R/W | Function                                                                                                   |

|-----------------------|-----|------------------------------------------------------------------------------------------------------------|

| CRDY/-BSY<br>(HOST->) | R/W | This bit is set to "1" when the RRDY/-BSY bit changes state. This bit may also be written by the host.     |

| RRDY/-BSY<br>(HOST->) | R/W | When read, this bit indicates +READY pin states. When written, this bit is used for CRDY/-BSY bit masking. |

#### 4. Socket and Copy register (Address 206H)

This register is used for identification of the card from the other cards. Host can read and write this register. This register should be set by host before this card's Configuration Option register set.

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|------|------|------|------|------|------|------|------|

| 0    | 0    | 0    | DRV# | 0    | 0    | 0    | 0    |

Note: initial value: 00H

| Name             | R/W | Function                                                                                                                                                                                                                 |

|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRV#<br>(HOST->) | R/W | This fields are used for the configuration of the plural cards. When host configures the plural cards, written the card's copy number in this field. In this way, host can perform the card's master/slave organization. |

### **CIS** informations

CIS informations are defined as follows. By reading attribute address from "0000 H", card CIS informations can be confirmed.

| Address | Data | 7 6 5 4                           | 3 2             | 1 0           | Description of contents                                                       | CIS function                        |

|---------|------|-----------------------------------|-----------------|---------------|-------------------------------------------------------------------------------|-------------------------------------|

| 000H    | 01H  | CISTPL_DEVIC                      | E               |               | Device info tuple                                                             | Tuple code                          |

| 002H    | 04H  | TPL_LINK                          |                 |               | Link length is 4 byte                                                         | Link to next tuple                  |

| 004H    | DFH  |                                   | W De<br>P<br>S  | vice speed    | Device type = DH: I/O device<br>WPS = 1: No WP<br>Device speed = 7: ext speed | Device type, WPS, speed             |

| 006H    | 4AH  | EXT Speed mantissa                |                 | eed<br>oonent | 400 ns if no wait                                                             | Extended speed                      |

| H800    | 01H  | 1x                                | 2k              | units         | 2k byte of address space                                                      | Device size                         |

| 00AH    | FFH  | List end marker                   |                 |               | End of device                                                                 | END marker                          |

| 00CH    | 1CH  | CISTPL_DEVIC                      | E_OC            |               | Other conditions device info tuple                                            | Tuple code                          |

| 00EH    | 04H  | TPL_LINK                          |                 |               | Link length is 4 bytes                                                        | Link to next tuple                  |

| 010H    | 02H  | EXT Reserved                      | V <sub>cc</sub> | MWAIT         | 3 V, wait is not used                                                         | Other conditions info field         |

| 012H    | D9H  |                                   | W De<br>P<br>S  | vice speed    | Device type = DH: I/O device<br>WPS = 1: No WP<br>Device speed = 1: 250 ns    | Device type, WPS, speed             |

| 014H    | 01H  | 1x                                | 2k              | units         | 2k byte of address space                                                      | Device size                         |

| 016H    | FFH  | List end marker                   |                 |               | End of device                                                                 | END marker                          |

| 018H    | 18H  | CISTPL_JEDEC                      | C_C             |               | JEDEC ID common memory                                                        | Tuple code                          |

| 01AH    | 02H  | TPL_LINK                          |                 |               | Link length is 2 bytes                                                        | Link to next tuple                  |

| 01CH    | DFH  | PCMCIA's manu<br>ID code          | ufactur         | er's JEDEC    | Manufacturer's ID code                                                        | JEDEC ID of PC Card ATA             |

| 01EH    | 01H  | PCMCIA JEDEC                      | devic           | e code        | 2nd byte of JEDEC ID                                                          |                                     |

| 020H    | 20H  | CISTPL_MANFI                      | D               |               | Manufacturer's ID code                                                        | Tuple code                          |

| 022H    | 04H  | TPL_LINK                          |                 |               | Link length is 4 bytes                                                        | Link to next tuple                  |

| 024H    | 07H  | Low byte of PCN manufacturer's of |                 |               | HITACHI JEDEC<br>manufacturer's ID                                            | Low byte of manufacturer's ID code  |

| 026H    | 00H  | High byte of PCI manufacturer's o |                 |               | Code of 0 because other byte is JEDEC 1 byte manufacture's ID                 | High byte of manufacturer's ID code |

| 028H    | 00H  | Low byte of prod                  | duct co         | de            | HITACHI code for PC CARD ATA                                                  | Low byte of product code            |

| 02AH    | 00H  | High byte of prod                 | duct co         | ode           | -                                                                             | High byte of product code           |

| Address | Data | 7 6 5 4 3 2 1 0       | Description of contents                                    | CIS function               |

|---------|------|-----------------------|------------------------------------------------------------|----------------------------|

| 02CH    | 15H  | CISTPL_VERS_1         | Level 1 version/product info                               | Tuple code                 |

| 02EH    | 15H  | TPL_LINK              | Link length is 15h bytes                                   | Link to next tuple         |

| 030H    | 04H  | TPPLV1_MAJOR          | PCMCIA2.0/JEIDA4.1                                         | Major version              |

| 032H    | 01H  | TPPLV1_MINOR          | PCMCIA2.0/JEIDA4.1                                         | Minor version              |

| 034H    | 48H  |                       | 'H'                                                        | Info string 1              |

| 036H    | 49H  |                       | 11'                                                        | _                          |

| 038H    | 54H  |                       | 'Т'                                                        | _                          |

| 03AH    | 41H  |                       | ' A '                                                      | -                          |

| 03CH    | 43H  |                       | 'С'                                                        | -                          |

| 03EH    | 48H  |                       | 'H'                                                        | _                          |

| 040H    | 49H  |                       | 11'                                                        | -                          |

| 042H    | 00H  |                       | Null terminator                                            | _                          |

| 044H    | 46H  |                       | 'F'                                                        | Info string 2              |

| 046H    | 4CH  |                       | ' L '                                                      | -                          |

| 048H    | 41H  |                       | ' А '                                                      | _                          |

| 04AH    | 53H  |                       | 'S'                                                        | _                          |

| 04CH    | 48H  |                       | 'H'                                                        | -                          |

| 04EH    | 00H  |                       | Null terminator                                            | -                          |

| 050H    | 35H  |                       | ' 5 '                                                      | Vender specific strings    |

| 052H    | 2EH  |                       | . ,                                                        | _                          |

| 054H    | 30H  |                       | · 0 ·                                                      | _                          |

| 056H    | 00H  |                       | Null terminator                                            | _                          |

| 058H    | FFH  | List end marker       | End of device                                              | END marker                 |

| 05AH    | 21H  | CISTPL_FUNCID         | Function ID tuple                                          | Tuple code                 |

| 05CH    | 02H  | TPL_LINK              | Link length is 2 bytes                                     | Link to next tuple         |

| 05EH    | 04H  | TPLFID_FUNCTION = 04H | Disk function, may be silicon, may be removable            | PC card function code      |

| 060H    | 01H  | Reserved R P          | R = 0: No BIOS ROM<br>P = 1: Configure card at<br>power on | System initialization byte |

| Address | Data | 7 6       | 5     | 4    | 3    | 2   | 1          | 0        | Description of contents                                                                                                                                                                                  | CIS function                                   |

|---------|------|-----------|-------|------|------|-----|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| 062H    | 22H  | CISTPL    | _FU   | INC  | Έ    |     |            |          | Function extension tuple                                                                                                                                                                                 | Tuple code                                     |

| 064H    | 02H  | TPL_LII   | NK    |      |      |     |            |          | Link length is 2 bytes                                                                                                                                                                                   | Link to next tuple                             |

| 066H    | 01H  | Disk fur  | nctio | n e  | xter | sio | n tu       | ple type | Disk interface type                                                                                                                                                                                      | Extension tuple type for disk                  |

| 068H    | 01H  | Disk into | erfac | ce t | ype  |     |            |          | PC card ATA interface                                                                                                                                                                                    | Interface type                                 |

| 06AH    | 22H  | CISTPL    | _FU   | JNC  | Έ    |     |            |          | Function extension tuple                                                                                                                                                                                 | Tuple code                                     |

| 06CH    | 03H  | TPL_LII   | NK    |      |      |     |            |          | Link length is 3 bytes                                                                                                                                                                                   | Link to next tuple                             |

| 06EH    | 02H  | Disk fur  | nctio | n e  | xter | sio | n tu       | ple type | Single drive                                                                                                                                                                                             | Extension tuple type for disk                  |

| 070H    | 0CH  | Reserve   | ed    | D    | U    | S   | V          |          | No $V_{PP}$ , silicon, single drive $V = 0$ : No $V_{PP}$ required $S = 1$ : Silicon $U = 1$ : Unique serial # $D = 0$ : Single drive on card                                                            | Basic ATA option parameters byte 1             |

| 072H    | 0FH  | R I       | E     | N    | P3   | P2  | P1         | P0       | P0: Sleep mode supported P1: Standby mode supported P2: Idle mode suppported P3: Drive auto power control N: Some config excludes 3X7 E: Index bit is emulated I: Twin IOIS16# data reg only R: Reserved | Basic ATA option parameters byte 2             |

| 074H    | 1AH  | CISTPL    | CC    | ONF  | IG   |     |            |          | Configuration tuple                                                                                                                                                                                      | Tuple code                                     |

| 076H    | 05H  | TPL_LII   | NK    |      |      |     |            |          | Link length is 5 bytes                                                                                                                                                                                   | Link to next tuple                             |

| 078H    | 01H  | RFS       | RM    | /IS  |      |     | R <i>A</i> | AS       | RFS: Reserved RMS: TPCC_RMSK size - 1 = 0 RAS: TPCC_RADR size - 1 = 1 1 byte register mask 2 byte config base address                                                                                    | Size of fields byte TPCC_SZ                    |

| 07AH    | 03H  | TPCC_     | LAS   | Т    |      |     |            |          | Entry with config index of 03H is final entry in table                                                                                                                                                   | Last entry of config registers                 |

| 07CH    | 00H  | TPCC_     | RAD   | )R ( | LSE  | 3)  |            |          | Configuration registers are located at 200H in REG space                                                                                                                                                 | Location of config registers                   |

| 07EH    | 02H  | TPCC_     | RAD   | )R ( | MS   | B)  |            |          | <del>-</del>                                                                                                                                                                                             |                                                |

| 080H    | 0FH  | Reserve   | ed    |      | S    | Р   | С          | I        | I: Configuration index C: Configuration and status P: Pin replacement S: Socket and copy                                                                                                                 | Configuration registers present mask TPCC_RMSK |

| Address | Data | 7 6 5 4 3 2 1 0                 | Description of contents                                                                                                                                                                                        | CIS function                                  |

|---------|------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 082H    | 1BH  | CISTPL_CFTABLE_ENTRY            | Configuration table entry tuple                                                                                                                                                                                | Tuple code                                    |

| 084H    | 08H  | TPL_LINK                        | Link length is 8 bytes                                                                                                                                                                                         | Link to next tuple                            |

| 086H    | COH  | I D Configuration index         | Memory mapped I/O configuration I = 1: Interface byte follows D = 1: Default entry Configuration index = 0                                                                                                     | Configuration table index byte TPCE_INDX      |

| 088H    | 40H  | W R P B Interface type          | W = 0: Wait not used R = 1: Ready active P = 0: WP used B = 0: BVD1 and BVD2 not used IF type = 0: Memory interface                                                                                            | Interface description field TPCE_IF           |

| 08AH    | A1H  | M MS IR IO T P                  | M = 1: Misc info present MS = 01: Memory space info single 2-byte length IR = 0: No interrupt info present IO = 0: No I/O port info present T = 0: No timing info present P = 1: V <sub>CC</sub> only info     | Feature selection byte TPCE_FS                |

| 08CH    | 01H  | R DIPIAISIHVLVNV                | Nominal voltage only follows R: Reserved DI: Power down current info PI: Peak current info AI: Average current info SI: Static current info HV: Max voltage info LV: Min voltage info NV: Nominal voltage info | Power parameters for V <sub>cc</sub>          |

| 08EH    | 55H  | X Mantissa Exponent             | Nominal voltage = 5 V                                                                                                                                                                                          | V <sub>cc</sub> nominal value                 |

| 090H    | 08H  | Length in 256 bytes pages (LSB) | Length of memory space is 2 kB                                                                                                                                                                                 | Memory space description structures (TPCE_MS) |

| 092H    | 00H  | Length in 256 bytes pages (MSB) | _                                                                                                                                                                                                              |                                               |

| 094H    | 20H  | X R P ROAT                      | X = 0: No more misc fields R: Reserved P = 1: Power down supported RO = 0: Not read only mode A = 0: Audio not supported T = 0: Single drive                                                                   | Miscellaneous features field<br>TPCE_MI       |

| Address | Data | 7    | 6    | 5    | 4    | 3   | 2          | 1    | (    | )  | Description of contents                                                                                                                                                                                        | CIS function                             |

|---------|------|------|------|------|------|-----|------------|------|------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| 096H    | 1BH  | CIST | ΓPL_ | _CF  | TAE  | 3LE | <u>_</u> E | N٦   | ΓR\  | 1  | Configuration table entry tuple                                                                                                                                                                                | Tuple code                               |

| 098H    | 06H  | TPL  | LIN  | IK   |      |     |            |      |      |    | Link length is 6 bytes                                                                                                                                                                                         | Link to next tuple                       |

| 09AH    | 00H  | I    | D    | Cor  | nfig | ura | tion       | n ir | nde  | х  | Memory mapped I/O configuration I = 0: No Interface byte D = 0: No Default entry Configuration index = 0                                                                                                       | Configuration table index byte TPCE_INDX |

| 09CH    | 01H  | M    | MS   | 3    | IR   | IO  | Т          | F    |      |    | M = 0: No Misc info MS = 00: No Memory space info IR = 0: No interrupt info present IO = 0: No I/O port info present T = 0: No timing info present P = 1: V <sub>cc</sub> only info                            | Feature selection byte TPCE_FS           |

| 09EH    | 21H  | R    | DI   | PI   | AI   | SI  | H          | / L  | 1 V. | NV | Nominal voltage only follows R: Reserved DI: Power down current info PI: Peak current info AI: Average current info SI: Static current info HV: Max voltage info LV: Min voltage info NV: Nominal voltage info | Power parameters for V <sub>cc</sub>     |

| 0A0H    | B5H  | Χ    | Ма   | ntis | sa   |     | Ex         | фc   | one  | nt | Nominal voltage = 3.0 V                                                                                                                                                                                        | V <sub>cc</sub> nominal value            |

| 0A2H    | 1EH  | Χ    | Ext  | ens  | ion  |     |            |      |      |    | +0.3 V                                                                                                                                                                                                         | Extension byte                           |

| 0A4H    | 4DH  | Х    | Ма   | ntis | sa   |     | Ex         | ф    | one  | nt | Max average current over 10 msec is 45 mA                                                                                                                                                                      | Max. average current                     |

| Address | Data | 7    | 6   | 5    | 4    | 3    | 2     | 1    | 0   | Description of contents                                                                                                                                                                                            | CIS function                                    |