# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note : Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

# 7630 Group

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

#### DESCRIPTION

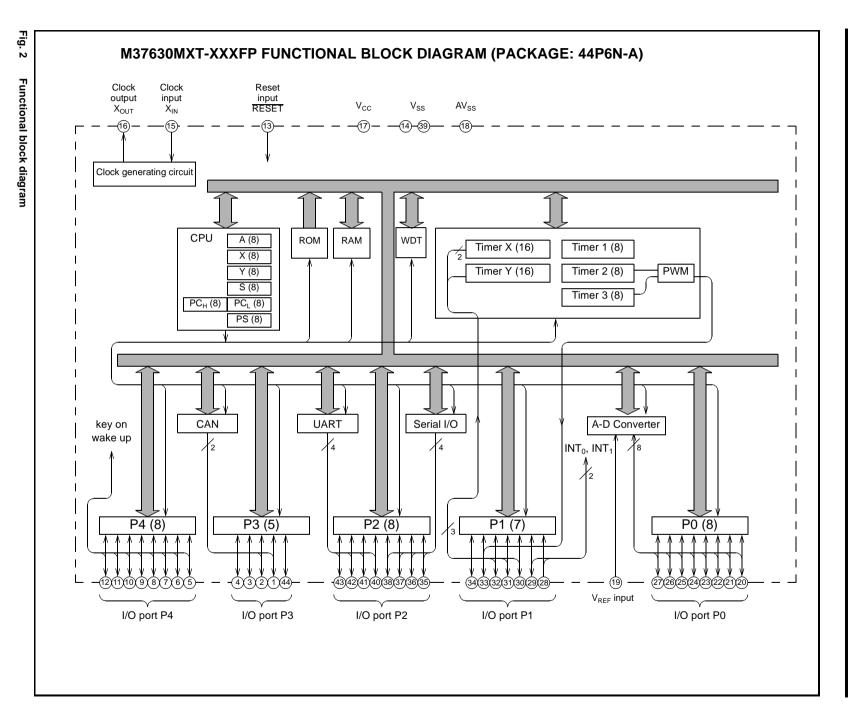

The 7630 group is a single chip 8-bit microcomputer designed with CMOS silicon gate technology.

Being equipped with a CAN (Controller Area Network) module circuit, the microcomputer is suited to drive automotive equipments. The CAN module complies with CAN specification version 2.0, part B and allows priority-based message management.

In addition to the microcomputers simple instruction set, the ROM, RAM and I/O addresses are placed in the same memory map to enable easy programming.

The built-in ROM is available as mask ROM or One Time PROM. For development purposes, emulator- and EPROM-type microcomputers are available as well.

## **FEATURES**

| ٠ | Basic machine-language instructions71                                             |

|---|-----------------------------------------------------------------------------------|

| • | Minimum instruction execution time                                                |

|   | (at 10 MHz oscillation frequency)0.2 μs                                           |

| • | Memory size<br>ROM16252 bytes (M37630M4T-XXXFP)<br>RAM512 bytes (M37630M4T-XXXFP) |

| ٠ | I/O ports                                                                         |

|   | Programmable I/O ports                                                            |

|   | Input                                                                             |

| • | Interrupts 24 sources, 24 vectors                             |

|---|---------------------------------------------------------------|

| • | Timers                                                        |

|   | 16-bit Timers 2 channels                                      |

|   | 8-bit Timers 3 channels                                       |

| • | Serial I/Os                                                   |

|   | Clock synchronous 1 channel                                   |

|   | UART 1 channel                                                |

| • | CAN module                                                    |

|   | (CAN specification version 2.0, part B)1 channel              |

| • | A-D converter                                                 |

| • | Watchdog timer1                                               |

| • | Clock Generating Circuit1                                     |

|   | Built-in with internal feedback resistor                      |

| • | Power source voltage                                          |

|   | (at 10 MHz oscillation frequency) 4.0 to 5.5 V                |

| • | Power dissipation                                             |

|   | In high-speed mode                                            |

|   | (at 8 MHz oscillation frequency, at 5 V power source voltage) |

| • | Operating temperature range                                   |

| • | Package                                                       |

# APPLICATION

Automotive controls

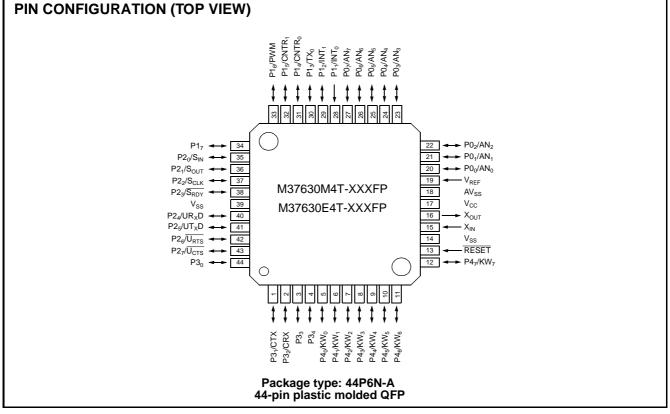

Fig. 1 Pin configuration of M37630M4T–XXXFP

мітзивізні міскосомритекз 7630 Group

Renesas Technology Corp.

Ν

# **PIN DESCRIPTION**

#### Table 1: Pin description

| Pin                                                                                                                                             | Name                           | Input/Output | Description                                                                                                                                                                                                            |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| $V_{CC}, V_{SS}$                                                                                                                                | Power source voltage           |              | Power supply pins; apply 4.0 to 5.5 V to $V_{\text{CC}}$ and 0 V to $V_{\text{SS}}$                                                                                                                                    |  |  |  |  |  |

| AV <sub>SS</sub>                                                                                                                                | Analog power<br>source voltage |              | Ground pin for A-D converter. Connect to V <sub>SS</sub>                                                                                                                                                               |  |  |  |  |  |

| RESET                                                                                                                                           | Reset input                    | Input        | Reset pin. This pin must be kept at "L" level for more than 2 $\mu$ s, to enter the reset state. If the crystal or ceramic resonator requires more time to stabilize, extend the "L" level period.                     |  |  |  |  |  |

| X <sub>IN</sub>                                                                                                                                 | Clock input                    | Input        | Input and output pins of the internal clock generating circuit. Connect a ceramic or                                                                                                                                   |  |  |  |  |  |

| X <sub>OUT</sub>                                                                                                                                | Clock output                   | Output       | quartz–crystal resonator between the X <sub>IN</sub> and X <sub>OUT</sub> pins. When an external clock source is used, connect it to X <sub>IN</sub> and leave X <sub>OUT</sub> open.                                  |  |  |  |  |  |

| V <sub>REF</sub>                                                                                                                                | Reference volt-<br>age input   | Input        | Reference voltage input pin for A-D converter                                                                                                                                                                          |  |  |  |  |  |

| P0 <sub>0</sub> /AN <sub>0</sub> —<br>P0 <sub>7</sub> /AN <sub>7</sub>                                                                          | I/O port P0                    | I/O          | CMOS I/O ports or analog input ports                                                                                                                                                                                   |  |  |  |  |  |

| P1 <sub>1</sub> /INT <sub>0</sub>                                                                                                               |                                | Input        | CMOS input port or external interrupt input port. The active edge (rising or falling) of external interrupts can be selected. This pin will be used as $V_{PP}$ pin during PROM programming of One Time PROM Versions. |  |  |  |  |  |

| P1 <sub>2</sub> /INT <sub>1</sub>                                                                                                               |                                | 1/0          | CMOS I/O port or external interrupt input port. The active edge (rising or falling) of external interrupts can be selected.                                                                                            |  |  |  |  |  |

| P1 <sub>3</sub> /TX <sub>0</sub>                                                                                                                |                                |              | CMOS I/O port or input pin used in the bi-phase counter mode                                                                                                                                                           |  |  |  |  |  |

| P1 <sub>4</sub> /CNTR <sub>0</sub>                                                                                                              | I/O port P1                    |              | /O CMOS I/O port or timer X input pin used for the event counter, pulse width mean ment and bi-phase counter mode                                                                                                      |  |  |  |  |  |

| P1 <sub>5</sub> /CNTR <sub>1</sub>                                                                                                              |                                |              | CMOS I/O port or timer Y input pin used for the event counter, pulse width and puperiod measurement mode                                                                                                               |  |  |  |  |  |

| P1 <sub>6</sub> /PWM                                                                                                                            |                                |              | CMOS I/O port or PWM output pin used in the PWM mode of timers 2 and 3                                                                                                                                                 |  |  |  |  |  |

| P1 <sub>7</sub>                                                                                                                                 |                                |              | CMOS I/O port                                                                                                                                                                                                          |  |  |  |  |  |

| P2 <sub>0</sub> /S <sub>IN</sub><br>P2 <sub>1</sub> /S <sub>OUT</sub><br>P2 <sub>2</sub> /S <sub>CLK</sub><br>P2 <sub>3</sub> /S <sub>RDY</sub> | 1/0                            | 1/0          | CMOS I/O ports or clock synchronous serial I/O pins                                                                                                                                                                    |  |  |  |  |  |

| $\begin{array}{c} P2_4/UR_XD\\ P2_5/UT_XD\\ P2_6/\overline{U_{RTS}}\\ P2_7/\overline{U_{CTS}} \end{array}$                                      | - I/O port P2                  | I/O          | CMOS I/O ports or asynchronous serial I/O pins                                                                                                                                                                         |  |  |  |  |  |

| P3 <sub>0</sub>                                                                                                                                 |                                |              | CMOS I/O port                                                                                                                                                                                                          |  |  |  |  |  |

| P3 <sub>1</sub> /CTX                                                                                                                            | I/O port D2                    | 1/0          | CMOS I/O port or CAN transmit data pin                                                                                                                                                                                 |  |  |  |  |  |

| P3 <sub>2</sub> /CRX                                                                                                                            | I/O port P3                    | I/O          | CMOS I/O port or CAN receive data pin                                                                                                                                                                                  |  |  |  |  |  |

| P3 <sub>3</sub> —P3 <sub>4</sub>                                                                                                                |                                |              | CMOS I/O port                                                                                                                                                                                                          |  |  |  |  |  |

| P4 <sub>0</sub> /KW <sub>0</sub> —<br>P4 <sub>7</sub> /KW <sub>7</sub>                                                                          | I/O port P4                    | I/O          | CMOS I/O ports. These ports can be used for key-on wake-up when configured as inputs.                                                                                                                                  |  |  |  |  |  |

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

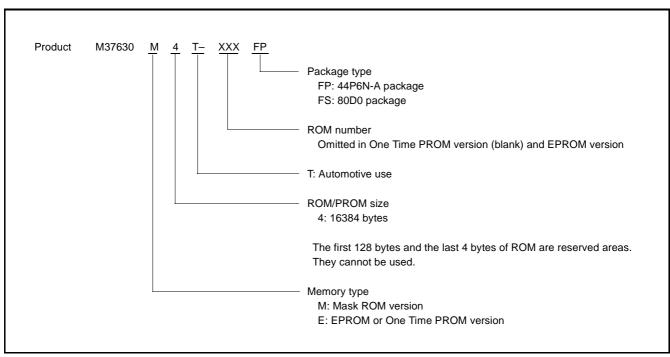

Fig. 3 Part numbering

PART NUMBERING

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

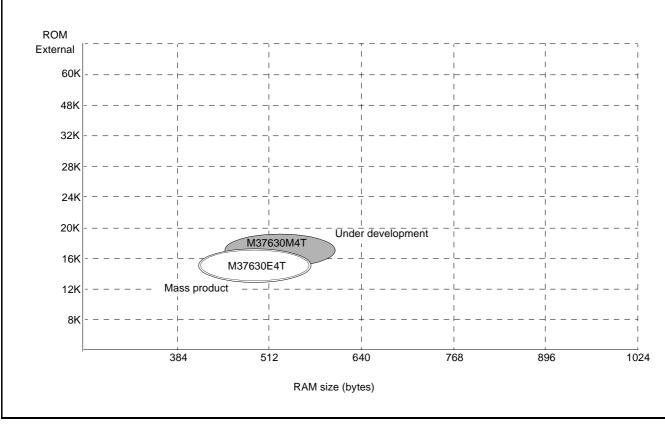

## **GROUP EXPANSION**

Mitsubishi plans to expand the 7630 group as follows:

#### **Memory Type**

Support mask ROM, One Time PROM and EPROM versions.

#### **Memory Size**

| ROM/PROM siz | e 16 Kbytes                    |

|--------------|--------------------------------|

| RAM size     |                                |

| Package      |                                |

| 44P6N-A      | 0.8mm-pitch plastic molded QFP |

80D0 .....0.8mm-pitch ceramic LCC (EPROM version)

Fig. 4 Memory expansion plan

#### Currently supported products are listed below:

#### Table 2: List of supported products

As of March 1998

| Product         | (P)ROM size (bytes)<br>ROM size for User ( ) | RAM size (bytes) | Package | Remarks                       |  |  |

|-----------------|----------------------------------------------|------------------|---------|-------------------------------|--|--|

| M37630M4T-XXXFP |                                              |                  |         | Mask ROM version              |  |  |

| M37630E4T-XXXFP | 16384 512                                    |                  | 44P6N-A | One Time PROM version         |  |  |

| M37630E4FP      | (16252)                                      |                  |         | One Time PROM version (blank) |  |  |

| M37630E4FS      |                                              |                  | 80D0    | EPROM version                 |  |  |

# FUNCTIONAL DESCRIPTION

#### **Central Processing Unit (CPU)**

The core of 7630 group microcomputers is the 7600 series CPU. This core is based on the standard instruction set of 740 series; however the performance is improved by allowing to execute the same instructions as that of the 740 series in less cycles. Refer to the 7600 Series Software Manual for details of the instruction set.

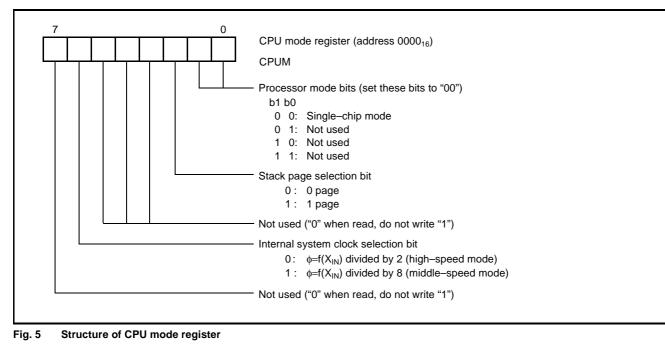

#### **CPU Mode Register CPUM**

The CPU mode register contains the stack page selection bit and internal system clock selection bit. The CPU mode register is allocated to address  $0000_{16}$ .

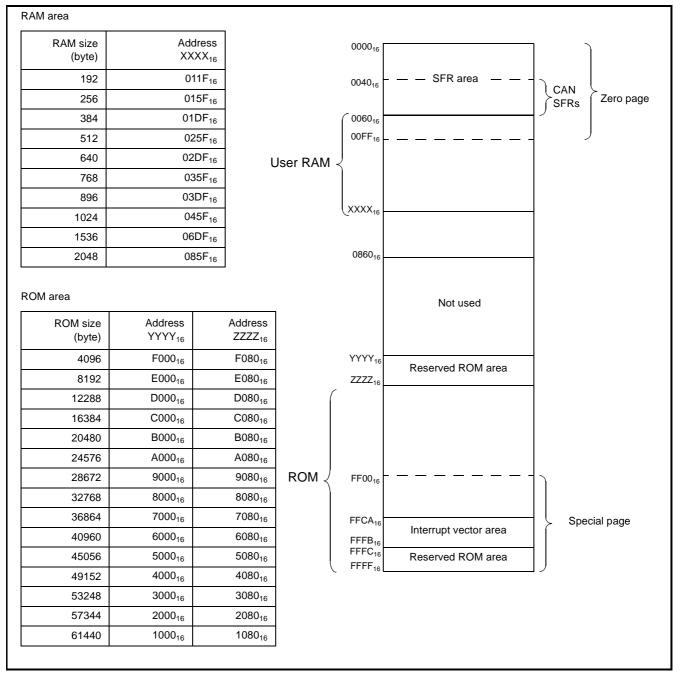

### MEMORY

#### Special Function Register (SFR) Area

The special function register (SFR) area contains the registers relating to functions such as I/O ports and timers.

#### RAM

RAM is used for data storage and for stack area of subroutine calls and interrupts.

#### ROM

ROM is used for storing user's program code as well as the interrupt vector area.

#### **Interrupt Vector Area**

The interrupt vector area is for storing jump destination addresses used at reset or when an interrupt is generated.

#### Zero Page

This area can be accessed most efficiently by means of the zero page addressing mode.

#### **Special Page**

This area can be accessed most efficiently by means of the special page addressing mode.

Fig. 6 Memory map diagram

# SPECIAL FUNCTION REGISTERS (SFR)

| -                  | CPU mode register                     | CPUM   |

|--------------------|---------------------------------------|--------|

| 0001 <sub>16</sub> | Not used                              |        |

| -                  | Interrupt request register A          | IREQA  |

| -                  | Interrupt request register B          | IREQB  |

| -                  | Interrupt request register C          | IREQC  |

| 0005 <sub>16</sub> | Interrupt control register A          | ICONA  |

| -                  | Interrupt control register B          | ICONB  |

| 0007 <sub>16</sub> | Interrupt control register C          | ICONC  |

| 0008 <sub>16</sub> | Port P0 register                      | P0     |

| -                  | Port P0 direction register            | P0D    |

|                    | Port P1 register                      | P1     |

| 000B <sub>16</sub> | Port P1 direction register            | P1D    |

|                    | Port P2 register                      | P2     |

| 000D <sub>16</sub> | Port P2 direction register            | P2D    |

| 000E <sub>16</sub> | Port P3 register                      | P3     |

| 000F <sub>16</sub> | Port P3 direction register            | P3D    |

| 0010 <sub>16</sub> | Port P4 register                      | P4     |

| 0011 <sub>16</sub> | Port P4 direction register            | P4D    |

| 0012 <sub>16</sub> | Serial I/O shift register             | SIO    |

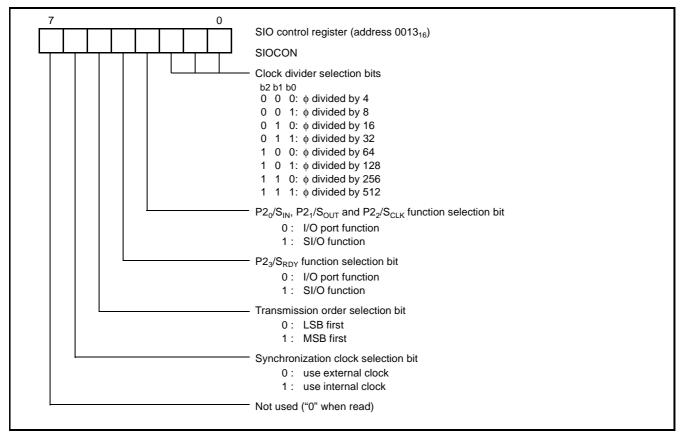

| 0013 <sub>16</sub> | Serial I/O control register           | SIOCON |

| 0014 <sub>16</sub> | A-D conversion register               | AD     |

| 0015 <sub>16</sub> | A-D control register                  | ADCON  |

| 0016 <sub>16</sub> | Timer 1                               | T1     |

| 0017 <sub>16</sub> | Timer 2                               | T2     |

| 0018 <sub>16</sub> | Timer 3                               | Т3     |

| 0019 <sub>16</sub> | Timer 123 mode register               | T123M  |

| 001A <sub>16</sub> | Timer XL                              | TXL    |

| 001B <sub>16</sub> | Timer XH                              | TXH    |

| 001C <sub>16</sub> | Timer YL                              | TYL    |

| 001D <sub>16</sub> | Timer YH                              | TYH    |

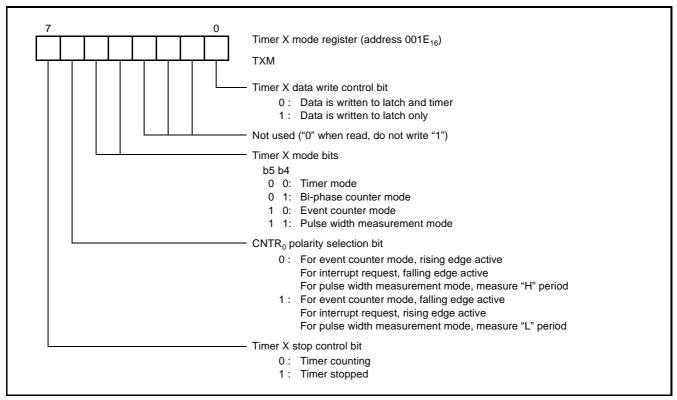

| 001E <sub>16</sub> | Timer X mode register                 | TXM    |

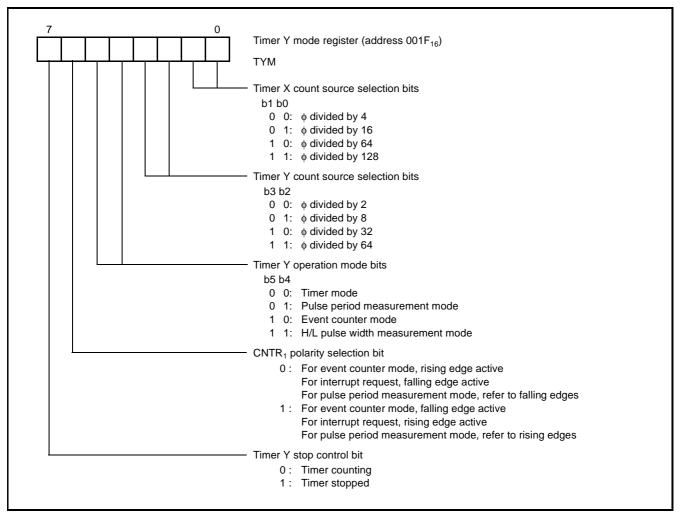

| 001F <sub>16</sub> | Timer Y mode register                 | TYM    |

| 0020 <sub>16</sub> | UART mode register                    | UMOD   |

| 0021 <sub>16</sub> | UART baud rate generator              | UBRG   |

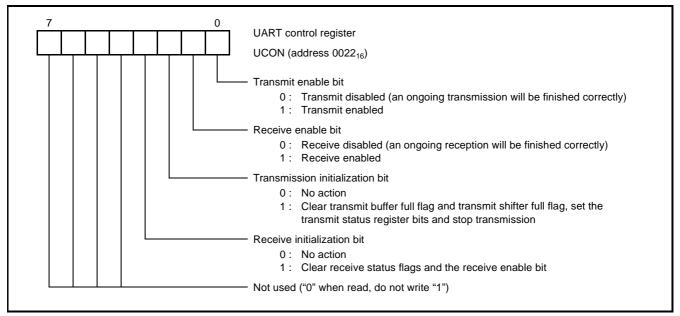

| 0022 <sub>16</sub> | UART control register                 | UCON   |

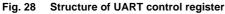

| 0023 <sub>16</sub> | UART status register                  | USTS   |

| 0024 <sub>16</sub> | UART transmit buffer register 1       | UTBR1  |

| 0025 <sub>16</sub> | UART transmit buffer register 2       | UTBR2  |

| 0026 <sub>16</sub> | UART receive buffer register 1        | URBR1  |

| 0027 <sub>16</sub> | UART receive buffer register 2        | URBR2  |

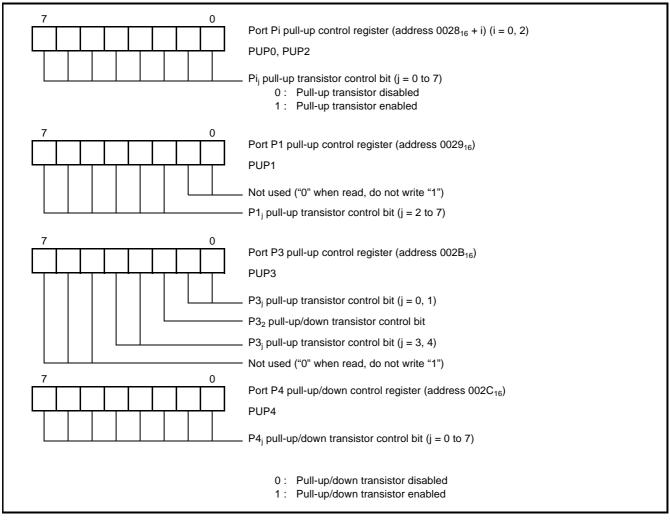

| 0028 <sub>16</sub> | Port P0 pull-up control register      | PUP0   |

| 0029 <sub>16</sub> | Port P1 pull-up control register      | PUP1   |

| 002A <sub>16</sub> | Port P2 pull-up control register      | PUP2   |

| 002B <sub>16</sub> | Port P3 pull-up control register      | PUP3   |

| 002C <sub>16</sub> | Port P4 pull-up/down control register | PUP4   |

| 002D <sub>16</sub> | Interrupt polarity selection register | IPOL   |

| 002E <sub>16</sub> | Watchdog timer register               | WDT    |

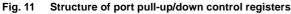

| 002F <sub>16</sub> | Polarity control register             | PCON   |

|                    |                                       |        |

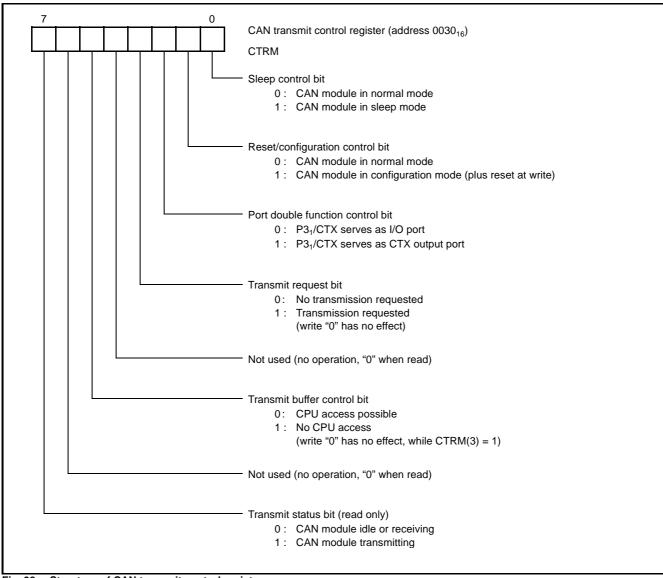

|                    | CAN transmit control register     | CTRM    |

|--------------------|-----------------------------------|---------|

|                    | CAN bus timing control register 1 | CBTCON1 |

|                    | CAN bus timing control register 2 | CBTCON2 |

|                    | CAN acceptance code register 0    | CACO    |

|                    | CAN acceptance code register 1    | CAC1    |

| 0035 <sub>16</sub> | CAN acceptance code register 2    | CAC2    |

| 0036 <sub>16</sub> | CAN acceptance code register 3    | CAC3    |

| 0037 <sub>16</sub> | CAN acceptance code register 4    | CAC4    |

| 0038 <sub>16</sub> | CAN acceptance mask register 0    | CAMO    |

| 0039 <sub>16</sub> | CAN acceptance mask register 1    | CAM1    |

| 003A <sub>16</sub> | CAN acceptance mask register 2    | CAM2    |

| 003B <sub>16</sub> | CAN acceptance mask register 3    | CAM3    |

| 003C <sub>16</sub> | CAN acceptance mask register 4    | CAM4    |

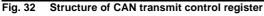

| 003D <sub>16</sub> | CAN receive control register      | CREC    |

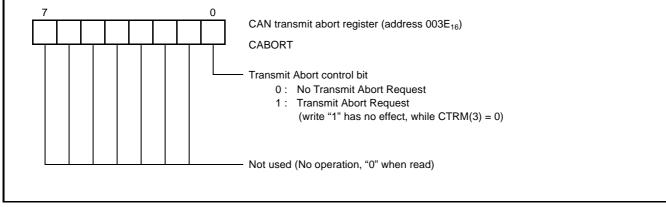

| 003E <sub>16</sub> | CAN transmit abort register       | CABORT  |

| 003F <sub>16</sub> | Reserved                          |         |

| 0040 <sub>16</sub> | CAN transmit buffer register 0    | CTBO    |

| 0041 <sub>16</sub> | CAN transmit buffer register 1    | CTB1    |

| 0042 <sub>16</sub> | CAN transmit buffer register 2    | CTB2    |

| 0043 <sub>16</sub> | CAN transmit buffer register 3    | CTB3    |

| 0044 <sub>16</sub> | CAN transmit buffer register 4    | CTB4    |

|                    | CAN transmit buffer register 5    | CTB5    |

| 0046 <sub>16</sub> | CAN transmit buffer register 6    | CTB6    |

|                    | CAN transmit buffer register 7    | CTB7    |

|                    | CAN transmit buffer register 8    | CTB8    |

|                    | CAN transmit buffer register 9    | CTB9    |

| 004A <sub>16</sub> | CAN transmit buffer register A    | СТВА    |

|                    | CAN transmit buffer register B    | СТВВ    |

|                    | CAN transmit buffer register C    | CTBC    |

|                    | CAN transmit buffer register D    | CTBD    |

|                    | Reserved                          |         |

|                    | Reserved                          |         |

|                    | CAN receive buffer register 0     | CRBC    |

|                    | CAN receive buffer register 1     | CRB1    |

|                    | CAN receive buffer register 2     | CRB2    |

|                    | CAN receive buffer register 3     | CRB3    |

|                    | CAN receive buffer register 4     | CRB4    |

|                    | CAN receive buffer register 5     | CRB5    |

|                    | CAN receive buffer register 6     | CRB6    |

|                    | CAN receive buffer register 7     | CRB7    |

|                    | CAN receive buffer register 8     | CRB8    |

|                    | CAN receive buffer register 9     | CRBS    |

|                    | CAN receive buffer register A     | CRBA    |

|                    | CAN receive buffer register B     | CRBB    |

|                    | CAN receive buffer register C     | CRBC    |

|                    | CAN receive buffer register D     | CRBD    |

|                    | Reserved                          | 000     |

|                    |                                   |         |

Fig. 7 Memory map of special register (SFR)

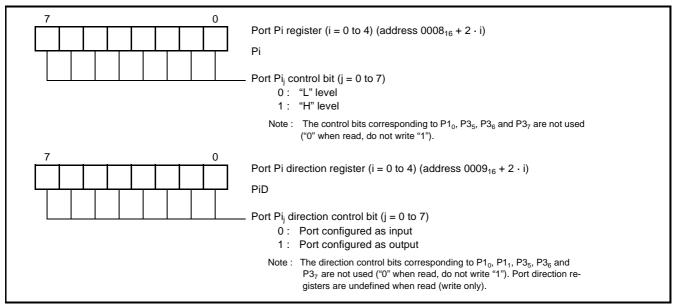

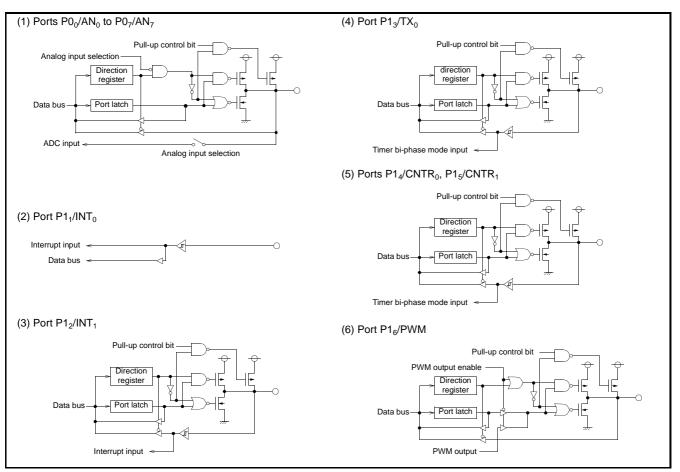

# I/O PORTS

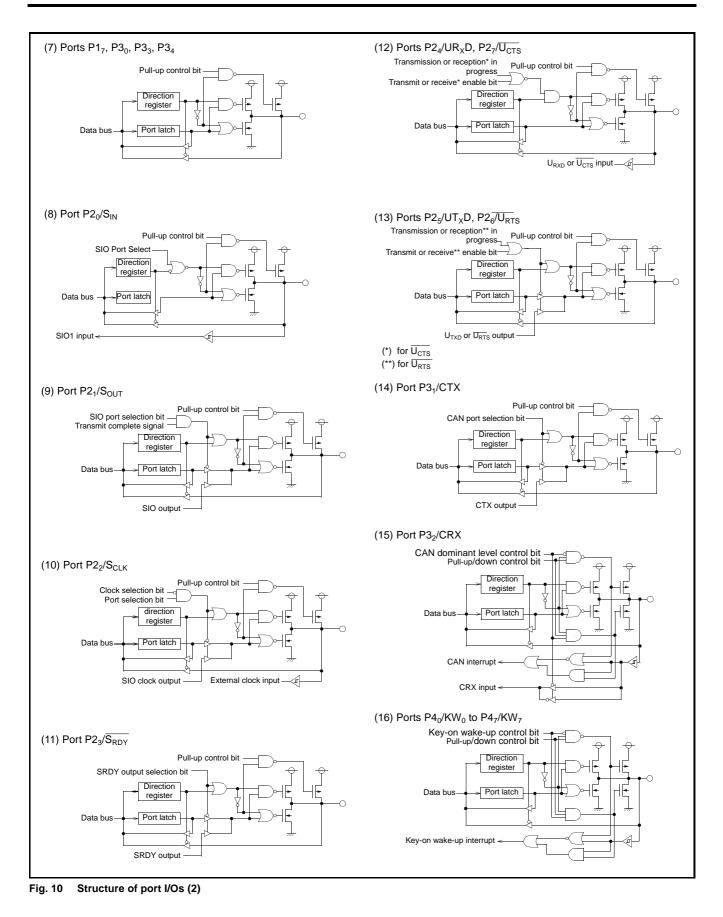

The 7630 group has 35 programmable I/O pins and one input pin arranged in five I/O ports (ports P0 to P4). The I/O ports are controlled by the corresponding port registers and port direction registers; each I/O pin can be controlled separately.

When data is read from a port configured as an output port, the port latch's contents are read instead of the port level. A port configured as an input port becomes floating and its level can be read. Data written to this port will affect the port latch only; the port remains floating.

Refer to Structure of port- and port direction registers, Structure of port I/Os (1) and Structure of port I/Os (2).

Fig. 8 Structure of port- and port direction registers

Fig. 9 Structure of port I/Os (1)

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

#### Port Pull-up/pull-down Function

Each pin of ports P0 to P4 except P1<sub>1</sub> is equipped with a programmable pull-up transistor. P3<sub>2</sub>/CRX and P4<sub>0</sub>/KW<sub>0</sub> to P4<sub>7</sub>/KW<sub>7</sub> are equipped with programmable pull-down transistors as well. The pull-up function of P0 to P3 can be controlled by the corresponding

port pull-up control registers (see Structure of port pull-up/down control registers). The pull-up/down function of ports  $P3_2$  and P4 can be controlled by the corresponding port pull-up/pull-down registers together with the polarity control register (see Structure of polarity control register).

Renesas Technology Corp.

#### **Port Overvoltage Application**

When configured as input ports, P1 to P4 may be subjected to overvoltage (V<sub>I</sub> > V<sub>CC</sub>) if the input current to the applicable port is limited to the specified values (see "Table 8:"). Use a serial resistor of appropriate size to limit the input current. To estimate the resistor value, assume the port voltage to be V<sub>CC</sub> at overvoltage condition. **Notes:**

- Subjecting ports to overvoltage may effect the supply voltage. Assure to keep  $V_{CC}$  and  $V_{SS}$  within the target limits.

- Avoid to subject ports to overvoltage causing  $V_{\text{CC}}$  to rise above 5.5 V.

- The overvoltage condition causing input current flowing through the internal port protection circuits has a negative effect on the ports noise immunity. Therefore, careful and intense testing of the target system's noise immunity is required. Refer to the "countermeasures against noise" of the corresponding users manual.

- Port P0 must not be subjected to overvoltage conditions.

## **INTERRUPTS**

There are 24 interrupts: 6 external, 17 internal, and 1 software.

#### Interrupt Control

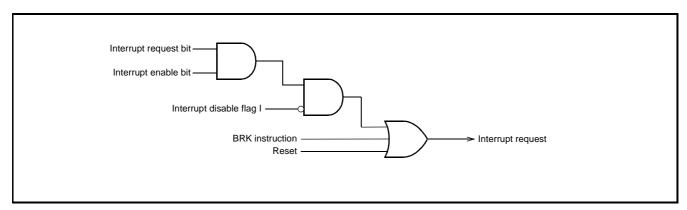

Each interrupt except the BRK instruction interrupt has both an interrupt request bit and an interrupt enable bit, and is controlled by the interrupt disable flag. An interrupt occurs when the corresponding interrupt request and enable bits are "1" and the interrupt disable flag is "0". Interrupt enable bits can be cleared or set by software. Interrupt request bits can be cleared by software but cannot be set by software. The BRK instruction interrupt and reset cannot be disabled with any flag or bit. The I flag disables all interrupt requests occur at the same time, the interrupt with the highest priority is accepted first.

#### **Interrupt Operation**

Upon acceptance of an interrupt, the following operations are automatically performed.

1. The processing being executed is stopped.

- 2. The contents of the program counter and processor status register are automatically pushed onto the stack.

- 3. Concurrently with the push operation, the interrupt jump destination address is read from the vector table into the program counter.

- 4. The interrupt disable flag is set and the corresponding interrupt request bit is cleared.

#### Notes on use

When the active edge of an external interrupt  $(INT_0, INT_1, CNTR_0, CNTR_1, CWKU or KOI)$  is changed, the corresponding interrupt request bit may also be set. Therefore, take the following sequence. (1) Disable the external interrupt which is selected.

- (2) Change the active edge in interrupt edge selection register. (in the case of CNTR<sub>0</sub>: Timer X mode register; in the case of

- CNTR<sub>1</sub>: Timer Y mode register) (3) Clear the interrupt request bit to "0".

- (4) Enable the external interrupt which is selected.

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

| Interrupt source              | Priority | Vector Address (Note 1) |                    | Interrupt Request Generating                                           | Demeric                                                 |  |  |

|-------------------------------|----------|-------------------------|--------------------|------------------------------------------------------------------------|---------------------------------------------------------|--|--|

| interrupt source              | FIIOIILy | High Low                |                    | Conditions                                                             | Remarks                                                 |  |  |

| Reset (Note 2)                | 1        | FFFB <sub>16</sub>      | FFFA <sub>16</sub> | At Reset                                                               | Non-maskable                                            |  |  |

| Watchdog timer                | 2        | FFF9 <sub>16</sub>      | FFF8 <sub>16</sub> | At Watchdog timer underflow                                            | Non-maskable                                            |  |  |

| ΙΝΤΟ                          | 3        | FFF7 <sub>16</sub>      | FFF6 <sub>16</sub> | At detection of either rising or falling edge of $INT_0$ interrupt     | External Interrupt<br>(active edge selectable)          |  |  |

| INT1                          | 4        | FFF5 <sub>16</sub>      | FFF4 <sub>16</sub> | At detection of either rising or falling edge of $INT_1$ interrupt     | External Interrupt<br>(active edge selectable)          |  |  |

| CAN successful transmit       | 5        | FFF3 <sub>16</sub>      | FFF2 <sub>16</sub> | At CAN module successful<br>transmission of message                    | Valid when CAN module is activated and request transmit |  |  |

| CAN successful receive        | 6        | FFF1 <sub>16</sub>      | FFF0 <sub>16</sub> | At CAN module successful reception of message                          | Valid when CAN module is activated                      |  |  |

| CAN overrun                   | 7        | FFEF <sub>16</sub>      | FFEE <sub>16</sub> | If CAN module receives message when receive buffers are full.          | Valid when CAN module is activated                      |  |  |

| CAN error passive             | 8        | FFED <sub>16</sub>      | FFEC <sub>16</sub> | When CAN module enters into error passive state                        | Valid when CAN module is active                         |  |  |

| CAN error bus off             | 9        | FFEB <sub>16</sub>      | FFEA <sub>16</sub> | When CAN module enters into bus off state                              | Valid when CAN module is active                         |  |  |

| CAN wake up                   | 10       | FFE9 <sub>16</sub>      | FFE8 <sub>16</sub> | When CAN module wakes up via CAN bus                                   |                                                         |  |  |

| Timer X                       | 11       | FFE7 <sub>16</sub>      | FFE6 <sub>16</sub> | At Timer X underflow or overflow                                       |                                                         |  |  |

| Timer Y                       | 12       | FFE5 <sub>16</sub>      | FFE4 <sub>16</sub> | At Timer Y underflow                                                   |                                                         |  |  |

| Timer 1                       | 13       | FFE3 <sub>16</sub>      | FFE2 <sub>16</sub> | At Timer 1 underflow                                                   |                                                         |  |  |

| Timer 2                       | 14       | FFE1 <sub>16</sub>      | FFE0 <sub>16</sub> | At Timer 2 underflow                                                   |                                                         |  |  |

| Timer 3                       | 15       | FFDF <sub>16</sub>      | FFDE <sub>16</sub> | At Timer 3 underflow                                                   |                                                         |  |  |

| CNTR0                         | 16       | FFDD <sub>16</sub>      | FFDC <sub>16</sub> | At detection of either rising or falling edge in $\text{CNTR}_0$ input | External Interrupt<br>(active edge selectable)          |  |  |

| CNTR1                         | 17       | FFDB <sub>16</sub>      | FFDA <sub>16</sub> | At detection of either rising or falling edge in $\text{CNTR}_1$ input | External Interrupt<br>(active edge selectable)          |  |  |

| UART receive                  | 18       | FFD9 <sub>16</sub>      | FFD8 <sub>16</sub> | At completion of UART receive                                          | Valid when UART is selected                             |  |  |

| UART transmit                 | 19       | FFD7 <sub>16</sub>      | FFD6 <sub>16</sub> | At completion of UART transmit                                         | Valid when UART is selected                             |  |  |

| UART transmit<br>buffer empty | 20       | FFD5 <sub>16</sub>      | FFD4 <sub>16</sub> | At UART transmit buffer empty                                          | Valid when UART is selected                             |  |  |

| UART receive<br>error         | 21       | FFD3 <sub>16</sub>      | FFD2 <sub>16</sub> | When UART reception error occurs.                                      | Valid when UART is selected                             |  |  |

| Serial I/O                    | 22       | FFD1 <sub>16</sub>      | FFD0 <sub>16</sub> | At completion of serial I/O data transmit and receive                  | Valid when serial I/O is selected                       |  |  |

| A-D conversion                | 23       | FFCF <sub>16</sub>      | FFCE <sub>16</sub> | At completion of A-D conversion                                        |                                                         |  |  |

| Key-on wake-up                | 24       | FFCD <sub>16</sub>      | FFCC <sub>16</sub> | At detection of either rising or falling edge of P4 input              | External Interrupt<br>(active edge selectable)          |  |  |

| BRK instruction               | 25       | FFCB <sub>16</sub>      | FFCA <sub>16</sub> | At BRK instruction execution                                           | Non-maskable                                            |  |  |

#### Table 3: Interrupt vector addresses and priority

Notes 1: Vector addresses contain interrupt jump destination address

2: Reset function in the same way as an interrupt with the highest priority

#### Fig. 13 Interrupt control

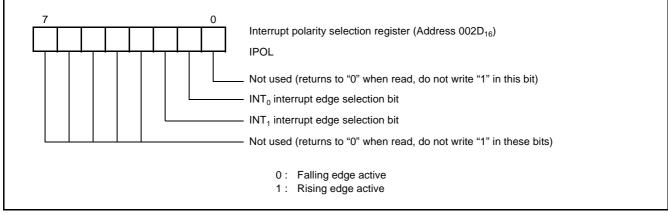

For the external interrupts INT0 and INT1, the active edge causing the interrupt request can be selected by the INT0 and INT1 interrupt edge selection bits of the interrupt polarity selection register (IPOL); please refer to Fig. 14 below.

Fig. 14 Structure of interrupt polarity selection register

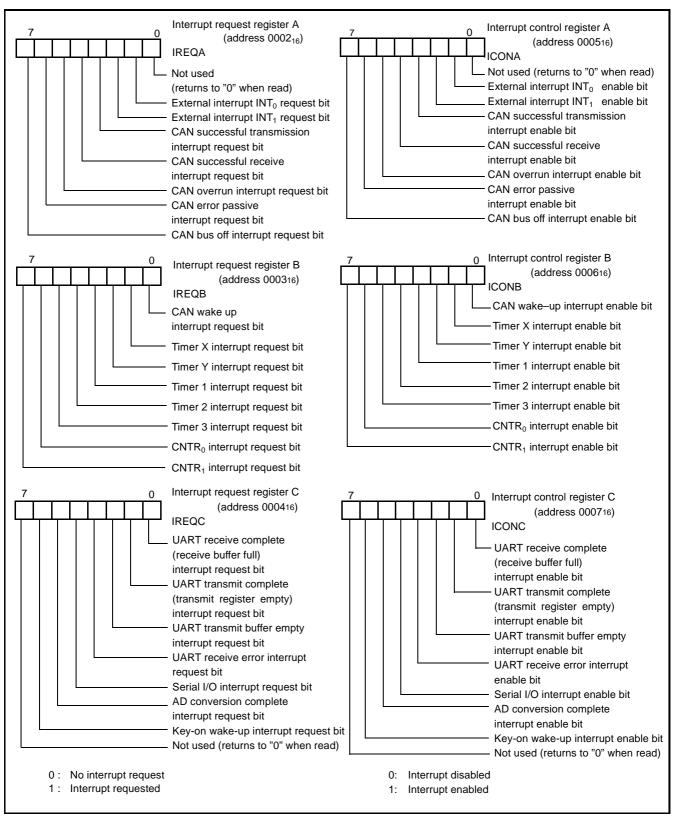

Fig. 15 Structure of interrupt request and control registers A, B and C

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

# **KEY-ON WAKE-UP**

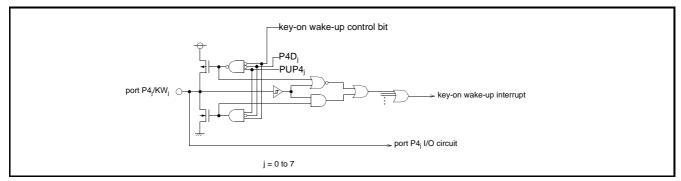

"Key-on wake-up" is one way of returning from a power-down state caused by the STP or WIT instruction. Any terminal of port P4 can be used to generate the key-on wake-up interrupt request. The active polarity can be selected by the key-on wake-up polarity control bit of PCON (see Fig. 12). If any pin of port P4 has the selected active level applied, the key-on wake-up interrupt request will be set to "1". Please refer to Fig. 16.

Fig. 16 Block diagram of key-on wake-up circuit

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

#### TIMERS

The 7630 group has five timers: two 16-bit timers and three 8-bit timers . All these timers will be described in detail below.

#### **16-bit Timers**

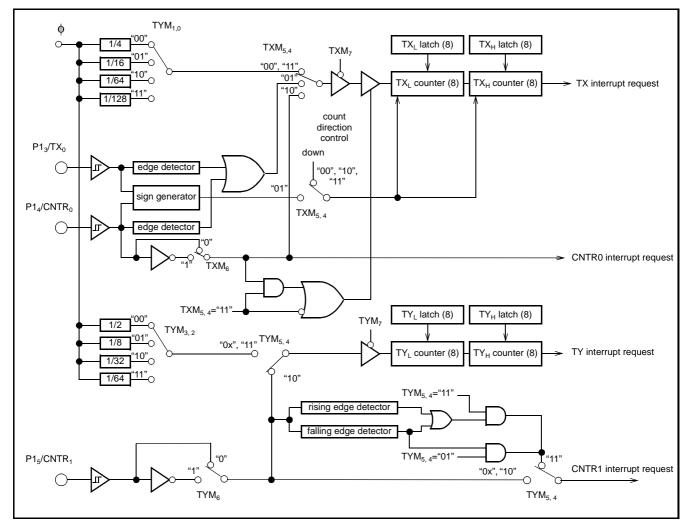

Timers X and Y are 16-bit timers with multiple operating modes. Please refer to Fig. 17.

Fig. 17 Block diagram of timers X and Y ( $\phi$  is internal system clock)

#### **Timer X**

Timer X is a 16-bit timer with a 16-bit reload latch supporting the following operating modes:

- (1) Timer mode

- (2) Bi-phase counter mode

- (3) Event counter mode

- (4) Pulse width measurement mode

These modes can be selected by the timer X mode register (TXM). In the timer- and pulse width measurement mode, the timer's count source can be selected by the timer X count source selection bits of the timer Y mode register (TYM). Please refer to the Figures below for the TXM and TYM bit assignment.

On read or write access to timer X, note that the high-order and loworder bytes must be accessed in the specific order.

#### Write method

When writing to the timer X, write the low-order byte first. The data written is stored in a temporary register which is assigned to the

same address as  $TX_L$ . Next, write the high-order byte. When this is finished, the data is placed in the timer X high-order reload latch and the low-order byte is transferred from its temporary register to the timer X low-order reload latch. Depending on the timer X write control bit, the latch contents are reloaded to the timer immediately (write control bit = "0") or on the next timer underflow (write control bit = "1").

#### Read method

When reading the timer X, read the high-order byte first. This causes the timer X high- and low-order bytes to be transferred to temporary registers being assigned to the same addresses as  $TX_H$  and  $TX_L$ . Next, read the low-order byte which is read from the temporary register. This method assures the correct timer value can be read during the timer count operation.

#### Timer X count stop control

Regardless of the actual operating mode, timer X can be stopped by setting the timer X count stop bit (bit 7 of the timer X mode register) to "1".

Fig. 18 Structure of Timer X mode register

#### **Timer Y**

Timer Y is a 16 bit timer with a 16-bit reload latch supporting the following operating modes:

- (1) Timer mode

- (3) Event counter mode

- (5) Pulse period measurement mode

- (6) H/L pulse width measurement mode

These modes can be selected by the timer Y mode register (TYM). In the timer, pulse period- and pulse width measurement modes' the timer's count source can be selected by the timer Y count source selection bits. Please refer to Fig. 19.

On read or write access to timer Y, note that the high-order and loworder bytes must be accessed in a specific order.

#### Write method

When writing to timer Y, write the low-order byte first. The data written is stored in a temporary register which is assigned to the same address as  $TY_L$ . Next, write the high-order byte. When this is finished, the data is placed in the timer Y high-order reload latch and the low-order byte is transferred from its temporary register to the timer Y low-order reload latch.

#### Read method

When reading the timer Y, read the high-order byte first. This causes the timer Y high- and low-order bytes to be transferred to temporary registers being assigned to the same addresses as  $TY_H$  and  $TY_L$ . Next, read the low-order byte which is read from the temporary register. This method assures the correct timer value can be read during timer count operation.

#### Timer Y count stop control

Regardless of the actual operating mode, timer Y can be stopped by setting the timer Y count stop bit (bit 7 of the timer Y mode register) to "1".

Fig. 19 Structure of timer Y mode register ( $\phi$  is internal system clock)

#### **Operating Modes**

#### (1) Timer mode

This mode is available with timer X and timer Y.

Count source

The count source for timer X and Y is the output of the corresponding clock divider. The division ratio can be selected by the timer Y mode register.

Operation

Both timers X and Y are down counters. On a timer underflow, the corresponding timer interrupt request bit will be set to "1", the contents of the corresponding timer latches will be reloaded to the counters and counting continues.

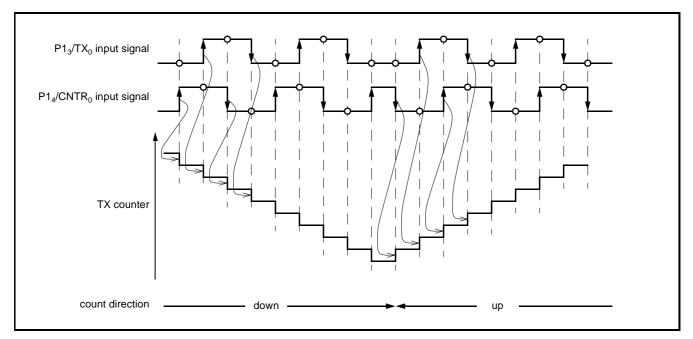

#### (2) Bi-phase counter mode (quadruplicate)

- This mode is available with timer X only.

- Count source

- The count sources are  $P1_4/CNTR_0$  and the  $P1_3/TX_0$  pins. • Operation

- Timer X will count both rising and falling edges on both input pins (see above). Refer to Timer X bi-phase counter mode operation for the timing chart of the bi-phase counter mode.

The count direction is determined by the edge polarity and level of count source inputs and may change during the count operation. Refer to the table below.

#### Table 4: Timer X count direction in Bi-phase counter mode

| P1 <sub>3</sub> /TX <sub>0</sub> | P1 <sub>4</sub> /CNTR <sub>0</sub> | Count direction |  |  |  |

|----------------------------------|------------------------------------|-----------------|--|--|--|

| ↑ Edge                           | L                                  | Up              |  |  |  |

| 1 Luge                           | Н                                  | Down            |  |  |  |

| ↓ Edge                           | L                                  | Down            |  |  |  |

| ↓ Edge                           | Н                                  | Up              |  |  |  |

| L                                | ↑ Edge                             | Down            |  |  |  |

| Н                                | 1 Euge                             | Up              |  |  |  |

| L                                | Edgo                               | Up              |  |  |  |

| Н                                | $\downarrow$ Edge                  | Down            |  |  |  |

On a timer over- or underflow, the corresponding interrupt request bit will be set to "1" and counting continues.

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Fig. 20 Timer X bi-phase counter mode operation

#### (3) Event counter mode

This mode is available with timer X and timer Y.

- Count source

- The count source for timer X is the input signal to the  $P1_4/CNTR_0$  pin and for timer Y the input signal to  $P1_5/CNTR_1$  pin.

- Operation

The timer counts down. On a timer underflow, the corresponding timer interrupt request bit will be set to "1", the contents of the corresponding timer latches will be reloaded to the counters and counting continues. The active edge used for counting can be selected by the polarity selection bit of the corresponding pin  $P1_4/CNTR_0$  or  $P1_5/CNTR_1$ . These bits are part of TXM (Structure of Timer X mode register) and TYM (Structure of timer Y mode register (f is internal system clock)) registers.

#### (4) Pulse width measurement mode

This mode is available with timer X only.

- Count source

- The count source is the output of timer X clock divider. The division ratio can be selected by the timer Y mode register.

- Operation

The timer counts down while the input signal level on  $P1_4/CNTR_0$  matches the active polarity selected by the  $CNTR_0$  polarity selection bit of TXM (Structure of Timer X mode register). On a timer underflow, the timer X interrupt request bit will be set to "1", the contents of the timer latches are reloaded to the counters and counting continues. When the input level changes from active polarity (as selected), the  $CNTR_0$  interrupt request bit will be set to "1." The measurement result may be obtained by reading timer X during interrupt service.

#### (5) Pulse period measurement mode

- This mode is available with timer Y only.

- Count source

The count source is the output of timer Y clock divider.

Operation

The active edge of input signal to be measured can be selected by  $CNTR_1$  polarity selection bit (Fig. 18). When this bit is set to "0", the time between two consecutive falling edges of the signal input to  $P1_5/CNTR_1$  pin will be measured, when the polarity bit is set to "1", the time between two consecutive rising edges will be measured.

The timer counts down. On detection of an active edge of input signal, the contents of the TY counters will be transferred to temporary registers assigned to the same addresses as TY. At the same time, the contents of TY latches will be reloaded to the counters and counting continues. The active edge of input signal also causes the  $CNTR_1$  interrupt request bit to be set to "1". The measurement result may be obtained by reading timer Y during interrupt service.

#### (6) H/L pulse width measurement mode

This mode is available with timer Y only.

- Count source The count source is the output of the timer Y's clock divider.

- Operation

This mode measures both the "H" and "L" periods of a signal input to  $P1_5/CNTR_1$  pin continuously. On detection of any edge (rising or falling) of input signal to  $P1_5/CNTR_1$  pin, the contents of timer Y counters are stored to temporary registers which are assigned to the same addresses as timer Y. At the same time, the contents of timer Y latches are reloaded to the counters and counting continues. The detection of an edge causes the CNTR1 interrupt request bit to be set to "1" as well. The result of measurement may be obtained by reading timer Y during interrupt service. This read access will address the temporary registers. On a timer underflow, the timer Y latches will be transferred to the counters and counting continues.

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

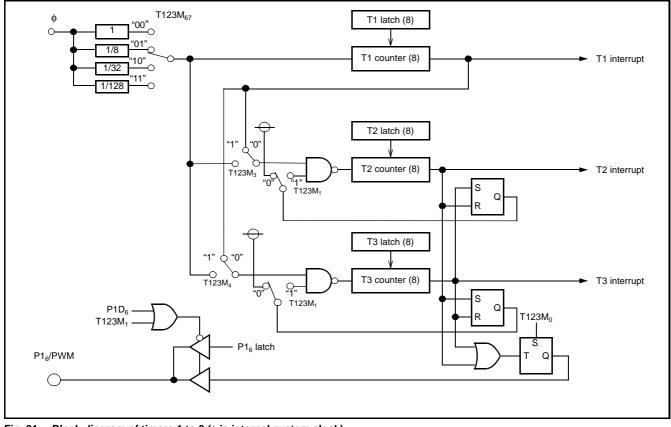

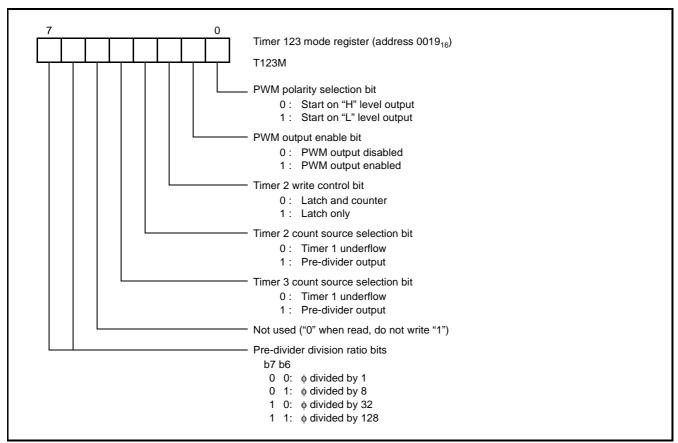

#### TIMER 1, TIMER 2, TIMER 3

Timers 1 to 3 are 8-bit timers with 8-bit reload latches and one common pre-divider. Timer 1 can operate in the timer mode only,

whereas timers 2 and 3 can be used to generate a PWM output signal timing as well. Timers 1 to 3 are down count timers. See Fig. 21.

Fig. 21 Block diagram of timers 1 to 3 ( $\phi$  is internal system clock)

#### Timer 1

The count source of timer 1 is the output of timer 123 pre-divider. The division ratio of the pre-divider can be selected by the predivider division ratio bits of timer 123 mode register (T123M). Refer to Timer 123 mode register configuration (f is internal system clock). On a timer 1 underflow, the timer 1 interrupt request bit will be set to "1".

Writing to timer 1 initializes the latch and counter.

#### Timers 2 and 3

The count source of timers 2 and 3 can be either the output of the timer 123 pre-divider or the timer 1 underflow. The count source can

be selected by the timer count source selection bits of timer 123 mode register (T123M).

Writing to timer 2 register affects the reload latch only or both of the reload latch and counter depending on the timer 2 write control bit of T123M. When the timer write control bit is set to "0", both latch and counter will be initialized simultaneously; when set to "1" only the reload latch will be initialized, on an underflow, the counter will be set to the modified reload value. Writing to timer 3 initializes latch and counter both.

Timer 2 or 3 underflow causes the timer 2 or 3 interrupt request bit to be set to "1".

Fig. 22 Timer 123 mode register configuration ( $\phi$  is internal system clock)

#### **Operating Modes**

#### (1) Timer Mode

This mode is available with timers 1 to 3.

Count source

For timer 1, the count source is the output of the corresponding pre-divider. For timers 2 and 3, the count source can be separately selected to be either the pre-divider output or timer 1 underflow.

Operation

The timer counts down. On a timer underflow, the corresponding timer interrupt request bit will be set to "1", the contents of the corresponding timer latch will be reloaded to the counter and counting continues.

#### (2) PWM Mode

This mode is available with timer 2 and 3.

Count source

The count source can be separately selected to be either the pre-divider output or timer 1 underflow.

Operation

When the PWM-mode is enabled, timer 2 starts counting. As soon as timer 2 underflows, timer 2 stops and timer 3 starts counting. If bit 0 is set, timer 2 determines the low duration and the initial output level is low. Timer 3 determines the high duration. If bit 0 is zero timer 2 determines the high duration and the initial output level is high. In this case timer 3 determines the low duration.

Note: Be sure to configure the  $P1_6/PWM$  pin as an output port before using PWM mode.

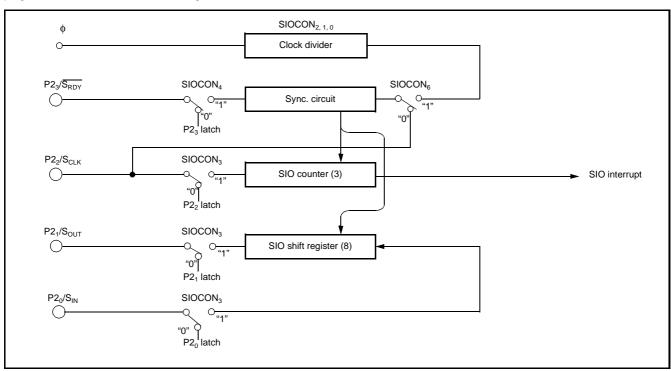

#### SERIAL I/Os

The serial I/O section of 7630 group consists of one clock synchronous and one asynchronous (UART) interface.

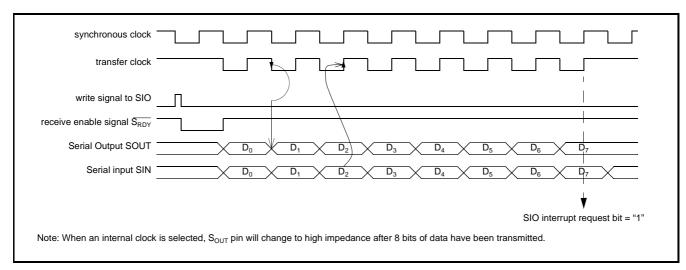

#### Clock Synchronous Serial I/O (SI/O)

The clock synchronous interface allows full duplex communication based on 8 bit word length. The transfer clock can be selected from an internal or external clock. When an internal clock is selected, a programmable clock divider allows eight different transmission speeds. Refer to Block diagram of clock synchronous I/O (f is internal system clock). The operation of the clock synchronous serial I/O can be configured by the serial I/O control register SIOCON; refer to Fig. 25.

Fig. 23 Block diagram of clock synchronous I/O ( $\phi$  is internal system clock)

#### (1) Clock synchronous serial I/O operation

Either an internal or external transfer clock can be selected by bit 6 of SIOCON. The internal clock divider can be programmed by bits 0 to 2 of SIOCON. Bit 3 of SIOCON determines whether the double function pins P2<sub>0</sub> to P2<sub>2</sub> will act as I/O ports or serve as SIO pins. Bit 4 of SIOCON allows the same selection for pin P2<sub>3</sub>.

When an internal transfer clock is selected, transmission can be triggered by writing data to the SI/O shift register (SIO, address

$0012_{\rm 16}).$  After an 8–bit transmission has been completed, the  $S_{\rm OUT}$  pin will change to high impedance and the SIO interrupt request bit will be set to "1".

When an external transfer clock is selected, the SIO interrupt request bit will be set to "1" after 8 cycles but the contents of the SI/O shift register continue to be shifted while the transfer clock is being input. Therefore, the clock needs to be controlled externally; the S<sub>OUT</sub> pin will not change to high impedance automatically.

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Fig. 24 Timing of clock synchronous SI/O function (LSB first selected)

#### **Clock Asynchronous Serial I/O (UART)**

The UART is a full duplex asynchronous transmit/receive unit. The built-in clock divider and baud rate generator enable a broad range of transmission speeds. Please refer to Block diagram of UART.

#### (1) Description

The transmit and receive shift registers have a buffer (consisting of high and low order byte) each. Since the shift registers cannot be

written to or read from directly, transmit data is written to the transmit buffer and receive data is read from the receive buffer. A transmit or receive operation will be triggered by the transmit enable bit and receive enable bit of the UART control register UCON (see Structure of UART control register). The double function terminals  $P2_5/UT_XD$ ,  $P2_6/URTS$  and  $P2_4/UR_XD$ ,  $P2_7/UCTS$  will be switched to serve as UART pins automatically.

#### (2) Baud rate selection

The baud rate of transmission and reception is determined by the setting of the prescaler and the contents of the UART baud rate generator register. It is calculated by: where p is the division ratio of

$$b = \frac{\phi}{16 \cdot p \cdot (n+1)}$$

the prescaler and n is the content of UART baud rate generator register. The prescalers division ration can be selected by the UART mode register (see below).

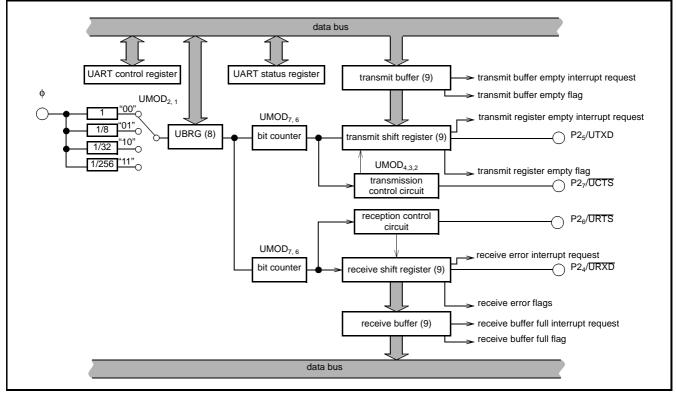

# UART mode register (UMOD, Structure of UART mode register)

The UART mode register allows to select the transmission and reception format with the following options:

- word length: 7, 8 or 9 bits

- parity: none, odd or even

- stop bits: 1 or 2

It allows to select the prescalers division ratio as well.

#### UART baud rate generator (UBRG)

This 8 bit register allows to select the baud rate of the UART (see above). Set this register to the desired value before enabling reception or transmission.

# UART control register (UCON, Structure of UART control register)

The UART control register consists of four control bits (bit 0 to bit 3) which allow to control reception and transmission.

# UART status register (USTS, Structure of UART status register)

The read-only UART status register consists of 7 bits (bit 0 to bit 6) which indicate the operating status of the UART function and various errors.

#### (3) Handshaking signals

When used as transmitter the UART will recognize the clear-tosend signal via P2<sub>7</sub>/UCTS terminal for handshaking. When used as receiver it will issue a request-to-send signal through P2<sub>6</sub>/URTS pin.

#### **Clear-to-send input**

When used as a transmitter (transmit enable bit set to "1"), the UART starts transmission after recognizing "L" level on  $P2_7/UCTS$ . After started the UART will continue to transmit regardless of the actual level of  $P2_7/UCTS$  or status of the transmit enable bit.

#### Request-to-send output

The UART controls the  $\text{P2}_{\text{6}}/\text{URTS}$  output according to the following conditions.

#### Table 5: Output control conditions

| Condition                                                      | P2 <sub>6</sub> /URTS |

|----------------------------------------------------------------|-----------------------|

| Receive enable bit is set to "1"                               |                       |

| Reception completed during receive enable<br>bit set to "1"    | "L"                   |

| Start bit (falling edge) detected                              |                       |

| Receive enable bit is set to "0" before recep-<br>tion started | "H"                   |

| Hardware reset                                                 |                       |

| Receive initialization bit is set to "1"                       |                       |

Fig. 26 Block diagram of UART

Fig. 27 Structure of UART mode register

Fig. 29 Structure of UART status register

# **CAN MODULE**

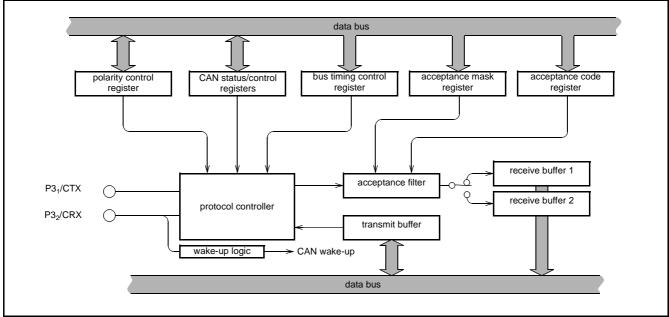

The CAN (Controller Area Network) interface of the 7630 group complies with the 2.0B specification, enabling reception and transmission of frames with either 11- or 29- bit identifier length. Refer to Fig. 31 for a block diagram of the CAN interface.

The programmer's interface to the CAN module is formed by three status/control registers (Fig. 32, Fig. 33, Fig. 34), two bus timing control registers (Fig. 35 Fig. 36), several registers for acceptance filtering (Fig. 37), the transmit and receive buffer registers (Fig. 38) and one dominant level control bit (Fig. 22).

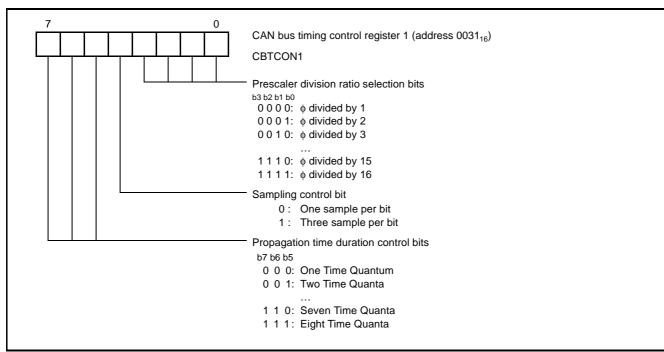

#### **Baud Rate Selection**

A programmable clock prescaler is used to derive the CAN module's basic clock from the internal system clock frequency ( $\phi$ ). Bit 0 to bit 3 of the CAN bus timing control register represent the prescaler allowing a division ratio from 1 to 1/16 to be selected. So the CAN module basic clock frequency f<sub>CANB</sub> can be calculated as follows:

$$f_{CANB} = \frac{\phi}{p+1}$$

where p is the value of the prescaler (selectable from 1 to 15). The effective baud rate of the CAN bus communication depends on the CAN bus timing control parameters and will be explained below.

#### **CAN Bus Timing Control**

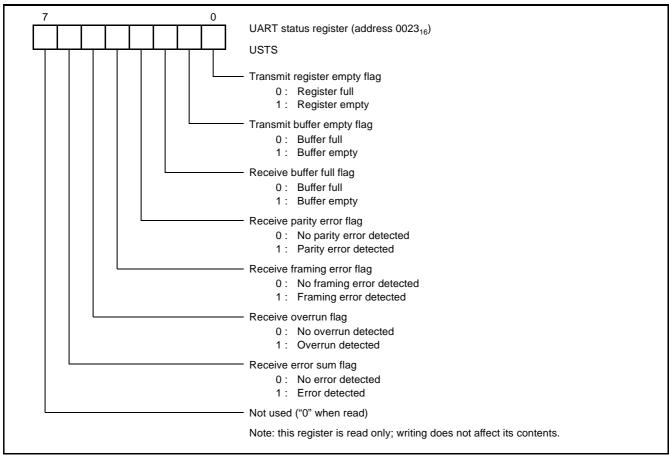

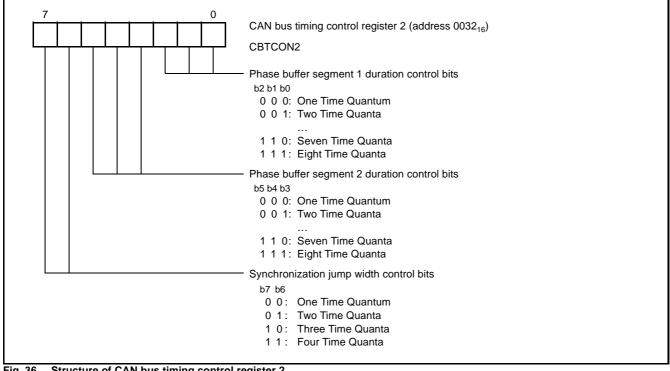

Each bit-time consists of four different segments (see Fig. 30):

- Synchronization segment (SS),

- Propagation time segment (PTS),

- Phase buffer segment 1 (PBS1) and

- Phase buffer segment 2 (PBS2).

#### Fig. 30 Bit time of CAN module

The first of these segments is of fixed length (one Time Quantum) and the latter three can be programmed to be 1 to 8 Time Quanta by the CAN bus timing control register 1 and 2 (see Fig. 35 and Fig. 36). The whole bit-time has to consist of minimum 8 and maximum 25 Time Quanta. The duration of one Time Quantum is the cycle time of  $f_{CANB}$ . For example, assuming  $\phi = 5$  MHz, p = 0, one Time Quantum will be 200 ns long. This allows the maximum transmission rate of 625 kb/s to be reached (assuming 8 Time Quanta per bit-time).

Fig. 31 Block diagram of CAN module

Fig. 35 Structure of CAN bus timing control register 1

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

| Acceptance code<br>registers: | name<br>CAC0<br>CAC1 | CSID <sub>5</sub>                                           | CSID <sub>4</sub>                       | Not used<br>CSID <sub>3</sub>                       | CSID <sub>2</sub>                                   | CSID <sub>9</sub><br>CSID <sub>1</sub>                       | CSID <sub>8</sub><br>CSID <sub>0</sub>                       | -                                                   | 0<br>CSID <sub>6</sub><br>Not used      | address<br>0033 <sub>16</sub><br>0034 <sub>16</sub>            |

|-------------------------------|----------------------|-------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------|----------------------------------------------------------------|

|                               | CAC2<br>CAC3<br>CAC4 | Not used<br>CEID <sub>13</sub><br>CEID <sub>5</sub>         | Not used<br>CEID <sub>12</sub><br>CEID₄ | Not used<br>CEID <sub>11</sub><br>CEID <sub>3</sub> | Not used<br>CEID <sub>10</sub><br>CEID <sub>2</sub> | CEID <sub>17</sub><br>CEID <sub>9</sub><br>CEID <sub>1</sub> | CEID <sub>16</sub><br>CEID <sub>8</sub><br>CEID <sub>0</sub> | CEID <sub>15</sub><br>CEID <sub>7</sub><br>Not used | CEID <sub>14</sub><br>CEID <sub>6</sub> | 0035 <sub>16</sub><br>0036 <sub>16</sub><br>0037 <sub>16</sub> |

|                               |                      | Select the                                                  |                                         | Ű                                                   | 2                                                   |                                                              | 0                                                            | otance filte                                        | ring.                                   | 0007 <sub>16</sub>                                             |

| Acceptance mask<br>registers: | CAM0<br>CAM1         | 7<br>Not used<br>MSID <sub>5</sub>                          | Not used<br>MSID <sub>4</sub>           | Not used<br>MSID <sub>3</sub>                       | MSID <sub>10</sub><br>MSID <sub>2</sub>             | MSID <sub>9</sub><br>MSID <sub>1</sub>                       | MSID <sub>8</sub><br>MSID <sub>0</sub>                       | MSID <sub>7</sub><br>Not used                       | 0<br>MSID <sub>6</sub><br>Not used      | 0038 <sub>16</sub><br>0039 <sub>16</sub>                       |

|                               | CAM2<br>CAM3         | Not used<br>MEID <sub>13</sub>                              | Not used<br>MEID <sub>12</sub>          | Not used<br>MEID <sub>11</sub>                      | Not used<br>MEID <sub>10</sub>                      | MEID <sub>17</sub><br>MEID <sub>9</sub>                      | MEID <sub>16</sub><br>MEID <sub>8</sub>                      | MEID <sub>15</sub><br>MEID <sub>7</sub>             | MEID <sub>14</sub><br>MEID <sub>6</sub> | 003A <sub>16</sub><br>003B <sub>16</sub>                       |

|                               |                      | MEID <sub>5</sub><br>0 : Mask id<br>1 : Compa<br>(Not used: | re identifie                            | er bit with a                                       | ,                                                   | MEID <sub>1</sub><br>e code reg                              | MEID <sub>0</sub>                                            | Not used                                            | Not used                                | 003C <sub>16</sub>                                             |

Fig. 37 Structure of CAN mask and code registers

| name       | 7                 |                                                                                                                                |                   |                   |                   |                   |                   | 0                 | offset             |

|------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|

| CTB0, CRB0 | Not used          | Not used                                                                                                                       | Not used          | SID <sub>10</sub> | SID <sub>9</sub>  | SID <sub>8</sub>  | SID <sub>7</sub>  | SID <sub>6</sub>  | 0000 <sub>16</sub> |

| CTB1, CRB1 | SID <sub>5</sub>  | $SID_4$                                                                                                                        | SID <sub>3</sub>  | SID <sub>2</sub>  | $SID_1$           | SID <sub>0</sub>  | RTR/SRR           | IDE               | 0001 <sub>16</sub> |

| CTB2, CRB2 | Not used          | Not used                                                                                                                       | Not used          | Not used          | EID <sub>17</sub> | EID <sub>16</sub> | EID <sub>15</sub> | EID <sub>14</sub> | 0002 <sub>16</sub> |

| CTB3, CRB3 | EID <sub>13</sub> | EID <sub>12</sub>                                                                                                              | EID <sub>11</sub> | EID <sub>10</sub> | EID <sub>9</sub>  | EID <sub>8</sub>  | EID <sub>7</sub>  | $EID_6$           | 0003 <sub>16</sub> |

| CTB4, CRB4 | EID <sub>5</sub>  | $EID_4$                                                                                                                        | EID <sub>3</sub>  | EID <sub>2</sub>  | EID <sub>1</sub>  | EID <sub>0</sub>  | RTR               | r1                | 0004 <sub>16</sub> |

| CTB5, CRB5 | Not used          | Not used                                                                                                                       | Not used          | r <sub>o</sub>    | DLC <sub>3</sub>  | DLC <sub>2</sub>  | DLC <sub>1</sub>  | DLC <sub>0</sub>  | 0005 <sub>16</sub> |

| CTB6, CRB6 |                   |                                                                                                                                |                   | data b            | oyte 0            |                   |                   |                   | 0006 <sub>16</sub> |

| CTB7, CRB7 |                   |                                                                                                                                |                   | data b            | oyte 1            |                   |                   |                   | 0007 <sub>16</sub> |

| CTB8, CRB8 |                   |                                                                                                                                |                   | data b            | oyte 2            |                   |                   |                   | 0008 <sub>16</sub> |

| CTB9, CRB9 |                   | data byte 3                                                                                                                    |                   |                   |                   |                   |                   |                   | 0009 <sub>16</sub> |

| CTBA, CRBA |                   |                                                                                                                                |                   | data b            | oyte 4            |                   |                   |                   | 000A <sub>16</sub> |

| CTBB, CRBB |                   |                                                                                                                                |                   | data b            | oyte 5            |                   |                   |                   | 000B <sub>16</sub> |

| CTBC, CRBC |                   | data byte 6                                                                                                                    |                   |                   |                   |                   |                   |                   | 000C <sub>16</sub> |

| CTBD, CRBD |                   | data byte 7                                                                                                                    |                   |                   |                   |                   |                   |                   | 000D <sub>16</sub> |

|            | Calculate         | Calculate the actual address as follows:                                                                                       |                   |                   |                   |                   |                   |                   |                    |

|            | RxD buffe         | TxD buffer address = 0040 <sub>16</sub> + offset<br>RxD buffer address = 0050 <sub>16</sub> +offset<br>Not used: write to "0") |                   |                   |                   |                   |                   |                   |                    |

Fig. 38 Structure of CAN transmission and reception buffer registers

Note 1: All CAN related SFRs must not be written in "CAN sleep" mode.

# **A-D CONVERTER**

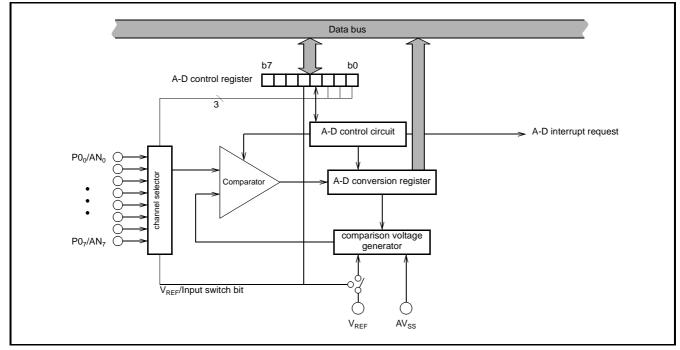

The A-D converter uses the successive approximation method with 8 bit resolution. The functional blocks of the A-D converter are described below. Refer to Block diagram of A-D converter.

#### **Comparison Voltage Generator**

The comparison voltage generator divides the voltage between AV\_{SS} and V\_{REF} by 256, and outputs the divided voltage.

#### **Channel Selector**

The channel selector selects one of ports  $\text{P0}_0/\text{AN}_0$  to  $\text{P0}_7/\text{AN}_7,$  and inputs its voltage to the comparator.

#### A-D conversion register AD

The A-D conversion register is a read-only register that stores the result of an A-D conversion. This register must not be read during an A-D conversion.

Fig. 39 Block diagram of A-D converter

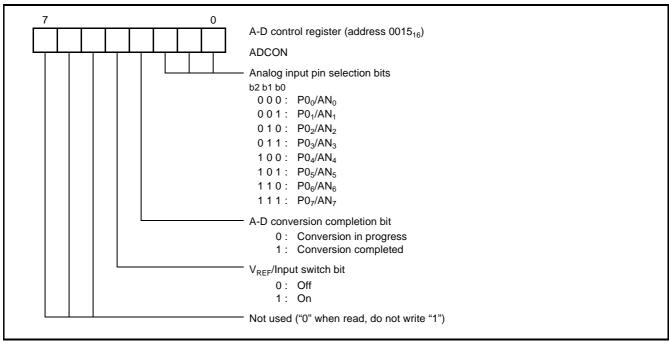

#### A-D control register (Structure of A-D control register)

The A-D control register controls the A-D conversion process. Bits 0 to 2 select a specific analog input pin. Bit 3 signals the completion of an A-D conversion. The value of this bit remains "0" during an A-

D conversion, and changes to "1" when an A-D conversion ends. Writing "0" to this bit starts the A-D conversion. Bit 4 is the  $V_{\text{REF}}/$  Input switch bit.

### **A-D Converter Operation**

The comparator and control circuit reference an analog input voltage with the reference voltage, then stores the result in the A-D conversion register. When an A-D conversion is complete, the control circuit sets the A-D conversion completion bit and the A-D interrupt request bit to "1". The result of A-D conversion can be obtained from the A-D conversion register, AD (address  $0014_{16}$ ). Note that the comparator is linked to a capacitor, so set  $f(X_{IN})$  to 500 kHz or higher during A-D conversion.

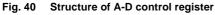

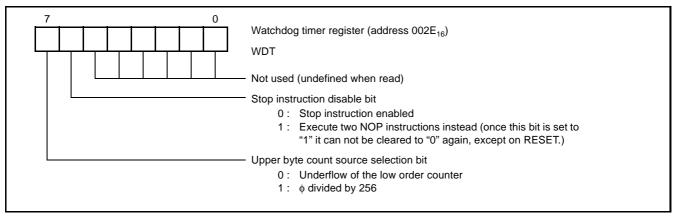

## WATCHDOG TIMER

The watchdog timer consists of two separate counters: one 7-bit counter (WD<sub>H</sub>) and one 4-bit counter (WD<sub>L</sub>). Cascading both counters or using the high-order counter allows only to select the time-out from either 524288 or 32768 cycles of the internal clock  $\phi$ . Refer to Fig. 41 and Fig. 42. Both counters are addressed by the same watchdog timer register (WDT). When writing to this register, both counters will be set to the following default values:

- the high-order counter will be set to address 7F<sub>16</sub>

- the low-order counter will be set to address  $\mathsf{F}_{16}$

regardless of the data written to the WDT register. Reading the watchdog timer register will return the corresponding control bit status, not the counter contents.

Once the WDT register is written to, the watchdog timer starts counting down and the watchdog timer interrupt is enabled. Once it is running, the watchdog timer cannot be disabled or stopped except by reset. On a watchdog timer underflow, a non-maskable watchdog timer interrupt will be requested.

To prevent the system being stopped by STP instruction, this instruction can be disabled by the STP instruction disable bit of WDT register. Once the STP instruction is disabled, it cannot be enabled again except by RESET.

Fig. 41 Block diagram of watchdog timer

Fig. 42 Structure of watchdog timer register ( $\phi$  is internal clock system)

### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

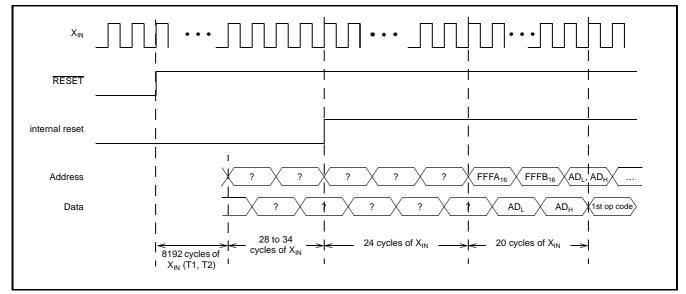

### **RESET CIRCUIT**

The 7630 group is reset according to the sequence shown in Fig. 44. It starts program execution from the address formed by the contents of the addresses FFFB<sub>16</sub> and FFFA<sub>16</sub>, when the RESET pin is held at "L" level for more than 2  $\mu$ s while the power supply voltage is

Fig. 43 Example of reset circuit

Fig. 44 Reset sequence

in the recommended operating condition and then returned to "H" level.

Refer to Fig. 43 for an example of the reset circuit.

### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

| Register                 | Address            | Register contents | Register                          | Address            | Register contents  |

|--------------------------|--------------------|-------------------|-----------------------------------|--------------------|--------------------|

| CPU mode reg.            | 0000 <sub>16</sub> | 48 <sub>16</sub>  | Timer XH                          | 001B <sub>16</sub> | FF <sub>16</sub>   |

| Interrupt request reg. A | 0002 <sub>16</sub> | 00 <sub>16</sub>  | Timer YL                          | 001C <sub>16</sub> | FF <sub>16</sub>   |

| Interrupt request reg. B | 0003 <sub>16</sub> | 00 <sub>16</sub>  | Timer YH                          | 001D <sub>16</sub> | FF <sub>16</sub>   |

| Interrupt request reg. C | 0004 <sub>16</sub> | 00 <sub>16</sub>  | Timer X mode reg.                 | 001E <sub>16</sub> | 00 <sub>16</sub>   |

| Interrupt control reg. A | 0005 <sub>16</sub> | 00 <sub>16</sub>  | Timer Y mode reg.                 | 001F <sub>16</sub> | 00 <sub>16</sub>   |

| Interrupt control reg. B | 0006 <sub>16</sub> | 00 <sub>16</sub>  | UART mode reg.                    | 0020 <sub>16</sub> | 0010               |

| Interrupt control reg. C | 0007 <sub>16</sub> | 00 <sub>16</sub>  | UART control reg.                 | 0022 <sub>16</sub> | 00 <sub>16</sub>   |

| Port P0 reg.             | 0008 <sub>16</sub> | 00 <sub>16</sub>  | UART status reg.                  | 0023 <sub>16</sub> | 07 <sub>10</sub>   |

| Port P0 direction reg.   | 0009 <sub>16</sub> | 00 <sub>16</sub>  | Port P0 pull-up control reg.      | 0028 <sub>16</sub> | 00 <sub>16</sub>   |

| Port P1 reg.             | 000A <sub>16</sub> | 00 <sub>16</sub>  | Port P1 pull-up control reg.      | 0029 <sub>16</sub> | 00 <sub>16</sub>   |

| Port P1 direction reg.   | 000B <sub>16</sub> | 00 <sub>16</sub>  | Port P2 pull-up control reg.      | 002A <sub>16</sub> | 00 <sub>16</sub>   |

| Port P2 reg.             | 000C <sub>16</sub> | 00 <sub>16</sub>  | Port P3 pull-up control reg.      | 002B <sub>16</sub> | 00 <sub>16</sub>   |

| Port P2 direction reg.   | 000D <sub>16</sub> | 00 <sub>16</sub>  | Port P4 pull-up/down control reg. | 002C <sub>16</sub> | 00 <sub>16</sub>   |

| Port P3 reg.             | 000E <sub>16</sub> | 00 <sub>16</sub>  | Interrupt polarity selection reg. | 002D <sub>16</sub> | 00 <sub>16</sub>   |

| Port P3 direction reg.   | 000F <sub>16</sub> | 00 <sub>16</sub>  | Watchdog timer reg.               | 002E <sub>16</sub> | 3F <sub>16</sub>   |

| Port P4 reg.             | 0010 <sub>16</sub> | 00 <sub>16</sub>  | Polarity control reg.             | 002F <sub>16</sub> | 0016               |

| Port P4 direction reg.   | 0011 <sub>16</sub> | 00 <sub>16</sub>  | CAN transmit control reg.         | 0030 <sub>16</sub> | 02 <sub>16</sub>   |

| Serial I/O control reg.  | 0013 <sub>16</sub> | 00 <sub>16</sub>  | CAN bus timing control reg. 1     | 0031 <sub>16</sub> | 00 <sub>16</sub>   |

| A-D control reg.         | 0015 <sub>16</sub> | 08 <sub>16</sub>  | CAN bus timing control reg. 2     | 0032 <sub>16</sub> | 00 <sub>16</sub>   |

| Timer 1                  | 0016 <sub>16</sub> | FF <sub>16</sub>  | CAN receive control reg.          | 003D <sub>16</sub> | 00 <sub>16</sub>   |

| Timer 2                  | 0017 <sub>16</sub> | 01 <sub>16</sub>  | CAN transmit abort reg.           | 003E <sub>16</sub> | 00 <sub>16</sub>   |

| Timer 3                  | 0018 <sub>16</sub> | FF <sub>16</sub>  | Processor status reg.             | (PS)               | 04 <sub>16</sub>   |

| Timer 123 mode reg.      | 0019 <sub>16</sub> | 40 <sub>16</sub>  | Program counter (high-order byte) | (PCH)              | contents of FFFB16 |

| Timer XL                 | 001A <sub>16</sub> | FF <sub>16</sub>  | Program counter (low-order byte)  | (PCL)              | contents of FFFA16 |

Note: The contents of RAM and registers other than the above registers are undefined after reset; thus software initialization is required.

Fig. 45 Internal status of microcomputer after reset

# **CLOCK GENERATING CIRCUIT**

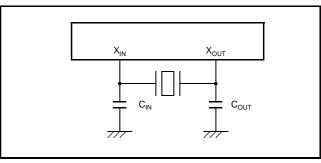

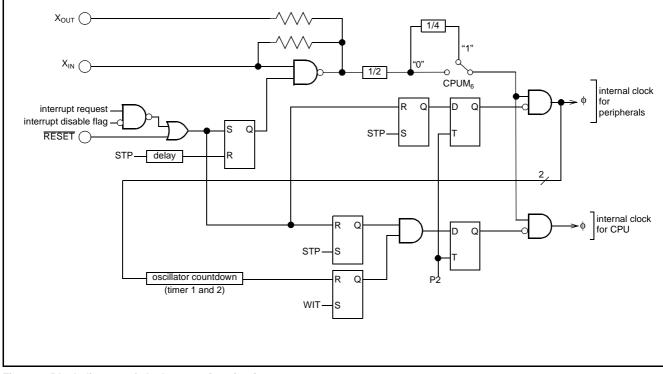

The 7630 group is equipped with an internal clock generating circuit.

Please refer to Fig. 46 for a circuit example using a ceramic resonator or quartz crystal oscillator. For the capacitor values, refer to the manufacturers recommended parameters which depend on each oscillators characteristics. When using an external clock, input it to the X<sub>IN</sub> pin and leave X<sub>OUT</sub> open.

### **Oscillation Control**

The 7630 group has two low power modes: the stop and the wait mode.

#### Stop mode

The microcomputer enters the stop mode by executing the STP instruction. The oscillator stops with the internal clock  $\varphi$  at "H" level. Timers 1 and 2 will be cascaded and initialized by their reload latches contents. The count source for timer 1 will be set to  $f(X_{\text{IN}})/16.$

Oscillation is restarted if an external interrupt is accepted or at reset. When using an external interrupt, the internal clock  $\phi$  remains at "H" level until timer 2 underflows allowing a time-out until the

Fig. 46 Ceramic resonator circuit

clock oscillation becomes stable. When using reset, a fixed time-out will be generated allowing oscillation to stabilize.

### Wait mode

The microcomputer enters the wait mode by executing the WIT instruction. The internal clock ø stops at "H" level while the oscillator keeps running.

Recovery from wait mode can be done in the same way as from stop mode. However, the time-out period mentioned above is not required to return from wait-mode, thus no such time-out mechanism has been implemented.

Note: Set the interrupt enable bit of the interrupt source to be used to return from stop or wait mode to "1" before executing STP or WIT instruction.

Fig. 47 Block diagram of clock generating circuit

# DATA REQUIRED FOR MASK ORDERS

The following are necessary when ordering a mask ROM production:

- 1 Mask ROM Order Confirmation Form

- 2 Mark Specification Form

- 3 Contents of Mask ROM, in EPROM form (three identical copies)

# **PROM PROGRAMMING METHOD**

The built-in PROM of the blank One Time PROM version and builtin EPROM version can be read or programmed with a general purpose PROM programmer using a special programming adapter. Set the address of PROM programmer to the user ROM area.

For the programming adapter type name, please refer to the following table:

#### Table 6: Programming adapter name

| MCU type         | Package | Programming adapter type |

|------------------|---------|--------------------------|

| One Time<br>PROM | 44P6N-A | PCA7430                  |

| EPROM            | 80D0    | PCA7431                  |

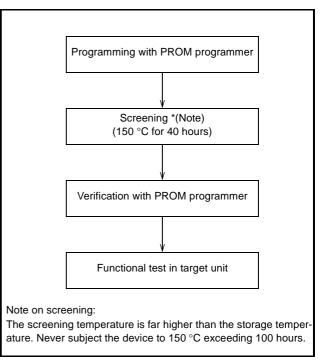

The PROM of the blank One Time PROM version is not tested or screened in the assembly process and following processes. To ensure proper operation after programming, the procedure shown in Fig. 48 is recommended to verify programming.

Fig. 48 Programming and testing of One Time PROM version

### Table 7: ABSOLUTE MAXIMUM RATINGS