# interdil

# CA3310, CA3310A

CMOS, 10-Bit, A/D Converters with Internal Track and Hold

August 1997

# Features

| • | CMOS Low Power (Typ)15mV |

|---|--------------------------|

| • | Single Supply Voltage    |

| • | Conversion Time          |

|   | Built-In Track and Hold  |

- Rail-to-Rail Input Range

- Latched Three-state Output Drivers

- Microprocessor-Compatible Control Lines

- Internal or External Clock

## **Applications**

- · Fast, No-Droop, Sample and Hold

- · Voice Grade Digital Audio

- **DSP Modems**

- **Remote Low Power Data Acquisition Systems**

- µP Controlled Systems

# Description

The Intersil CA3310 is a fast, low power, 10-bit successive approximation analog-to-digital converter, with microprocessorcompatible outputs. It uses only a single 3V to 6V supply and typically draws just 3mA when operating at 5V. It can accept full rail-to-rail input signals, and features a built-in track and hold. The track and hold will follow high bandwidth input signals, as it has only a 100ns (typical) input time constant.

The ten data outputs feature full high-speed CMOS threestate bus driver capability, and are latched and held through a full conversion cycle. Separate 8 MSB and 2 LSB enables, a data ready flag, and conversion start and ready reset inputs complete the microprocessor interface.

An internal, adjustable clock is provided and is available as an output. The clock may also be driven from an external source.

## Ordering Information

| PART<br>NUMBER | LINEARITY<br>(INL, DNL) |            | PACKAGE     | PKG.<br>NO. |

|----------------|-------------------------|------------|-------------|-------------|

| CA3310E        | ±0.75 LSB               | -40 to 85  | 24 Ld PDIP  | E24.6       |

| CA3310AE       | ±0.5 LSB                | -40 to 85  | 24 Ld PDIP  | E24.6       |

| CA3310M        | ±0.75 LSB               | -40 to 85  | 24 Ld SOIC  | M24.3       |

| CA3310AM       | ±0.5 LSB                | -40 to 85  | 24 Ld SOIC  | M24.3       |

| CA3310D        | ±0.75 LSB               | -55 to 125 | 24 Ld SBDIP | D24.6       |

| CA3310AD       | ±0.5 LSB                | -55 to 125 | 24 Ld SBDIP | D24.6       |

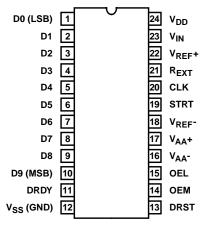

#### **Pinout**

CA3310, CA3310A (PDIP, SBDIP, SOIC) **TOP VIEW**

| INPUT RANGE    | R1    | R2    | R3    | R4    | R5    |

|----------------|-------|-------|-------|-------|-------|

| 0V TO 2.5V     | 4.99K | 9.09K | OPEN  | 4.99K | 9.09K |

| 0V TO 5V       | 4.99K | 4.53K | OPEN  | 4.99K | 4.53K |

| 0V TO 10V      | 10K   | 4.53K | OPEN  | 10K   | 4.53K |

| -2.5V TO +2.5V | 4.99K | 9.09K | 9.09K | 4.99K | 4.53K |

| -5V TO +5V     | 10K   | 9.09K | 9.09K | 10K   | 4.53K |

## CA3310, CA3310A

#

# Analog Supply Voltage ( $V_{AA}$ +) . . . . . . . . . $V_{DD}$ ±0.5V Any Other Terminal . . . . . . . . . $V_{SS}$ -0.5V to $V_{DD}$ + 0.5V DC Input Current or Output (Protection Diode)

DC Output Drain Current, per Output . ±35mA

Total DC Supply or Ground Current . ±70mA

#### **Operating Conditions**

| emperature Range (T <sub>A</sub> ) |               |

|------------------------------------|---------------|

| Package Type D                     | 55°C to 125°C |

|                                    | 40°C to 85°C  |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)                        | θ <sub>JA</sub> (°C/ | W) $\theta_{JC}$ ( $^{o}C/W$ ) |

|-------------------------------------------------------------|----------------------|--------------------------------|

| PDIP Package                                                | 7                    | 5 N/A                          |

| SBDIP Package                                               | 7                    | 0 22                           |

| SOIC Package                                                | 7                    | 5 N/A                          |

| Maximum Junction Temperature                                |                      |                                |

| Plastic Packages                                            |                      | 150 <sup>o</sup> C             |

| Hermetic Package                                            |                      |                                |

| Maximum Storage Temperature (T <sub>STG</sub> ) .           |                      | 65°C to 150°C                  |

| Maximum Lead Temperature (Soldering (SOIC - Lead Tips Only) |                      |                                |

| (OOIO - Load Tips Offis)                                    |                      |                                |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

**Electrical Specifications**  $T_A = 25^{\circ}\text{C}$ ,  $V_{DD} = V_{AA} + = 5\text{V}$ ,  $V_{REF} + = 4.608\text{V}$ ,  $V_{SS} = V_{AA} - = V_{REF} - = GND$ , CLK = External 1MHz, Unless Otherwise Specified

| PARAMETER                    | 2                               | TEST CONDITIONS                                                     | MIN                   | TYP   | MAX                  | UNITS                   |

|------------------------------|---------------------------------|---------------------------------------------------------------------|-----------------------|-------|----------------------|-------------------------|

| ACCURACY (See Text For       | Definitions)                    |                                                                     | ·                     |       |                      |                         |

| Resolution                   |                                 |                                                                     | 10                    | -     | -                    | Bits                    |

| Differential Linearity Error | CA3310                          |                                                                     | -                     | ±0.5  | ±0.75                | LSB                     |

|                              | CA3310A                         |                                                                     | -                     | ±0.25 | ±0.5                 | LSB                     |

| Integral Linearity Error     | CA3310                          |                                                                     | -                     | ±0.5  | ±0.75                | LSB                     |

|                              | CA3310A                         |                                                                     | -                     | ±0.25 | ±0.5                 | LSB                     |

| Gain Error                   | CA3310                          |                                                                     | -                     | ±0.25 | ±0.5                 | LSB                     |

|                              | CA3310A                         |                                                                     | -                     | -     | ±0.25                | LSB                     |

| Offset Error                 | CA3310                          |                                                                     | -                     | ±0.25 | ±0.5                 | LSB                     |

|                              | CA3310A                         |                                                                     | -                     | -     | ±0.25                | LSB                     |

| ANALOG OUTPUT                |                                 |                                                                     |                       |       |                      |                         |

| Input Resistance             |                                 | In Series with Input Sample Capacitors                              | -                     | 330   | -                    | Ω                       |

| Input Capacitance            |                                 | During Sample State                                                 | -                     | 300   | -                    | pF                      |

| Input Capacitance            |                                 | During Hold State                                                   | -                     | 20    | -                    | pF                      |

| Input Current                |                                 | At $V_{IN} = V_{REF} + = 5V$                                        | -                     | -     | +300                 | μΑ                      |

|                              |                                 | At V <sub>IN</sub> = V <sub>REF</sub> - = 0V                        | -                     | -     | -100                 | μΑ                      |

| Static Input Current         |                                 | STRT = V+, CLK = V+<br>At V <sub>IN</sub> = V <sub>REF</sub> + = 5V | -                     | -     | 1                    | μΑ                      |

|                              |                                 | At V <sub>IN</sub> = V <sub>REF</sub> - = 0V                        | -                     | -     | -1                   | μΑ                      |

| Input + Full-Scale Range     |                                 | (Note 2)                                                            | V <sub>REF</sub> - +1 | -     | V <sub>DD</sub> +0.3 | V                       |

| Input - Full-Scale Range     |                                 | (Note 2)                                                            | V <sub>SS</sub> -0.3  | -     | V <sub>REF</sub> +-1 | V                       |

| Input Bandwidth              | dth From Input RC Time Constant |                                                                     | -                     | 1.5   | -                    | MHz                     |

| DIGITAL INPUTS DRST, C       | EL, OEM, ST                     | RT, CLK                                                             | -                     |       |                      |                         |

| High-Level Input Voltage     |                                 | Over V <sub>DD</sub> = 3V to 6V (Note 2)                            | 70                    | -     | -                    | % of<br>V <sub>DD</sub> |

| Low-Level Input Voltage      |                                 | Over V <sub>DD</sub> = 3V to 6V (Note 2)                            | -                     | -     | 30                   | % of<br>V <sub>DD</sub> |

| Input Leakage Current        |                                 | Except CLK                                                          | -                     | -     | ±1                   | μΑ                      |

| Input Capacitance            |                                 | (Note 2)                                                            | -                     | -     | 10                   | pF                      |

| Input Current                |                                 | CLK Only (Note 2)                                                   | -                     | -     | ±400                 | μΑ                      |

# CA3310, CA3310A

| PARAMETER                                                  | TEST CONDITIONS                                    | MIN | TYP  | MAX  | UNITS              |

|------------------------------------------------------------|----------------------------------------------------|-----|------|------|--------------------|

| DIGITAL OUTPUTS D0 - D9, DRDY                              | -                                                  |     |      |      |                    |

| High-Level Output Voltage                                  | I <sub>SOURCE</sub> = -4mA                         | 4.6 | -    | -    | V                  |

| Low-Level Output Voltage                                   | I <sub>SINK</sub> = 6mA                            | -   | -    | 0.4  | V                  |

| Three-State Leakage                                        | Except DRDY                                        | -   | -    | ±1   | μΑ                 |

| Output Capacitance                                         | Except DRDY (Note 2)                               | -   | -    | 20   | pF                 |

| CLK OUTPUT                                                 | ·                                                  |     | •    |      | •                  |

| High-Level Output Voltage                                  | I <sub>SOURCE</sub> = 100μA (Note 2)               | 4   | -    | -    | V                  |

| Low-Level Output Voltage                                   | I <sub>SINK</sub> = 100μA (Note 2)                 | -   | -    | 1    | V                  |

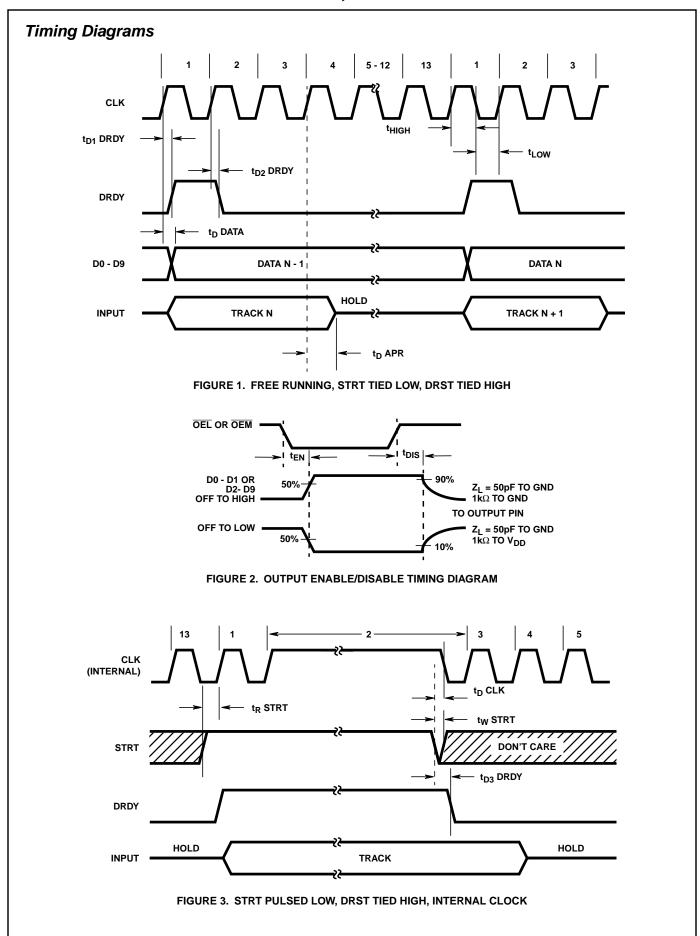

| TIMING                                                     | ·                                                  |     | •    |      | •                  |

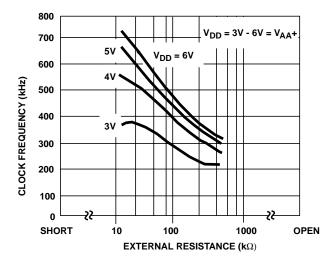

| Clock Frequency                                            | Internal, CLK and R <sub>EXT</sub> Open            | 200 | 300  | 400  | kHz                |

|                                                            | Internal, CLK Shorted to R <sub>EXT</sub>          | 600 | 800  | 1000 | kHz                |

|                                                            | External, Applied to CLK (Note 2) (Max)            | -   | 4    | 2    | MHz                |

|                                                            | (Min)                                              | 100 | 10   | -    | kHz                |

| Clock Pulse Width, t <sub>LOW</sub> , t <sub>HIGH</sub>    | External, Applied to CLK:<br>See Figure 1 (Note 2) | 100 | -    | -    | ns                 |

| Conversion Time                                            | Internal, CLK Shorted to R <sub>EXT</sub>          | 13  | -    | -    | μs                 |

| Aperture Delay, t <sub>D</sub> APR                         | See Figure 1                                       | -   | 100  | -    | ns                 |

| Clock to Data Ready Delay, t <sub>D1</sub> DRDY            | See Figure 1                                       | -   | 150  | -    | ns                 |

| Clock to Data Ready Delay, t <sub>D2</sub> DRDY            | See Figure 1                                       | -   | 250  | -    | ns                 |

| Clock to Data Delay, t <sub>D</sub> Data                   | See Figure 1                                       | -   | 200  | -    | ns                 |

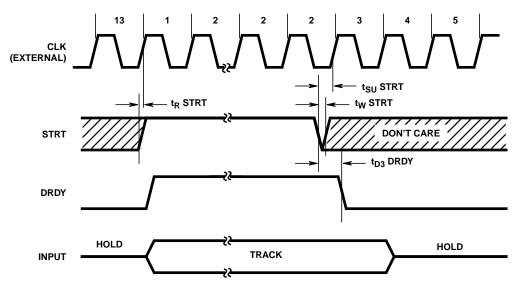

| Start Removal Time, t <sub>R</sub> STRT                    | See Figures 3 and 4 (Note 1)                       | -   | -120 | -    | ns                 |

| Start Setup Time, t <sub>SU</sub> STRT                     | See Figure 4                                       | -   | 160  | -    | ns                 |

| Start Pulse Width, t <sub>W</sub> STRT                     | See Figures 3 and 4                                | -   | 10   | -    | ns                 |

| Start to Data Ready Delay, t <sub>D3</sub> DRDY            | See Figures 3 and 4                                | -   | 170  | -    | ns                 |

| Clock Delay from Start, t <sub>D</sub> CLK                 | See Figure 3                                       | -   | 200  | -    | ns                 |

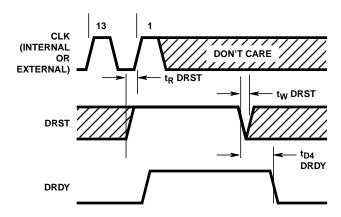

| Ready Reset Removal Time, t <sub>R</sub> DRST              | See Figure 50 (Note 1)                             | -   | -80  | -    | ns                 |

| Ready Reset Pulse Width, t <sub>W</sub> DRST               | See Figure 5                                       | -   | 10   | -    | ns                 |

| Ready Reset to Data Ready Delay, t <sub>D4</sub> DRDY      | See Figure 5                                       | -   | 35   | -    | ns                 |

| Output Enable Delay, t <sub>EN</sub>                       | See Figure 2                                       | -   | 40   | -    | ns                 |

| Output Disable Delay, t <sub>DIS</sub>                     | See Figure 2                                       | -   | 50   | -    | ns                 |

| SUPPLIES                                                   |                                                    |     |      |      |                    |

| Supply Operating Range, V <sub>DD</sub> or V <sub>AA</sub> | (Note 2)                                           | 3   | -    | 6    | V                  |

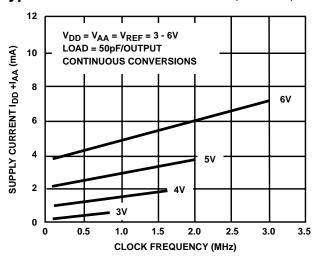

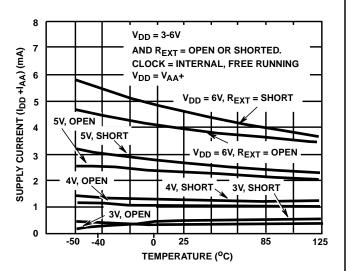

| Supply Current, I <sub>DD</sub> + I <sub>AA</sub>          | See Figures 14, 15                                 | -   | 3    | 8    | mA                 |

| Supply Standby Current                                     | Clock Stopped During Cycle 1                       | -   | 3.5  | -    | mA                 |

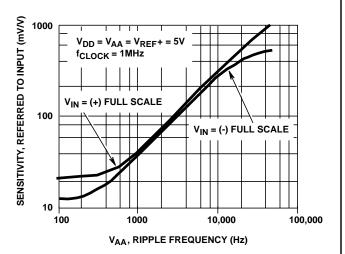

| Analog Supply Rejection                                    | At 120Hz, See Figure 13                            | -   | 25   | -    | mV/V               |

| Reference Input Current                                    | See Figure 10                                      | -   | 160  | -    | μА                 |

| TEMPERATURE DEPENDENCY                                     | · · · · · · · · · · · · · · · · · · ·              |     |      | -    | -                  |

| Offset Drift                                               | At 0 to 1 Code Transition                          | -   | -4   | -    | μV/ <sup>o</sup> C |

| Gain Drift                                                 | At 1022 to 1023 Code Transition                    | -   | -6   | -    | μV/ <sup>o</sup> C |

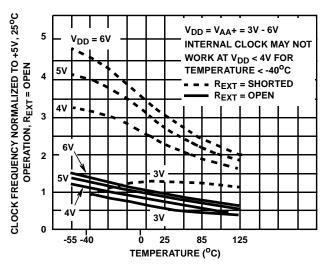

| Internal Clock Speed                                       | See Figure 7                                       | -   | -0.5 | -    | %/°C               |

## NOTES:

- 1. A (-) removal time means the signal can be removed after the reference signal.

- 2. Parameter not tested, but guaranteed by design or characterization.

# Timing Diagrams (Continued)

FIGURE 4. STRT PULSED LOW, DRST TIED HIGH, EXTERNAL CLOCK

FIGURE 5. DRST PULSED LOW, STRT TIED HIGH

# **Typical Performances Curves**

FIGURE 6. INTERNAL CLOCK FREQUENCY vs EXTERNAL RESISTANCE

FIGURE 7. INTERNAL CLOCK FREQUENCY vs

TERMPERATURE AND SUPPLY VOLTAGE

# Typical Performances Curves (Continued)

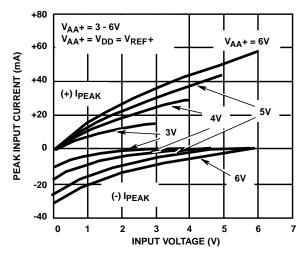

FIGURE 8. PEAK INPUT CURRENT vs INPUT VOLTAGE

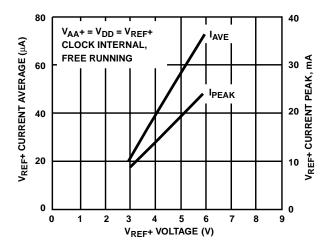

FIGURE 10. V<sub>REF</sub>+ CURRENT vs V<sub>REF</sub>+ VOLTAGE

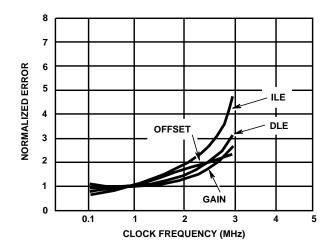

FIGURE 12. NORMALIZED GAIN, OFFSET, INTEGRAL AND DIFFERENTIAL LINEARITY ERRORS vs CLOCK SPEED

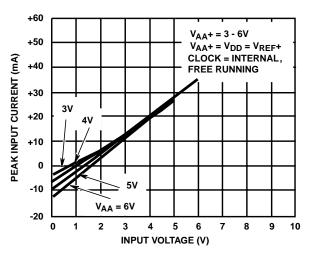

FIGURE 9. AVERAGE INPUT CURRENT vs INPUT VOLTAGE

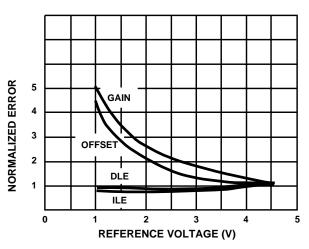

FIGURE 11. NORMALIZED GAIN, OFFSET, INTEGRAL AND DIFFERENTIAL LINEARITY ERRORS vs REFERENCE VOLTAGE

FIGURE 13. VAA SUPPLY SENSITIVITY

# Typical Performances Curves (Continued)

FIGURE 14. SUPPLY CURRENT vs CLOCK FREQUENCY

FIGURE 15. SUPPLY CURRENT vs TEMPERATURE

**TABLE 1. PIN DESCRIPTIONS**

| PIN NUMBER | NAME               | DESCRIPTION                                                                                                                                                 |

|------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-10       | D0 - D9            | Three-State outputs for data bits representing 2 <sup>0</sup> (LSB) through 2 <sup>9</sup> (MSB).                                                           |

| 11         | DRDY               | Output flag signifying new data is available. Goes high at end of clock period 13, goes low when new conversion started. Also reset asynchronously by DRST. |

| 12         | V <sub>SS</sub>    | Digital Ground.                                                                                                                                             |

| 13         | DRST               | Active low input, resets DRDY.                                                                                                                              |

| 14         | OEM                | Active low input, three-state enable of D2 - D9.                                                                                                            |

| 15         | OEL                | Active low input, three-state enable of D0, D1.                                                                                                             |

| 16         | V <sub>AA</sub> -  | Analog Ground.                                                                                                                                              |

| 17         | V <sub>AA</sub> +  | Analog + Supply.                                                                                                                                            |

| 18         | V <sub>REF</sub> - | Reference input voltage, sets 0 code (-) end of input range.                                                                                                |

| 19         | STRT               | Active Low Start Conversion Input. Recognized after end of clock period 13.                                                                                 |

| 20         | CLK                | Clock input or output. Conversion functions are synchronous to high-going edge.                                                                             |

| 21         | R <sub>EXT</sub>   | Clock adjust input when using internal clock.                                                                                                               |

| 22         | V <sub>REF</sub> + | Reference input voltage, set 1023 code (+) end of input range.                                                                                              |

| 23         | V <sub>IN</sub>    | Analog Input.                                                                                                                                               |

| 24         | V <sub>DD</sub>    | Digital + Supply.                                                                                                                                           |

#### **TABLE 2. OUTPUT CODES**

| CODE<br>DESCRIPTION                                                   | INPUT VOLTAGE (NOTE 1) (V <sub>REF+</sub> - V <sub>REF-</sub> ) = 4.608V | MSB |    |    | BINA | RY OU | TPUT | CODE |    |    | LSB | DECIMAL |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------|-----|----|----|------|-------|------|------|----|----|-----|---------|

| $LSB = \frac{(V_{REF+} - V_{REF-})}{1024}$                            | (V)                                                                      | D9  | D8 | D7 | D6   | D5    | D4   | D3   | D2 | D1 | D0  | COUNT   |

| Zero                                                                  | 0.000                                                                    | 0   | 0  | 0  | 0    | 0     | 0    | 0    | 0  | 0  | 0   | 0       |

| 1 LSB                                                                 | 0.0045                                                                   | 0   | 0  | 0  | 0    | 0     | 0    | 0    | 0  | 0  | 1   | 1       |

| <sup>1</sup> / <sub>4</sub> (V <sub>REF</sub> + - V <sub>REF</sub> -) | 1.152                                                                    | 0   | 1  | 0  | 0    | 0     | 0    | 0    | 0  | 0  | 0   | 256     |

| <sup>1</sup> / <sub>2</sub> (V <sub>REF</sub> + - V <sub>REF</sub> -) | 2.304                                                                    | 1   | 0  | 0  | 0    | 0     | 0    | 0    | 0  | 0  | 0   | 512     |

| <sup>3</sup> / <sub>4</sub> (V <sub>REF</sub> + - V <sub>REF</sub> -) | 3.456                                                                    | 1   | 1  | 0  | 0    | 0     | 0    | 0    | 0  | 0  | 0   | 768     |

| (V <sub>REF</sub> + - V <sub>REF</sub> -) - 1 LSB                     | 4.6035                                                                   | 1   | 1  | 1  | 1    | 1     | 1    | 1    | 1  | 1  | 1   | 1023    |

NOTE:

<sup>1.</sup> The voltages listed above are the ideal centers of each output code shown as a function of its associated reference voltage.

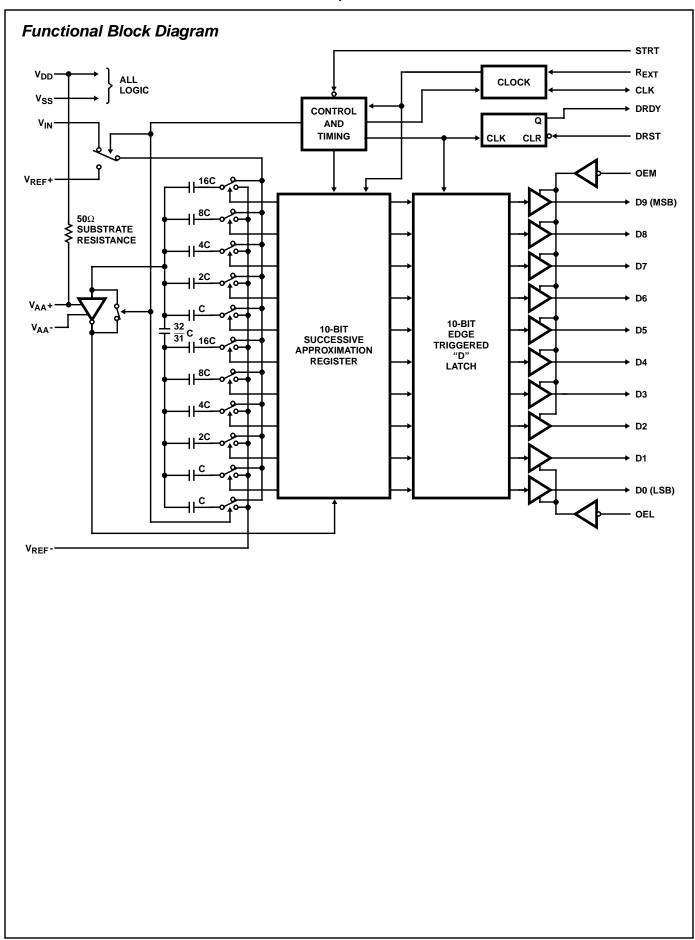

## **Device Operation**

The CA3310 is a CMOS 10-bit, analog-to-digital converter that uses capacitor-charge balancing to successively approximate the analog input. A binarily weighted capacitor network forms the D-to-A "Heart" of the device. See the Functional Diagram of the CA3310.

The capacitor network has a common node which is connected to a comparator. The second terminal of each capacitor is individually switchable to the input, V<sub>RFF</sub>+ or V<sub>RFF</sub>-.

During the first three clock periods of a conversion cycle, the switchable end of every capacitor is connected to the input. The comparator is being auto-balanced at its trip point, thus setting the voltage at the capacitor common node.

During the fourth period, all capacitors are disconnected from the input, the one representing the MSB (D9) is connected to the  $V_{REF}$ + terminal, and the remaining capacitors to  $V_{REF}$ -. The capacitor-common node, after the charges balance out, will represent whether the input was above or below  $^{1}/_{2}$  of ( $V_{REF}$ + -  $V_{REF}$ ).

At the end of the fourth period, the comparator output is stored and the MSB capacitor is either left connected to  $V_{REF}$ + (if the comparator was high) or returned to  $V_{REF}$ -. This allows the next comparison to be at either  $^3/_4$  or  $^1/_4$  of  $(V_{REF}$ +- $V_{REF}$ -).

At the end of periods 5 through 12, capacitors representing the next to MSB (D8) through the next to LSB (D1) are tested, the result stored, and each capacitor either left at  $V_{REF}$ + or at  $V_{REF}$ -.

At the end of the 13th period, when the LSB (D0) capacitor is tested, D0 and all the previous results are shifted to the output registers and drivers. The capacitors are reconnected to the input, the comparator returns to the balance state, and the data-ready output goes active. The conversion cycle is now complete.

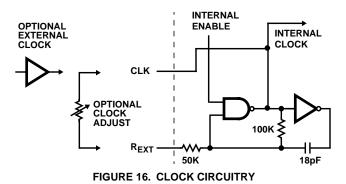

#### Clock

The CA3310 can operate either from its internal clock or from one externally supplied. The CLK pin functions either as the clock output or input. All converter functions are synchronous with the rising edge of the clock signal.

Figure 16 shows the configuration of the internal clock. The clock output drive is low power: if used as an output, it should not have more than 1 CMOS gate load applied, and wiring capacitance should be kept to a minimum.

The  $R_{\text{EXT}}$  pin allows adjusting of the internal clock frequency by connecting a resistor between  $R_{\text{EXT}}$  and CLK. Figure 6 shows the typical relationship between the resistor and clock speed, while Figure 7 shows clock speed versus temperature and supply voltage.

The internal clock will shut down if the A/D is not restarted after a conversion. This is described under Control Timing. The clock could also be shut down with an open collector driver applied to the CLK pin. This should only be done during the sample portion (the first three periods) of a conversion cycle, and might be useful for using the device as a digital sample and hold: this is described further under Applications.

If an external clock is supplied to the CLK pin, it must have sufficient drive to overcome the internal clock source. The external clock can be shut off, but again only during the sample portion of a conversion cycle. At other times, it must be above the minimum frequency shown in the specifications.

If the internal or external clock was shut off during the conversion time (clock cycles 4 through 13) of the A/D, the output might be invalid due to balancing capacitor droop.

An external clock must also meet the minimum  $t_{\mbox{LOW}}$  and  $t_{\mbox{HIGH}}$  times shown in the specifications. A violation may cause an internal miscount and invalidate the results.

#### **Control Signals**

The CA3310 may be synchronized from an external source by using the STRT (Start Conversion) input to initiate conversions, or if STRT is tied low, may be allowed to free-run. In the free-running mode, illustrated in Figure 1, each conversion takes 13 clock periods.

The input is tracked from clock period 1 through period 3, then disconnected as the successive approximation takes place. After the start of the next period 1 (specified by  $T_D$  data), the output is updated.

The DRDY (Data Ready) status output goes high (specified by  $t_{D1}$  DRDY) after the start of clock period 1, and returns low (specified by  $t_{D2}$  DRDY) after the start of clock period 2. DRDY may also be asynchronously reset by a low on DRST (to be discussed later).

If the output data is to be latched externally by the DRDY signal, the trailing edge of DRDY should be used: there is no guaranteed set-up time to the leading edge.

The 10 output data bits are available in parallel on three-state bus driver outputs. When low, the OEM input enables the most significant byte (D2 through D9) while the OEL input enables the two least significant bits (D0, D1).  $t_{\text{EN}}$  and  $t_{\text{DIS}}$  specify the output enable and disable times, respectively. See Figure 2.

When the STRT input is used to initiate conversions, operation is slightly different depending on whether an internal or external clock is used.

Figure 3 illustrates operation with an internal clock. If the STRT signal is removed (at least t<sub>R</sub> STRT) before clock period 1, and is not reapplied during that period, the clock

will shut off after entering period 2. The input will continue to track the DRDY output will remain high during this time.

A low signal applied to STRT (at least  $t_W$  STRT wide) can now initiate a new conversion. The STRT signal (after a delay of  $t_{D3}$  DRDY) will cause the DRDY flag to drop, and (after a delay of  $t_D$  CLK) cause the clock to restart.

Depending on how long the clock was shut off, the low portion of clock period 2 may be longer than during the remaining cycles.

The input will continue to track until the end of period 3, the same as when free-running.

Figure 4 illustrates the same operation as above, but with an external clock. If STRT is removed (at least  $t_R$  STRT) before clock period 1, and not reapplied during that period, the clock will continue to cycle in period 2. A low signal applied to STRT will drop the DRDY flag as before, and with the first positive-going clock edge that meets the  $t_{SU}$  STRT set-up time, the converter will continue with clock period 3.

The DRDY flag output, as described previously, goes active at the start of period 1, and drops at the start of period 2 or upon a new STRT command, whichever is later. It may also be controlled with the DRST (Data Ready Reset) input. Figure 5 depicts this operation.

DRST must be removed (at least  $t_R$  DRST) before the start of period 1 to allow DRDY to go high. A low level on DRST (at least  $t_W$  DRST wide) will (after a delay of  $t_{D4}$  DRDY) drop DRDY.

#### **Analog Input**

The analog input pin is a predominantly capacitive load that changes between the track and hold periods of a conversion cycle. During hold, clock period 4 through 13, the input loading is leakage and stray capacitance, typically less than  $0.1\mu A$  and 20pF.

At the start of input tracking, clock period 1, some charge is dumped back to the input pin. The input source must have low enough impedance to dissipate the charge by the end of the tracking period. The amount of charge is dependent on supply and input voltages. Figure 8 shows typical peak input currents for various supply and input voltages, while Figure 9 shows typical average input currents. The average current is also proportional to clock frequency, and should be scaled accordingly.

During tracking, the input appears as approximately a 300pF capacitor in series with 330 $\Omega$ , for a 100ns time constant. A full-scale input swing would settle to  $^{1}/_{2}$  LSB ( $^{1}/_{2048}$ ) in 7RC time constants. Doing continuous conversions with a 1MHz clock provides 3 $\mu$ s of tracking time, so up to 1k $\Omega$  of external source impedance (400ns time constant) would allow proper settling of a step input.

If the clock was slower, or the converter was not restarted immediately (causing a longer sample lime), a higher source impedance could be used.

The CA3310s low-input time constant also allows good tracking of dynamic input waveforms. The sampling rate with a 1MHz clock is approximately 80kHz. A Nyquist rate (f<sub>SAMPLE</sub>/2) input sine wave of 40kHz would have negligible attenuation and a phase lag of only 1.5 degrees.

#### **Accuracy Specifications**

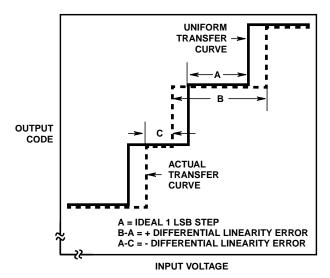

The CA3310 accepts an analog input between the values of  $V_{REF}$ - and  $V_{REF}$ +, and quantizes it into one of  $2^{10}$  or 1024 output codes. Each code should exist as the input is varied through a range of  $^{1}/_{1024}$  X ( $V_{REF}$ + -  $V_{REF}$ -), referred to as 1 LSB of input voltage. A differential linearity error, illustrated in Figure 17, occurs if an output code occurs over other than the ideal (1 LSB) input range. Note that as long as the error does not reach -1 LSB, the converter will not miss any codes.

FIGURE 17. DIFFERENTIAL LINEARITY ERROR

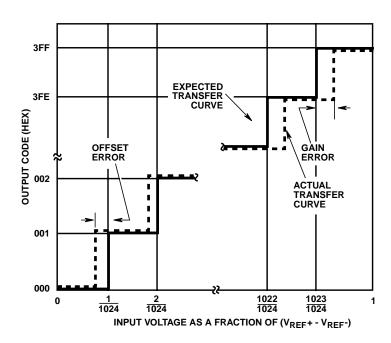

The CA3310 output should change from a code of  $000_{16}$  to  $001_{16}$  at an input voltage of ( $V_{REF}$ -+1 LSB). It should also change from a code of  $3FE_{16}$  to  $3FF_{16}$  at an input of ( $V_{REF}$ +-1 LSB). Any differences between the actual and expected input voltages that cause these transitions are the offset and gain errors, respectively. Figure 18 illustrates these errors.

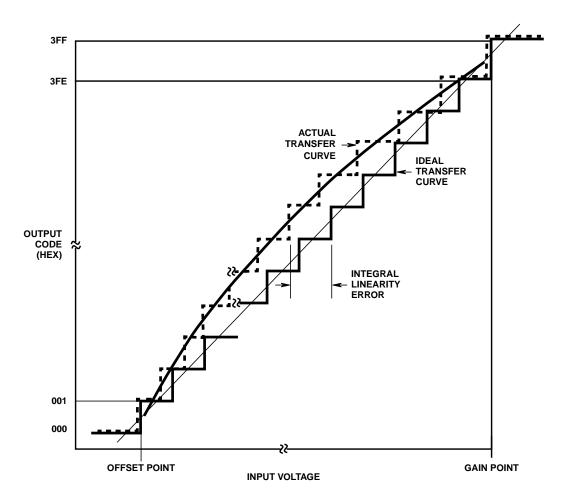

As the input voltage is increased linearly from the point that causes the 000<sub>16</sub> to 001<sub>16</sub> transition to the point that causes the 3FE<sub>16</sub> to 3FF<sub>16</sub> transition, the output code should also increase linearly. Any deviation from this input-to-output correspondence is integral linearity error, illustrated in Figure 19.

Note that the integral linearity is referenced to a straight line drawn through the actual end points, not the ideal end points. For absolute accuracy to be equal to the integral linearity, the gain and offset would have to be adjusted to ideal.

#### Offset and Gain Adjustments

The  $V_{REF}+$  and  $V_{REF}-$  pins, references for the two ends of the analog input range, are the only means of doing offset or gain adjustments. In a typical system, the  $V_{REF}-$  might be returned to a clean ground, and offset adjustment done on an input amplifier.  $V_{REF}+$  would then be adjusted for gain.

$V_{REF}\text{-}$  could be raised from ground to adjust offset or to accommodate an input source that can't drive down to ground. There are current pulses that occur, however, during the successive approximation part of a conversion cycle, as the charge-balancing capacitors are switched between  $V_{REF}\text{-}$  and  $V_{REF}\text{+}$ . For that reason,  $V_{REF}\text{-}$  and  $V_{REF}\text{+}$  should be well bypassed. Figure 10 shows peak and average  $V_{REF}\text{+}$  current.

FIGURE 18. GAIN AND OFFSET ERROR

FIGURE 19. NORMALIZED GAIN, OFFSET, INTEGRAL AND DIFFERENTIAL LINEARITY ERRORS VS REFERENCE VOLTAGE

#### **Other Accuracy Effects**

Linearity, offset, and gain errors are dependent on the magnitude of the full-scale input range,  $V_{REF}$ + -  $V_{REF}$ -. Figure 11 shows how these errors vary with full-scale range.

The clocking speed is a second factor that affects conversion accuracy. Figure 12 shows the typical variation of linearity, offset, and gain errors versus clocking speed.

Gain and offset drift due to temperature are kept very low by means of auto-balancing the comparator. The specifications show typical offset and gain dependency on temperature.

There is also very little linearity change with temperature, only that caused by the slight slowing of CMOS with increasing temperature. At 85°C, for instance, the ILE and DLE would be typically those for a 20% faster clock than at 25°C.

#### **Power Supplies and Grounding**

$\rm V_{DD}(+)$  and  $\rm V_{SS}(GND)$  are the digital supply pins: they operate all internal logic and the output drivers. Because the output drivers can cause fast current spikes in the  $\rm V_{DD}$  and  $\rm V_{SS}$  lines,  $\rm V_{SS}$  should have a low impedance path to digital ground and  $\rm V_{DD}$  should be well bypassed.

Except for  $V_{DD}$ +, which is a substrate connection to  $V_{DD}$ , all pins have protection diodes connected to  $V_{DD}$  and  $V_{SS}$ : input transients above  $V_{DD}$  or below  $V_{SS}$  will get steered to the digital supplies. Current on these pins must be limited by external means to the values specified under maximum ratings.

The  $V_{AA}$ + and  $V_{AA}$ - terminals supply the charge-balancing comparator only. Because the comparator is autobalanced between conversions, it has good low frequency supply rejection. It does not reject well at high frequencies, however:  $V_{AA}$ - should be returned to a clean analog ground, and  $V_{AA}$ + should be RC decoupled from the digital supply.

There is approximately  $50\Omega$  of substrate impedance between  $V_{DD}$  and  $V_{AA}+$ . This can be used, for example, as part of a low-pass RC filter to attenuate switching supply noise. A 10pF capacitor from  $V_{AA}+$  to ground would attenuate 30kHz noise by approximately 40dB. Note that back-to-back diodes should be placed from  $V_{DD}$  to  $V_{AA}+$  to handle supply to capacitor turn-on or turn-off current spikes.

Figure 16 shows  $V_{AA}$ + supply rejection versus frequency. Note that the frequency to be rejected scales with the clock: the 100Hz rejection with a 100kHz clock would be roughly equivalent to the 1kHz rejection with a 1MHz clock.

The supply current for the CA3310 is dependent on clock frequency, supply voltage, and temperature. Figure 14 shows the typical current versus frequency and voltage, while Figure 15 shows it versus temperature and voltage. Note that if stopped in auto-balance, the supply current is typically somewhat higher than if free-running. See Specifications.

# **Application Circuits**

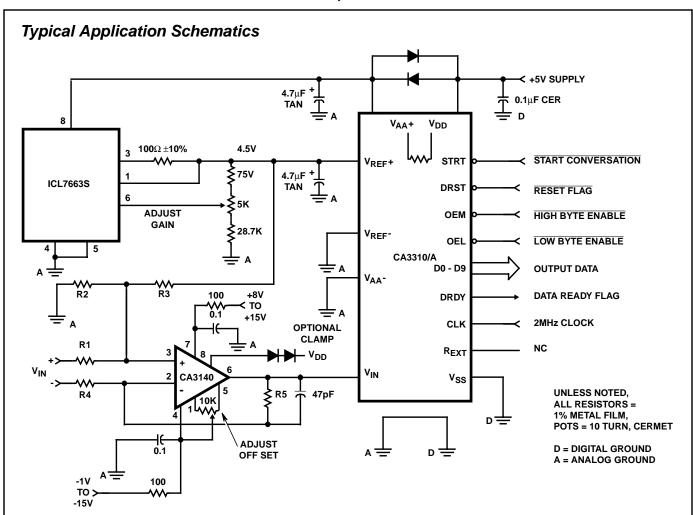

#### **Differential Input A/D System**

As the CA3310 accepts a unipolar positive-analog input, the accommodation of other ranges requires additional circuitry. The input capacitance and the input energy also force using a low-impedance source for all but slow speed use. Figure 20 shows the CA3310 with a reference, input amplifier, and input-scaling resistors for several input ranges.

The ICL7663S regulator was chosen as the reference, as it can deliver less than 0.25V input-to-output (dropout) voltage and uses very little power. As high a reference as possible is generally desirable, resulting in the best linearity and rejection of noise at the CA3310.

The tantalum capacitor sources the  $V_{\text{REF}}$  current spikes during a conversion cycle. This relieves the response and peak current requirements of the reference.

The CA3140 operational amplifier provides good slewing capability for high bandwidth input signals and can quickly settle the energy that the CA3310 outputs at its  $V_{\text{IN}}$  terminal. It can also drive close to the negative supply rail.

If system supply sequencing or an unknown input voltage is likely to cause the operational amplifier to drive above the  $V_{DD}$  supply, a diode clamp can be added from pin 8 of the operational amplifier to the  $V_{DD}$  supply. The minus drive current is low enough not to require protection.

With a 2MHz clock (~150kHz sampling), Nyquist criteria would give a maximum input bandwidth of 75kHz. The resistor values chosen are low enough to not seriously degrade system bandwidth (an operational amplifier settling) at that clock frequency. If A/D clock frequency and bandwidth requirements are lower, the resistor values (and input impedance) can be made correspondingly higher.

The A/D system would generally be calibrated by tying  $V_{IN}$ - to ground and applying a voltage to  $V_{IN}$ + that is 0.5 LSB ( $^{1}/_{2048}$  of full-scale range) above ground. The operational amplifier offset should be adjusted for an output code dithering between 000<sub>16</sub> and 001<sub>16</sub> for unipolar use, or 100<sub>16</sub> and 101<sub>16</sub> for bipolar use. The gain would then be adjusted by applying a voltage that is 1.5 LSB below the positive full scale input, and adjusting the reference for an output dithering between 3FE<sub>16</sub> and 3FF<sub>16</sub>.

Note that R1 through R5 should be very well matched, as they affect the common-mode rejection of the A/D system. Also, if R2 and R3 are not matched, the offset adjust of the operational amplifier may not have enough adjustment range in bipolar systems.

The common-mode input range of the system is set by the supply voltage available to the operational amplifier. The range that can be applied to the  $V_{\mbox{IN}}$ - terminal can be calculated by:

$\left(\frac{R4}{R5} + 1\right)$  V<sub>IN</sub>- for the most negative,

$\left(\frac{R4}{R5}+1\right) \quad \left(V_{IN}\text{+ -2.5V}\right)$  -  $\left(\frac{R4}{R5}\right)V_{REF}\text{+}$  for the most positive.

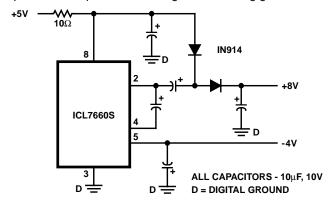

#### Single +5V Supply

If only a single +5V supply is available, an ICL7660 can be used to provide approximately +8V and -4V to the operational amplifier. Figure 20 shows this approach. Note that the converter and associated capacitors should be grounded to the digital supply. The  $1k\Omega$  in series with each supply at the operational amplifier isolates digital and analog grounds.

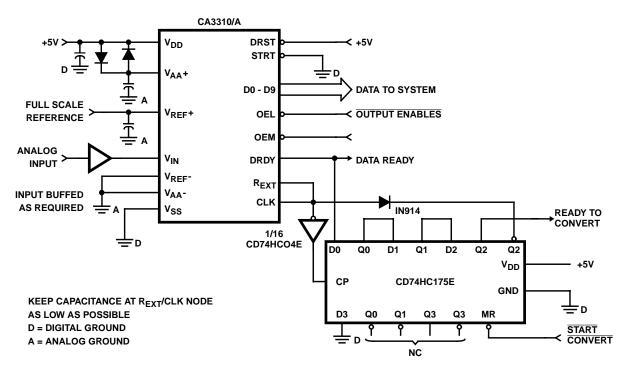

#### **Digital Sample and Hold**

With a minimum of external logic, the CA3310 can be made to wait at the verge of ending a sample. A start pulse will then, after the internal aperture delay, capture the input and finish the conversion cycle. Figure 21 illustrates this application.

The CA3310 is connected as if to free run. The Data Ready signal is shifted through a CD74HC175, and at the low-going clock edge just before the sample would end, is used to hold the clock low.

The same signal, active high, is available to indicate the CA3310 is ready to convert. A low pulse to reset the CD74HC175 will now release the clock, and the sample will

end as it goes positive. Ten cycles later, the conversion will be complete, and DRDY will go active.

# **Operating and Handling Considerations**

#### **HANDLING**

All inputs and outputs of Intersil CMOS devices have a network for electrostatic protection during handling. Recommended handling practices for CMOS devices are described in ICAN-6526, "Guide to Better Handling and Operation of CMOS Integrated Circuits".

#### **OPERATING**

#### **Operating Voltage**

During operation near the maximum supply voltage limit, care should be taken to avoid or suppress power supply turn-on and turn-off transients, power supply ripple, or ground noise; any of these conditions must not cause  $V_{DD}$  -  $V_{SS}$  to exceed the absolute maximum rating.

#### **Input Signals**

To prevent damage to the input protection circuit, input signals should never be greater than  $V_{DD}$  +0.3V nor less than  $V_{SS}$ -0.3V. Input currents must not exceed 20mA even when the power supply is off.

#### **Unused Inputs**

A connection must be provided at every input terminal. All unused Input terminals must be connected to either  $V_{DD}$  or  $V_{SS}$ , whichever is appropriate.

#### **Output Short Circuits**

Shorting of outputs to  $V_{\mbox{DD}}$  or  $V_{\mbox{SS}}$  may damage CMOS devices by exceeding the maximum device dissipation.

FIGURE 20. DIGITAL TRACK-AND-HOLD BLOCK DIAGRAM

# CA3310, CA3310A

|                                                 |                                                                                            | and tested under <b>ISO9000</b> quality systems certific<br>make changes in circuit design and/or specifications at any tin                  |            |

|-------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------|

| notice. Accordingly, the reader is cautioned to | verify that data sheets are current before umed by Intersil or its subsidiaries for its us | placing orders. Information furnished by Intersil is believed to be<br>ee; nor for any infringements of patents or other rights of third par | e accurate |

|                                                 |                                                                                            | ucts, see web site http://www.intersil.com                                                                                                   |            |

| Sales Office Headquarte                         | rs                                                                                         |                                                                                                                                              |            |

| NORTH AMERICA<br>Intersil Corporation           | EUROPE<br>Intersil SA                                                                      | <b>ASIA</b><br>Intersil (Taiwan) Ltd.                                                                                                        |            |

| P. O. Box 883, Mail Stop 53-204                 | Mercure Center                                                                             | Taiwan Limited                                                                                                                               |            |

6-20

100, Rue de la Fusee

TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05

1130 Brussels, Belgium

Melbourne, FL 32902

TEL: (321) 724-7000

FAX: (321) 724-7240

7F-6, No. 101 Fu Hsing North Road

Taipei, Taiwan

Republic of China TEL: (886) 2 2716 9310 FAX: (886) 2 2715 3029