# 250 MSPS Video Digital-to-Analog Converter

FUNCTIONAL BLOCK DIAGRAM

## AD9701

### FEATURES

250 MSPS Update Rate Low Glitch Impulse Complete Composite Functions Internal Voltage Reference Single -5.2 V Supply

### **APPLICATIONS**

Raster Scan Displays Color Graphics Automated Test Equipment TV Video Reconstruction

### **GENERAL DESCRIPTION**

The AD9701 is a high speed, 8-bit digital-to-analog converter with fully integrated composite video functions. High speed ECL input registers provide synchronous operation of data and control functions up to 250 MSPS.

The AD9701 incorporates onboard control functions including horizontal sync, blanking, reference white level and a 10% bright signal for highlighting. The setup level is also adjustable from 0 IRE units to 20 IRE units through the control pin. An internal voltage reference allows the AD9701 to operate as a stand-alone video reconstruction DAC.

The AD9701 is available as an industrial temperature range device,  $-25^{\circ}$ C to  $+85^{\circ}$ C, and as an extended temperature range

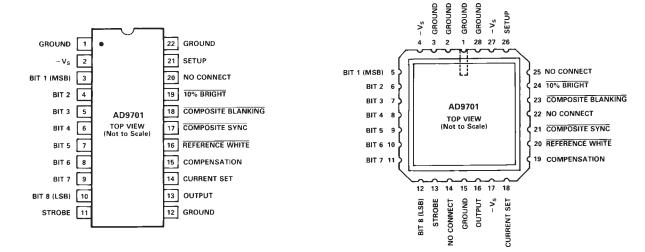

device,  $-55^{\circ}$ C to  $+125^{\circ}$ C. Both grades of the AD9701 are packaged in a 22-pin ceramic DIP with the extended temperature device also available in a 28-pin LCC package.

### **PIN CONFIGURATIONS**

### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 617/329-4700 World Wide Web Site: http://www.analog.com Fax: 617/326-8703 © Analog Devices, Inc., 1996

# AD9701-SPECIFICATIONS

### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Supply Voltage (-V <sub>S</sub> )7 V                                       |

|----------------------------------------------------------------------------|

| Digital Input Voltages (Including STROBE, SYNC,                            |

| BLANKING, 10% BRIGHT and REFERENCE                                         |

| WHITE)0 V to -V <sub>S</sub>                                               |

| Analog Output Current 37 mA                                                |

| Power Dissipation $(+25^{\circ}C \text{ Free Air})^2 \dots 780 \text{ mW}$ |

| Operating Temperature Range                |

|--------------------------------------------|

| AD9701BQ                                   |

| AD9701SQ/SE                                |

| Storage Temperature Range65°C to +150°C    |

| Junction Temperature                       |

| Lead Soldering Temperature (10 sec) +300°C |

## **ELECTRICAL CHARACTERISTICS** (Supply Voltages = -5.2 V; R<sub>L</sub> = $37.5 \Omega$ ; Setup = 0 V, unless otherwise noted)

|                                                  |              | Α       | D9701BQ   |          | AD      | 9701SQ/S | E        |            |

|--------------------------------------------------|--------------|---------|-----------|----------|---------|----------|----------|------------|

| Parameter                                        | Temp         | Min     | Тур       | Max      | Min     | Тур      | Max      | Units      |

| RESOLUTION                                       |              | 8       |           |          | 8       |          |          | Bits       |

| DC ACCURACY                                      |              |         |           |          |         |          |          |            |

| Differential Linearity                           | +25°C        |         | 0.25      | 0.5      |         | 0.25     | 0.5      | LSB        |

| 2 moronidai 2mounty                              | Full         |         | 0120      | 1.0      |         | 0120     | 1.0      | LSB        |

| Integral Linearity                               | +25°C        |         | 0.25      | 0.5      |         | 0.25     | 0.5      | LSB        |

|                                                  | Full         |         |           | 1.0      |         |          | 1.0      | LSB        |

| Monotonicity                                     | Full         |         | Guarante  |          |         |          |          |            |

| INITIAL OFFSET ERROR <sup>3</sup>                |              |         |           |          |         |          |          |            |

| Zero-Scale Offset Error <sup>4</sup>             | +25°C        |         | 0.05      | 0.9      |         | 0.05     | 0.9      | mV         |

|                                                  | Full         |         |           | 0.9      |         |          | 0.9      | mV         |

| Zero-Scale Offset Drift Coefficient              | Full         |         | 2         |          |         | 2        |          | μV/°C      |

| Full-Scale Drift Coefficient                     | Full         |         | 50        |          |         | 50       |          | μV/°C      |

| ANALOG OUTPUT                                    |              |         |           |          |         |          |          |            |

| Voltage Output <sup>5</sup>                      |              |         |           |          |         |          |          |            |

| 10% Bright <sup>6</sup>                          | Full         | -0.9    | 0         |          | -0.9    | 0        |          | mV         |

| Reference White                                  | Full         | -67.45  | -71       | -74.55   | -67.45  | -71      | -74.55   | mV         |

| Blanking (Setup = $0 \text{ IRE})^7$             | Full         | -698.55 | -708.5    | -718.45  | -698.55 | -708.5   | -718.45  | mV         |

| Sync (Setup = $0$ IRE) <sup>8</sup>              | Full         | -979.25 | -993.5    | -1007.75 | -979.25 | -993.5   | -1007.75 | mV         |

| Current Output <sup>5</sup>                      |              |         |           |          |         |          |          |            |

| 10% Bright <sup>6</sup>                          | Full         | -0.024  | 0         |          | -0.024  | 0        |          | mA         |

| Reference White                                  | Full         | -1.805  | -1.9      | -1.996   | -1.805  | -1.9     | -1.995   | mA         |

| Blanking (Setup = $0 \text{ IRE}$ ) <sup>7</sup> | Full         | -18.63  | -18.9     | -19.16   | -18.63  | -18.9    | -19.16   | mA         |

| Sync (Setup = $0$ IRE) <sup>8</sup>              | Full         | -26.11  | -26.5     | -26.87   | -26.11  | -26.5    | -26.87   | mA         |

| Output Compliance Range                          | Full         |         | -1.6; +0. | 1        | 0.40    | -1.6; +0 | .1       | V          |

| Output Resistance                                | +25°C        | 640     | 800       |          | 640     | 800      |          | Ω          |

| DYNAMIC PERFORMANCE                              |              |         |           |          |         |          |          |            |

| Update Rate                                      | +25°C        | 225     | 250       | _        | 225     | 250      | _        | MSPS       |

| Output Propagation Delay <sup>9</sup>            | +25°C        |         | 5         | 6        |         | 5        | 6        | ns         |

| Output Settling Time <sup>10</sup>               |              |         | _         |          |         | _        |          |            |

| Current                                          | +25°C        |         | 8         |          |         | 8        |          | ns         |

| Voltage                                          | +25°C        |         | 12        |          |         | 12       |          | ns         |

| Output Slew Rate <sup>11</sup>                   | +25°C        | 255     | 300       |          | 255     | 300      |          | V/µs       |

| Output Rise Time <sup>11</sup>                   | +25°C        |         | 1.7       | 2.0      |         | 1.7      | 2.0      | ns         |

| Output Fall Time <sup>11</sup>                   | +25°C        |         | 1.7       | 2.0      |         | 1.7      | 2.0      | ns         |

| Glitch Impulse                                   | +25°C        |         | 60        | 70       |         | 60       | 70       | pV-s       |

| SETUP CONTROL <sup>12</sup>                      |              |         |           |          |         |          |          |            |

| Setup Level (Grounded)                           | Full         |         | 0         |          |         | 0        |          | IRE        |

| Setup Level (Open)                               | Full         |         | 7.5       |          |         | 7.5      |          | IRE        |

| Setup Level                                      | En           |         | 10        |          |         | 10       |          |            |

| (Tied to $-5.2$ V with 1 k $\Omega$ )            | Full<br>Full |         | 10<br>20  |          |         | 10<br>20 |          | IRE<br>IRE |

| Setup Level (-5.2 V)                             | Full         |         | ۵0        |          |         | 20       |          | IKE        |

| DIGITAL INPUTS                                   |              |         |           |          |         |          |          |            |

| Logic "1" Voltage                                | Full         | -1.1    |           |          | -1.1    |          |          | V          |

| Logic "0" Voltage                                | Full         |         |           | -1.5     |         |          | -1.5     | V          |

| Logic "1" Current                                | Full         |         |           | 100      |         |          | 100      | μA         |

| Logic "0" Current                                | Full         |         |           | 15       |         |          | 15       | μA         |

| Input Capacitance                                | +25°C        |         | 4         | 5.5      |         | 4        | 5.5      | pF         |

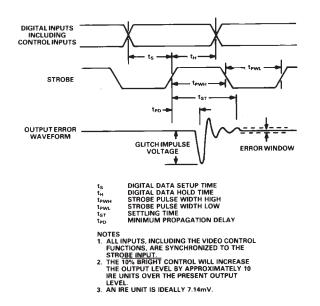

| Data Setup Time                                  | +25°C        | 0.1     |           |          | 0.1     |          |          | ns         |

| Data Hold Time                                   | +25°C        | 1.4     |           |          | 1.4     |          |          | ns         |

### AD9701

|                                            |       | AD9701BQ |     |     | AD9701SQ/SE |     |     |       |  |

|--------------------------------------------|-------|----------|-----|-----|-------------|-----|-----|-------|--|

| Parameter                                  | Temp  | Min      | Тур | Max | Min         | Тур | Max | Units |  |

| POWER SUPPLY <sup>13</sup>                 |       |          |     |     |             |     |     |       |  |

| Supply Current (–5.2 V)                    | +25°C |          | 140 | 160 |             | 140 | 160 | mA    |  |

|                                            | Full  |          |     | 160 |             |     | 160 | mA    |  |

| Nominal Power Dissipation                  | +25°C |          | 728 |     |             | 728 |     | mW    |  |

| Power Supply Rejection Ratio <sup>14</sup> | Full  |          | 3   | 6   |             | 3   | 6   | mV/V  |  |

NOTES

<sup>1</sup>Absolute maximum ratings are limiting values to be applied individually, and beyond which serviceability of the circuit may be impaired. Functional operability under any of these conditions is not necessarily implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>2</sup>Typical thermal impedance . . .

22-Pin Ceramic  $\theta_{JA} = 64^{\circ}C/W; \theta_{JC} = 16^{\circ}C/W$ 28-Pin Ceramic LCC  $\theta_{JA} = 70^{\circ}C/W; \theta_{JC} = 21^{\circ}C/W$ <sup>3</sup>SYNC, BLANKING, and REFERENCE WHITE are inactive (Logic "1"). I<sub>SET</sub>  $\approx 1.26$  V/R<sub>SET</sub>.

<sup>4</sup>All bits at logic HIGH.

<sup>5</sup>All values are relative to full-scale output after being normalized to nominal value. Typical variation in full-scale output from device to device can reach ±10%, for a fixed R<sub>SET</sub> resistor.

<sup>6</sup>The effect of 10% BRIGHT algebraically adds to the output waveform. <sup>7</sup>The output level with BLANKING active (Logic "0") is determined by the setup control level.

<sup>8</sup>In normal operation, the BLANKING input is activated (Logic "0") prior to or in conjunction with the SYNC input. The effect of the SYNC output is relative to the setup level.

<sup>9</sup>Measured from edge of STROBE to 50% transition point of the output signal. <sup>10</sup>Measured with full-scale change in output level, from the 10% transition level to within  $\pm 0.2\%$  of the final output value.

<sup>11</sup>Measured from 10% to 90% transition point for full-scale step output.

<sup>12</sup>An IRE unit is 1% of the Grey Scale (GS range) with a 0 IRE setup level.

$^{13}$  Supply Voltage should remain stable within  $\pm 5\%$  for normal operation.

$^{14}$  Measured at ±5% of –V<sub>S</sub>.

Specifications subject to change without notice.

### DIGITAL INPUTS VS. ANALOG OUTPUT

| Bit<br>1 | Bit<br>2 | Bit<br>3 | Bit<br>4 | Bit<br>5 | Bit<br>6 | Bit<br>7 | Bit<br>8 | 10%<br>Bright | Ref.<br>White | Blanking | Comp.<br>Sync | Analog<br>Output (mV) |

|----------|----------|----------|----------|----------|----------|----------|----------|---------------|---------------|----------|---------------|-----------------------|

| 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 0             | 1             | 1        | 1             | 0                     |

| 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1             | 1             | 1        | 1             | -71                   |

| 1        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0             | 1             | 1        | 1             | -320                  |

| 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0             | 1             | 1        | 1             | -637.5                |

| 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 1             | 1             | 1        | 1             | -708.5                |

| X        | Х        | X        | Х        | Х        | X        | X        | Х        | 0             | 0             | 1        | 1             | 0                     |

| Х        | X        | X        | X        | X        | X        | X        | X        | 1             | 0             | 1        | 1             | -71                   |

| Х        | X        | X        | X        | X        | X        | X        | X        | 0             | 1             | 0        | 1             | $-637.50^{1}$         |

| Х        | X        | X        | X        | X        | X        | X        | X        | 0             | 1             | 0        | 1             | $-690.75^{2}$         |

| Х        | X        | X        | X        | X        | X        | X        | X        | 0             | 1             | 0        | 1             | $-708.50^{3}$         |

| Х        | X        | X        | X        | X        | X        | X        | X        | 0             | 1             | 0        | 1             | $-779.50^{4}$         |

| X        | Х        | Х        | Х        | Х        | Х        | X        | Х        | 0             | 1             | 0        | 0             | $-922.50^{1}$         |

| Х        | X        | X        | X        | X        | X        | X        | X        | 0             | 1             | 0        | 0             | $-975.75^{2}$         |

| Х        | X        | X        | X        | X        | X        | X        | X        | 0             | 1             | 0        | 0             | $-993.50^{3}$         |

| Х        | X        | X        | X        | X        | X        | X        | X        | 0             | 1             | 0        | 0             | $-1064.50^4$          |

| X        | Х        | Х        | Х        | Х        | Х        | Х        | Х        | 1             | 1             | 0        | 0             | $-993.50^{1}$         |

| Х        | X        | X        | X        | X        | X        | X        | X        | 1             | 1             | 0        | 0             | $-1046.75^{2}$        |

| Х        | X        | X        | X        | X        | X        | X        | X        | 1             | 1             | 0        | 0             | $-1064.50^{3}$        |

| Х        | X        | X        | X        | X        | X        | X        | X        | 1             | 1             | 0        | 0             | $-1135.50^4$          |

NOTES

<sup>1</sup>Setup (Pin 21) grounded (0 IRE units).

<sup>2</sup>Setup (Pin 21) open (7.5 IRE units). <sup>3</sup>Setup (Pin 21) to -5.2 V through 1 k (0 IRE units).

<sup>4</sup>Setup (Pin 21) to -5.2 V (20 IRE units).

### **ORDERING GUIDE**

| Device   | Temperature<br>Range | Description                        | Package<br>Option* |

|----------|----------------------|------------------------------------|--------------------|

| AD9701BQ | -25°C to +85°C       | 22-Pin DIP, Industrial Temperature | Q-22               |

| AD9701SE | -55°C to +125°C      | 28-Pin LCC, Extended Temperature   | E-28A              |

| AD9701SQ | -55°C to +125°C      | 22-Pin DIP, Extended Temperature   | Q-22               |

\*E = Leadless Ceramic Chip Carrier; Q = Cerdip.

## AD9701

### FUNCTIONAL DESCRIPTION

| Pin Name           | Description                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| GROUND             | One of three ground returns. All grounds should be connected together near the AD9701.                                                                                                                                                                                                           |  |  |  |  |  |  |

| -V <sub>S</sub>    | Negative supply pin, nominally –5.2 V.                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| BIT 1 (MSB)        | One of eight digital input bits. BIT 1 (MSB) is the most-significant-bit of the digital input word.                                                                                                                                                                                              |  |  |  |  |  |  |

| BIT 2-BIT 7        | One of eight digital input bits.                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| BIT 8 (LSB)        | One of eight digital input bits. BIT 8 (LSB) is the least-significant-bit of the digital input word.                                                                                                                                                                                             |  |  |  |  |  |  |

| STROBE             | Data and control register strobe input. STROBE is leading edge triggered.                                                                                                                                                                                                                        |  |  |  |  |  |  |

| GROUND             | One of three ground returns. All grounds should be connected together near the AD9701.                                                                                                                                                                                                           |  |  |  |  |  |  |

| SETUP              | The SETUP input determines the position of the blanking level relative to the "reference black" level (all data bits at logic "0"). The setup level is adjustable from 0 IRE units to 20 IRE units below the reference black level (an IRE unit is 1% of the "grey scale" range).                |  |  |  |  |  |  |

|                    | SETUP LEVEL CONFIGURATION (PIN 21)                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|                    | 0 IRE Units Ground                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|                    | 7.5 IRE Units Open                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|                    | 10 IRE Units Connection to $-5.2$ V through 1 k $\Omega$                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|                    | 20 IRE Units Connection to -5.2 V                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 10% BRIGHT         | $\overline{10\%}$ BRIGHT adds an additional current to the output level, equal to roughly 10% of the "grey scale" range. The $\overline{10\%}$ BRIGHT is active logic LOW and operates independently of all other inputs.                                                                        |  |  |  |  |  |  |

| COMPOSITE BLANKING | The <b>COMPOSITE BLANKING</b> input, active logic LOW, forces output to the blanking level set with the SETUP input.                                                                                                                                                                             |  |  |  |  |  |  |

| COMPOSITE SYNC     | The COMPOSITE SYNC input, active LOW, creates a negative going horizontal synchronization pulse relative to the blanking level. Under normal operating conditions, the COMPOSITE BLANKING signal should precede and extend past the COMPOSITE SYNC signal. See SETUP for additional information. |  |  |  |  |  |  |

| REFERENCE WHITE    | The <b>REFERENCE WHITE</b> input, active LOW, overrides the data inputs and forces the output to the maximum "grey scale" level.                                                                                                                                                                 |  |  |  |  |  |  |

| COMPENSATION       | The COMPENSATION input insures adequate gain stability for the internal reference amplifier.<br>Under normal operating conditions, the COMPENSATION input is decoupled to ground through a 0.1 $\mu$ F capacitor.                                                                                |  |  |  |  |  |  |

| CURRENT SET        | The CURRENT SET input determines the full-scale or "grey scale" range. The effects of the video control functions are in addition to the "grey scale" range. (168 $\Omega \le R_{SET} \le 600 \Omega$ ).<br>$I_{OUTmax} \approx 4 I_{SET} = 4(1.26 \text{ V/R}_{SET})$                           |  |  |  |  |  |  |

| OUTPUT             | Analog output.                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| GROUND             | One of three ground returns. All grounds should be connected together near the AD9701.                                                                                                                                                                                                           |  |  |  |  |  |  |

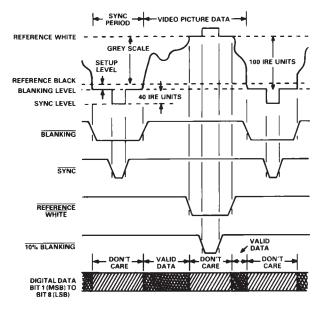

### SYSTEM TIMING DIAGRAMS

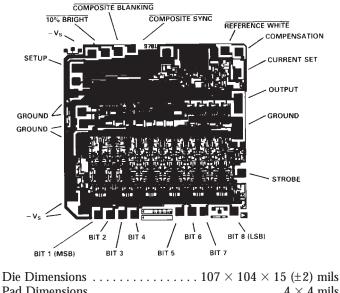

### DIE LAYOUT AND MECHANICAL INFORMATION

| Pad Dimensions                                     |

|----------------------------------------------------|

| Metalization Aluminum                              |

| Backing None                                       |

| Substrate PotentialV <sub>S</sub>                  |

| Passivation Oxynitride                             |

| Die Attach                                         |

| Bond Wire 1.25 mil Aluminum; Ultrasonic Bonding or |

| 1 mil Gold; Gold Ball Bonding                      |

### **APPLICATIONS INFORMATION**

Raster scan video displays image data on a line by line basis, with timing and control signals inserted between the lines. The control signals include the horizontal synchronization pulses, which are used to align the display circuitry at the beginning of each line. After the complete video image is displayed on the monitor, the process begins again with the next image. The vertical reset pulse(s) that initiate this timing sequence are located between each video image.

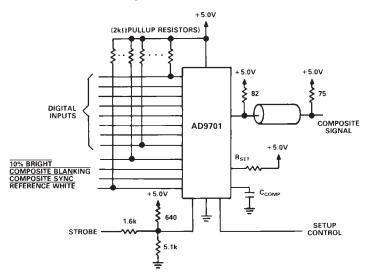

Raster Graphics Configuration for TTL Systems

The image data is distinguished from the timing information by its location relative to the blanking level. The blanking reference level is at the blackest extreme of the image data and all timing signals are designed to fall below the blanking level so as not to be seen on the monitor. The actual image data is located above the blanking level and it may be further separated from the timing signal by the setup level. The setup level is simply a buffer zone between the timing and image data.

Generation of the timing signals for the AD9701 is controlled by the COMPOSITE BLANKING and the COMPOSITE SYNC inputs. In normal operation, the output level of the AD9701 is forced to the blanking level (black) with the COM-POSITE BLANKING control so that when the synchronization occurs, it will not interfere (be seen) with the monitor image. The COMPOSITE SYNC control forces the output level below the blanking level, generating the synchronization pulse.

The "grey scale" is the image intensity range located above the blanking level by the amount of the setup level. The setup level is "reference black," the darkest displayable picture intensity. The top of the "grey scale" is "reference white" or the brightest picture intensity. As an 8-bit device, the AD9701 divides the "gray scale" into 256 individual levels.

Normal raster scan waveforms divide the region between the blanking level and reference white into 100 IRE units (International Radio Engineers). The setup level can range from 0 to 20 IRE units but typically is around 10 IRE units, and the synchronization pulse level typically falls 40 IRE units below the blanking level. For the AD9701, the reference white level is 10 IRE units below the full-scale output range (0 mA<sub>OUT</sub>).

In terms of priority, the **REFERENCE WHITE** control overrides the data inputs, but both **COMPOSITE SYNC** and **COMPOSITE BLANKING** override the data inputs and the **REFERENCE WHITE** control. A fourth control is active at all times, 10% **BRIGHT**, which adds approximately 10 IRE units to the output level no matter what the input state of the AD9701. The 10% **BRIGHT** control is primarily used to highlight areas of the video image.

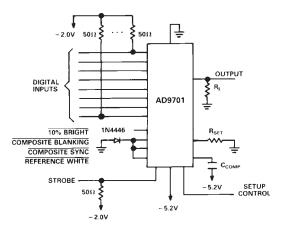

As with any high-speed device, the AD9701 requires a substantial low impedance ground plane and high quality ground connections to achieve the best performance. Performance can also be improved with adequate power supply decoupling near the supply pins of the AD9701. In ECL mode, the output of the AD9701 is designed to drive 75  $\Omega$  cable directly, with 75  $\Omega$  terminations to ground at both ends of the cable. For TTL configurations, the output should be terminated to +5.0 V through an 82  $\Omega$  resistor (see circuit below).

Standard Reconstruction Configuration

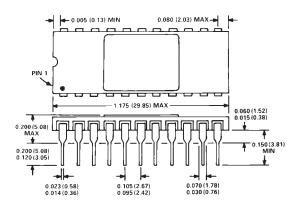

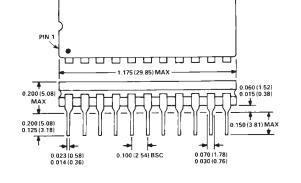

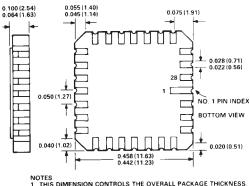

### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

### 22-Pin Side-Brazed DIP

22-Pin Ceramic DIP

<u>, na a a a a a a a</u>

0.098 (2.49) MAX 🕳

- 0.005 (0.13) MIN

28-Pin LCC

NOTES 1. THIS DIMENSION CONTROLS THE OVERALL PACKAGE THICKNESS. 2. APPLIES TO ALL FOUR SIDES. 3. ALL TERMINALS ARE GOLD PLATED.