# TOSHIBA

## TC35821F 155 Mbps SONET/SDH ATM Framer

#### **Features**

- SONET STS-3c and STS-1/SDH STM-1

- 155.52Mbps PECL Serial Network Interface

- On-chip Clock Recovery

- Transmit Clock Synthesis

- 19.44MHz to 155.52 MHz

- UTOPIA Level-1 & 2 Interface

- 144-pin PQFP

- 0.6 micron CMOS, 5 volts

### Description

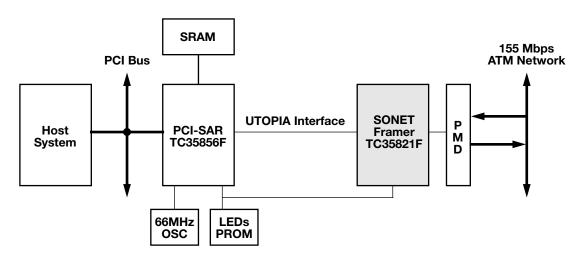

The TC35821F is a single-chip 155.52 Megabits per second (Mbps) framer chip for asynchronous transfer mode (ATM) physical layer application. It can be used for network interface card (NIC), switch and router applications.

The TC35821F offers cost-effective physical layer controller solutions. In NIC applications, an ATM framer chip used in conjunction with a transceiver on one side and a segmentation and reassembly (SAR) chip on the other provides a complete ATM solution. The interface to the SAR device is via

the industry standard UTOPIA (Universal Test and Operations Physical Layer Interface for ATM) level one or two interface. Toshiba's TC35856F 155Mbps PCI-SAR and TC35853F 155Mbps SAR are examples of SARs which can be used with the TC35821F.

The TC35821F supports SONET standards STS-1 and STS-3C. It contains a 155.52 megahertz (MHz) pseudo emitter coupled logic serial line interface to the transceiver chips. The device offers programmable section overhead (SOH)/ path overhead (POH) handling and operates internally at 19.44MHz/6.48MHz with a maximum 40 MHz cell-interface operation. The TC35821F is designed in 0.6 micron CMOS technology and operates on a single +5.0 volt power supply.

The TC35821F 155Mbps framer contains clock recovery circuits, byte alignment and frame synchronization, frame descrambling, frame overhead analysis, ATM cell synchronization, ATM cell header error correction and ATM cell payload descramble functions. Its transmit functions include ATM cell payload scramble, ATM header error correction (HEC) generation, frame overhead generation, frame assembly and frame scrambling. In addition, access to the chip registers from the central processing unit is available for configuration, status, diagnostics error counter and cell counter.

Figure 1. 155 Mbps System Block Diagram (Including SAR and Framer)

Figure 2. LQFP144-P-2020-0.50A [144-Pin LQFD (Thin Quad Flat Package – 1.4mm)] Unit: mm

- 1. This techynical data may be controlled under U.S. Export Administration Regulations and may be subject to the approval of the U.S. Department of Commerce prior to export. Any export or reexport, directly or indirectly, in contravention of the U.S. Export Administration Regulations is strictly prohibited.

- 2. The information in this document has been carefully checked and is believed to be reliable; however, no responsibility can be assumed for inaccuracies that may not have been caught. All information in this document is subject to change without prior notice. Furthermore, Toshiba cannot assume responsibility for the use of any license under the patent rights of Toshiba or any third parties.

#### TOSHIBA AMERICA ELECTRONIC COMPONENTS, INC.

#### **Regional Sales Offices**

| Irvine, CA          | Atlanta, GA         | Boston, MA          | Portland, OR        |

|---------------------|---------------------|---------------------|---------------------|

| TEL: (714) 453-0224 | TEL: (770) 931-3363 | TEL: (617) 224-0074 | TEL: (503) 629-0818 |

| FAX: (714) 453-0125 | FAX: (770) 931-7602 | FAX: (617) 224-1096 | FAX: (503) 629-0827 |

| San Jose, CA        | Chicago, IL         | Edison, NJ          | Dallas, TX          |

| TEL: (408) 456-8900 | TEL: (708) 945-1500 | TEL: (908) 248-8070 | TEL: (972) 480-0470 |

| FAX: (408) 456-8910 | FAX: (708) 945-1044 | FAX: (908) 248-8030 | FAX: (972) 235-4114 |