# ST18952

## DIGITAL SIGNAL PROCESSOR (DSP) CHIP

PRELIMINARY DATA

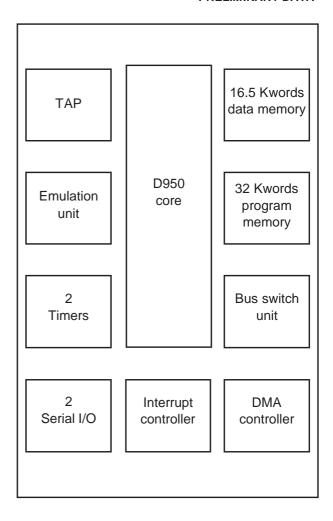

#### ■ Programmable D950 Core

- Data calculation unit

- Address calculation unit

- Program control unit

- Fast and flexible buses

- 66MIPS 15 ns instruction cycle time

- 16.5 Kwords data memory (RAM)

- **32 Kwords program memory (RA42 1714 01)**

- Interrupt controller

- DMA controller

- Serial input/output

- Timer

- Bus switch unit

- Emulation unit

- JTAG IEEE 1149.1 test access port

12 January 98 42 1714 01

# —— Table of Contents ——

| Intro | duction                                                                                                                                             | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | ·                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.1   |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Men   | · ·                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | •                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| _     |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| _     |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| _     | ·                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| _     | •                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | ·                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | G .                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | ·                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| _     | •                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | ·                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| -     |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | ·                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | ·                                                                                                                                                   | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | ·                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                                                                                                                                     | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | Pin I Fund D95 4.1 Mem 5.1 5.2 Bus 6.1 6.2 DM/ 7.1 7.2 Inter 8.1 Time 9.1 SIO 10.1 Exte Syst 12.1 12.2 JTA Elect 15.1 15.2 15.3 Y SF 16.1 16.2 16.3 | Memory 5.1 Internal memory resource 5.2 Direct bus extension Bus Switch Unit 6.1 BSU operation 6.2 BSU control registers DMA Controller 7.1 DMA operation 7.2 DMA registers Interrupt Controller 8.1 Interrupt controller registers Timers 9.1 Timer registers SIO 10.1 SIO registers External Coprocessor System Control 12.1 System registers 12.2 Clocks JTAG IEEE 1149.1 test access port Emulation Unit Electrical Specifications 15.1 DC Absolute maximum ratings 15.2 DC Electrical characteristics Y SPACE Memory Mapping 16.1 Memory map 16.2 Serial input/output registers 16.3 Timer registers |

# Table of Contents

|    | 16.5 System control registers        | 58 |

|----|--------------------------------------|----|

|    | 16.6 DMA controller registers        | 59 |

|    | 16.7 Interrupt controller registers  | 59 |

|    | 16.8 Emulation unit registers        | 60 |

|    | 16.9 D950Core control registers      | 60 |

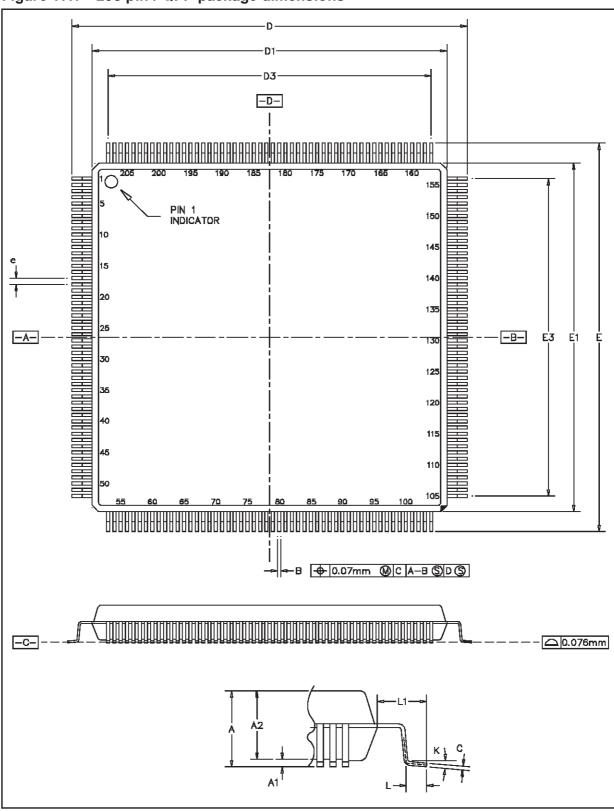

| 17 | ST18952 Package Specifications       | 61 |

|    | 17.1 208 pin PQFP pinout             | 61 |

|    | 17.2 208 pin PQFP package dimensions | 62 |

| 18 | Device ID                            | 64 |

| 19 | Ordering Information                 | 64 |

| 20 | Revision History                     | 64 |

## 1 Introduction

The ST18952 chip includes the SGS-Thomson D950 16-bit fixed point digital signal processor core, 16.5 Kwords of data memory, 32 Kwords of program memory, and the following on-chip peripherals:

- Interrupt controller (ITC)

- DMA controller (DMA)

- Bus switch unit (BSU)

- Synchronous input/output (SIO)

- Timer (TIM)

- Emulation unit (EMU)

- Tap controller (TAP)

It also includes an oscillator and a PLL for generation of the D950Core clock.

The ST18952 is used on the D950 Emulation Card (called the D952 module) developed by SGS-Thomson.

It can also be used for application development by customers.

Custom development is eased by providing direct access to the D950 instruction and data buses to allow simultaneous access to external memories or peripherals (with wait-states).

For full details of the D950Core refer to the D950Core datasheet (document number 42-1709).

# 2 Pin Description

The following tables detail the ST18952 pin set. There is one table for each group of pins. The tables detail the pin name, type and a short description of the pin function.

Signal names have an overbar if they are active low, otherwise they are active high.

Table 2.1 Direct I bus extension (35 pins)

| Pin name | Туре | Description                               |

|----------|------|-------------------------------------------|

| IDE0-15  | I/O  | Instruction data extension bus.           |

| IAE0-15  | 0    | Instruction address extension bus.        |

| ĪRDĒ     | 0    | I-extension bus read strobe. Active low.  |

| ĪWRE     | 0    | I-extension bus write strobe. Active low. |

| ĪBSE     | 0    | I-extension bus strobe. Active low.       |

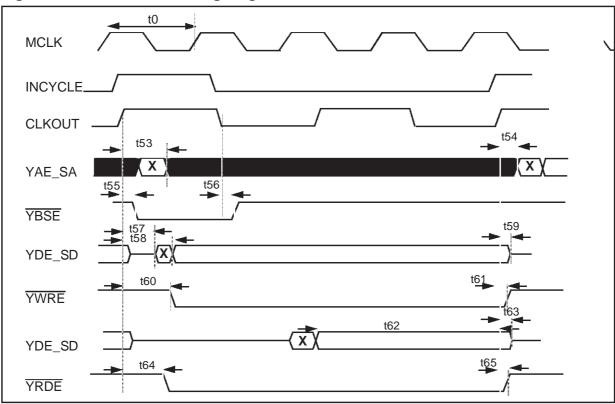

Table 2.2 Direct Y bus extension (35 pins)

| Pin name | Туре | Description                               |

|----------|------|-------------------------------------------|

| YDE0-15  | I/O  | Y data extension bus.                     |

| YAE0-15  | 0    | Y address extension bus.                  |

| YRDE     | 0    | Y-extension bus read strobe. Active low.  |

| YWRE     | 0    | Y-extension bus write strobe. Active low. |

| YBSE     | 0    | Y-extension bus strobe. Active low.       |

Table 2.3 Direct X bus extension / bus extension through bus switch unit (39 pins)

| Pin name   | Туре | Description                                                                   |

|------------|------|-------------------------------------------------------------------------------|

| ED_XDE0-15 | I/O  | Multiplexed input/output. Bus switch unit extension data bus or X data exten- |

|            |      | sion bus.                                                                     |

| EA_XAE0-15 | 0    | Multiplexed output. Bus switch unit extension address bus or X address ex-    |

|            |      | tension bus.                                                                  |

| EIRD       | 0    | BSU EIRD output                                                               |

| EIWR       | 0    | BSU EIWR output                                                               |

| XBSE       | 0    | X extension bus data strobe                                                   |

| EYRD       | 0    | BSU EYRD output                                                               |

| EYWR       | 0    | BSU EYWR output                                                               |

| XRDE_EXRD  | 0    | Multiplexed output.                                                           |

|            |      | X-extension bus read strobe (XRDE) or BSU EXRD output.                        |

| XWRE_EXWR  | 0    | Multiplexed output.                                                           |

|            |      | X-extension bus write strobe (XWRE) or BSU EXWR output.                       |

Table 2.4 General purpose parallel port / Interrupt requests (8 pins)

| Pin name  | Туре | Description                                                                       |

|-----------|------|-----------------------------------------------------------------------------------|

| P_ITRQ0-7 | I/O  | Multiplexed input/output. Parallel port I/O or external interrupt request (ITRQ). |

## Table 2.5 Clocks (6 pins)

| Pin name | Type | Description                                                                                                                                                                                                                                       |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTAL    | I    | Oscillator input.                                                                                                                                                                                                                                 |

| XTAL     | 0    | Oscillator output. Nominal oscillator frequency is 27 MHz.                                                                                                                                                                                        |

| MCLK     | I    | Master clock input (use of external clock generator).                                                                                                                                                                                             |

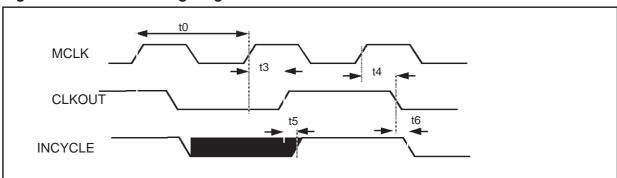

| CLK_MODE | I    | Clock mode select input.  When low the oscillator and internal PLL are enabled. The 950 receives its Master clock from the PLL at 5 times the oscillator frequency.  When high the PLL is disabled. The D950 receives its master clock from MCLK. |

| INCYCLE  | 0    | Instruction cycle. Asserted high for 1 CLKOUT cycle at the beginning of instruction cycle.                                                                                                                                                        |

| CLKOUT   | 0    | Output clock (at input clock/2 frequency).                                                                                                                                                                                                        |

## Table 2.6 Bus control (3 pins)

| Pin name | Туре | Description                                                                                                                                                                                                                                                                                      |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DTACK    | I    | Data transfer acknowledge input. Active low. It is combined in a OR gate with BSU DTACK output in order to generate the DTACK signal for the D950Core. It controls extension of bus cycles by insertion of wait-states when using external memory either through Bus-switch or direct extension. |

| HOLD     | I    | External Bus Hold request input. Active low.                                                                                                                                                                                                                                                     |

| HOLDACK  | 0    | Hold acknowledge output. Active low.                                                                                                                                                                                                                                                             |

6/66

Table 2.7 D950Core control (10 pins)

| Pin name  | Туре | Description                                                                |

|-----------|------|----------------------------------------------------------------------------|

| RESET     | I    | Reset input. Active low.                                                   |

|           |      | Initializes the 950-Core to the RESET state.                               |

| RESET_OUT | 0    | Reset output (system reset). Active low.                                   |

| <u>ГР</u> | I    | Low power input. Active low.                                               |

| LPACK     | 0    | Low power acknowledge. Active low.                                         |

| MODE      | I    | Mode selection for Reset.                                                  |

|           |      | 0: forces reset address to 0x0000                                          |

|           |      | 1: forces reset address to 0xFC00                                          |

| IRD_WR    | 0    | Program memory read/write indicator.                                       |

| VCI       | 0    | Valid coprocessor instruction output.                                      |

|           |      | Asserted low during the instruction cycle preceding a coprocessor instruc- |

|           |      | tion to enable operation of an external coprocessor.                       |

| STACKX    | 0    | X stack read/write instruction flag.                                       |

| STACKY    | 0    | Y stack read/write instruction flag.                                       |

| IDT_EN    | I    | I-bus direct transfer enable (to BSU peripheral). Active low.              |

Table 2.8 Emulation unit (7 pins)

| Pin name      | Туре | Description                                                                  |

|---------------|------|------------------------------------------------------------------------------|

| ERQ           | I    | Emulator Halt Request. Active low.                                           |

|               |      | Halts program execution and enters emulation mode.                           |

| IDLE          | 0    | Output flag asserted high when the processor is halted due to an emulation   |

|               |      | halt request or a valid breakpoint condition. Asserted low when the proces-  |

|               |      | sor is not Halted or during execution of an instruction under control of the |

|               |      | emulator.                                                                    |

| HALTACK       | 0    | Halt acknowledge. Active high.                                               |

|               |      | Asserted high when the processor is halted from an Emulator Halt request     |

|               |      | or when a valid Breakpoint condition is met.                                 |

| SNAP          | 0    | Snapshot. Active high.                                                       |

|               |      | Asserted high when executing an instruction if Snapshot mode is enabled.     |

| AXEBP         | I    | Enable breakpoint on X address bus when high.                                |

| AYEBP         | Ī    | Enable breakpoint on Y address bus when high.                                |

| AIEBP_SCAN_EN | Ī    | Enable breakpoint on I address bus when high.                                |

Table 2.9 JTAG IEEE 1149.1 test access port (5 pins)

| Pin name | Туре | Description                                                   |

|----------|------|---------------------------------------------------------------|

| TDI      | I    | Test data input.                                              |

| TCK      | I    | Test clock.                                                   |

| TMS      | I    | Test mode select.                                             |

| TDO      | 0    | Test data output.                                             |

| TRST     | I    | Test logic reset (also used for Emulator module). Active low. |

Table 2.10 DMA controller / Serial input/output (8 pins)

| Pin name    | Туре | Description                                  |

|-------------|------|----------------------------------------------|

| DMARQ0/SRD0 | I    | DMA request 0 or SIO0 Receive data           |

| DMARQ1/SCK0 | I/O  | DMA request 1 or SIO0 Data clock             |

| DMARQ2/SRD1 | I    | DMA request 2 or SIO1 Receive data           |

| DMARQ3/SCK1 | I/O  | DMA request 3 or SIO1 Data clock             |

| DMACK0/STD0 | 0    | DMA acknowledge 0 or SIO0 Transmit data      |

| DMACK1/SFS0 | I/O  | DMA acknowledge 1 or SIO0 Frame synchronizer |

| DMACK2/STD1 | 0    | DMA acknowledge 2 or SIO1 Transmit data      |

| DMACK3/SFS1 | I/O  | DMA acknowledge 3 or SIO1 Frame synchronizer |

## 3 Functional Overview

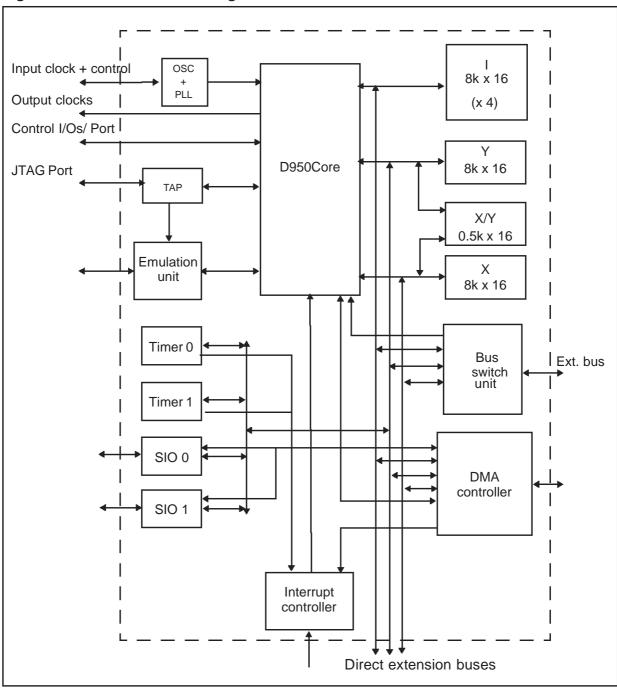

A block diagram of the ST18952 is shown below. The modules that comprise the ST18952 are outlined in this section and described in detail in the following sections.

Figure 3.1 ST18952 block diagram

#### D950Core

The D950Core is a general purpose programmable 16-bit fixed point Digital Signal Processor Core. The main blocks of the D950Core include an arithmetic data calculation unit, a program control unit and an address calculation unit, able to manage up to 64k (program) and 128k (data) x 16-bit memory spaces.

#### **Memory**

One 32 Kword and two 8 Kword single port memories are included on-chip:

- 32 Kword instruction memory on I space

- 8 Kword X-Data memory on X space

- 8 Kword Y-Data memory on Y space

One 512 word dual port memory is shared on X and Y spaces.

Memory can be extended off-chip for all three spaces in two ways:

- Directly Accesses to program and data memories can be performed simultaneously. Insertion of wait-states is necessary in case of nominal frequency work.

- 2: Through the bus switch unit Accesses to the different external spaces are multiplexed and wait-states are added.

### Bus switch unit

The bus switch unit (BSU) is a bi-directional switcher which switches the 3 internal buses (I, X and Y) to the external (E) bus.

#### **DMA** controller

The DMA controller manages data transfer between memories and external peripherals. There are four independent DMA channels. Transfers can occur on X/Y/I spaces (simultaneous transfers on X and Y spaces).

#### Interrupt controller

The interrupt controller (ITC) can manage up to eight external interrupts. Each source can be individually activated and programmed as edge or level triggered. A 'pending interrupt' flag displays the source waiting for service (this flag is writable to allow a software interrupt capability). The priority of interrupts is programmable.

#### **Timers**

There are two timer (TIM) units on the ST18952. The timers enable interrupts to be generated after predefined periods of time.

#### SIO

There are two synchronous serial input/output (SIO) ports enable a link to serial devices such as codecs and to other processors.

#### **Oscillator and PLL**

A 27 MHz crystal can be used with the on-chip oscillator and PLL to provide the D950Core clock input. The PLL module multiplies the oscillator frequency by a factor of 10 and generates a 270 MHz signal. A programmable divider is connected to the PLL output to generate the D950 clock input. The division range is 2 to 256.

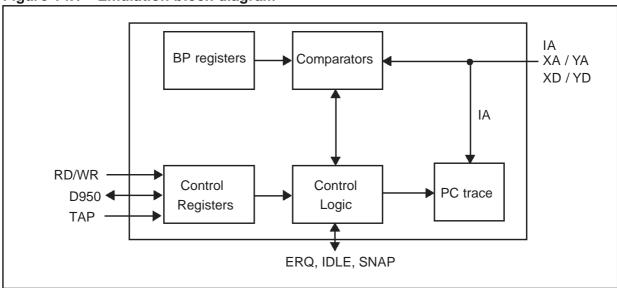

### Emulation unit and JTAG IEEE 1149.1 test access port

The emulation unit (EMU) performs functions dedicated to emulation and test through the external IEEE 1149.1 JTAG interface.

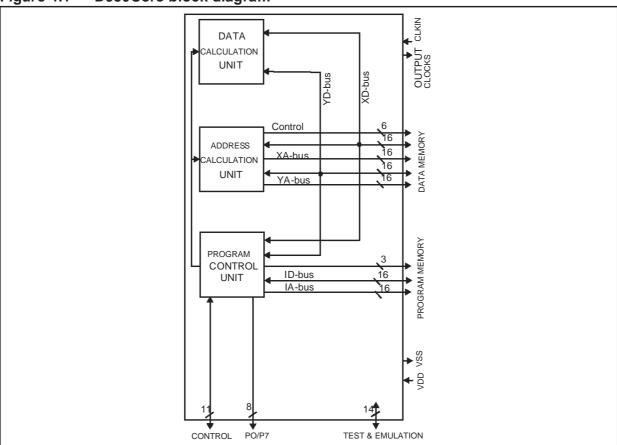

## 4 **D950Core**

The D950Core is composed of three main units.

- Data Calculation Unit (DCU)

- Address Calculation Unit (ACU)

- Program Control Unit (PCU)

For full details of the D950 DSP core refer to the D950Core datasheet (*document number 42-1709*).

These units are organized in an HARVARD architecture around three bidirectional 16-bit buses, two for data and one for instruction. Each of these buses is dedicated to an unidirectional 16-bit address bus (XA/YA/IA).

An 8-bit general purpose parallel port (P0-P7) can be configured (input or output). A test condition is attached to each bit to test external events.

The D950Core is controlled through interface pins related to interrupt, low-power mode, reset and miscellaneous functions.

Figure 4.1 D950Core block diagram

Data buses (XD/YD and XA/YA) are provided externally. Data memories (RAM, ROM) and peripherals registers are mapped in these address spaces.

Instruction bus (ID/IA) gives access to program memory (RAM, ROM). Each bus has its own control interface.

Table 4.1 Data/instruction bus and corresponding address bus.

|    | Data/instruction bus | 5      | Corresponding address bus |                |        |  |  |  |

|----|----------------------|--------|---------------------------|----------------|--------|--|--|--|

| XD | Bidirectional        | 16-bit | XA                        | Unidirectional | 16-bit |  |  |  |

| YD | Bidirectional        | 16-bit | YA                        | Unidirectional | 16-bit |  |  |  |

| ID | Bidirectional        | 16-bit | IA                        | Unidirectional | 16-bit |  |  |  |

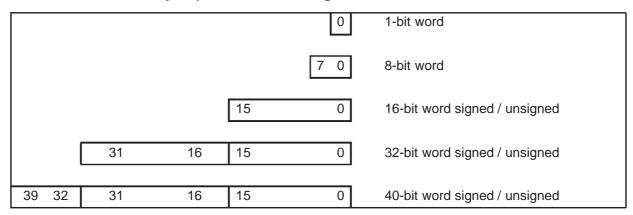

Depending on the calculation mode, the D950Core DCU computes operands which can be considered as 16 or 32-bit, signed or unsigned. It includes a 16 x 16-bit parallel multiplier able to implement MAC-based functions in one cycle per MAC. A 40-bit arithmetic and logic unit, including an 8-bit extension for arithmetic operations, implements a wide range of arithmetic and logic functions. A 40-bit barrel shifter unit and a bit manipulation unit are included.

The tables below illustrate the different types of word length and word format available for manipulation.

Table 4.2 Summary of possible word lengths and formats

| For        | mat      | Minimum | Maximum       |

|------------|----------|---------|---------------|

| fractional | signed   | - 1     | + 0.999969481 |

|            | unsigned | 0       | + 0.99996948  |

| integer    | signed   | - 32768 | + 32767       |

|            | unsigned | 0       | + 65535       |

# 4.1 D950Core registers

| Register | Function                                                                     |

|----------|------------------------------------------------------------------------------|

| вх       | Modulo base address for X-memory space                                       |

| MX       | Modulo maximum address for X-memory space                                    |

| BY       | Modulo base address for Y-memory space                                       |

| MY       | Modulo maximum address for Y-memory space                                    |

| POR      | Port Output Register - 8LSB are significant, 8MSB are undefined when reading |

| PIR      | Port Input Register                                                          |

| PCDR     | Port Control Direction Register                                              |

| PCSR     | Port Control Sensitivity Register                                            |

### **PCDR**

The Port Control Direction register defines the data direction of each port pin. After reset, PCDR default value is 0 (Port pins are configured as inputs)

|   | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---|----|----|----|----|----|----|---|---|-----|-----|-----|-----|-----|-----|-----|-----|

| ſ | -  | -  | -  | -  | -  | -  | - | - | P7D | P6D | P5D | P4D | P3D | P2D | P1D | P0D |

| Bit         | Function                                      |  |  |  |  |  |  |

|-------------|-----------------------------------------------|--|--|--|--|--|--|

| PiD         | Port pin direction                            |  |  |  |  |  |  |

|             | 0: Input port pin (def.)                      |  |  |  |  |  |  |

|             | 1: Output port pin                            |  |  |  |  |  |  |

| Bits 8 - 15 | RESERVED (read: undefined, write: don't care) |  |  |  |  |  |  |

### **PCSR**

The Port Control Sensitivity register defines sensitivity of each port pin. After reset, PCSR default value is 0 (Port pins are configured as level-sensitive).

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|----|----|----|----|----|----|---|---|-----|-----|-----|-----|-----|-----|-----|-----|

| -  | -  | -  | -  | -  | -  | - | - | P7S | P6S | P5S | P4S | P3S | P2S | P1S | P0S |

| Bit         | Function                                      |  |  |  |  |  |  |  |

|-------------|-----------------------------------------------|--|--|--|--|--|--|--|

| PiS         | Port pin sensitivity                          |  |  |  |  |  |  |  |

|             | 0: Level sensitive (def.)                     |  |  |  |  |  |  |  |

|             | 1: Edge sensitive                             |  |  |  |  |  |  |  |

| Bits 8 - 15 | RESERVED (read: undefined, write: don't care) |  |  |  |  |  |  |  |

14/66

#### 5 **Memory**

#### 5.1 Internal memory resource

One 32 Kword and two 8 Kword single port memories are included on-chip:

- Instruction memory on I space from address 0 to 32767 (32 K)

- X-Data memory on X space from address 0 to 8191 (8 K)

- Y-Data memory on Y space from address 0 to 8191 (8 K)

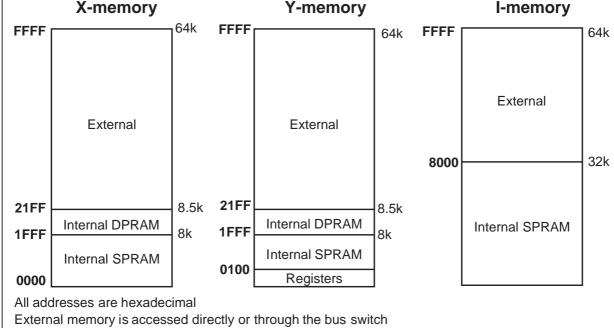

One 512 word dual port memory is shared on X and Y spaces, from addresses 8192 (8 K) to 8703 (8.5K). This is represented graphically below.

Note: the first 256 addresses of the Y space are reserved for the D950 memory-mapped registers and for on-chip memory mapped peripherals.

Memory can be extended off-chip for all three spaces in two ways:

- 1: Directly Accesses to program and data memories can be performed simultaneously. Insertion of wait-states is necessary in case of nominal frequency work.

- 2: Through the bus switch unit Accesses to the different external spaces are multiplexed and wait-states are added.

The specific details on the operation of the BSU are described separately in "Bus Switch Unit" on page 18.

Figure 5.1 **Memory mapping** Y-memory X-memory 64k **FFFF FFFF** 64k **FFFF**

#### 5.2 Direct bus extension

#### **Direct extension for I-memory**

The internal program memory is used from address 0 to 32767 (32 K). Note, no detection is provided when an internal space is declared as an external one for the BSU.

The I-bus direct transfer enable signal (IDT\_EN) determines whether an access is made directly to external memory or via the BSU. If reset occurs with the MODE signal set to '1' (select reset address to xFC00), then

- if IDT\_EN input = 0: access to external memory is through the BSU

- if IDT\_EN input = 1: access to direct external memory space

IAE/IBSE/IRDE/IWRE are always driven except in the case of an external HOLD request.

Note: an external coprocessor will work only when executing program in the external space.

IDE bus is an output only when a direct external write is detected. IDE bus is an input in the case of:

- · an external memory read

- DMA (write) transfers between an external peripheral and internal memory

#### **Direct extension for X-memory**

The internal X memory is used from address 0 to 8703 (8.5 K). It is extended with external memory from address 8704 (8.5K) to 65535 (64K) with the XE bus extension.

The direct extension is managed by the bus switch unit. When the EN\_X bit of the BSU XER register (see "XER0/1: X-memory space control registers" on page 20) is set to '0', it generates only software wait-states and access is direct. If the EN\_X bit is set to '1', data goes via the BSU.

X extension and bus switch share the same I/O's.

#### **Direct extension for Y-memory**

The internal Y memory is used from address 0 to 8703 (8.5 K). It is extended with external memory from address 8704 (8.5 K) to 65535 (64 K) with the YE bus extension.

Address 0 to 256 of the Y space are reserved for memory mapped registers.

Note: The BSU and X direct extension share the same I/O, therefore extension of IE through the BSU is not possible when direct extension is selected for X/Y. Some combinations of the EN\_I, EN\_X and EN\_Y bits of the BSU control registers IER/XER/YER are not allowed, as shown in Table 5.1 below.

Table 5.1 Possible BSU register settings

| EN_I | EN_X | EN_Y | Operation                                                            | Allowed or forbidden                    |

|------|------|------|----------------------------------------------------------------------|-----------------------------------------|

| 1    | 1    | 1    | Exchanges enabled on I/X/Y spaces                                    | Allowed                                 |

| 1    | 1    | 0    | Exchanges enabled on I and X spaces Only DTACK generation on Y space | Allowed                                 |

| 1    | 0    | 1    | Exchanges enabled on I and Y spaces Only DTACK generation on X space | Forbidden (X direct & I/Y through BSU)  |

| 1    | 0    | 0    | Exchanges enabled on I space Only DTACK generation on X and Y spaces | Forbidden<br>(X direct & I through BSU) |

| 0    | 1    | 1    | Exchanges enabled on X and Y spaces Only DTACK generation on I space | Allowed                                 |

| 0    | 1    | 0    | Exchanges enabled on X space Only DTACK generation on I and Y spaces | Allowed                                 |

| 0    | 0    | 1    | Exchanges enabled on Y space Only DTACK generation on I and X spaces | Forbidden (X direct & Y through BSU)    |

| 0    | 0    | 0    | No exchange Only DTACK generation on I, X and Y spaces               | Allowed                                 |

## 6 Bus Switch Unit

The three memory spaces can be extended off-chip through the bus switch unit (BSU) peripheral. The figure below shows the layout of the D950Core BSU.

INTERNAL MEMORIES & PERIPHERALS X XD MEM. MEM MEM. IRD/XRD/YRD INTERNAL MEMORIES & PERIPHERALS ED BUS YD D950Core EXRD/DS SWITCH EXWR/RD IWR/XWR/YWR UNIT EYRD/DS INTERNAL MEMORIES EYWR/RD & PERIPHERALS EIRD/DS IID/I XD/IYD DEID/DEXD/DEYD EIWR/RD DTACKin IDT\_EN IΑ IBS/XBS/YBS DTACK AS-DSP \_ VR02020A

Figure 6.1 D950Core Bus Switch Unit

## 6.1 BSU operation

The BSU recognizes a bus cycle when a bus extension strobe (IBSE, XBSE or YBSE) goes active. The BSU decodes the address value to determine if an external memory access is requested on the I, X or Y-bus and generates the appropriate signals on the external bus side. The BSU generates software wait-states, depending on the setting of the control register.

If more than one external memory access is attempted at one instruction cycle, they are serviced sequentially in the following order: I-bus, X-bus, Y-bus.

Each external access requires one basic instruction clock cycle (2 CLKIN cycles), extended by, at least, one wait-state (2 CLKIN cycles). The number of wait-states can be extended, either by software with the BSU control registers (see Section 6.2), or by hardware with the DTACK input signal.

## 6.2 BSU control registers

INTERNAL0

**DEFAULT MAPPING (RESET)**

Figure 6.2

The BSU is programmed by six control registers mapped in the Y-memory space. These define the type of memory used, internal to external boundary address crossing, exchange type (external direct or through the BSU) and software wait-states count.

There are 2 registers per memory space, making it possible to define 2 sets of boundaries and wait state numbers.

INTERNAL1

**INTERNAL0**

USER MAPPING (CAN CHANGE BY 1K STEP)

VALUE 0

EXTERNAL

64K

63K

62K

EXTERNAL

VALUE 1

VALUE 1

Default and user mapping examples

The BSU control registers include a reference address on bits 4 to 9, where the internal/external memory boundary value is stored (see Figure 6.2), and software wait-states count on bits 0 to 3, allowing up to 16 wait-states.

VALUE 0 H

External addressing is recognized by comparing these address bits for each valid address from IA, XA and YA, to the reference address contained into the corresponding control register.

If the address is greater or equal to the reference value, an external access proceeds.

In the following register descriptions, '-' means RESERVED (read: 0, write: don't care).

## XER0/1: X-memory space control registers

After reset, XER0/1 default values are 0x83EF/0x83FF

| 15 | 14   | 13 | 12 | 11 | 10 | 9    | 8    | 7    | 6    | 5    | 4    | 3  | 2  | 1  | 0  |

|----|------|----|----|----|----|------|------|------|------|------|------|----|----|----|----|

| IM | EN_X | -  | -  | -  | -  | XA15 | XA14 | XA13 | XA12 | XA11 | XA10 | W3 | W2 | W1 | W0 |

| Bit     | Function                                                        |

|---------|-----------------------------------------------------------------|

| W3:0    | Wait state count (1 to 16) for off-chip access (X-memory space) |

| XA15:10 | X-memory space map for boundary on-chip or off-chip             |

| EN_X    | Enable for X-space data exchanges                               |

| IM      | Intel/Motorola                                                  |

|         | 0: Motorola type for memories                                   |

|         | 1: Intel type for memories (default)                            |

## YER0/1: Y-memory space control registers

After reset, YER0/1 default values are 0x83EF/0x83FFI

| 15 | 14   | 13 | 12 | 11 | 10 | 9    | 8    | 7    | 6    | 5    | 4    | 3  | 2  | 1  | 0  |

|----|------|----|----|----|----|------|------|------|------|------|------|----|----|----|----|

| IM | EN_Y | -  | -  | -  | -  | YA15 | YA14 | YA13 | YA12 | YA11 | YA10 | W3 | W2 | W1 | W0 |

| Bit     | Function                                                        |

|---------|-----------------------------------------------------------------|

| W3:0    | Wait state count (1 to 16) for off-chip access (Y-memory space) |

| YA15:10 | Y-memory space map for boundary on-chip or off-chip             |

| EN_Y    | Enable for Y-space data exchanges                               |

| IM      | Intel/Motorola                                                  |

|         | 0: Motorola type for memories                                   |

|         | 1: Intel type for memories (default)                            |

## IER0/1: Instruction memory control registers

After reset, IER0/1 default values are 0x83EF/0x83FF or 0xC3EF/0xC3FF (the EN\_I value depends on the  $\overline{IDT}_{\overline{EN}}$  input value

| 15 | 14   | 13 | 12 | 11 | 10 | 9    | 8    | 7    | 6    | 5    | 4    | 3  | 2  | 1  | 0  |

|----|------|----|----|----|----|------|------|------|------|------|------|----|----|----|----|

| IM | EN_I | -  | -  | -  | -  | IA15 | IA14 | IA13 | IA12 | IA11 | IA10 | W3 | W2 | W1 | W0 |

| Bit     | Function                                                        |

|---------|-----------------------------------------------------------------|

| W3:0    | Wait state count (1 to 16) for off-chip access (I-memory space) |

| IA15:10 | I-memory space map for boundary on-chip or off-chip             |

| EN_I    | Enable for I-space data exchanges                               |

| IM      | Intel/Motorola                                                  |

|         | 0: Motorola type for memories                                   |

|         | 1: Intel type for memories (default)                            |

20/66

## 7 DMA Controller

The DMA controller manages data transfer between memories and external peripherals and has the following features:

- four independent DMA channels

- transfers on X / Y / I spaces (simultaneous transfers on X and Y spaces)

- cycle stealing operation:

- 3 cycles for a single data transfer (+1 cycle for transfers on I space)

- (n+2) cycles for an n-data block transfer (+1cycle for transfers on I space)

- each channel has:

- 3 signals: request (DMARQ), acknowledge (DMACK), interrupt request (DIT)

- 4x16 bit registers for block transfer facilities

- fixed priority between the four channels (highest channel 0, lowest channel 3)

The DMA controller  $\overline{\text{DMARQ0-3}}$  inputs and  $\overline{\text{DMACK0-3}}$  outputs are available as primary inputs, in the case of SIO inhibition. This is set by the DMAR register (see "DMAR: DMA management register" on page 44).

Figure 7.1 **DMA** controller  $\overline{AS}$ -D $\overline{SP}$ INTERRUPT D950Core YRD CONTROLLER 16 YWR YBS PERIPHERAL DMA CLK RESET HOLD HOLDACK DMAR00 IRD DMARQ1 IWR DMARQ2 IBS DMARQ3 XRD DMA CONTROLLER PERIPHERAL XWR DMACK0 XBS DMACK1 DMACK2 DMACK3 DTACK DIP ENA

## 7.1 DMA operation

The DMA controller interface contains four independent channels allowing data transfer on I-memory space and simultaneous data transfer on X and Y-memory spaces. When requests to transfer data on the same bus occur at the same time on different channels, the requests are concatenated to be acknowledged during the same transfer according to fixed priority. Channel 0 has the highest priority ranging to channel 3 with the lowest priority.

The DMA transfer is based on a DSP cycle stealing operation:

- DMA controller generates a 'hold request'.

- The core sends back a 'hold acknowledge' to the DMA controller and enters the hold state (bus released).

- The DMA controller manages the transfer and enters its idle state at the end of the transfer, until reception of a new DMA request. The 'hold request' signal is removed.

The data transfer duration is n+2 cycles, split into:

- One cycle inserted at the beginning of the transfer when bus controls are released by the D950Core, n cycles for the number of data words to be transferred.

- Another cycle is inserted at the end of the transfer when bus controls are released by the DMA controller.

Single or block data can be transferred. The DMA request signal (DMARQ) can be either edge (single) or level (block) sensitive. Data blocks can be transferred one data at a time using an edge sensitive request signal.

A double buffering mechanism is available to deal with data blocks requiring the allocation of 2N addresses for the transfer of an N data block.

An interrupt can be used to warn AS-DSP that a predefined number of data have been transferred and are ready to be processed. Interrupt requests are sent from the DMA controller to the interrupt controller. The selected channels must be edge sensitive and the user has to define the proper priority.

## 7.2 DMA registers

### **Address registers**

Two 16-bit registers (unsigned) are dedicated per channel for address transfer:

- DIA: initial address. Contains the initial address of the selected address bus (see DBC-bit of DGC register).

- DCA: current address. Contains the value to be transferred to the selected address bus (see DBC-bit of DGC register) during the next transfer. The different DCA values are:

| Reset | DAI | DLA | DCC = 0 | DCA(n+1)   |

|-------|-----|-----|---------|------------|

| 1     | X   | X   | X       | 0          |

| 0     | 0   | X   | X       | DCA(n)     |

| 0     | 1   | 0   | X       | DCA(n) + 1 |

| 0     | 1   | 1   | 0       | DCA(n) + 1 |

| 0     | 1   | 1   | 1       | DIA        |

Note: See "DAIC: Address/interrupt control register" on page 24 for DAI and DLA definitions

#### **Counting registers**

Two 16-bit registers (unsigned) per channel are dedicated for count transfer.

For a transfer of an N data block, DIC and DCC registers have to be loaded with N-1.

When DCC content is 0 (valid transfer count), it is loaded with DIC content for the next transfer.

- DIC: initial count. Contains the total number of transfers of the entire block

- DCC: current count. Contains the remaining number of transfers required to fill the entire block. It is decremented after each transfer. The DCC values are:

| Reset | DCC = 0 | DCA(n+1)   |

|-------|---------|------------|

| 1     | X       | 0          |

| 0     | 0       | DCA(n) - 1 |

| 0     | 1       | DIC        |

### **Control registers**

Three 16-bit control registers are dedicated to the DMA controller interface. These are the general control register, the address interrupt control register and the mask sensitivity control register. They are detailed below.

## **DGC: General control register**

Three bits are dedicated for each DMA channel (bits 0 to 2 to channel 0, bits 4 to 6 to channel 1, bits 8 to 10 to channel 2, bits 12 to 14 to channel 3).

(Address = 0040, Reset = 0000h, Read/Write).

|   | 15 | 14   | 13   | 12   | 11 | 10   | 9    | 8    | 7 | 6    | 5    | 4    | 3 | 2    | 1    | 0    |

|---|----|------|------|------|----|------|------|------|---|------|------|------|---|------|------|------|

| ſ | -  | DRW3 | DBC1 | DBC0 | -  | DRW2 | DBC1 | DBC0 | - | DRW1 | DBC1 | DBC0 | - | DRW0 | DBC1 | DBC0 |

| Bit       | Function                     |

|-----------|------------------------------|

| DBC1/DBC0 | Bus choice for data transfer |

|           | 00: X-bus (default)          |

|           | 01: Y-bus                    |

|           | 10: I-bus                    |

|           | 11: reserved                 |

| DRWi      | Data transfer direction      |

|           | 0: Write access (default)    |

|           | 1: Read access               |

## **DAIC: Address/interrupt control register**

Four bits are dedicated for each DMA channel (bits 0 to 3 to channel 0, bits 4 to 7 to channel 1, bits 8 to 11 to channel 2, bits 12 to 15 to channel 3).

(Address = 0042, Reset = 0000h, Read/Write)

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| DAI3 | DLA3 | DIP3 | DIE3 | DAI2 | DLA2 | DIP2 | DIE2 | DAI1 | DLA1 | DIP1 | DIE1 | DAI0 | DLA0 | DIP0 | DIE0 |

| Bit   | Function                                                                |

|-------|-------------------------------------------------------------------------|

| DIEi  | Enable interrupt                                                        |

|       | 0: Interrupt request output associated to channel i is masked (default) |

|       | Interrupt request output associated to channel i is not masked          |

| DIPi  | Interrupt pending                                                       |

|       | 0: No pending interrupt on channel i (default)                          |

|       | 1: Pending interrupt on channel i (enabled if DIP_ENA input is high)    |

| DLAi: | Load address                                                            |

|       | 0: DCAi content incremented after each data transfer (default)          |

|       | 1: DCAi content loaded with DIA content if DCCi value is 0,             |

|       | or DCAi content incremented if DCCi value is not equal to 0             |

| DAIi  | Address increment                                                       |

|       | 0: DCAi content unchanged (default)                                     |

|       | DCAi content modified according to DLAi state                           |

## DMS: Mask sensitivity control register

Two bits are dedicated to each DMA channel (bits 0 and 1 to channel 0, bits 4 and 5 to channel 1, bits 8 and 9 to channel 2, bits 12 and 13 to channel 3).

(Address = 0041, Reset = x3333h, Read/Write)

|   | 15 | 14 | 13   | 12   | 11 | 10 | 9    | 8    | 7 | 6 | 5    | 4    | 3 | 2 | 1    | 0    |

|---|----|----|------|------|----|----|------|------|---|---|------|------|---|---|------|------|

| ľ | -  | -  | DSE3 | DMK3 | -  | -  | DSE2 | DMK2 | - | - | DSE1 | DMK1 | - | - | DSE0 | DMK0 |

| Bit  | Function                        |

|------|---------------------------------|

| DMKi | DMA mask                        |

|      | 0: DMA channel not masked       |

|      | 1: DMA channel masked (default) |

| DSEi | DMA sensitivity                 |

|      | 0: Low level                    |

|      | 1: Falling edge (default)       |

## 8 Interrupt Controller

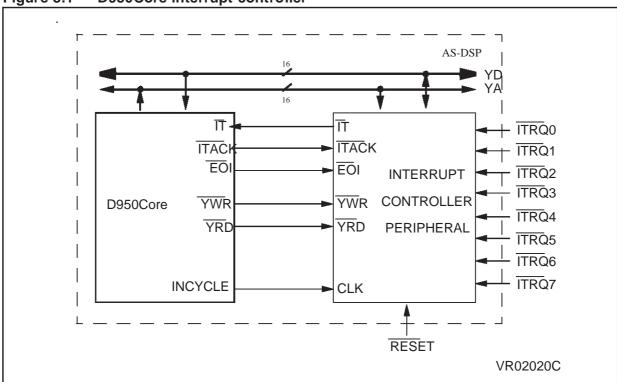

The interrupt controller (ITC) can manage up to eight external interrupts. The interrupt controller has the following features:

- 8 independent interrupt sources, each one associated with:

- 16-bit programmable interrupt vector provides the address of the first instruction of the interrupt routine associated with the source.

- mask bit, enabling each source to be activated or deactivated

- sensitivity bit (edge/level)

- 2-bit programmable priority level

- 'pending interrupt' flag displays the source waiting for service. This flag is writable to allow a software interrupt capability.

- Interrupt processing whenever its priority level is higher than the current priority level.

- Nested of up to 4 interrupts(the stack content is accessible in read or write).

Figure 8.1 D950Core interrupt controller

The interrupt controller ITRQ inputs can be connected to external interrupt requests or to internal peripheral requests, this is dependent on the setting of the port/interrupt control (PICR) system register, see Table on page 43 for details. The interrupt controller receives interrupt

requests from primary inputs P\_ITRQ0-7 on its inputs ITRQ0-7 when bit 0-7 of the PICR register is set to '0'. Otherwise, the ITRQ0-7 input is connected to internal peripheral interrupt request output. Each input can be programmed independently.

## 8.1 Interrupt controller registers

The interrupt controller interface is controlled by status and control registers mapped into the Y-memory space. Status registers are not write-protected.

## IVO0-7: Interrupt vector0-7 address registers

The IVO0-7 registers (one per external interrupt) contain the first address of the interrupt routine and are associated with the respective interrupt input ITRQ0-7. The register content of the interrupt under service is provided on the YD bus during the cycle following the ITACK falling edge.

(Address = 0020-0027, No reset value, Read/Write)

|   | 15     | 14     | 13     | 12     | 11     | 10     | 9     | 8     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| ſ | IVi 15 | IVi 14 | IVi 13 | IVi 12 | IVi 11 | IVi 10 | IVi 9 | IVi 8 | IVi 7 | IVi 6 | IVi 5 | IVi 4 | IVi 3 | IVi 2 | IVi 1 | IVi 0 |

### ICR: Interrupt control register

The ICR register displays the current priority level and up to four stacked priority levels.

(Address = 0028, Reset = 000Bh, Read/Write))

| 15         | 14 | 13         | 12 | 11 | 10         | 9 | 8 | 7 | 6        | 5  | 4  | 3        | 2 | 1  | 0 |

|------------|----|------------|----|----|------------|---|---|---|----------|----|----|----------|---|----|---|

| SPL4 (2:0) |    | SPL3 (2:0) |    |    | SPL2 (2:0) |   |   | S | SPL1 (2: | 0) | ES | GPL (2:0 |   | 0) |   |

| Bit  | Function                                                   |

|------|------------------------------------------------------------|

| CPL  | Current priority level (-1, 0, 1, 2 or 3) (default is 011) |

| ES   | Empty stack flag                                           |

|      | 0: stack is used                                           |

|      | 1: stack is not used (default)                             |

| SPL1 | 3-bit 1st stacked priority level                           |

| SPL2 | 3-bit 2nd stacked priority level                           |

| SPL3 | 3-bit 3rd stacked priority level                           |

| SPL4 | 3-bit 4th stacked priority level                           |

| The current priority I | evels available are | shown in below. |

|------------------------|---------------------|-----------------|

|------------------------|---------------------|-----------------|

| Priority level | Coding    | Acceptable IT level priority |

|----------------|-----------|------------------------------|

| - 1            | 111       | 0,1,2,3                      |

| 0              | 000       | 1,2,3                        |

| 1              | 001       | 2,3                          |

| 2              | 010       | 3                            |

| 3              | 011       |                              |

| Reserved       | 100 - 110 |                              |

An interrupt request is acknowledged when its priority level (coded in the IPR register) is higher than the current priority level. In this case, the current priority level becomes the interrupt priority level and the previous current priority level is pushed onto the stack and displayed as stack priority level (SPL)1.

The process is repeated over a range of four interrupt requests and the four previous current stack priority levels are displayed on SPL1, SPL2, SPL3 and SPL4. If less than four interrupts are pushed onto the stack, the unused SPL words are set to '000'. At the end of the interrupt routine, the priority levels are popped from the stack.

The empty stack (ES) flag is used to indicate whether the stack is used or not. The ISP word of the ISP register indicates the depth of the stack (see below).

INTERRUPT LEVEL 2 **INTERRUPT LEVEL 3 PROGRAM** PROGRAM IT2 PROGRAM IT3 **ICR** SPL4 SPL3 SPL2 SPL1 ES CPL SPL4 SPL3 SPL2 SPL1 ES CPL SPL4 SPL3 SPL2 SPL1 ES CPL Χ Χ Χ -1 2 3 **ISPR** ISP **ISP ISP** 0 1 2

Figure 8.2 **ICR** and **ISPR** Operation

## IMR: Interrupt mask/sensitivity register

(Address = 0029, Reset = 5555h, Read/Write)

| `   |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| IS7 | IM7 | IS6 | IM6 | IS5 | IM5 | IS4 | IM4 | IS3 | IM3 | IS2 | IM2 | IS1 | IM1 | IS0 | IM0 |

| Bit | Function                                   |

|-----|--------------------------------------------|

| IM  | Interrupt mask                             |

|     | 0: Interrupt is not masked                 |

|     | 1: Interrupt is masked (default)           |

| IS  | Sensitivity                                |

|     | 0: ITRQ is active on a low level (default) |

|     | 1: ITRQ is active on a falling edge        |

Each interrupt input ITRQ0-7 can be masked individually when the corresponding IM0-7 bit is set. In this case any activity on the ITRQ0-7 pin is ignored. All IM bits are set during DSP reset.

ITRQ0-7 is active either on a low level when IS0-7 is low (by default on reset) or on a falling edge when IS0-7 is high.

When ITRQ0-7 is active on a low level, it must stay low until the ITACK falling edge is sampled.

## IPR: Interrupt priority register

(Address = 002A, Reset = 0000h, Read/Write))

| 15   | 14    | 13   | 12    | 11   | 10    | 9   | 8     | 7    | 6     | 5    | 4    | 3    | 2    | 1    | 0    |

|------|-------|------|-------|------|-------|-----|-------|------|-------|------|------|------|------|------|------|

| IP7( | (1:0) | IP6( | (1:0) | IP5( | (1:0) | IP4 | (1:0) | IP3( | (1:0) | IP2( | 1:0) | IP1( | 1:0) | IP0( | 1:0) |

| Bit | Function                                               |

|-----|--------------------------------------------------------|

| IP  | Interrupt priority level (0, 1, 2 or 3) (default is 0) |

The IPR register contains the priority level of each ITRQ0-7 interrupt input. IP0-7 priority level is coded using two bits. The different values of IP are 0, 1, 2, 3 (0 lowest priority, 3 highest priority).

When two  $\overline{ITRQ}$  with the same priority level are requesting during the same cycle, the first acknowledged interrupt is the one corresponding to the lowest number (for example,  $\overline{ITRQ0}$  acknowledged prior to  $\overline{ITRQ3}$ ).

57

### ISPR: Interrupt stack pointer register

(Address = 002B, Reset = 0000h, Read/Write)

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2  | 1      | 0 |

|----|----|----|----|----|----|---|---|---|---|---|---|---|----|--------|---|

| -  | -  | -  | -  | -  | -  | - | - | - | - | - | - | - | 13 | SP(2:0 | ) |

| Bit  | Function                                         |

|------|--------------------------------------------------|

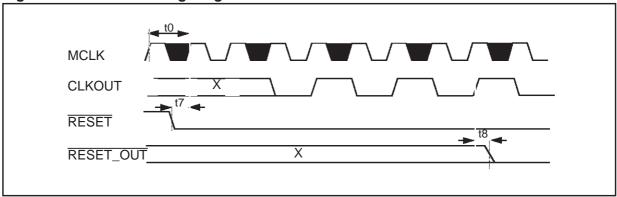

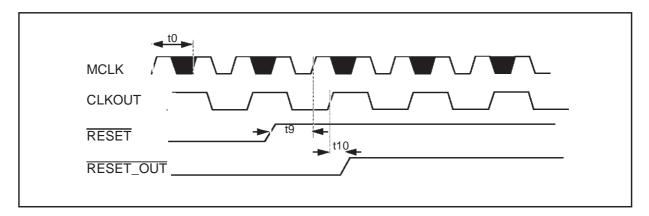

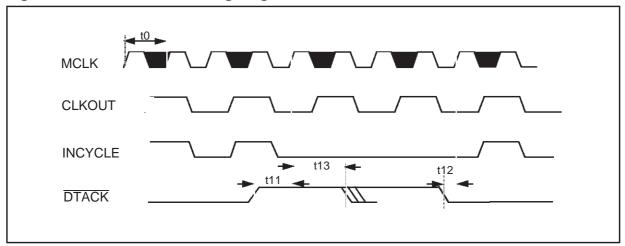

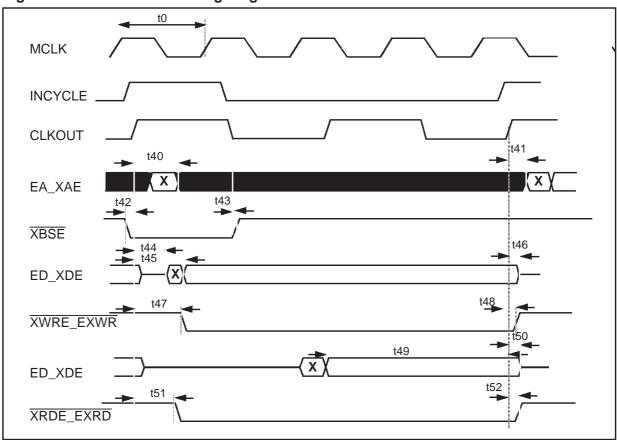

| ISPR | Number of stacked priority levels (0, 1, 2 or 3) |