#### **REFERENCE APP NOTE 7374**

August 1996

## **CMOS Keyboard Encoder**

#### Features

- Directly Interfaces with CDP1800-Series Microprocessor

- · Low Power Dissipation

- · Three-State Outputs

- Scans and Generates Code for 53 Key ASCII Keyboard Plus 32 HEX Keys (SPST Mechanical Contact Switches)

- · Shift, Control, and Alpha Lock Input

- RC-Controlled Debounce Circuitry

- Single Supply 4V to 10.5V...... (CDP1871A)

4V to 6.5V...... (CDP1871AC)

- N-Key Lockout

#### Ordering Information

| PACKAGE | TEMP. RANGE    | 5V          | 10V       | PKG.<br>NO. |

|---------|----------------|-------------|-----------|-------------|

| PDIP    | -40°C to +85°C | CDP1871ACE  | CDP1871AE | E40.6       |

| PLCC    | -40°C to +85°C | CDP1871ACQ  | -         | N44.65      |

| SBDIP   | -40°C to +85°C | CDP1871ACD  | CDP1871AD | D40.6       |

| Burn-In |                | CDP1871ACDX | -         | D40.6       |

#### Description

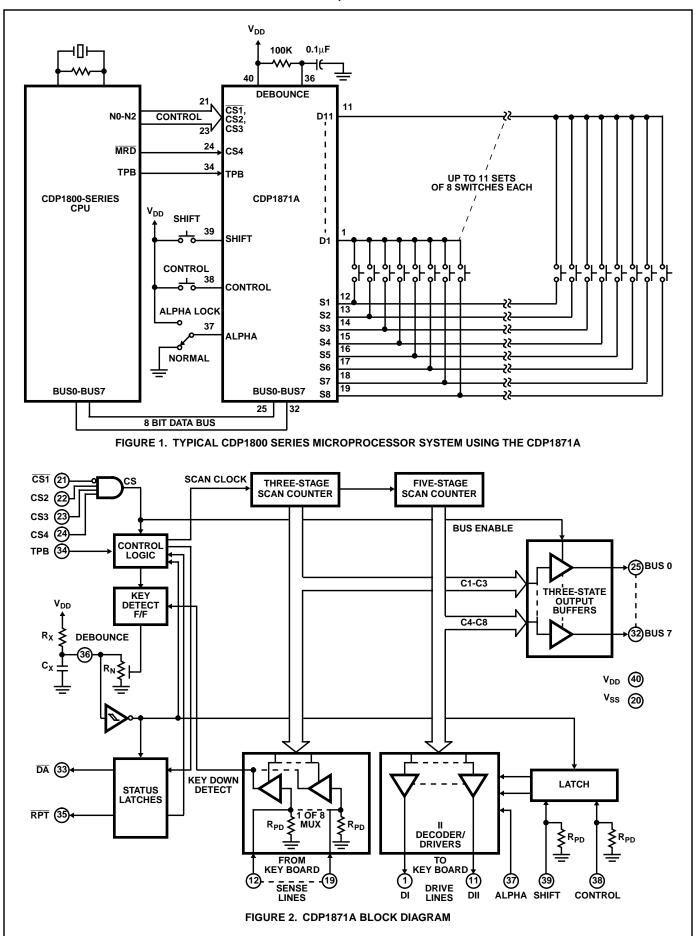

The CDP1871A is a keyboard encoder designed to directly interface between a CDP1800-series microprocessor and a mechanical keyboard array, providing up to 53 ASCII coded keys and 32 HEX coded keys, as shown in the system diagram (Figure 1).

The keyboard may consist of simple single-pole single-throw (SPST) mechanical switches. Inputs are provided for alpha-lock, control, and shift functions, allowing 160 unique codes. An external R-C input is available for user-selectable debounce times. The N-key lock-out feature prevents unwanted key codes if two or more keys are pressed simultaneously.

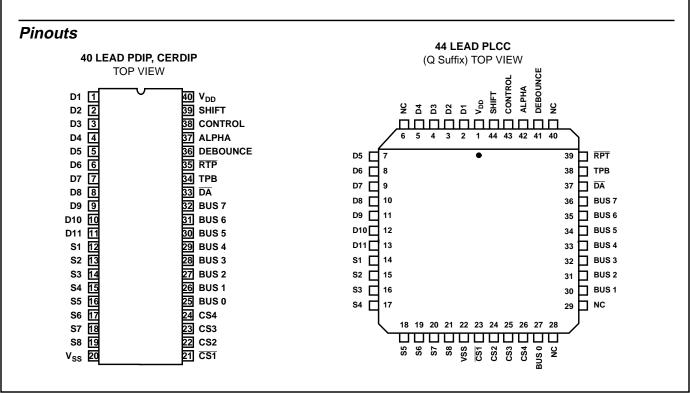

The CDP1871A and CDP1871AC are functionally identical. They differ in that the CDP1871A has a recommended operating voltage range of 4V to 10.5V, and the CDP1871AC has a recommended operating voltage range 4V to 6.5V. These types are supplied in 40 lead dual-in-line ceramic packages (D suffix), and 40 lead dual-in-line plastic packages (E suffix), and 44 lead plastic chip-carrier packages (Q suffix).

#### **Absolute Maximum Ratings**

| (All Voltages Referenced to V <sub>SS</sub> Terminal) |                               |

|-------------------------------------------------------|-------------------------------|

| CDP1871A                                              | 0.5V to +11V                  |

| CDP1871AC                                             | 0.5V to +7V                   |

| Input Voltage Range, All Inputs                       | 0.5V to V <sub>DD</sub> +0.5V |

| DC Input Current, any One Input                       | ±10mA                         |

#### **Thermal Information**

| Thermal Resistance (Typical)                      | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (oC/W) |

|---------------------------------------------------|----------------------|----------------------|

| PDIP Package                                      | 60                   | N/A                  |

| PLCC Package                                      | 50                   | N/A                  |

| SBDIP Package                                     | 60                   | 18                   |

| Device Dissipation Per Output Transistor          |                      |                      |

| T <sub>A</sub> = Full Package Temperature Range   |                      |                      |

| (All Package Types)                               |                      | 100mW                |

| Operating Temperature Range (T <sub>A</sub> )     |                      |                      |

| Package Type D                                    | 55 <sup>o</sup>      | °C to +125°C         |

| Package Type E and Q                              | 40                   | 0°C to +85°C         |

| Storage Temperature Range (T <sub>STG</sub> )     | 65°                  | °C to +150°C         |

| Lead Temperature (During Soldering)               |                      |                      |

| At distance $1/16 \pm 1/32$ In. $(1.59 \pm 0.79)$ | nm)                  |                      |

| from case for 10s max                             |                      | +265°C               |

|                                                   |                      |                      |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

**Recommended Operating Conditions** At T<sub>A</sub> = -40 to +85°C. For maximum reliability, operating conditions should be selected so that operation is always within the following ranges:

|                                                               |                              |                        | LIMITS          |                                          |                 |                 |       |  |  |  |

|---------------------------------------------------------------|------------------------------|------------------------|-----------------|------------------------------------------|-----------------|-----------------|-------|--|--|--|

|                                                               |                              | v                      | CDP1871AD,      | CDP1871AD, CDP1871AE CDP1871ACD, CDP1871 |                 |                 |       |  |  |  |

| PARAMETER                                                     |                              | V <sub>DD</sub><br>(V) | MIN             | MAX                                      | MIN             | MAX             | UNITS |  |  |  |

| Supply Voltage Range                                          |                              |                        | 4               | 10.5                                     | 4               | 6.5             | V     |  |  |  |

| Recommended Input Voltage<br>Range                            |                              |                        | V <sub>SS</sub> | V <sub>DD</sub>                          | V <sub>SS</sub> | V <sub>DD</sub> | V     |  |  |  |

| Clock Input Frequency, TPB<br>(Keyboard Capacitance = 200 pF) | f <sub>CL</sub>              | 5                      | DC              | 0.4                                      | DC              | 0.4             | MHz   |  |  |  |

| (Neyboard Capacitarice = 200 pr )                             | yboard Capacitance = 200 pF) |                        | DC              | 0.8                                      | -               | -               | MHz   |  |  |  |

#### NOTE:

#### Static Electrical Specifications At $T_A = -40$ to +85 °C, Unless Otherwise Specified

|                                                  |                 | CC                    | ONDITION               | s                      |      |                        | LIM | ITS                      |                |     |       |

|--------------------------------------------------|-----------------|-----------------------|------------------------|------------------------|------|------------------------|-----|--------------------------|----------------|-----|-------|

|                                                  |                 |                       |                        |                        | -    | CDP1871AD<br>CDP1871AE |     | CDP1871ACD<br>CDP1871ACE |                |     |       |

| PARAMETER                                        |                 | ν <sub>ο</sub><br>(۷) | V <sub>IN</sub><br>(V) | V <sub>DD</sub><br>(V) | MIN  | (NOTE 1)<br>TYP        | MAX | MIN                      | (NOTE1)<br>TYP | MAX | UNITS |

| Quiescent Device<br>Current                      | I <sub>DD</sub> | -                     | 0.5                    | 5                      | -    | 0.1                    | 50  | -                        | 1              | 200 | μΑ    |

| Current                                          |                 | -                     | 0, 10                  | 10                     | -    | 1                      | 200 | -                        | -              | -   | μΑ    |

| Output Low Drive (Sink) Current (Except Debounce | I <sub>OL</sub> | 0.4                   | 0, 5                   | 5                      | 0.5  | 1                      | -   | 0.5                      | 1              | -   | mA    |

| and D1-D11)                                      |                 | 0.5                   | 0, 10                  | 10                     | 1    | 2                      | -   | -                        | -              | -   | mA    |

| Debounce                                         | I <sub>OL</sub> | 0.4                   | 0, 5                   | 5                      | 0.75 | 1.5                    | -   | 0.75                     | 1.5            | -   | mA    |

|                                                  |                 | 0.5                   | 0, 10                  | 10                     | 1    | 2                      | -   | -                        | -              | -   | mA    |

| D1-D11                                           | I <sub>OL</sub> | 0.4                   | 0, 5                   | 5                      | 0.05 | 0.1                    | -   | 0.05                     | 0.1            | -   | mA    |

|                                                  |                 | 0.5                   | 0, 10                  | 10                     | 0.1  | 0.2                    | -   | -                        | -              | -   | mA    |

<sup>1.</sup> Printed-circuit board mount: 57mm x 57mm minimum area x 1.6mm thick G10 epoxy glass, or equivalent.

# CDP1871A, CDP1871ACCDP1871A, CDP1871AC

# Static Electrical Specifications At $T_A$ = -40 to +85 $^{\rm o}$ C, Unless Otherwise Specified (Continued)

|                                                  |                   | cc                 | CONDITIONS LIMITS      |                        |       |                      |      |      |                        |      |       |

|--------------------------------------------------|-------------------|--------------------|------------------------|------------------------|-------|----------------------|------|------|------------------------|------|-------|

|                                                  |                   |                    |                        |                        |       | DP1871AD<br>DP1871AE |      | _    | DP1871ACE<br>DP1871ACE |      |       |

| PARAMETER                                        |                   | V <sub>O</sub> (V) | V <sub>IN</sub><br>(V) | V <sub>DD</sub><br>(V) | MIN   | (NOTE 1)             | MAX  | MIN  | (NOTE1)<br>TYP         | MAX  | UNITS |

| Output High Drive (Source)                       | I <sub>OH</sub>   | 4.6                | 0, 5                   | 5                      | -0.3  | -0.6                 | -    | -0.3 | -0.6                   | -    | mA    |

| Current                                          |                   | 9.5                | 0, 10                  | 10                     | -0.75 | -1.5                 | -    | -    | -                      | -    | mA    |

| Input Low Voltage                                | V <sub>IL</sub>   | 0.5, 4.5           | -                      | 5                      | -     | -                    | 1.5  | -    | -                      | 1.5  | V     |

| (Except Debounce)                                |                   | 1, 9               | -                      | 10                     | -     | -                    | 3    | -    | -                      | -    | V     |

| Input High Voltage                               | V <sub>IH</sub>   | 0.5, 4.5           | -                      | 5                      | 3.5   | -                    | -    | 3.5  | -                      | -    | V     |

| (Except Debounce)                                |                   | 1, 9               | -                      | 10                     | 7     | -                    | -    | -    | -                      | -    | V     |

| Debounce Schmitt Trigger<br>Input Voltage        | V <sub>D</sub>    | 0.4                | -                      | 5                      | 2.0   | 3.3                  | 4.0  | 2.0  | 3.3                    | 4.0  | V     |

| Positive Trigger Voltage                         |                   | 0.5                | -                      | 10                     | 4.0   | 6.3                  | 8.0  | -    | -                      | -    | V     |

| Negative Trigger Voltage                         | V <sub>N</sub>    | 0.4                | -                      | 5                      | 0.8   | 1.8                  | 3.0  | 0.8  | 1.8                    | 3.0  | V     |

|                                                  |                   | 0.5                | -                      | 10                     | 1.9   | 4.0                  | 6.0  | -    | -                      | -    | V     |

| Hysteresis                                       | V <sub>H</sub>    | 0.4                | 0, 5                   | 5                      | 0.3   | 1.6                  | 2.6  | 0.3  | 1.6                    | 2.6  | V     |

|                                                  |                   | 0.5                | 0, 10                  | 10                     | 0.7   | 2.3                  | 4.7  | -    | -                      | -    | V     |

| Output Voltage Low Level                         | V <sub>OL</sub>   | -                  | 0, 5                   | 5                      | -     | 0                    | 0.05 | -    | 0                      | 0.05 | V     |

|                                                  |                   | -                  | 0, 10                  | 10                     | -     | 0                    | 0.05 | -    | -                      | -    | V     |

| Output Voltage High Level                        | V <sub>OH</sub>   | -                  | 0, 5                   | 5                      | 4.95  | 5                    | -    | 4.95 | 5                      | -    | V     |

|                                                  |                   | -                  | 0, 10                  | 10                     | 9.95  | 10                   | -    | -    | -                      | -    | V     |

| Input Leakage Current<br>(Except S1-S8, Shift,   | I <sub>IN</sub>   | -                  | 0, 5                   | 5                      | -     | 0.01                 | 1    | -    | 0.01                   | 1    | μА    |

| Control)                                         |                   | -                  | 0, 10                  | 10                     | -     | 0.01                 | 1    | -    | -                      | -    | μА    |

| Three-State Output Leakage                       | I <sub>OUT</sub>  | 0, 5               | 0, 5                   | 5                      | -     | 0.01                 | 1    | -    | 0.02                   | 2    | μΑ    |

| Current                                          |                   | 0, 10              | 0, 10                  | 10                     | -     | 0.02                 | 2    | -    | -                      | -    | μΑ    |

| Pull-Down Resistor Value (S1-S8, Shift, Control) | R <sub>PD</sub>   | -                  | -                      | -                      | 7     | 14                   | 24   | 7    | 14                     | 24   | kΩ    |

| Operating Current<br>(All Outputs Unloaded)      |                   |                    |                        |                        |       |                      |      |      |                        |      |       |

| $f_{CL} = 0.4MHz$                                | I <sub>OPER</sub> | 0.5, 4.5           | 0, 5                   | 5                      | -     | 0.6                  | -    | -    | 0.6                    | -    | mA    |

| $f_{CL} = 0.8MHz$                                |                   | 1, 9               | 0, 10                  | 10                     | -     | 2.7                  | -    | -    | -                      | -    | mA    |

#### NOTE:

<sup>1.</sup> Typical values are for  $T_A = +25^{\circ}C$  and nominal  $V_{DD}$ .

# Functional Description of CDP1871A Terminals

#### D1 - D11 (Outputs):

Drive lines for the 11 x 8 keyboard switch matrix. These outputs are connected through the external switch matrix to the sense lines (S1 - S8).

#### S1 - S8 (Inputs):

Sense lines for the 11 x 8 keyboard maxtrix. These inputs have internal pull-down resistors and are driven high by appropriate drive line when a keyboard switch is closed.

#### CS1, CS2, CS3, CS4 (Inputs):

Chip select inputs, which are used to enable the three-state data bus outputs (BUS 0 - BUS 7) and to enable the resetting of the status flag ( $\overline{DA}$ ), which occurs on the low-to-high transition of TPB. These four inputs are normally connected to the N-lines (N0-N2) and  $\overline{MRD}$  output of the CDP1800-series microprocessor. (Table 2)

#### BUS 0 - BUS 7 (Outputs):

Three-state data bus outputs which provide the ASCII and HEX codes of the detected keys. The outputs are normally connected to the BUS 0 - BUS 7 terminals of the CDP1800-series microprocessor.

#### DA (Output):

The data available output flag which is set low when a valid key closure is detected. It is reset high by the low-to-high transition of TPB when data is read from the CDP1871A. This output is normally connected to a flag input ( $\overline{\text{EF1}}$  -  $\overline{\text{EF4}}$ ) of the CDP1800-series microprocessor.

#### TPB (Input):

The input clock used to drive the scan generator and reset the status flag  $(\overline{DA})$ . This input is normally connected to the TPB output of the CDP1800-series microprocessor.

#### RPT (Output):

The repeat output flag which is used to indicate that a key is still closed after data has been read from the CDP1871A ( $\overline{DA}$  = high). It remains low as long as the key is closed and is used for an autorepeat function, under CPU control. This output is normally connected to a flag input ( $\overline{EF1}$  -  $\overline{EF4}$ ) of the CDP1800-series microprocessor.

#### **DEBOUNCE** (Input):

This input is connected to the junction of an external resistor to  $V_{DD}$  and capacitor to  $V_{SS}$ . It provides a debounce time delay (t  $\cong$  RC) after the release of a key. If a debounce is not desired, the external pull-up resistor is still required.

#### ALPHA, SHIFT, CONTROL (Inputs):

A high on the SHIFT or CONTROL inputs will be internally latched (after the debounce time) and the drive and sense line decoding will be modified as shown in Table 3. They are normally connected to the keyboard, but produce no code by themselves. The SHIFT and CONTROL inputs have internal pull-down resistors to simplify use with momentary contact switches. The ALPHA input is not latched and is designed for a standard SPDT switch to provide an alpha-lock function. When ALPHA = 1 the drive and sense line decoding will be modified as shown in Table 3.

#### $V_{DD}$ , $V_{SS}$ :

$V_{DD}$  is the positive supply voltage input.  $V_{SS}$  is the most negative supply voltage terminal and is normal connected to ground. All outputs swing from  $V_{SS}$  to  $V_{DD}$ . The recommended input voltage swing is from  $V_{SS}$  to  $V_{DD}$ .

**TABLE 1. SWITCH INPUT FUNCTIONS**

| CONTROL | SHIFT | ALPHA | KEY FUNCTION |

|---------|-------|-------|--------------|

| 0       | 0     | 0     | Normal       |

| 1       | Х     | Х     | Control      |

| 0       | 1     | Х     | Shift        |

| 0       | 0     | 1     | Alpha        |

NOTE: X = Don't Care

#### **TABLE 2. VALID N-LINE CONNECTIONS**

|                        |     | CDP1871 | A SIGNAL    |    | CPU INPUT |

|------------------------|-----|---------|-------------|----|-----------|

| CPU                    | CS4 | CS3     | INSTRUCTION |    |           |

| CDP1800- Series Signal | MRD | N2      | N0          | N1 | INP5      |

|                        | MRD | N0      | N1          | N2 | INP3      |

|                        | MRD | N2      | N1          | N0 | INP6      |

#### TABLE 3. DRIVE AND SENSE LINE KEYBOARD CONNECTIONS (NOTE 2)

| SENSE          |    |   |    |    |   |                |   |                | DRIV | E LINE         | S   |         |                    |                 |                  |                  |                  |

|----------------|----|---|----|----|---|----------------|---|----------------|------|----------------|-----|---------|--------------------|-----------------|------------------|------------------|------------------|

| LINES          | D  | 1 |    | )2 | [ | O <sub>3</sub> | 0 | ) <sub>4</sub> |      | ) <sub>5</sub> |     | 6       | D <sub>7</sub>     | D <sub>8</sub>  | D <sub>9</sub>   | D <sub>10</sub>  | D <sub>11</sub>  |

| S <sub>1</sub> | SP | 0 | (  | 8  | í | @              | Н | Н              | Р    | Р              | Х   | Х       | Space              | 80 <sub>1</sub> | 88 <sub>16</sub> | 90 <sub>16</sub> | 98 <sub>16</sub> |

|                | 0  |   | 8  |    | @ | NUL            | h | BS             | р    | DLE            | х   | CA<br>N |                    | 6               |                  |                  |                  |

| S <sub>2</sub> | !  | 1 | )  | 9  | Α | А              | - | _              | Q    | Q              | Υ   | Υ       |                    | 81 <sub>1</sub> | 89 <sub>16</sub> | 91 <sub>16</sub> | 99 <sub>16</sub> |

|                | 1  |   | 9  |    | а | SOH            | - | H              | q    | DC1            | у   | EM      |                    | 6               |                  |                  |                  |

| S <sub>3</sub> | "  | 2 | *  | :  | В | В              | J | J              | R    | R              | Z   | Z       | Line<br>Feed       | 82 <sub>1</sub> | 8A <sub>16</sub> | 92 <sub>16</sub> | 9A <sub>16</sub> |

|                | 2  |   | •  |    | b | STX            | j | LF             | r    | DC2            | Z   | SU<br>B | reed               | 6               |                  |                  |                  |

| S <sub>4</sub> | #  | 3 | +  | ;  | С | С              | K | К              | S    | S              | {   | [       | Escape             | 83 <sub>1</sub> | 8B <sub>16</sub> | 93 <sub>16</sub> | 9B <sub>16</sub> |

|                | 3  |   | ;  |    | С | ETX            | k | VT             | S    | DC3            | [   | ES<br>C | 6                  | 6               |                  |                  |                  |

| S <sub>5</sub> | \$ | 4 | <  | ,  | D | D              | L | L              | Т    | Т              |     | \       |                    | 84 <sub>1</sub> | 8C <sub>16</sub> | 94 <sub>16</sub> | 9C <sub>16</sub> |

|                | 4  |   | ,  |    | d | EOT            | I | FF             | t    | DC4            | \   | FS      |                    |                 |                  |                  |                  |

| S <sub>6</sub> | %  | 5 | II | -  | Е | E              | М | М              | U    | U              | }   | ]       | Carriage<br>Return | 85 <sub>1</sub> | 8D <sub>16</sub> | 95 <sub>16</sub> | 9D <sub>16</sub> |

|                | 5  |   | ı  |    | е | ENQ            | m | CR             | u    | NA<br>K        | ]   | GS      | Retuin             | 6               |                  |                  |                  |

| S <sub>7</sub> | &  | 6 | ^  |    | F | F              | N | N              | ٧    | ٧              | ~   | 1       |                    | 86 <sub>1</sub> | 8E <sub>16</sub> | 96 <sub>16</sub> | 9E <sub>16</sub> |

|                | 6  |   |    |    | f | ACK            | n | so             | >    | SY<br>N        | 1   | RS      |                    | 6               |                  |                  |                  |

| S <sub>8</sub> | ı  | 7 | ?  | /  | G | G              | 0 | 0              | W    | W              | Del | -       | Delete             | 87 <sub>1</sub> | 8F <sub>16</sub> | 97 <sub>16</sub> | 9F <sub>16</sub> |

|                | 7  |   | /  |    | g | BEL            | 0 | SI             | W    | ЕТВ            | -   | US      |                    | 6               |                  |                  |                  |

| KFY: | SHIFT (Note 1) | ALPHA (Note 1)   |

|------|----------------|------------------|

| –    | NORMAL         | CONTROL (Note 1) |

#### NOTES:

- 1. CONTROL overrides SHIFT and ALPHA = No Response

- $2. \ \ Showing \ ASCII \ outputs \ for \ all \ combinations \ with \ and \ without \ SHIFT, \ ALPHA \ LOCK \ and \ CONTROL.$

- 3. Drive lines 8, 9, 10 and 11 generate non-ASCII hex values which can be used for special codes.

TABLE 4. HEXIDECIMAL VALUES OF ASCII CHARACTERS

|     |    |    |    | IADL |               |     |     |    | 2.5 | <u> </u> |   |   |     |

|-----|----|----|----|------|---------------|-----|-----|----|-----|----------|---|---|-----|

|     |    |    |    |      |               |     | 1   | T  | IM: | SD       | T |   |     |

|     |    |    |    |      | b7            | 0   | 0   | 0  | 0   | 1        | 1 | 1 | 1   |

|     |    |    |    |      | b6 — <b>→</b> | 0   | 0   | 1  | 1   | 0        | 0 | 1 | 1   |

|     |    | ВІ | TS |      | b5 →          | 0   | 1   | 0  | 1   | 0        | 1 | 0 | 1   |

|     | b4 | b3 | b2 | b1   | HEX           | 0   | 1   | 2  | 3   | 4        | 5 | 6 | 7   |

|     | 0  | 0  | 0  | 0    | 0             | NUL | DLE | SP | 0   | @        | Р | \ | р   |

|     | 0  | 0  | 0  | 1    | 1             | SOH | DC1 | !  | 1   | Α        | Q | а | q   |

|     | 0  | 0  | 1  | 0    | 2             | STX | DC2 | íí | 2   | В        | R | b | r   |

|     | 0  | 0  | 1  | 1    | 3             | ETX | DC3 | #  | 3   | С        | S | С | S   |

|     | 0  | 1  | 0  | 0    | 4             | EOT | DC4 | \$ | 4   | D        | Т | d | t   |

|     | 0  | 1  | 0  | 1    | 5             | ENQ | NAK | %  | 5   | E        | U | е | u   |

|     | 0  | 1  | 1  | 0    | 6             | ACK | SYN | &  | 6   | F        | ٧ | f | V   |

|     | 0  | 1  | 1  | 1    | 7             | BEL | ETB | /  | 7   | G        | W | g | w   |

| LSD | 1  | 0  | 0  | 0    | 8             | BS  | CAN | (  | 8   | Н        | Х | h | х   |

|     | 1  | 0  | 0  | 1    | 9             | HT  | EM  | )  | 9   | I        | Y | i | у   |

|     | 1  | 0  | 1  | 0    | А             | LF  | SUB | *  | :   | J        | Z | j | Z   |

|     | 1  | 0  | 1  | 1    | В             | VT  | ESC | +  | ;   | K        | [ | k | {   |

|     | 1  | 1  | 0  | 0    | С             | FF  | FS  | ,  | <   | L        | \ | I |     |

|     | 1  | 1  | 0  | 1    | D             | CR  | GS  | -  | =   | М        | ] | m | }   |

|     | 1  | 1  | 1  | 0    | Е             | SO  | RS  |    | >   | N        | 1 | n | ~   |

|     | 1  | 1  | 1  | 1    | F             | SI  | US  | /  | ?   | 0        | - | 0 | DEL |

#### Operation

The CDP1871A is made up of two major sections: the counter/scan-selection logic and the control logic (Figure 2). The counter and scan-selection logic scans the keyboard array using the drive lines (D1-D11) and the sense lines (S1-S8). The outputs of the internal 5-stage scancounter are conditionally encoded by the ALPHA, SHIFT, and CONTROL inputs (Table 1, Table 3) and are used to drive the D1-D11 output lines high one at a time. Each D1-D11 output may drive up to eight keys, which are sampled by the sense line inputs (S1-S8). The S1-S8 inputs are enabled by the internal 3-stage scancounter.

The control logic interfaces with the CDP1800-series I/O and timing signals to establish timing and status conditions for the CDP1871A.

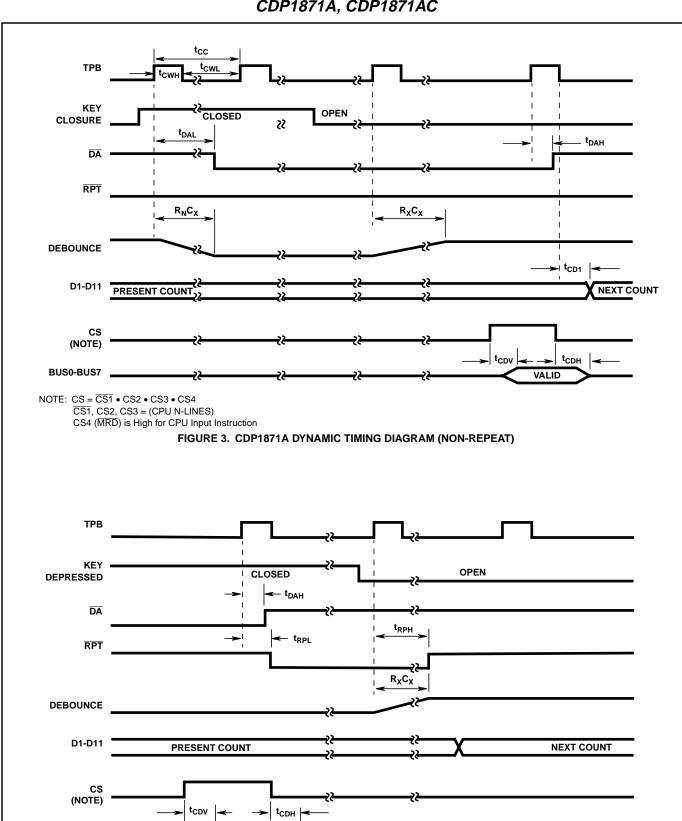

The TPB input clocks the scancounters and is also used to reset the Data Available output  $(\overline{DA})$ . When a valid keydown condition is detected on a sense line, the control logic inhibits the clock to the scancounters on the next low-to-high transition of TPB and the  $\overline{DA}$  output is set low. The scancounter

outputs (C1 - C8) represent the ASCII and HEX key codes and are used to drive the BUS 0 - BUS 7 outputs, which interface directly to the CDP1800-Series data bus. The BUS 0 - BUS 7 outputs, which are normally three-stated, are enabled by decoding the CS inputs during a CPU input instruction (Table 2). The low-to-high transition of TPB during the input instruction resets the  $\overline{\rm DA}$  output high. Once the  $\overline{\rm DA}$  output has been reset, it cannot go low again until the present key is released and a new keydown condition is detected. (This prevents unwanted repeated keycode outputs which may be caused by fast software routines).

After the depressed key is released and the debounce delay (determined by RX, CX) has occurred, the scan clock inhibit is removed, allowing the scancounters to advance on the following high-to-low transitions of TPB. This provides an N-key lockout feature, which prevents the entry of erroneous codes when two or more keys are pressed simultaneously. The first key pressed in the scanning order is recognized, while all other keys pressed are ignored until the first key is released

and read by the CPU, at which time the next key pressed in the scanning order is detected. If the first key remains closed after the CPU reads the data and resets the  $\overline{\text{DA}}$  output, on the low-to-high transition of TPB, an auxiliary signal ( $\overline{\text{RPT}}$ ) is generated and is available to the CPU to indicate an autorepeat condition. The  $\overline{\text{RPT}}$  output is reset high at the end of the debounce delay after the depressed key is released.

The DEBOUNCE input provides a terminal connection for an external user-selected RC circuit to eliminate false detection of a keydown condition caused by keyboard noise. The operation of the DEBOUNCE circuit is shown in Figure 2 (Pin 36). When a valid keydown is detected, the on-chip active-resistor device ( $R_N$ ) is enabled and the external capacitor

$(C_X)$  is discharged, providing a key closure debounce time  $\cong R_N C_X$ . This discharge is sensed by the Schmitt-trigger inverter, which clocks the  $\overline{DA}$  flip-flop (latching the  $\overline{DA}$  output low and inhibiting the scan clock). (The  $\overline{DA}$  F/F is reset by the low-to-high transition of TPB when the CS inputs are enabled). When a valid key-release is detected RN is disabled and  $C_X$  begins to charge through the external resistor  $(R_X)$ , providing a key-release debounce time  $\cong R_X C_X$ . This charge time is again sensed by the Schmitt-trigger inverter, enabling the scan clock to continue on the next high-to-low transitions of TPB, after the current keycode data is read by the CPU.

#### **Dynamic Electrical Specifications** At $T_A = -40$ to $+85^{\circ}$ C, $V_{DD} \pm 5\%$ , Unless Otherwise Specified

|                                  |                  |                        |       |                 | LIM   | IITS   |                 |        |        |

|----------------------------------|------------------|------------------------|-------|-----------------|-------|--------|-----------------|--------|--------|

|                                  |                  |                        | CDP18 | 371AD, CDP1     | 871AE | CDP187 | 1ACD, CDP1      | 871ACE |        |

| PARAMETER                        |                  | V <sub>DD</sub><br>(V) | MIN   | (NOTE 1)<br>TYP | MAX   | MIN    | (NOTE 1)<br>TYP | MAX    | UNITS  |

| Clock Cycle Time                 | t <sub>CC</sub>  | 5                      | -     | -               | -     | -      | -               | -      | Note 2 |

|                                  |                  | 10                     | -     | -               | -     | -      | -               | -      | Note 2 |

| Clock Pulse Width High           | t <sub>CWH</sub> | 5                      | 100   | 40              | -     | 100    | 40              | -      | ns     |

|                                  |                  | 10                     | 50    | 20              | -     | -      | -               | -      | ns     |

| Data Available Valid Delay       | t <sub>DAL</sub> | 5                      | -     | 260             | 500   | -      | 260             | 500    | ns     |

|                                  |                  | 10                     | -     | 130             | 250   | -      | -               | -      | ns     |

| Data Available Invalid Delay     | t <sub>DAH</sub> | 5                      | -     | 70              | 150   | -      | 70              | 150    | ns     |

|                                  |                  | 10                     | -     | 35              | 75    | -      | -               | =      | ns     |

| Scan Count Delay<br>(Non-Repeat) | t <sub>CD1</sub> | 5                      | -     | 850             | 1900  | -      | 850             | 1900   | ns     |

| (поп-кереаі)                     |                  | 10                     | -     | 425             | 950   | -      | -               | -      | ns     |

| Data Out Valid Delay             | t <sub>CDV</sub> | 5                      | -     | 120             | 250   | -      | 120             | 250    | ns     |

|                                  |                  | 10                     | -     | 60              | 125   | -      | -               | -      | ns     |

| Data Out Hold Time               | t <sub>CDH</sub> | 5                      | -     | 100             | 200   | -      | 100             | 200    | ns     |

|                                  |                  | 10                     | -     | 50              | 100   | -      | -               | -      | ns     |

| Repeat Valid Delay               | t <sub>RPL</sub> | 5                      | -     | 150             | 400   | -      | 150             | 400    | ns     |

|                                  |                  | 10                     | -     | 75              | 200   | -      | -               | -      | ns     |

| Repeat Invalid Delay             | t <sub>RPH</sub> | 5                      | -     | 350             | 700   | -      | 350             | 700    | ns     |

|                                  |                  | 10                     | -     | 170             | 350   | -      | -               | -      | ns     |

#### NOTES:

<sup>1.</sup> Typical values are for  $T_A = +25^{\circ}C$  and nominal  $V_{DD}$ .

<sup>2.</sup>  $t_{CC} = t_{CWH} + t_{CWL}$   $t_{CWL} = t_{CD1} + KC$ k = 0.9ns per pF

c = Keyboard capacitance (pF)

NOTE:  $CS = \overline{CS1} \cdot CS2 \cdot CS3 \cdot CS4$ CS1, CS2, CS3 = (CPU N-LINES) CS4 (MRD) is High for CPU Input Instruction

BUS0-BUS7

FIGURE 4. FIGURE 4. CDP1871A DYNAMIC TIMING DIAGRAM (REPEAT)

VALID

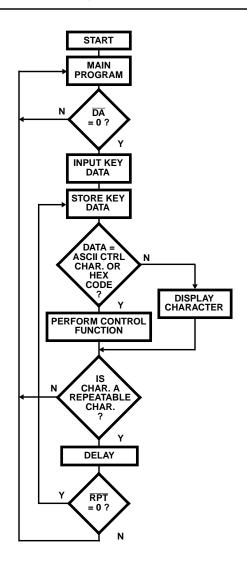

FIGURE 5. TYPICAL SYSTEM SOFTWARE FLOWCHART FOR CDP1871A, CDP1871AC

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com

#### Sales Office Headquarters

#### **NORTH AMERICA**

Intersil Corporation P. O. Box 883, Mail Stop 53-204 Melbourne, FL 32902 TEL: (407) 724-7000

FAX: (407) 724-7000

#### EUROPE

Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05

#### **ASIA**

Intersil (Taiwan) Ltd.

Taiwan Limited

7F-6, No. 101 Fu Hsing North Road

Taipei, Taiwan

Republic of China

TEL: (886) 2 2716 9310

FAX: (886) 2 2715 3029