# High-Performance 8-Bit CMOS EPROM Microcontrollers with 10-bit A/D

# PIC17LC752/756A is tested for high frequency, low voltage operation - 16 MHz @ 3V

## **Microcontroller Core Features:**

- · Only 58 single word instructions to learn

- All single cycle instructions (250 ns) except for program branches and table reads/writes which are two-cycle

- · Operating speed:

- DC 16 MHz clock input

- DC 250 ns instruction cycle

- 8 x 8 Single-Cycle Hardware Multiplier

- · Interrupt capability

- 16 level deep hardware stack

- · Direct, indirect, and relative addressing modes

- Internal/external program memory execution,

Capable of addressing 64K x 16 program memory space

| Dovice      | Men           | nory      |

|-------------|---------------|-----------|

| Device      | Program (x16) | Data (x8) |

| PIC17LC752  | 8K            | 678       |

| PIC17LC756A | 16K           | 902       |

# **Peripheral Features:**

- Up to 50 I/O pins with individual direction control

- 10-bit, multi-channel analog-to-digital converter

- High current sink/source for direct LED drive

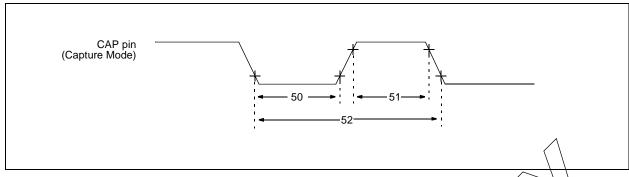

- · Four capture input pins

- Captures are 16-bit, max resolution 250 ns

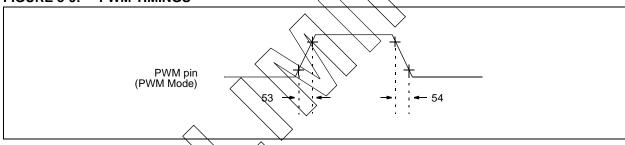

- Three PWM outputs (resolution is 1- to 10-bits)

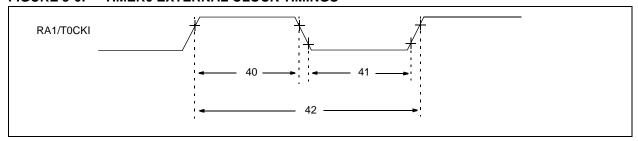

- TMR0: 16-bit timer/counter with 8-bit programmable prescaler

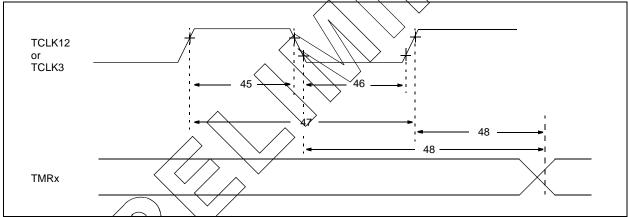

- TMR1: 8-bit timer/counter

- TMR2: 8-bit timer/counter

- TMR3: 16-bit timer/counter

- Two Universal Synchronous Asynchronous Receiver Transmitters (USART/SCI) with Independent baud rate generators

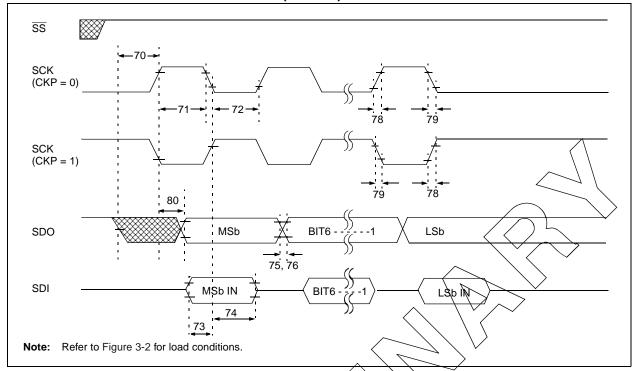

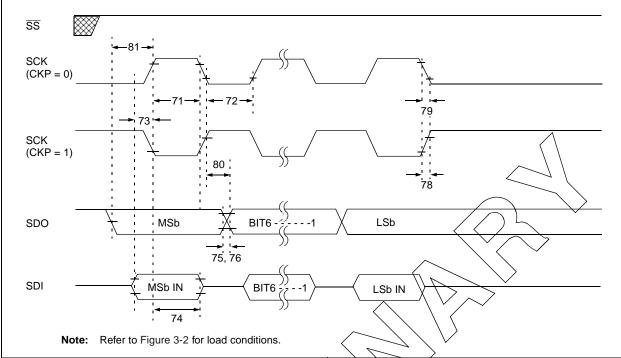

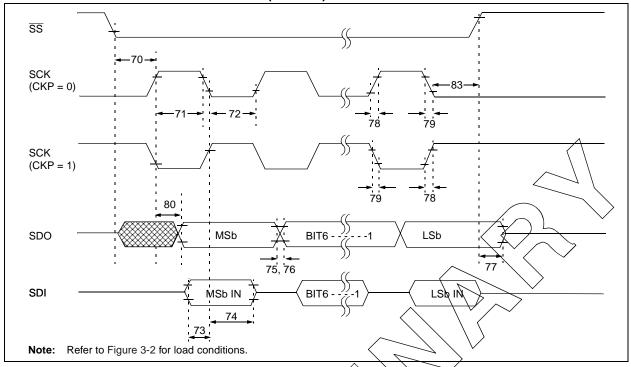

- Master Synchronous Serial Port (MSSP) with SPI™ and I<sup>2</sup>C™ modes (including I<sup>2</sup>C master mode)

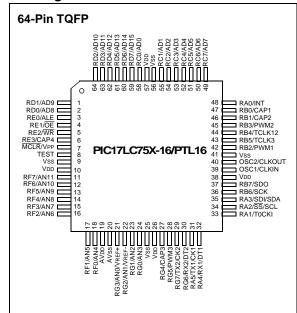

# **Pin Diagrams**

# **Special Microcontroller Features:**

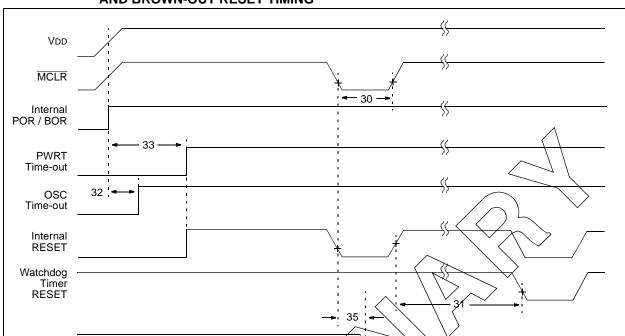

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- Brown-out Reset

- Code-protection

- · Power saving SLEEP mode

- · Selectable oscillator options

# **CMOS Technology:**

- Low-power, high-speed CMOS EPROM technology

- · Fully static design

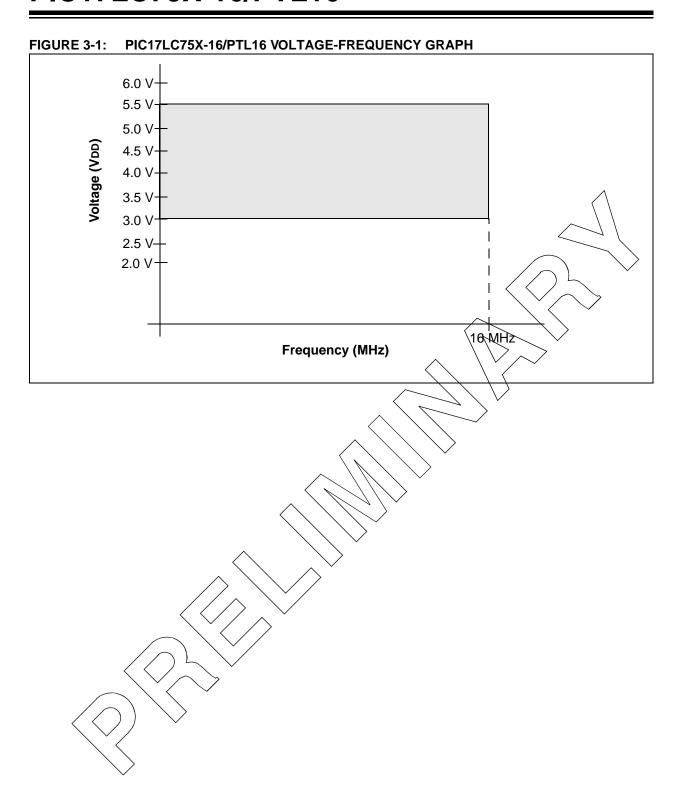

- Wide operating voltage range (3.0V to 5.5V)

- · Commercial and Industrial temperature ranges

- Low-power consumption

- < 5 mA @ 5V, 4 MHz

- 100 μA typical @ 4.5V, 32 kHz

- < 1 μA typical standby current @ 5V

## **Table of Contents**

| 1.0 Overview                   | 3  |

|--------------------------------|----|

| 2.0 Development Support        |    |

| 3.0 Electrical Characteristics |    |

| 4.0 DC and AC Characteristics  |    |

| 5.0 Packaging Information      |    |

| Index                          | 39 |

| On-Line Support                |    |

| Reader Response                | 42 |

| Product Identification System  | 43 |

## To Our Valued Customers

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

#### **New Customer Notification System**

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

#### Frrata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended workarounds. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Corrections to this Data Sheet**

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please:

- Fill out and mail in the reader response form in the back of this data sheet.

- E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

# 1.0 OVERVIEW

This data sheet covers the PIC17LC752-16/PTL16 and PIC17LC756A-16/PTL16 devices. The functional characteristics of these devices are identical to the PIC17LC752A/756A devices. For electrical specifications, see the electrical specifications contained within this document. For all other information about these devices, see the PIC17C7XX data sheet (DS30289).

| Feature                             | es         | PIC17C752                 | PIC17LC752-16/PTL16  | PIC17C756A             | PIC17LC756A-16/PTL16 | PIC17C762                 | PIC17C766                 |  |

|-------------------------------------|------------|---------------------------|----------------------|------------------------|----------------------|---------------------------|---------------------------|--|

| Maximum Freque of Operation         | ncy        | 33 MHz                    | 16 MHz               | 33 MHz                 | 16 MHz               | 33 MHz                    | 33 MHz                    |  |

| Operating Voltage                   | Range      | 3.0 - 5.5V                | 3.0 - 5.5V           | 3.0 - 5.5V             | 3.0 - 5.5V           | 3.0 - 5.5V                | 3.0 - 5.5V                |  |

| Program                             | (EPROM)    | 8K                        | 8K                   | 16K                    | 16K                  | 8K                        | 16K                       |  |

| Memory (x16)                        | (ROM)      | _                         | _                    | _                      | _                    | _                         | _                         |  |

| Data Memory (by                     | tes)       | 678                       | 678                  | 902                    | 902                  | 678                       | 902                       |  |

| Hardware Multipli                   | er (8 x 8) | Yes                       | Yes                  | Yes                    | Yes                  | Yes                       | Yes                       |  |

| Timer0<br>(16-bit + 8-bit pos       | stscaler)  | Yes                       | Yes                  | Yes                    |                      |                           | Yes                       |  |

| Timer1 (8-bit)                      |            | Yes                       | Yes                  | Yes                    | Yes                  | Yes                       | Yes                       |  |

| Timer2 (8-bit)                      |            | Yes                       | Yes                  | Yes                    | Yes                  | Yes                       | Yes                       |  |

| Timer3 (16-bit)                     |            | Yes                       | Yes                  | Yes                    | Yes                  | Yes                       | Yes                       |  |

| Capture inputs (16-bit)             |            | 4                         | 4                    | 4                      | 4                    | 4                         | 4                         |  |

| PWM outputs (up to 10-bit)          |            | 3                         | 3                    | 3                      | 3                    | 3                         | 3                         |  |

| USART/SCI                           |            | 2                         | 2                    | 2                      | 2                    | 2                         | 2                         |  |

| A/D channels (10-bit)               |            | 12                        | 12                   | 12                     | 12                   | 16                        | 16                        |  |

| SSP (SPI/I <sup>2</sup> C w/M mode) | Master     | Yes                       | Yes                  | Yes                    | Yes Yes              |                           | Yes                       |  |

| Power-on Reset                      |            | Yes                       | Yes                  | Yes                    | Yes                  | Yes                       | Yes                       |  |

| Watchdog Timer                      |            | Yes                       | Yes                  | Yes                    | Yes                  | Yes                       | Yes                       |  |

| External Interrupt                  | S          | Yes                       | Yes                  | Yes                    | Yes                  | Yes                       | Yes                       |  |

| Interrupt Sources                   |            | 18                        | 18                   | 18                     | 18                   | 18                        | 18                        |  |

| Code Protect                        |            | Yes                       | Yes                  | Yes                    | Yes                  | Yes                       | Yes                       |  |

| Brown-out Reset                     |            | Yes                       | Yes                  | Yes                    | Yes                  | Yes                       | Yes                       |  |

| In-circuit Serial Pr                | rogramming | Yes                       | Yes                  | Yes                    | Yes                  | Yes                       | Yes                       |  |

| I/O Pins                            |            | 50                        | 50                   | 50                     | 50                   | 66                        | 66                        |  |

| I/O High Current                    | Source     | 25 mA                     | 25 mA                | 25 mA                  | 25 mA                | 25 mA                     | 25 mA                     |  |

| Capability                          | Sink       | 25 mA <sup>(1)</sup>      | 25 mA <sup>(1)</sup> | 25 mA <sup>(1)</sup>   | 25 mA <sup>(1)</sup> | 25 mA <sup>(1)</sup>      | 25 mA <sup>(1)</sup>      |  |

| Package Types                       |            | 68-pin LCC<br>68-pin TQFP | 64-pin TQFP          | 68-pin LCC 64-pin TQFP |                      | 80-pin QFP<br>84-pin PLCC | 80-pin QFP<br>84-pin PLCC |  |

TABLE 1-1:

PIC17C7XX FAMILY OF DEVICES

PIC17LC75X-16/PTL16

Note 1: Pins RA2 and RA3 can sink up to 60 mA.

# 2.0 DEVELOPMENT SUPPORT

The PICmicro<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- · Integrated Development Environment

- MPLAB™ IDE Software

- Assemblers/Compilers/Linkers

- MPASM Assembler

- MPLAB-C17 and MPLAB-C18 C Compilers

- MPLINK/MPLIB Linker/Librarian

- Simulators

- MPLAB-SIM Software Simulator

- Emulators

- MPLAB-ICE Real-Time In-Circuit Emulator

- PICMASTER®/PICMASTER-CE In-Circuit Emulator

- ICEPIC™

- In-Circuit Debugger

- MPLAB-ICD for PIC16F877

- · Device Programmers

- PRO MATE® II Universal Programmer

- PICSTART® Plus Entry-Level Prototype Programmer

- · Low-Cost Demonstration Boards

- PICDEM-17

# 2.1 <u>MPLAB Integrated Development</u> <u>Environment Software</u>

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a Windows®-based application which contains:

- · Multiple functionality

- editor

- simulator

- programmer (sold separately)

- emulator (sold separately)

- · A full featured editor

- · A project manager

- · Customizable tool bar and key mapping

- · A status bar

- · On-line help

MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PICmicro tools (automatically updates all project information)

- · Debug using:

- source files

- absolute listing file

- object code

The ability to use MPLAB with Microchip's simulator, MPLAB-SIM, allows a consistent platform and the ability to easily switch from the cost-effective simulator to the full featured emulator with minimal retraining.

## 2.2 MPASM Assembler

MPASM is a full featured universal macro assembler for all PICmicro MCU's. It can produce absolute code directly in the form of HEX files for device programmers, or it can generate relocatable objects for MPLINK.

MPASM has a command line interface and a Windows shell and can be used as a standalone application on a Windows 3.x or greater system. MPASM generates relocatable object files, Intel standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file which contains source lines and generated machine code, and a COD file for MPLAB debugging.

MPASM features include:

- MPASM and MPLINK are integrated into MPLAB projects.

- MPASM allows user defined macros to be created for streamlined assembly.

- MPASM allows conditional assembly for multi purpose source files.

- MPASM directives allow complete control over the assembly process.

# 2.3 MPLAB-C17 and MPLAB-C18 C Compilers

The MPLAB-C17 and MPLAB-C18 Code Development Systems are complete ANSI 'C' compilers and integrated development environments for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

# 2.4 MPLINK/MPLIB Linker/Librarian

MPLINK is a relocatable linker for MPASM and MPLAB-C17 and MPLAB-C18. It can link relocatable objects from assembly or C source files along with precompiled libraries using directives from a linker script.

MPLIB is a librarian for pre-compiled code to be used with MPLINK. When a routine from a library is called from another source file, only the modules that contains that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications. MPLIB manages the creation and modification of library files.

#### MPLINK features include:

- MPLINK works with MPASM and MPLAB-C17 and MPLAB-C18.

- MPLINK allows all memory areas to be defined as sections to provide link-time flexibility.

#### MPLIB features include:

- MPLIB makes linking easier because single libraries can be included instead of many smaller files.

- MPLIB helps keep code maintainable by grouping related modules together.

- MPLIB commands allow libraries to be created and modules to be added, listed, replaced, deleted, or extracted.

## 2.5 MPLAB-SIM Software Simulator

The MPLAB-SIM Software Simulator allows code development in a PC host environment by simulating the PICmicro series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file or user-defined key press to any of the pins. The execution can be performed in single step, execute until break, or trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C17 and MPLAB-C18 and MPASM. The Software Simulator offers the flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

# 2.6 MPLAB-ICE High Performance Universal In-Circuit Emulator with MPLAB IDE

The MPLAB-ICE Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PICmicro microcontrollers (MCUs). Software control of MPLAB-ICE is provided by the MPLAB Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB-ICE allows expansion to support new PICmicro microcontrollers.

The MPLAB-ICE Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows 3.x/95/98 environment were chosen to best make these features available to you, the end user.

MPLAB-ICE 2000 is a full-featured emulator system with enhanced trace, trigger, and data monitoring features. Both systems use the same processor modules and will operate across the full operating speed range of the PICmicro MCU.

## 2.7 PICMASTER/PICMASTER CE

The PICMASTER system from Microchip Technology is a full-featured, professional quality emulator system. This flexible in-circuit emulator provides a high-quality, universal platform for emulating Microchip 8-bit PICmicro microcontrollers (MCUs). PICMASTER systems are sold worldwide, with a CE compliant model available for European Union (EU) countries.

## 2.8 ICEPIC

ICEPIC is a low-cost in-circuit emulation solution for the Microchip Technology PIC16C5X, PIC16C6X, PIC16C7X, and PIC16CXXX families of 8-bit one-time-programmable (OTP) microcontrollers. The modular system can support different subsets of PIC16C5X or PIC16CXXX products through the use of interchangeable personality modules or daughter boards. The emulator is capable of emulating without target application circuitry being present.

# 2.9 PRO MATE II Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode. PRO MATE II is CE compliant.

The PRO MATE II has programmable VDD and VPP supplies which allow it to verify programmed memory at VDD min. and VDD max. for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In stand-alone mode the PRO MATE II can read, verify or program PICmicro devices. It can also set code-protect bits in this mode.

# 2.10 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, low-cost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

PICSTART Plus supports all PICmicro devices with up to 40 pins. Larger pin count devices such as the PIC16C92X, and PIC17C76X may be supported with an adapter socket. PICSTART Plus is CE compliant.

#### 2.11 **PICDEM-17**

The PICDEM-17 is an evaluation board that demonstrates the capabilities of several Microchip microconincluding PIC17C752, PIC17C756. PIC17C762, and PIC17C766. All necessary hardware is included to run basic demo programs, which are supplied on a 3.5-inch disk. A programmed sample is included, and the user may erase it and program it with the other sample programs using the PRO MATE II or PICSTART Plus device programmers and easily debug and test the sample code. In addition, PICDEM-17 supports down-loading of programs to and executing out of external FLASH memory on board. The PICDEM-17 is also usable with the MPLAB-ICE or PICMASTER emulator, and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

**DEVELOPMENT TOOLS FROM MICROCHIP TABLE 2-1:**

| MCP2510  MCRFXXX  HCSXXX  24CXX/ 25CXX/ PIC18CXXZ  PIC16C9XX  PIC16C9XX  PIC16C9XX | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \     | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | `                   | · · · · · · · · · · · · · · · · · · · | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` | ```                           | · · · · · · · · · · · · · · · · · · ·        | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                 |             | >        |          |          |            |           | · · · · · · · · · · · · · · · · · · · |                        |                           |                                 | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \            | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \              | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

|------------------------------------------------------------------------------------|-------------------------------------------|---------------------------------------|---------------------|---------------------------------------|---------------------------------------|---------------------------------------|-----------------------------------------|-------------------------------|----------------------------------------------|-------------------------------------------------------|-------------|----------|----------|----------|------------|-----------|---------------------------------------|------------------------|---------------------------|---------------------------------|--------------------------------------------------|----------------------------------------------------|---------------------------------------|

|                                                                                    |                                           |                                       |                     |                                       |                                       |                                       |                                         | *>                            |                                              |                                                       |             | +        | +        |          |            |           |                                       |                        |                           |                                 |                                                  |                                                    |                                       |

| PIC16C6X                                                                           | `                                         |                                       |                     | `                                     | ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` | ` <u>`</u>                            | >                                       | *                             | ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` `        | ``````````````````````````````````````                |             | >        | +        |          |            |           |                                       |                        |                           |                                 |                                                  |                                                    |                                       |

| PIC12CXX)                                                                          | ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` `     |                                       |                     | ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` | ` '                                   | ` '                                   | ` <u>`</u>                              |                               | ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` `        | >                                                     | <i>&gt;</i> | >        |          |          | ^          |           |                                       |                        |                           |                                 |                                                  |                                                    |                                       |

|                                                                                    | MPLAB™ Integrated Development Environment | MPLAB™ C17 Compiler                   | MPLAB™ C18 Compiler | MPASM/MPLINK                          | MPLAB™-ICE                            | PICMASTER/PICMASTER-CE                | ICEPIC™ Low-Cost                        | MPLAB-ICD In-Circuit Debugger | PICSTART®Plus<br>Low-Cost Universal Dev. Kit | E<br>PRO MATE <sup>®</sup> II<br>Universal Programmer | SIMICE      | PICDEM-1 | PICDEM-2 | PICDEM-3 | PICDEM-14A | PICDEM-17 | KEELoq® Evaluation Kit                | KEELOQ Transponder Kit | microlD™ Programmer's Kit | 125 kHz microID Developer's Kit | 125 kHz Anticollision microID<br>Developer's Kit | 13.56 MHz Anticollision microlD<br>Developer's Kit | MCP2510 CAN Developer's Kit           |

# 3.0 PIC17LC75X-16/PTL16 ELECTRICAL CHARACTERISTICS

## **Absolute Maximum Ratings †**

| Ambient temperature under bias                                                                                                                                                                           | 55°C to +125°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Storage temperature                                                                                                                                                                                      | 65°C to +150°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Voltage on VDD with respect to Vss                                                                                                                                                                       | 0V to +7.5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Voltage on MCLR with respect to Vss (Note 2)                                                                                                                                                             | 0.3V to +14V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Voltage on RA2 and RA3 with respect to Vss                                                                                                                                                               | 0.3V to +8.5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Voltage on all other pins with respect to Vss                                                                                                                                                            | 0.3½ to VDD + 0.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Total power dissipation (Note 1)                                                                                                                                                                         | 1.0W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Maximum current out of Vss pin(s) - total (@ 70°C)                                                                                                                                                       | 500 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Maximum current into VDD pin(s) - total (@ 70°C)                                                                                                                                                         | 500 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Input clamp current, lik (VI < 0 or VI > VDD)                                                                                                                                                            | ±20 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Output clamp current, IOK (VO < 0 or VO > VDD)                                                                                                                                                           | ±20 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Maximum output current sunk by any I/O pin (except RA2 and RA3)                                                                                                                                          | 35 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Maximum output current sunk by RA2 or RA3 pins  Maximum output current sourced by any I/O pin  Maximum current sunk by PORTA and PORTB (combined)  Maximum current sourced by PORTA and PORTB (combined) | 60 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Maximum output current sourced by any I/O pin                                                                                                                                                            | 20 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Maximum current sunk by PORTA and PORTB (combined)                                                                                                                                                       | 150 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Maximum current sourced by PORTA and PORTB (combined)                                                                                                                                                    | 100 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Maximum current sunk by PORTC, PORTD and PORTE (combined)                                                                                                                                                | 150 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Maximum current sourced by PORTC, PORTD and PORTE (sombined)                                                                                                                                             | 100 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Maximum current sunk by PORTF and PORTG (combined)                                                                                                                                                       | 150 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Maximum current sourced by PORTF and PORTG (combined)                                                                                                                                                    | 100 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Note to Developing the instantian in colorated as fallow Discharge (Inc. 7 Inc.)                                                                                                                         | $\Sigma (() / z = 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + 1 / z + $ |

**Note 1:** Power dissipation is calculated as follows:  $Pdis \neq VdQx \times \{IDD - \Sigma IOH\} + \sum \{(VDD-VOH) \times IOH\} + \sum \{(VOL \times IOL)\} \times \{(VDD-VOH) \times IOH\} + \sum \{(VDD-$

Note 2: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin, rather than pulling this pin directly to Vss.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

CAUTION: ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000V readily accumulate on the human body and test equipment and can discharge without detection. Although the PIC17LC75X 16/PTL16 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

# 3.1 DC CHARACTERISTICS: PIC17LC75X-16/PTL16 (Commercial)

| DC CHAI              | RACTERIS       | TICS                                                             | Standard Op<br>Operating te |            |            |                | ess otherwise stated)<br>≤ +70°C for commercial                                     |

|----------------------|----------------|------------------------------------------------------------------|-----------------------------|------------|------------|----------------|-------------------------------------------------------------------------------------|

| Param.<br>No.        | Sym            | Characteristic                                                   | Min                         | Typ†       | Max        | Units          | Conditions                                                                          |

| D001                 | VDD            | Supply Voltage                                                   | 3.0                         | _          | 5.5        | V              |                                                                                     |

| D002                 | VDR            | RAM Data Retention<br>Voltage (Note 1)                           | 1.5 *                       | -          | _          | V              | Device in SLEEP mode                                                                |

| D003                 | VPOR           | VDD start voltage to<br>ensure internal<br>Power-on Reset signal | -                           | Vss        | -          | V              | See section on Power-on<br>Reset for details                                        |

| D004                 | SVDD           | VDD rise rate to ensure proper operation                         | 0.010 *                     | _          | -          | V/ms           | See Section on Power-on<br>Reset for details                                        |

| D005                 | VBOR           | Brown-out Reset voltage trip point                               | 3.65                        | -          | 4.35       | X              |                                                                                     |

| D006                 | VPORTP         | Power-on Reset trip point                                        | -                           | 2.2        | <u> </u>   |                | VØD = VPORTP                                                                        |

| D010<br>D011<br>D014 | IDD            | Supply Current<br>(Note 2)                                       | -<br>-<br>-                 | 3 85       | 6 *<br>150 | mA<br>mA<br>μA | FOSC = 4 MHz (Note 4) FOSC = 16 MHz, VDD = 3V FOSC = 32 kHz, (EC osc configuration) |